# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

## ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# R8A66597FP/DFP/BG

ASSP (USB2.0 2Port Host/1Port Peripheral Controller)

RJJ03F0130-0102 Rev1.02 2008.10.17

# 1概要

## 1.1 概要

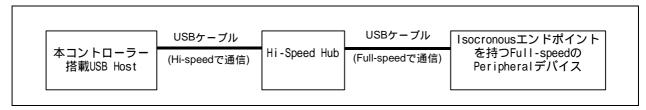

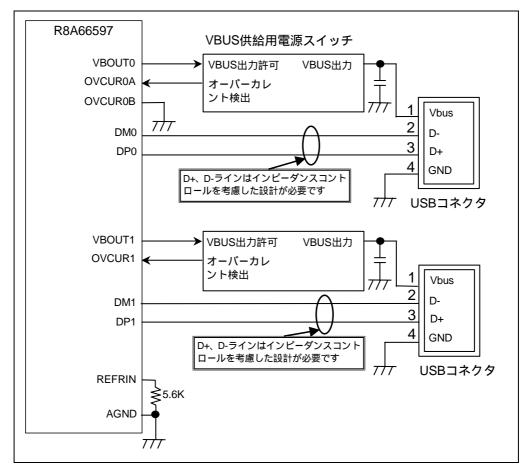

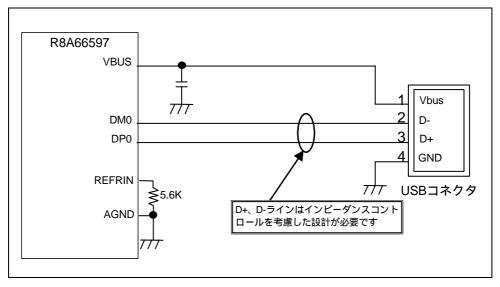

R8A66597は、USBホスト機能及びペリフェラル機能を備えたOn-The-Go対応のUSBコントローラーです。 ホストコントローラー機能選択時は、USB (Universal Serial Bus) 規格Rev.2.0のHi-Speed転送、Full-Speed転送、 Low-Speed転送に対応し、USBポートを2ポート使用可能です。

ペリフェラルコントローラー機能選択時は、USB規格Rev.2.0のHi-Speed転送、Full-Speed転送に対応し、USBポートを1ポート使用可能です。

本コントローラーは、USBトランシーバを内蔵し、USB規格Rev.2.0で定義されている全転送タイプに対応しています。

本コントローラーは、データ転送用に8.5Kバイトのバッファメモリを内蔵し、最大10本のパイプを使用できます。また、パイプ1-9に対しては、通信を行うペリフェラル機器やユーザーシステムに合わせた、任意のエンドポイントアドレスの割り付けが可能です。CPUとの接続は、セパレートバスとマルチプレクスバスのどちらかを選択できます。また、CPUバスインタフェースとは独立したスプリットバスインタフェース(DMAインタフェース専用)を備え、高速大容量データ転送を要求されるシステムに適しています。

## 1.2 特長

#### 1.2.1 USB Hi-Speed対応のホストコントローラーとペリフェラルコントローラーを内蔵

- USBホストコントローラーとペリフェラルコントローラーを内蔵

- USBホスト機能とペリフェラル機能をレジスタ設定により切り替え可能

- USBトランシーバ内蔵

#### 1.2.2 低消費電力

- 1.5Vコア電源採用による動作時の低消費電力を実現

- Low Power Sleep Mode機能搭載により、携帯機器向けにも適したUSB未使用時の低消費電力を実現

- USB機能未使用時にVIF電源のみオンにすることにより、待機電流を非常に小さく抑える事が可能

- 1.5Vコア電源用のレギュレータを内蔵し、3.3V単一電源で動作可能

## 1.2.3 省スペース実装対応

- 少ない外付け素子かつ省スペース実装が可能

- ・VBUS信号をコントローラーの入力端子に直接接続可能

- ・D+プルアップ抵抗内蔵(ペリフェラル機能選択時)

- ・D+、D-のプルダウン抵抗内蔵(ホスト機能選択時)

- ・D+、D-終端抵抗内蔵(Hi-Speed動作時)

- ・D+、D-出力抵抗内蔵 (Full/Low-Speed動作時)

### 1.2.4 USB全転送タイプに対応

- アイソクロナス転送対応を含むUSB全転送タイプに対応

- ・コントロール転送

- ・バルク転送

- ・インタラプト転送(High Bandwidthは非対応)

- ・アイソクロナス転送(High Bandwidthは非対応)

#### 1.2.5 パスインタフェース

- 16bitCPUバスインタフェース

- ・16bitセパレートバス/16bitマルチプレクスバス対応

- ・8/16bit単位DMA転送対応(スレーブ機能)

- 8bitスプリットバス(外部DMAC専用)インタフェース

- DMAインタフェースを2ch内蔵

- DMA転送により40Mバイト/秒の高速データ転送が可能

#### 1.2.6 パイプコンフィグレーション

- USB通信用バッファメモリを8.5Kバイト内蔵

- 最大10本のパイプを選択可能(デフォルトコントロールパイプを含む)

- プログラマブルなパイプ構成

- パイプ1-9は任意のエンドポイントアドレスを割り付け可能

- 各パイプの設定可能な転送条件

- ・パイプ0:コントロール転送、シングルバッファで256バイト固定

- ・パイプ1~2:バルク転送 / アイソクロナス転送、連続転送モード、 バッファサイズはプログラマブル (片面最大2Kバイトまで指定可能、ダブルバッファ指定可能)

- ・パイプ3~5:バルク転送、連続転送モード、

- バッファサイズはプログラマブル(片面最大2Kバイトまで指定可能、ダブルバッファ指定可能)

- ・パイプ6~9:インタラプト転送、シングルバッファで64バイト固定

## 1.2.7 ホスト機能選択時の特長

- Hi-Speed転送 (480Mbps)、Full-Speed転送 (12Mbps)及び、Low-Speed転送 (1.5Mbps)に対応

- ハブを1段経由し、複数のペリフェラル機器と接続可能

- リセットハンドシェイク自動応答

- SOF、パケット送信のスケジュールを自動化

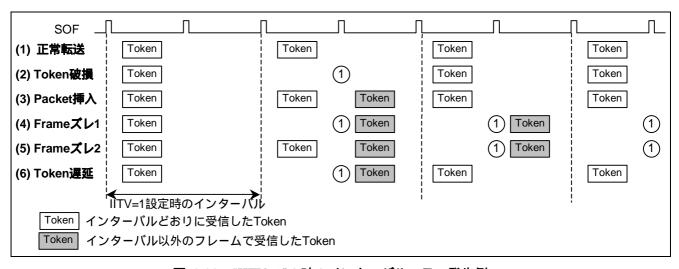

- アイソクロナス転送、インタラプト転送の転送インターバル設定機能

### 1.2.8 ペリフェラル機能選択時の特長

- Hi-Speed転送 (480Mbps)とFull-Speed転送 (12Mbps)に対応

- リセットハンドシェイク自動応答による、Hi-Speed動作、もしくはFull-Speed動作自動認識

- コントロール転送ステージ管理機能

- デバイスステート管理機能

- SET ADDRESSリクエストに対する自動応答機能

- NAK応答割り込み機能(NRDY)

- SOF補間機能

#### 1.2.9 On-the-go対応を容易にする機能

- 起動時のA-Device/B-Device判定を容易にするためのID端子及びID端子モニタービットを内蔵

- Host Negotiation Protocolを容易にするための制御ビットを搭載

### 1.2.10 その他の機能

- バイトエンディアンスワップ機能により、ビッグエンディアン、リトルエンディアンのどちらのCPUにも対応可能

- トランザクションカウントによるトランスファー終了機能

- 外部トリガ(DEND端子)によるDMA転送の終了機能

- SOFパルス出力機能

- PLL内蔵により、3種類の入力クロック選択可能

- ・48MHz/24MHz/12MHzから選択

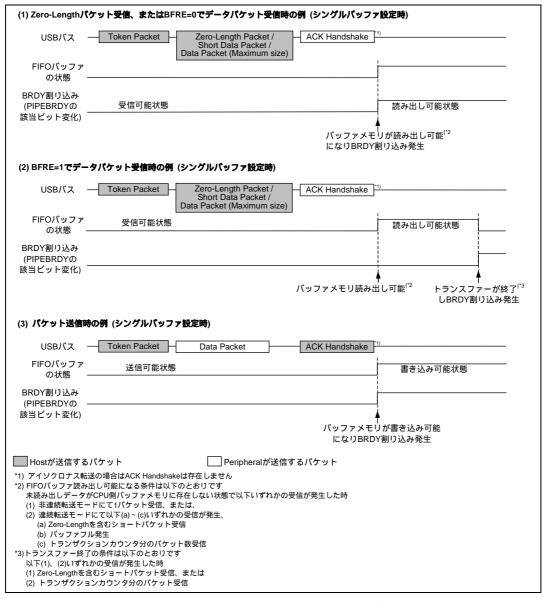

- BRDY割り込みイベント通知タイミング変更機能(BFRE)

- DxFIFOポートで指定したパイプのデータ読み出し後自動バッファメモリクリア機能(DCLRM)

- クロック停止状態からの自動クロック供給機能

- トランスファー終了による応答PIDのNAK設定機能(SHTNAK)

## 1.2.11 用途

ナビゲーションシステム、DVDレコーダ、セットトップボックス、オーディオ機器、プリンタ、外部ストレージ機器、 その他USB搭載の機器全般

## 1.3 パッケージ

#### ピン配置図 1.3.1

に本コントローラーの端子配置図 (上面図) を示します。

図 1.1 R8A66597FP/DFP端子配置図

|    |                                                                                             |         |            | R8A    | 6659   | 7BG     |         |       |      |   |  |

|----|---------------------------------------------------------------------------------------------|---------|------------|--------|--------|---------|---------|-------|------|---|--|

|    |                                                                                             | 7.      | <b>ドール</b> | /配置    | ( T    | OP V    | IEW     | )     |      |   |  |

|    | 1                                                                                           | 2       | 3          | 4      | 5      | 6       | 7       | 8     | 9    | - |  |

| Α  | GND                                                                                         | D15     | D14        | D10    | GND    | D5/AD5  | D2/AD2  | D0    | GND  | A |  |

| В  | VIF                                                                                         | INT_N   | D13        | D11    | VIF    | D4/AD4  | D1/AD1  | CS_N  | VIF  | В |  |

| С  | DREQ0_N                                                                                     | DACK0_N | SOF_N      | D9     | D7/AD7 | D3/AD3  | WR1_N   | WR0_N | RD_N | С |  |

| D  | DREQ1_N                                                                                     | DACK1_N | DEND0_N    | D12    | D8     | D6/AD6  | A6      | A4    | A5   | D |  |

| E  | GND                                                                                         | VDD     | DEND1_N    | SD0    | GND    | A7/ALE  | А3      | VDD   | GND  | E |  |

| F  | SD2                                                                                         | SD3     | SD4        | SD1    | VBOUT0 | A2      | GND     | MPBUS | A1   | F |  |

| G  | SD5                                                                                         | SD6     | AVCC       | VBOUT1 | OVCUR1 | EXTLP0  | ID0     | RST_N | VCC  | G |  |

| Н  | VIF                                                                                         | SD7     | XIN        | AGND   | VCC    | OVCUR0B | OVCUR0A | GND   | VBUS | н |  |

| J  | GND                                                                                         | VCC     | XOUT       | REFRIN | DM1    | DP1     | GND     | DM0   | DP0  | J |  |

|    | 1 2 3 4 5 6 7 8 9                                                                           |         |            |        |        |         |         |       |      |   |  |

| Lo | 各信号名の"_N"は パッケージ<br>Lowアクティブであることを<br>示します。 R8A66597BG: PLBG0081KA-A: 81pinLFBGA (0.5mmピッチ) |         |            |        |        |         |         |       |      |   |  |

図 1.2 R8A66597BG端子配置図

## 1.4 端子説明

表 1.1に本コントローラーの端子説明表を、表 1.2に未使用端子の処理方法を示します。

表 1.1 端子説明表

| 区分      | 端子名       | 名称                  | I/O | 機能                                               | 端子数 | 端子のネ         | 犬態 *5)       |

|---------|-----------|---------------------|-----|--------------------------------------------------|-----|--------------|--------------|

|         |           |                     |     |                                                  |     | リセッ<br>ト中    | リセッ<br>ト直後   |

| CPUバスイ  | D15-0     | データバス               | I/O | I<br>16bitデータバスです。                               | 16  | *2)          | *2)          |

| ンタフェー   | L         | マルチプレクス             |     | マルチプレクスバス設定時、本端子群をデータ                            | . • | ~)           | ~)           |

| ス       |           | アドレスバス              |     | バスの一部(D7-D1)、もしくはアドレスバス                          |     |              |              |

|         |           |                     |     | (A7-A1)として時分割で用います。                              |     |              |              |

|         | A7-1      | アドレスバス              | IN  | 7bitアドレスバスです。                                    | 7   | 入力           | 入力           |

|         |           |                     |     | 16bitデータバスのためA0はありません。                           |     | *3)          | *3)          |

|         | ALE       | アドレスラッチ             | IN  | マルチプレクスバス設定時、A7端子をALE信号                          |     | 入力           | 入力           |

|         |           | イネーブル               |     | として使用します。                                        |     |              |              |

|         | CS_N      | チップセレクト             | IN  | "L"レベルで本コントローラーが選択されます。                          | 1   | 入力           | 入力           |

|         | 55.11     |                     |     |                                                  | 4   | *4)          | *4)          |

|         | RD_N      | リードストロー             | IN  |                                                  | 1   | 入力           | 入力           |

|         | WDO N     | ブ                   | INI | データを読み出します。                                      | 4   | \ <u>+</u>   | \            |

|         | WR0_N     | D7-0バイトライ           | IN  | 立ち上がりエッジでD7-D0を本コントローラー                          | ı   | 入力           | 入力           |

|         | WR1_N     | トストローブ<br>D15-8バイトラ | IN  | のレジスタに書き込みます。                                    | 1   | *4)          | *4)          |

|         | VVIX I_IN |                     | IIN | 立ち上がりエッジでD15-D8を本コントロー                           | ı   | 入力<br>*4)    | 入力<br>*4)    |

|         | MPBUS     | イトストローブ<br>バスモード選択  | IN  | ラーのレジスタに書き込みます。<br>"L"レベルでセパレートバスです。             | 1   | 入力           | 入力           |

|         | IVIPBUS   | ハスモート選択             | IIN | L レヘルとセハレートハスとり。<br> "H"レベルでマルチプレクスバスです。         | 1   | パル<br>*1)    | *1)          |

|         |           |                     |     | F レヘルとマルテフレクスハスとす。<br> "H"/"L"どちらかのレベルに固定してください。 |     | 1)           | 1)           |

| SPLITバス | SD7-0     | スプリットデー             | 1/0 |                                                  | 8   | 入力           | 入力           |

| インタフ    | 307-0     | タバス                 | 1/0 | ハフリッドハスが選択されている場合はスプ<br> リットバスのデータバスとして機能します。    | O   | ハハ<br>(Hi-Z) | ハハ<br>(Hi-Z) |

| エース     |           | 3/12                |     | サッドハスのナータハスとして機能しよす。<br>                         |     | (111-2)      | (111-2)      |

|         | DREQ0_N   | DMAリクエスト            | OUT | D0FIFOポート、D1FIFOポートのDMA転送リク                      | 2   | Н            | Н            |

|         | DREQ1_N   |                     |     | エストを通知します。                                       |     |              |              |

| ェース     |           | DMAアクノリッ            | IN  | D0FIFOポート、D1FIFOポートのDMAアクノリ                      | 2   | 入力           | 入力           |

|         | _         | ジ                   |     | ッジ信号を入力してください。                                   |     | , (, )       | , (, )       |

|         | DEND0_N   | DMA転送終了             | I/O |                                                  | 2   | 入力           | 入力           |

|         | DEND1_N   | , == 3              |     | 号として他の周辺チップまたはCPUから転送                            |     | (Hi-Z)       | (Hi-Z)       |

|         |           |                     |     | 終了信号を受け付けます。                                     |     | , ,          | , ,          |

|         |           |                     |     | <fifoポートアクセス読み出し方向時>出力信</fifoポートアクセス読み出し方向時>     |     |              |              |

|         |           |                     |     | 号として転送の最終データを示します。                               |     |              |              |

| 割り込み    | INT_N     | 割り込み                | OUT | "L"アクティブでUSB通信に関する各種割り込                          | 1   | Н            | Н            |

| /SOF出力  |           |                     |     | みを通知します。アクティブはデフォルト"L"                           |     |              |              |

|         |           |                     |     | アクティブですが、ソフトウェアでINTAビット                          |     |              |              |

|         |           |                     |     | の設定値を変更することにより、"H"アクティブ                          |     |              |              |

|         |           |                     |     | に設定可能です                                          |     |              |              |

|         | SOF_N     | SOFパルス出力            | OUT |                                                  | 1   | Н            | Н            |

|         | 2/12/     | 7×+= m ) +          |     | 力します。                                            | _   |              |              |

| クロック    | XIN       | 発振用入力               | IN  | XIN、XOUTの間に水晶振動子を接続してくださ                         | 1   |              |              |

|         | XOUT      | 上<br>発振用出力          | OUT | い。外部クロック入力する場合は、XINに外部<br>クロック信号を接続し、XOUTは開放してくだ | 1   |              |              |

|         | λου:      |                     |     | プロック信号を接続し、XOUTは開放してくた<br>さい。                    | •   |              |              |

| システム    | RST_N     | リセット信号              | IN  | 本コントローラーを"L"レベルで初期化します。                          | 1   | 入力(L)        | 入力(H)        |

| 制御      |           |                     |     |                                                  |     |              | ` ′          |

| USBバスイ  |           | USB D+データ           | I/O | USBバスのD+端子に接続してください。                             | 2   | 入力           | 入力           |

| ンタフェー   | DP1       |                     |     |                                                  |     | (Hi-Z)       | (Hi-Z)       |

| ス       | DM0       | USB D-データ           | I/O | USBバスのD-端子に接続してください。                             | 2   | 入力           | 入力           |

|         | DM1       |                     |     |                                                  |     | (Hi-Z)       | (Hi-Z)       |

| 区分       | 端子名     | 名称       | I/O  | 機能                                           | 端子数              | 端子のキ   | 犬態 *5) |

|----------|---------|----------|------|----------------------------------------------|------------------|--------|--------|

|          |         |          |      |                                              |                  | リセッ    | リセッ    |

|          |         |          |      |                                              |                  | ト中     | 卜直後    |

| VBUS     | VBUS    | VBUS入力   | IN   | <host controller機能選択時=""></host>             | 1                | 入力     | 入力     |

| 監視入力     |         |          |      | オープンまたは、USBバスのVbusに直接接続し                     |                  | (Hi-Z) | (Hi-Z) |

|          |         |          |      | てください。                                       |                  |        |        |

|          |         |          |      | 接続されるデバイスへのVbus供給はできま                        |                  |        |        |

|          |         |          |      | せん。                                          |                  |        |        |

|          |         |          |      | <peripheral controller機能選択時=""></peripheral> |                  |        |        |

|          |         |          |      | USBバスのVbusに直接接続してください。                       |                  |        |        |

|          |         |          |      | Vbusの接続/切断を検出することができます。                      |                  |        |        |

|          |         |          |      | Vbusに接続しない場合は5Vに接続してくださ                      |                  |        |        |

| 甘淮北七     | REFRIN  | リファレンス入  | IN   | い。                                           | 1                |        |        |

| 基準抵抗     | KEFKIN  |          |      | 5.6k ±1%抵抗を介してアナログGND端子に<br>接続してください。        | I                |        |        |

|          | ID0     | カ        |      | 接続してください<br>USB Mini-ABレセプタクルのID端子に接続して      | 1                | λ +-   | 入力     |

| OTG関連    | IDO     | ID入力     | IIN  | USB MIMI-ABレセフタクルのID蛹子に接続して<br>ください。         | 1                | 入力     | 人刀     |

| USB Host | VBOUT0  | 外部電源オン   | OLIT |                                              | 2                | 1      | 1      |

| 時電源管理    |         | アロ电泳カン   | 001  | が記載が回路へのの1701日が日に使用します。 がお電源回路に接続してください。     | 2                | L      | _      |

| 関連       |         |          |      | DP0,DM0をOTGとして使用する場合は、                       |                  |        |        |

| 12,12    |         |          |      | VBOUT1端子は使用できません。                            |                  |        |        |

|          | OVCUROA | PORT0用オー | IN   |                                              | 2                | 入力     | 入力     |

|          | OVCUR0B | バーカレント入  |      | 力に使用します。PORTO用の外部電源回路に接                      |                  | /(/)   | /(/)   |

|          |         | カ        |      | 続してください。                                     |                  |        |        |

|          |         | , ,      |      | 外部電源回路からのオーバーカレント検出入                         |                  |        |        |

|          |         |          |      | 力が1本の場合はOVCUR0Aに接続し、                         |                  |        |        |

|          |         |          |      | OVCUROBをHighまたはLowに固定してくださ                   |                  |        |        |

|          |         |          |      | ι I <sub>0</sub>                             |                  |        |        |

|          | OVCUR1  | PORT1用オー | IN   | 外部電源回路からのオーバーカレント検出入                         | 1                | 入力     | 入力     |

|          |         | バーカレント入  |      | 力に使用します。PORT1用の外部電源回路に接                      |                  |        |        |

|          |         | カ        |      | 続してください。                                     |                  |        |        |

|          |         |          |      | DP0,DM0をOTGとして使用する場合は、                       |                  |        |        |

|          |         |          |      | OVCUR1端子は使用できません                             |                  |        |        |

|          | EXTLP0  |          | OUT  |                                              | 1                | L      | L      |

|          |         | 制御       |      | に低消費電力モードオン/オフ切り替えに使用                        |                  |        |        |

|          |         |          |      | します。PORT0用の外部電源回路に接続してく                      |                  |        |        |

|          |         |          |      | ださい。                                         |                  |        |        |

| 電源/GND   |         | アナログ電源   | -    | 3.3Vに接続してください。                               | 1                |        |        |

|          | AGND    | アナログGND  | -    |                                              | 1                |        |        |

|          | VCC     | 電源       | -    |                                              | 3                |        |        |

|          | GND     | GND      | -    |                                              | 9 (FP)<br>10(BG) |        |        |

|          | VIF     | IO電源     | -    |                                              | 4                |        |        |

|          | VDD     | コア電源     |      |                                              | 2                |        |        |

|          |         |          |      | を出力。コア電源の安定化の為、GNDとの間に                       |                  |        |        |

|          |         |          |      | コンデンサ(4.7uF,0.1uF)を接続してください。                 |                  |        |        |

|          |         |          |      | 尚、外部電源の接続は不要です。                              |                  |        |        |

|          | l .     | 1        |      |                                              |                  |        |        |

- \*1) MPBUS 端子の入力レベルは、H/W リセット直後に確定している必要があります。また、動作中には切り替えを行わないでください。

- \*2) CS\_N="L" かつ RD\_N="L"の時出力、それ以外は入力となります。

- \*3) MPBUS="H"の時には、Hi-Z 入力(オープン)可能です。

- \*4)  $CS_N$ 、 $WR0_N$  および  $WR1_N$  信号は、リセット中およびリセット解除直後は以下(a)もしくは(b)の状態を保ってください。

- (a)  $CS_N="H"$  (b)  $WR0_N="H"$ 、かつ、 $WR1_N="H"$

- \*5) "端子の状態"欄の説明

(a) 入力 : 入力ポート、Hi-Z状態(オープン)不可(b) 入力(Hi-Z) : 入力ポート、Hi-Z状態(オープン)可能

(c) H、L、H/L : 出力ポートの状態を示します

## 表 1.2 R8A66597未使用端子の処理例

| 区分              | 端子名                         | 処理内容                                                               |

|-----------------|-----------------------------|--------------------------------------------------------------------|

| SPLIT バスインタフェース | SD7-0                       | オープン                                                               |

|                 | DREQ0_N, DREQ1_N            | オープン                                                               |

| DMAバスインタフェース    | DACK0_N, DACK1_N            | VIFの"H"レベルに固定*1)                                                   |

|                 | DEND0_N, DEND1_N            | オープン*2)                                                            |

| SOF出力           | SOF_N                       | オープン                                                               |

| VBUS監視入力        | VBUS                        | Host機能選択時:<br>オープン<br>ペリフェラル機能選択時:<br>USBコネクタのVBUS信号に<br>接続してください。 |

|                 | ID0                         | "L"固定                                                              |

| USB Host        | VBOUT0, VBOUT1              | オープン                                                               |

| 時電源管理関連         | OVCUR0A, OVCUR0B,<br>OVCUR1 | "L"固定                                                              |

|                 | EXTLP0                      | オープン                                                               |

<sup>\*1)</sup> DACKn\_N端子を使用しない場合、DMAnCFGレジスタのDFROMビットを"000"に かつDACKAビットを"0"に設定してください(n=0,1)

<sup>\*2)</sup> DENDn\_N端子を使用しない場合、DMAnCFGレジスタのDENDEビットを"0"に設 定してください (n=0,1)

## 1.5 端子機能構成

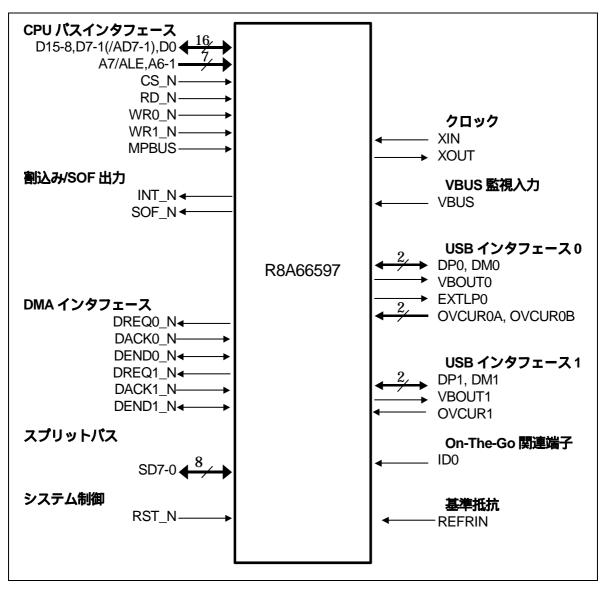

図 1.3に本コントローラーの端子機能構成図を示します。

図 1.3 端子機能構成図

### 1.6 機能概要

#### 1.6.1 コントローラー機能選択

本コントローラーはレジスタ設定によりホスト機能とペリフェラル機能を切り替えることが可能です。 またホスト、ペリフェラルのどちらの機能を選択した場合も、ハードウェアが、USB転送Speedを自動認識します。

#### 1.6.2 パスインタフェース

本コントローラーは、下記に示すバスインタフェースに対応しています。

#### 1.6.2.1 外部パスインタフェース

本コントローラーは、CPUバスインタフェースを使用して、制御用レジスタにアクセスします。

CPUとのバスインタフェースは、下記の2種類のアクセス方法に対応しています。チップセレクト端子(CS\_N)及び3本のストローブ端子(RD\_N、WR0\_N、WR1\_N)でアクセスしてください。

(1) 16bitセパレートバス

7本のアドレスバス(A7-1)、及び16本のデータバス(D15-0)を使用します。

(2) 16bitマルチプレクスバス

ALE端子(ALE)、及び16本のデータバス(D15-0)を使用します。データバスは、アドレスとデータを時分割で使用します。

セパレートバス、及びマルチプレクスバスは、H/Wリセット解除時のMPBUS端子信号レベルで選択します。

#### 1.6.2.2 FIFO パッファメモリアクセス方法

本コントローラーは、USBデータ転送用のFIFOバッファメモリへのアクセス方法として下記の2種類に対応しています。CPU (DMAC) からFIFOポートアクセス (読み出し / 書き込み) を行うことにより、FIFOバッファメモリからの読み出し (への書き込み) を行うことが出来ます。

(1) CPUアクセス

アドレス信号、及びコントロール信号を使用して、データをFIFOバッファメモリに書き込み、もしくはFIFOバッファメモリから読み出してください。

(2) DMAアクセス

CPU内蔵DMAC、もしくは専用DMACから、データを本コントローラーのFIFOバッファメモリに書き込み、もしくはFIFOバッファメモリから読み出してください。

USBデータ通信はリトルエンディアンで行われます。FIFOポートアクセスにはバイトエンディアンスワップ機能があり、16bitアクセスの場合には、レジスタ設定によるエンディアン切り替えができます。

#### 1.6.2.3 DMAC からの FIFO パッファメモリアクセス方法

FIFOバッファメモリへのアクセスをDMAアクセスで行う場合は、さらに下記2種類のアクセス方法を選択できます。

- (1) CPUとの共有バスを使用する方法

- (2) 専用バス(スプリットバス)を使用する方法

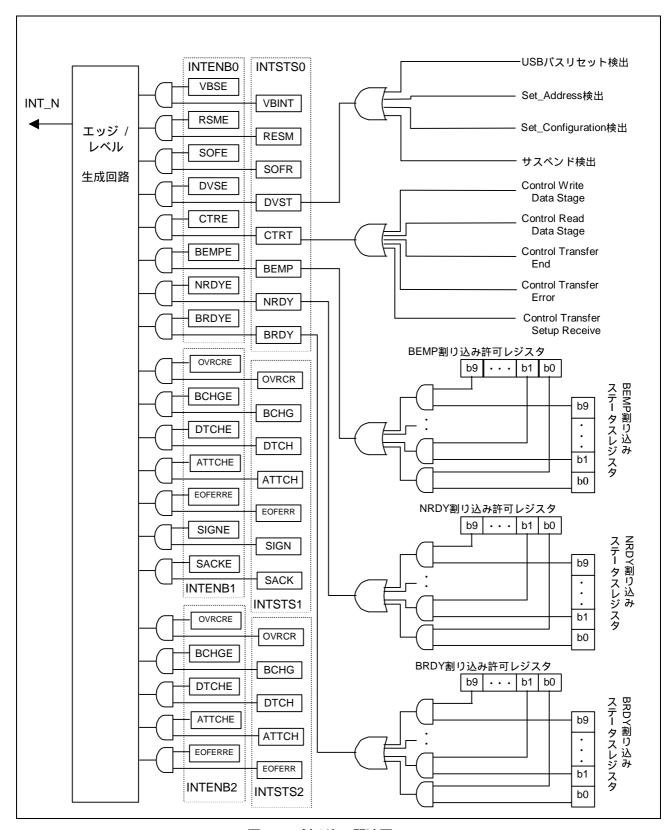

#### 1.6.3 USBイベント

本コントローラーは、USB動作上のイベントを割り込みによりユーザーシステムに通知します。また、DMAインタフェースを選択したパイプのバッファメモリへのアクセスが可能なことを、DREQ信号をアサートすることにより通知します。

ソフトウエアの設定により種類別、要因別に割り込み通知の可否を選択することができます。

### 1.6.4 USBデータ転送

本コントローラーは、USB通信のコントロール転送、バルク転送、インタラプト転送、及びアイソクロナス転送の全種 類のデータ転送が可能です。各転送タイプに対するパイプのリソースは下記のとおりです。

- (1) コントロール転送専用パイプ:1本

- (2) インタラプト転送専用パイプ:4本

- (3) バルク転送専用パイプ:3本

- (4) バルク転送もしくはアイソクロナス転送選択パイプ; 2本

各パイプは、ユーザーシステムに合わせて転送タイプ、エンドポイントアドレス、マックスパケットサイズ等のUSB 転送に必要な設定を行ってください。

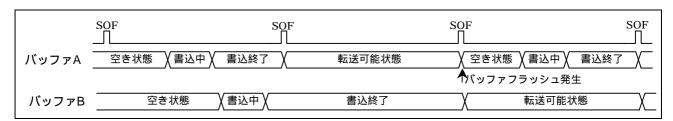

また、本コントローラーは、8.5Kバイトのバッファメモリを内蔵しています。バルク転送専用パイプ、及びバルク転送 もしくはアイソクロナス転送選択パイプに対しては、ユーザーシステムによるバッファメモリの割り当てやバッファ動作 モードなどの設定を行ってください。バッファ動作モード設定は、ダブルバッファ構成やデータパケットの連続転送機能 により、少ない割り込み回数で、高速なデータ転送が可能です。バルク転送及びアイソクロナス転送を行うパイプでの効 率のよいデータ転送のために、トランザクションカウンタ機能によるトランスファー終了機能を備えています。

ユーザーシステムの制御用CPU、及びDMAコントローラーからのバッファメモリへのアクセスは、3本のFIFOポート レジスタを通して行います。

#### 1.6.5 DMAC(ダイレクトメモリアクセスコントローラー)からのアクセス用インタフェース

DMAインタフェースは、DxFIFOポートを使用した、ユーザーシステムと本コントローラーの間のデータ転送であり、 CPUが介在しないデータ転送です。本コントローラーは、2チャンネルのDMAインタフェースを備えており、下記のよ うな機能を有しています。

- (1) 転送終了信号(DEND信号)によるトランスファー終了通知機能

- (2) Zero-Lengthパケット受信時のFIFOバッファ自動クリア機能

本コントローラーは、下記の2種類のDMA転送に対応したインタフェースを備えています。

- (1) サイクルスチール転送

- 1データ転送(1バイト/1ワード)ごとにDREQ端子のアサート、ネゲートが繰り返される転送。

- (2) バースト転送

当該FIFOポートに、割り当てられたパイプのバッファメモリ領域分、もしくはDEND信号による転送終了まで DREQ端子をアサートしたままネゲートしない転送。

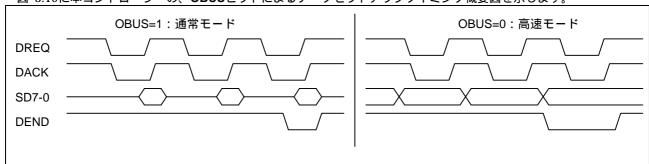

また、DMAインタフェースのハンドシェーク信号(端子)として「CS\_N、RD\_N、WR\_N」、もしくはDACK\_Nを選択 可能です。スプリットバスを使用したDMA転送では、DMAxCFGレジスタのOBUSビット操作でデータセットアップタ イミングを変更することにより、高速なDMA転送が可能です。

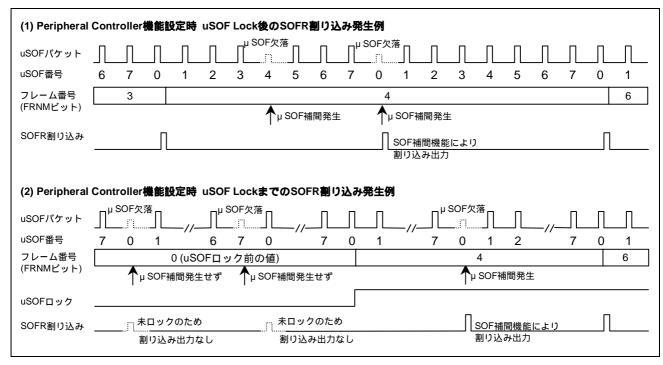

## 1.6.6 SOFパルス出力機能

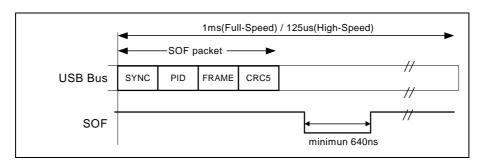

SOFパケットの送受信タイミングを通知するSOFパルス出力機能を備えています。ホストコントローラー機能選択 時には、SOFパケットの送信時にSOF\_N端子にパルスを出力します。ペリフェラルコントローラー機能選択時には SOFパケットの受信時にSOF\_N端子にパルスを出力します。SOFパケット破損時もSOF補間タイマにより、一定間 隔でパルスを出力します。

#### 1.6.7 外付け素子の取り込み

本コントローラーは、下記の外付け素子を内蔵しています。また、VBUS端子は5V耐圧のため、ユーザーシステムは、 VBUS信号を本コントローラーに直接入力することができます。

(1) D+、D-ラインの制御に必要な抵抗

USB通信時に必要となる以下のD+、D-の抵抗を内蔵しています。

- ・D+プルアップ抵抗(Peripheral Controller機能選択時)

- ・D+、D-のプルダウン抵抗(Host Controller機能選択時)

- ・D+、D-の終端抵抗(Hi-Speed動作時)

- ・D+、D-の出力抵抗 (Full/Low -Speed動作時)

- (2) 48MHz、及び480MHzのPLL 3種類の外部クロック(12MHz/24MHz/48MHz)から一つを選択し、動作させることができます。

- (3) 3.3V->1.5Vレギュレータ コア電源用の1.5Vを本コントローラー内部で生成します。インターフェイス電源を3.3Vで使用するシステムでは、 本コントローラーを単一電源で動作させることが可能です。

# 2レジスタ

## <u>レジスタ表の見方</u>

ビット番号 各レジスタは、16ビットの内部バスに接続されています。

奇数番地はb15~b8に、偶数番地はb7~b0になります。

リセット後の状態 リセット動作直後のレジスタ初期状態を示します。

H/WリセットはRST\_N端子から外部リセット信号を入力した場合の初期状態です。 USBリセットは本コントローラーがUSBバスリセットを検出した場合の初期状態です。

なお、リセット動作中に特筆すべき事項は注意事項で記載しています。

"-"は本コントローラーによる操作がなく、ユーザー設定が保持されている状態です。

"?"は値が不定な状態であることを示します。

S/W Access条件 ソフトウェアがレジスタをアクセスする場合の条件です。

H/W Access条件 本コントローラーがリセット動作以外でレジスタをアクセスする場合の条件です。

R · · · · Read Only

W · · · · Write Only

R/W · · · Read / Write

R(0) · · "0"Read Only

W(1) · · "1"Write Only

Remarks 備考、および、詳細説明項目番号です。

H時...Host Controller機能選択時 P時...Peripheral Controller機能選択時

ビットシンボル及びビット名称です。

Function 機能説明です。特に断りのない場合は、読み出し時の値は

ソフトウェアまたはハードウェアが書き込んだ値です。

#### <表記例>

Name

網掛け部分には何も配置されていません。"0"に固定してください。

| Bit Number → | 15,/     | 14   | 13   | 12   | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------|----------|------|------|------|----|----|---|---|---|---|---|---|---|---|---|---|

| Bit Symbol → | <b>V</b> | Abit | Bbit | Cbit |    |    |   |   |   |   |   |   |   |   |   |   |

| H/Wリセット →    | ?        | 0    | 0    | 0    |    |    |   |   |   |   |   |   |   |   |   |   |

| USBリセット →    | ?        | 0    | -    | -    |    |    |   |   |   |   |   |   |   |   |   |   |

| bit | Name            | Function                                 | S/W           | H/W | Remarks             |

|-----|-----------------|------------------------------------------|---------------|-----|---------------------|

| 15  | 何も配置されていません     | ん。"0"に固定してください。                          |               |     |                     |

| 14  | A bit<br>AAA 許可 | 0:動作禁止<br>1:動作許可                         | R/W           | R   | P時<br>書<br>込み<br>禁止 |

| 13  | B bit<br>BBB 動作 | 0:Low 出力<br>1:High 出力                    | R             | W   |                     |

| 12  | C bit<br>CCC 制御 | 0: • • • • • • • • • • • • • • • • • • • | R(0)/<br>W(1) | R   |                     |

|     |                 |                                          |               |     |                     |

<<Remarks>>

## 2.1 レジスタ一覧

表 2.1に本コントローラーのレジスター覧表を示します。

表 2.1 レジスター覧表

| Address  | Symbol    | Name                          | Index |

|----------|-----------|-------------------------------|-------|

| 00       | SYSCFG0   | システムコンフィグレーションコントロールレジスタ      |       |

| 02       | SYSCFG1   | Port1システムコンフィグレーションコントロールレジスタ |       |

| 04       | SYSSTS0   | Port0システムコンフィグレーションステータスレジスタ  |       |

| 06       | SYSSTS1   | Port1システムコンフィグレーションステータスレジスタ  |       |

| 08       | DVSTCTR0  | Port0デバイスコントロールレジスタ           |       |

| 0A       | DVSTCTR 1 | Port1デバイスコントロールレジスタ           |       |

| 0C       | TESTMODE  | テストモードレジスタ                    |       |

| 0E       | PINCFG    | データピンコンフィグレーションレジスタ           |       |

| 10       | DMA0CFG   | DMA0ピンコンフィグレーションレジスタ          |       |

| 12       | DMA1CFG   | DMA1ピンコンフィグレーションレジスタ          |       |

| 14       | CFIFO     | CFIFOポートレジスタ                  |       |

| 16       | 01110     |                               |       |

| 18       | D0FIFO    | D0FIFOポートレジスタ                 |       |

| 1A       |           |                               |       |

| 1C       | D1FIFO    | D1FIFOポートレジスタ                 |       |

| 1E       |           |                               |       |

| 20       | CFIFOSEL  | CFIFOポート選択レジスタ                |       |

| 22       | CFIFOCTR  | CFIFOポートコントロールレジスタ            |       |

| 24       |           |                               |       |

| 26       |           |                               |       |

| 28       | D0FIFOSEL | D0FIFOポート選択レジスタ               |       |

| 2A       | D0FIFOCTR | D0FIFOポートコントロールレジスタ           |       |

| 2C       | D1FIFOSEL | D1FIFOポート選択レジスタ               |       |

| 2E       | D1FIFOCTR | D1FIFOポートコントロールレジスタ           |       |

| 30       | INTENB0   | 割り込み許可レジスタ0                   |       |

| 32       | INTENB1   | 割り込み許可レジスタ1                   |       |

| 34       | INTENB2   | 割り込み許可レジスタ2                   |       |

| 36       | BRDYENB   | BRDY割り込み許可レジスタ                |       |

| 38       | NRDYENB   | NRDY割り込み許可レジスタ                |       |

| 3A       | BEMPENB   | BEMP割り込み許可レジスタ                |       |

| 3C       | SOFCFG    | SOF出力コンフィグレーションレジスタ           |       |

| 3E       |           |                               |       |

| 40       | INTSTS0   | 割り込みステータスレジスタ0                |       |

| 42       | INTSTS1   | 割り込みステータスレジスタ1                |       |

| 44       | INTSTS2   | 割り込みステータスレジスタ2                |       |

| 46       | BRDYSTS   | BRDY割り込みステータスレジスタ             |       |

| 48       | NRDYSTS   | NRDY割り込みステータスレジスタ             |       |

| 4A       | BEMPSTS   | BEMP割り込みステータスレジスタ             |       |

| 4C       | FRMNUM    | フレームナンバレジスタ                   |       |

| 4E       | UFRMNUM   | マイクロフレームナンバレジスタ               |       |

| 50<br>54 | USBADDR   | USBアドレスレジスタ                   |       |

| 54<br>56 | USBREQ    | USBリクエストタイプレジスタ               |       |

| 58       | USBVAL    | USBリクエストバリューレジスタ              |       |

|          | USBINDX   | USBリクエストインデックスレジスタ            |       |

| 5A       | USBLENG   | USBリクエストレングスレジスタ              |       |

| 5C       | DCPCFG    | DCPコンフィグレーションレジスタ             |       |

| 5E       | DCPMAXP   | DCPマックスパケットサイズレジスタ            |       |

| 60       | DCPCTR    | DCPコントロールレジスタ                 |       |

| 62<br>64 | DIDECE    | パイプウィンドウ選切しぶった                |       |

| 04       | PIPESEL   | パイプウィンドウ選択レジスタ                |       |

| Address    | Symbol               | Name                                                | Index |

|------------|----------------------|-----------------------------------------------------|-------|

| 66         | <b>C</b> yllinger    | 1,0,1,0                                             | maex  |

| 68         | PIPECFG              | パイプコンフィグレーションレジスタ                                   |       |

| 6A         | PIPEBUF              | パイプバッファ指定レジスタ                                       |       |

| 6C         | PIPEMAXP             | パイプマックスパケットサイズレジスタ                                  |       |

| 6E         | PIPEPERI             | パイプ周期制御レジスタ                                         |       |

| 70         | PIPE1CTR             | PIPE1コントロールレジスタ                                     |       |

| 72         | PIPE2CTR             | PIPE2コントロールレジスタ                                     |       |

| 74         | PIPE3CTR             | PIPE3コントロールレジスタ                                     |       |

| 76         | PIPE4CTR             | PIPE4コントロールレジスタ                                     |       |

| 78         | PIPE5CTR             | PIPE5コントロールレジスタ                                     |       |

| 7A         | PIPE6CTR             | PIPE6コントロールレジスタ                                     |       |

| 7C         | PIPE7CTR             | PIPE7コントロールレジスタ                                     |       |

| 7E         | PIPE8CTR             | PIPE8コントロールレジスタ                                     |       |

| 80         | PIPE9CTR             | PIPE9コントロールレジスタ                                     |       |

| 82-8E      |                      |                                                     |       |

| 90         | PIPE1TRE             | PIPE1トランザクションカウンタイネーブルレジスタ                          |       |

| 92         | PIPE1TRN             | PIPE1トランザクションカウンタレジスタ                               |       |

| 94         | PIPE2TRE             | PIPE2トランザクションカウンタイネーブルレジスタ                          |       |

| 96         | PIPE2TRN             | PIPE2トランザクションカウンタレジスタ                               |       |

| 98         | PIPE3TRE             | PIPE3トランザクションカウンタイネーブルレジスタ                          |       |

| 9A<br>9C   | PIPE3TRN<br>PIPE4TRE | PIPE3トランザクションカウンタレジスタ                               |       |

| 9C<br>9E   | PIPE4TRE<br>PIPE4TRN | PIPE4トランザクションカウンタイネーブルレジスタ                          |       |

| A0         | PIPE5TRE             | PIPE4トランザクションカウンタレジスタ                               |       |

| AU<br>A2   | PIPESTRE<br>PIPESTRN | PIPE5トランザクションカウンタイネーブルレジスタ<br>PIPE5トランザクションカウンタレジスタ |       |

| A4-CE      | PIPESTRIN            | PIPE5トラフザクションカワフタレシスタ                               |       |

| D0         | DEVADD0              | デバイスアドレス0コンフィグレーションレジスタ                             |       |

| D2         | DEVADD1              | デバイスアドレス1コンフィグレーションレジスタ                             |       |

| D4         | DEVADD2              | デバイスアドレス2コンフィグレーションレジスタ                             |       |

| D6         | DEVADD3              | デバイスアドレス3コンフィグレーションレジスタ                             |       |

| D8         | DEVADD4              | デバイスアドレス4コンフィグレーションレジスタ                             |       |

| DA         | DEVADD5              | デバイスアドレス5コンフィグレーションレジスタ                             |       |

| DC         | DEVADD6              | デバイスアドレス6コンフィグレーションレジスタ                             |       |

| DE         | DEVADD7              | デバイスアドレス7コンフィグレーションレジスタ                             |       |

| E0         | DEVADD8              | デバイスアドレス8コンフィグレーションレジスタ                             |       |

| E2         | DEVADD9              | デバイスアドレス9コンフィグレーションレジスタ                             |       |

| E4         | DEVADDA              | デバイスアドレスAコンフィグレーションレジスタ                             |       |

| <b>E</b> 6 |                      |                                                     |       |

網掛けの番地には何も配置されていません。アクセスを行わないでください。

# 2.2 ビットシンボル一覧

表 2.2に本コントローラーのビットシンボル一覧表を示します。

表 2.2 ビットシンボル一覧表

|      |                        |        |        |           | 쵊        | 番地               |          |         |          |                |            |                | 偶数       | 番地         |           |          |          |

|------|------------------------|--------|--------|-----------|----------|------------------|----------|---------|----------|----------------|------------|----------------|----------|------------|-----------|----------|----------|

| addr | レジスタ名                  | 15     | 14     | 13        | 12       | 11               | 10       | 9       | 8        | 7              | 6          | 5              | 4        | 3          | 2         | 1        | 0        |

| 00   | SYSCFG0                | XT     |        | XCKE      | 12       | PLLC             | SCKE     | - U     | - U      | HSE            | DCFM       | DRPD           | DPRPU    |            |           |          | USBE     |

|      | SYSCFG1                | Α.     | 7 (    | TORE      | CNTFLG   | 1 220            | COILE    | PCSDIS  | LPSMF    | HSE            | BOI III    | DRPD           | Di iti o |            |           |          | OUDE     |

| -    | SYSSTS0                | OVC    | MON    |           | 51111 20 |                  |          | . 662.6 | 2. 02    |                |            | SOFEA          |          |            | IDMON     | LN       | ST       |

|      | SYSSTS1                | OVC    |        |           |          |                  |          |         |          |                |            | SOFEA          |          |            | 12.11.011 | LN       |          |

|      | DVSTCTR0               |        |        |           |          | HNPBTOA          | FXTI P0  | VBOUT   | WKUP     | RWUPE          | USBRST     | RESUME         | UACT     |            |           | RHST     | •        |

|      | DVSTCTR1               |        |        |           |          | THE BYOK         | 271121 0 | VBOUT   |          | RWUPE          |            | RESUME         |          |            |           | RHST     |          |

|      | TESTMODE               |        |        |           |          |                  |          | 12001   |          | TOTAL E        | COBITOT    | TECOME         | 07101    |            | UT        |          |          |

|      | PINCFG                 | LDRV   |        |           |          |                  |          |         |          |                |            |                |          |            |           |          | INTA     |

|      | DMA0CFG                | LDITT  | DREQA  | BURST     |          |                  | DACKA    |         | DFORM    |                | DENDA      | PKTM           | DENDE    |            | OBUS      |          | 114174   |

|      | DMA1CFG                |        |        | BURST     |          |                  | DACKA    |         | DFORM    |                | DENDA      | PKTM           | DENDE    |            | OBUS      |          |          |

|      | CFIFO                  |        | DILLAK | DOIGO     |          |                  | DAONA    |         | CFP      | OPT            | DENDA      | I IXTIVI       | DENDE    |            | OBOO      |          |          |

| 16   | 0. 1. 0                |        |        |           |          |                  |          |         | 011      | OKI            |            |                |          |            |           |          |          |

|      | D0FIFO                 |        |        |           |          |                  |          |         | D0FF     | OPT            |            |                |          |            |           |          |          |

| 1A   | B01 11 0               |        |        |           |          |                  |          |         | DOLL     | OICI           |            |                |          |            |           |          |          |

|      | D1FIFO                 |        |        |           |          |                  |          |         | D1FIF    | PORT           |            |                |          |            |           |          |          |

| 1E   | 2 11 11 O              |        |        |           |          |                  |          |         | וווע     | JICI           |            |                |          |            |           |          |          |

|      | CFIFOSEL               | RCNT   | REW    |           |          |                  | MBW      |         | BIGEND   |                |            | ISEL           |          |            | CURI      | PIPF     |          |

|      | CFIFOCTR               | BVAL   | BCLR   | FRDY      |          |                  | INIDAA   |         | PIGEIND  |                | DT         | LN             |          | l          | CURI      | 1 II L   |          |

| 24   | CI II OCTK             | DVAL   | BOLK   | FRUI      |          |                  |          |         |          |                | ا <i>ا</i> | LIN            |          |            |           |          |          |

| 26   |                        |        |        |           |          |                  |          |         |          |                |            |                |          |            |           |          |          |

|      | D0FIFOSEL              | RCNT   | REW    | DCLRM     | DREQE    |                  | MBW      |         | BIGEND   |                |            |                |          |            | CURI      | DIDE     |          |

|      | D0FIFOCTR              | BVAL   | BCLR   | FRDY      | DREQE    |                  | IVIDVV   |         | DIGEND   |                | DT         | LN             |          |            | CURI      | FIFE     |          |

|      | D1FIFOSEL              | RCNT   | REW    |           | DREQE    |                  | MBW      |         | BIGEND   |                | l l        | LIN            |          |            | CUR       | DIDE     |          |

|      | D1FIFOSEL<br>D1FIFOCTR | BVAL   | BCLR   | FRDY      | DREQE    |                  | IVIDVV   |         | DIGEND   |                | DT         | I NI           |          |            | CURI      | PIPE     |          |

| _    | INTENB0                | VBSE   | RSME   | SOFE      | DVSE     | CTRE             | BEMPE    | NRDYE   | DDDVE    |                | וט         | LIN            |          |            |           |          |          |

|      | INTENB1                |        | BCHGE  | SUFE      |          |                  | DEIVIPE  | NKUTE   | DKUTE    |                | EOFERRE    | CICNE          | SACKE    |            |           |          |          |

|      | INTENB2                |        |        |           |          | ATTCHE           |          |         |          |                |            |                | SAUKE    |            |           |          |          |

|      | BRDYENB                | OVRCRE | BCHGE  |           | DICHE    | ATTCHE           |          |         |          |                | EOFERRE    |                |          |            |           |          |          |

|      | NRDYENB                |        |        |           |          |                  |          |         |          |                |            | PIPER          |          |            |           |          |          |

|      | BEMPENB                |        |        |           |          |                  |          |         |          |                |            | PIPEN<br>PIPEB |          |            |           |          |          |

|      | SOFCFG                 |        |        |           |          |                  |          |         |          |                | BRDYM      |                | EDGESTS  | 00         | FM        |          |          |

| 3E   | SOFCFG                 |        |        |           |          |                  |          |         | TRNENSEL |                | DKDIM      | INIL           | EDGESTS  | 30         | F IVI     |          |          |

|      | INTSTS0                | VBINT  | RESM   | SOFR      | DVST     | CTRT             | BEMP     | NRDY    | BRDY     | VBSTS          |            | DVSQ           |          | VALID      |           | CTSQ     |          |

|      | INTSTS0                | OVRCR  | BCHG   | SUFK      | DTCH     | ATTCH            | DEIVIF   | INKUT   | DKUT     | VDS13          | EOFERR     |                | SACK     | VALID      |           | CISQ     |          |

|      | INTSTS1                | OVRCR  | BCHG   |           | DTCH     | ATTCH            |          |         |          |                | EOFERR     | SIGN           | SACK     |            |           |          |          |

|      | BRDYSTS                | OVNCK  | BCHG   |           | DIGII    | ATTOIT           |          |         |          |                | LOFERN     | PIPEI          | DDDV     |            |           |          |          |

|      | NRDYSTS                |        |        |           |          |                  |          |         |          |                |            | PIPEI          |          |            |           |          |          |

|      | BEMPSTS                |        |        |           |          |                  |          |         |          |                |            | PIPE           |          |            |           |          |          |

|      | FRMNUM                 | OVRN   | CRCE   |           |          |                  |          | 1       |          |                |            | FRNM           |          |            |           |          |          |

|      | UFRMNUM                | OVKIN  | UNUE   |           |          |                  |          |         |          |                |            | EIZINIVI       |          |            |           | UFRNM    |          |

|      | USBADDR                |        |        |           |          |                  |          |         |          |                |            |                |          | JSBADDF    | <u> </u>  | OFKINIVI |          |

| 52   | COPUDDI                |        |        |           |          |                  |          |         |          |                |            |                |          |            | \         |          |          |

|      | USBREQ                 |        |        |           | hDa.     | quest            |          |         |          |                |            |                | bmRequ   | ioetTyroo  |           |          |          |

|      | USBVAL                 |        |        |           | DRec     | <sub>fueor</sub> |          |         | wVa      | aluo           |            |                | bilikequ | iest i ype |           |          |          |

|      | USBINDX                |        |        |           |          |                  |          |         |          |                |            |                |          |            |           |          |          |

|      | USBLENG                |        |        |           |          |                  |          |         | wln      |                |            |                |          |            |           |          |          |

|      | DCPCFG                 |        |        |           |          |                  |          |         | WLe      | ngth<br>SHTNAK |            |                | DIR      |            |           |          |          |

|      | DCPCFG                 |        | רי     | (CE)      |          |                  |          |         | CINTIND  | SHINAK         |            |                | אוע      | MVDC       |           |          |          |

|      |                        | DOTO   |        | SEL COOLD | CCCTC    |                  |          |         | 2001     | COCET          | COMON      | DDLIOV         | DINIOE   | MXPS       | CCDI      | , r      | <u> </u> |

|      | DCPCTR                 | BSTS   | SUKEQ  | CSCLR     | CSSIS    | SUREQCLR         |          |         | SQULK    | SUSET          | SQMON      | LR021          | PINGE    |            | CCPL      | PI       | υ        |

| 62   | DIDECEI                |        |        |           |          |                  |          |         |          |                |            |                |          |            | 5:5-      | CEL      |          |

|      | PIPESEL                |        |        |           |          |                  |          |         |          |                |            |                |          |            | PIPE      | SEL      |          |

| 66   | DIDECEO                |        | DE.    |           |          |                  | DEST     | DD: 5   | ONITY    | OLUTAL S       |            |                | D:0      |            |           |          |          |

|      | PIPECFG                | TY     | PΕ     |           |          |                  | BFRE     | DBLB    | CNTMD    | SHTNAK         |            |                | DIR      |            | EPN       | IUM      |          |

| ьΑ   | PIPEBUF                |        |        |           | BUFSIZE  |                  |          | CNIC    |          |                | <u> </u>   |                |          | BUFNMB     |           |          |          |

RENESAS

| addr       |                      |      |        |            | 一一一一一一一一一一一一一一一一一一一一一一一一一一一一一一一一一一一一一一一 | 番地 |        |         |              |            |       |       | 偶数 | 番地 |   |      |        |

|------------|----------------------|------|--------|------------|-----------------------------------------|----|--------|---------|--------------|------------|-------|-------|----|----|---|------|--------|

| addr       | レジスタ名                | 15   | 14     | 13         | 12                                      | 11 | 10     | 9       | 8            | 7          | 6     | 5     | 4  | 3  | 2 | 1    | 0      |

| 6C         | PIPEMAXP             |      | DEV    | 'SEL       |                                         |    |        |         |              |            |       | MXPS  |    | •  | • |      |        |

| 6E         | PIPEPERI             |      |        |            | IFIS                                    |    |        |         |              |            |       |       |    |    |   | IITV |        |

| 70         | PIPE1CTR             | BSTS | INBUFM | CSCLR      | CSSTS                                   |    | ATREPM | ACLRM   | SQCLR        | SQSET      | SQMON | PBUSY |    |    |   |      | PID    |

| 72         | PIPE2CTR             | BSTS | INBUFM | CSCLR      | CSSTS                                   |    | ATREPM | ACLRM   | SQCLR        | SQSET      | SQMON | PBUSY |    |    |   |      | PID    |

| 74         | PIPE3CTR             | BSTS | INBUFM | CSCLR      | CSSTS                                   |    | ATREPM | ACLRM   | SQCLR        | SQSET      | SQMON | PBUSY |    |    |   |      | PID    |

| 76         | PIPE4CTR             | BSTS | INBUFM | CSCLR      | CSSTS                                   |    | ATREPM | ACLRM   | SQCLR        | SQSET      | SQMON | PBUSY |    |    |   |      | PID    |

| 78         | PIPE5CTR             | BSTS | INBUFM | CSCLR      | CSSTS                                   |    | ATREPM | ACLRM   | SQCLR        | SQSET      | SQMON | PBUSY |    |    |   |      | PID    |

| 7A         | PIPE6CTR             | BSTS |        | CSCLR      | CSSTS                                   |    |        | ACLRM   | SQCLR        | SQSET      | SQMON | PBUSY |    |    |   |      | PID    |

| 7C         | PIPE7CTR             | BSTS |        | CSCLR      | CSSTS                                   |    |        | ACLRM   | SQCLR        | SQSET      | SQMON | PBUSY |    |    |   |      | PID    |

| 7E         | PIPE8CTR             | BSTS |        | CSCLR      | CSSTS                                   |    |        | ACLRM   | SQCLR        | SQSET      | SQMON | PBUSY |    |    |   |      | PID    |

| 80         | PIPE9CTR             | BSTS |        | CSCLR      | CSSTS                                   |    |        | ACLRM   | SQCLR        | SQSET      | SQMON | PBUSY |    |    |   |      | PID    |

| 82-        |                      |      |        |            |                                         |    |        |         |              |            |       |       |    |    |   |      |        |

| 8E         | DIDE (TDE            |      |        |            |                                         |    |        |         |              |            |       |       |    |    |   |      |        |

|            | PIPE1TRE             |      |        |            |                                         |    |        | TRENB   | TRCLR        |            |       |       |    |    |   |      |        |

|            | PIPE1TRN             |      |        |            |                                         |    |        | I       | TRN          | CNT        |       |       |    |    |   |      |        |

| <u> </u>   | PIPE2TRE             |      |        |            |                                         |    |        | TRENB   | TRCLR        |            |       |       |    |    |   |      |        |

| ••         | PIPE2TRN             |      |        |            |                                         |    |        | I       | TRN          | CNT        |       |       |    |    |   |      |        |

| ••         | PIPE3TRE             |      |        |            |                                         |    |        | TRENB   | TRCLR        |            |       |       |    |    |   |      |        |

| 07.        | PIPE3TRN             |      |        |            |                                         |    |        |         | TRN          | CNI        |       |       |    |    |   |      |        |

|            | PIPE4TRE<br>PIPE4TRN |      |        |            |                                         |    |        | TRENB   | TRCLR        | ONT        |       |       |    |    |   |      |        |

|            | PIPE4TRN<br>PIPE5TRE |      |        |            |                                         |    |        | TDEND   | TRN          | CNI        |       |       |    |    |   |      |        |

|            | PIPESTRE<br>PIPESTRN |      |        |            |                                         |    |        | TRENB   | TRCLR<br>TRN | CNT        |       |       |    |    |   |      |        |

| A4-        | PIPESTRIN            |      |        |            |                                         |    |        |         | IKIN         | CIVI       |       |       |    |    |   |      |        |

| CE         |                      |      |        |            |                                         |    |        |         |              |            |       |       |    |    |   |      |        |

| D0         | DEVADD0              |      |        | HPP        | HUB                                     |    | ı      | HUBPOR  |              | USB        | SPD   |       |    |    |   |      | RTPORT |

|            | DEVADD1              |      |        | HPP        |                                         |    |        | HUBPOR  |              | USB        |       |       |    |    |   |      | RTPORT |

|            | DEVADD2              |      |        | HPP        | -                                       |    |        | HUBPOR  |              | USB        | -     |       |    |    |   |      | RTPORT |

|            | DEVADD3              |      |        | HPP        | -                                       |    |        | HUBPOR  |              | USB        | -     |       |    |    |   |      | RTPORT |

|            | DEVADD4<br>DEVADD5   |      | -      | HPP<br>HPP | -                                       |    |        | HUBPORT |              | USB<br>USB | -     |       |    |    |   |      | RTPORT |

|            | DEVADDS<br>DEVADD6   |      |        | HPP        | _                                       |    |        | HUBPOR  |              | USB        | _     |       |    |    |   |      | RTPORT |

|            | DEVADDO<br>DEVADD7   |      |        | HPP        | _                                       |    |        | HUBPOR  |              | USB        |       |       |    |    |   |      | RTPORT |

|            | DEVADD7              |      |        | HPP        |                                         |    |        | HUBPOR  |              | USB        | _     |       |    |    |   |      | RTPORT |

|            | DEVADD9              |      |        | HPP        |                                         |    |        | HUBPOR  |              | USB        |       |       |    |    |   |      | RTPORT |

| E4         | DEVADDA              |      |        | HPP        | HUB                                     |    |        | HUBPOR  | Γ            | USB        | SPD   |       |    |    |   |      | RTPORT |

| <b>E</b> 6 |                      |      |        |            |                                         |    |        |         |              |            |       |       |    |    |   |      |        |

XTAL 0

## 2.3 システムコンフィグレーションコントロール

XCKE

0

◆ システムコンフィグレーションコントロールレジスタ【SYSCFG0】 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6

PLLC SCKE

0

0

|   | <アドレ | ノス:00 | H>   |

|---|------|-------|------|

| 3 | 2    | 1     | 0    |

|   |      |       | USBE |

| ? | ?    | ?     | Ω    |

5

DCFM DRPD DPRPU

0

0

| Bit   | Name                       | Function                                                                                                                                                          | S/W | H/W | Remarks                  |

|-------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|

| 15-14 | XTAL<br>XIN クロック選択         | XIN 端子から入力するクロックの周波数を指定します。<br>00: 12MHz 入力<br>01: 24MHz 入力<br>10: 48MHz 入力<br>11: Reserved                                                                       | R/W | R   |                          |

| 13    | XCKE<br>発振バッファ許可           | 発振バッファ動作の禁止/許可を指定します。<br>0: 発振バッファ動作禁止<br>1: 発振バッファ動作許可                                                                                                           | R/W | R   |                          |

| 12    | 何も配置されていません。"0"に固定して       | てください。                                                                                                                                                            |     |     |                          |

| 11    | PLLC<br>48MHzPLL 動作許可      | 48MHzPLL 動作の禁止/許可を指定します。<br>0: PLL 動作禁止<br>1: PLL 動作許可                                                                                                            | R/W | R/W |                          |

| 10    | SCKE<br>USB プロッククロック許可     | USB ブロックへの 48MHz クロック供給の停止/許可を指定します。<br>0: USB ブロックへのクロック供給停止<br>1: USB ブロックへのクロック供給許可                                                                            | R/W | R/W |                          |

| 9-8   | 何も配置されていません。"0"に固定して       |                                                                                                                                                                   |     |     | •                        |

| 7     | HSE<br>PORT0 Hi-Speed 動作許可 | PORT0 の Hi-Speed 動作禁止/許可を指定します。<br>0: Hi-Speed 動作禁止<br>(Peripheral 機能選択時:Full-Speed、<br>Host 機能選択時: Full-/Low-Speed)<br>1: Hi-Speed 動作許可(コントローラーが通信<br>Speed を検出) | R/W | R   |                          |

| 6     | DCFM<br>コントローラー機能選択        | 本コントローラーの機能を指定します。<br>0: Peripheral Controller 機能選択<br>1: Host Controller 機能選択                                                                                    | R/W | R   |                          |

| 5     | DRPD<br>PORT0 D+/D-ライン抵抗制御 | PORT0 の Host Controller 機能用、D+/D-ライン Pull Down の禁止/許可を指定します。<br>0: Pull Down 禁止<br>1: Pull Down 許可                                                                | R/W | R   | H<br>(P 時<br>"0"を設<br>定) |

|       | DPRPU<br>PORT0 D+ライン抵抗制御   | PORT0のPeripheral Controller 機能用 D+ライン PullUp の禁止/許可を指定します。<br>0: Pull Up 禁止<br>1: Pull Up 許可                                                                      | R/W | R   | P<br>(H 時<br>"0"を設<br>定) |

| 3-1   | 何も配置されていません。"0"に固定して       | てください。                                                                                                                                                            |     |     |                          |

| 0     | USBE<br>USB ブロック動作許可       | USB ブロックの動作禁止/許可を指定します。<br>0: USB ブロック動作禁止<br>1: USB ブロック動作許可                                                                                                     | R/W | R   |                          |

HSE

0

0

<<Remarks>>

なし

## 2.3.1 XINクロック選択ビット(XTAL)

本ビットに、XIN端子に接続する水晶振動子、または発振器に応じた値を設定してください。本コントローラーは本ビットの設定値によって、48MHzPLLの逓倍数を判断します。

本ビットの設定はハードウェアリセットリセット直後に行い、本コントローラの動作中は変更しないでください。

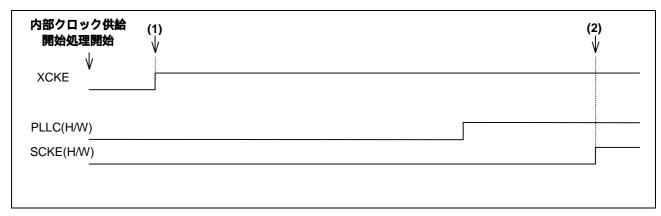

#### 2.3.2 **発振パッファ許可ビット**(XCKE)

本ビットを"1"に設定することにより、本コントローラーの発振バッファ動作を許可します。発振バッファ動作を禁止する時には"0"を書き込んでください。

本コントローラーがクロック復帰処理を行っている期間("CNTFLG=1"が表示されている期間)は、"XCKE=0"を書き込まないでください。また、クロック復帰処理終了時には、必ず"XCKE=1"を書き込んでください。

## 2.3.3 48MHzPLL動作許可ビット(PLLC)

本ビットを"1"に設定することにより、本コントローラーの48MHzPLLの動作を許可します。48MHzPLLの動作を禁止する時には"0"を書き込んでください。

#### 2.3.4 USBプロッククロック許可ピット(SCKE)

本ビットを"1"に設定することにより、本コントローラーのUSBブロックへのクロック供給を許可します。USBブロックへのクロック供給を禁止する時には"0"を書き込んでください。

表 2.3に本ビットが"0"の時に書き込み可能なレジスタを示します。その他のレジスタへの書き込みは行えません。 本ビットが"0"の時の各レジスタの読み出しは可能です。

表 2.3 "SCKE=0"の時に、ソフトウェアによる書き込みが可能なレジスタ一覧

| アドレス | レジスタ名   |

|------|---------|

| 00H  | SYSCFG0 |

| 02H  | SYSCFG1 |

| 0EH  | PINCFG  |

### 2.3.5 Hi-Speed動作許可ビット(HSE)

本ビットを"1"に設定することにより、PORT0に対してHi-Speed動作を許可します。"HSE=1"を設定した場合、本コントローラーはReset Handshakeの結果に従いPORT0をHi-SpeedまたはFull-Speed動作させます。

#### 2.3.5.1 Host Controller 機能選択時

"HSE=0"を設定した場合、当該PORTはLow-Speed動作、または、Full-Speed動作を行います。

当該PORTにLow-SpeedのPeripheralデバイスがアタッチされたことを検出した場合には、必ず"HSE=0"を設定してください。

"HSE=1"を設定した場合、本コントローラーはReset Handshake Protocolの結果に従い、自動的に当該PORTをHi-SpeedまたはFull-Speed動作させます。

本ビットの変更は、"アタッチ検出 (ATTCH割り込み検出)後からUSBバスリセット実行前("USBRST=1"設定前)"の期間に行ってください。

#### 2.3.5.2 Peripheral Controller 機能選択時

"HSE=0"を設定した場合、本コントローラーはFull-Speed動作を行います。

"HSE=1"を設定した場合、本コントローラーはReset Handshake Protocolの結果に従い自動的にHi-SpeedまたはFull-Speed動作を行います。

本ビットの書き換えは、"DPRPU=0"の時に行ってください。

### 2.3.6 コントローラー機能選択ビット(DCFM)

本ビットを設定することにより、本コントローラーをHost Controller機能またはPeripheral Controller機能に指定します。

本ビットの書き換えは、"DPRPU=0かつDRPD=0"の時に行ってください。

## 2.3.7 PORT0用D+,D-ライン抵抗制御 (DRPD、DPRPU)

表 2.4にPORTOのUSBデータバスの抵抗についての設定を示します。DRPDビット及びDPRPUビットでUSBデータバスの抵抗選択を行ってください。

| 設定   | 設定 内容                      |           |           | USB データバス抵抗制御                          |  |  |

|------|----------------------------|-----------|-----------|----------------------------------------|--|--|

| DRPD | DRPD DPRPU D- Line D+ Line |           | D+ Line   | Remarks                                |  |  |

| 0    | 0                          | Open      | Open      |                                        |  |  |

| 0    | 1                          | Open      | Pull-Up   | Peripheral Controller として動作させる場合はこの設定に |  |  |

|      |                            |           |           | してください                                 |  |  |

| 1    | 0                          | Pull-Down | Pull-Down | Host Controller として動作させる場合はこの状態に設定し    |  |  |

|      |                            |           |           | てください                                  |  |  |

| 1    | 1                          | Pull-Down | Pull-Up   | 設定埜止                                   |  |  |

表 2.4 PORTO USBデータバス抵抗の制御

## 2.3.7.1 Host Controller 機能用 PORT0 PullDown 抵抗制御 (DRPD)

Host Controller機能選択時に本ビットを"1"に設定すると、本コントローラーはPORT0のD+、D-ラインをPull Downします。

本ビットへの"1"設定は、Host Controller機能選択時に行ってください。

#### 2.3.7.2 Peripheral Controller 機能用 PORT0 D+Pull Up 抵抗制御 (DPRPU)

Peripheral Controller機能選択時に本ビットを"1"に設定すると、本コントローラーはPORT0のD+ラインを3.3VにPull Upし、USBホストに対してアタッチを通知することができます。

また、本ビットを"1"から"0"に変更することにより、本コントローラーはD+ラインのPull Upを解消しますので、 USBホストに対してデタッチしたと見せることができます。

本ビットへの"1"設定は、Peripheral Controller機能選択時に行ってください。

#### USBプロック動作許可ピット(USBE) 2.3.8

本ビットを設定することにより、本コントローラーのUSBブロックの動作許可、禁止を行います。 "USBE=1"から"USBE=0"に変更した場合には、本コントローラーは表 2.5、表 2.6に示すビットを初期化します。

表 2.5 "USBE=0"書き込みにより初期化されるレジスター覧 (Peripheral Controller機能選択 ("DCFM=0"設定) 時)

| レジスタ名                | ビット名                      | Remark                   |

|----------------------|---------------------------|--------------------------|

| SYSSTS0<br>SYSSTS1   | LNST                      | Host Controller機能選択時は値保持 |

| DVSTCTR0<br>DVSTCTR0 | RHST                      |                          |

| INTSTS0              | DVSQ                      | Host Controller機能選択時は値保持 |

| USBADDR              | USBADDR                   | Host Controller機能選択時は値保持 |

| USBREQ               | bRequest<br>bmRequestType | Host Controller機能選択時は値保持 |

| USBVAL               | wValue                    | Host Controller機能選択時は値保持 |

| USBINDX              | wIndex                    | Host Controller機能選択時は値保持 |

| USBLENG              | wLength                   | Host Controller機能選択時は値保持 |

## 表 2.6 "USBE=0"書き込みにより初期化されるレジスター覧 (Host Controller機能選択 ("DCFM=1"設定) 時)

| レジスタ名                | ビット名  | Remark                         |

|----------------------|-------|--------------------------------|

| DVSTCTR0<br>DVSTCTR0 | RHST  |                                |

| FRMNUM               | FRNM  | Peripheral Controller機能選択時は値保持 |

| UFRMNUM              | UFRNM | Peripheral Controller機能選択時は値保持 |

本ビットの変更は、"SCKE=1"の時に行ってください。

Host Controller機能選択時は、"DPRD=1"設定後、LNSTビットのチャタリング除去を行い、USBバスの状態が安 定したことを確認した後で、"USBE=1"の設定を行ってください。

14 13

15

◆ PORT1システムコンフィグレーションコントロールレジスタ【SYSCFG1】

9

0

8

0

0

PCSDIS LPSME HSE

12 11 10

CNTFLG 0

| <アドレス:02H> |   |   |   |  |  |  |

|------------|---|---|---|--|--|--|

| 3          | 2 | 1 | 0 |  |  |  |

|            |   |   |   |  |  |  |

| 2          | 2 | 2 | 2 |  |  |  |

4

DRPD

0

| Bit   | Name                      | Function                            | S/W   | H/W      | Remarks |  |  |

|-------|---------------------------|-------------------------------------|-------|----------|---------|--|--|

|       |                           |                                     | 0, 11 | 1 1/ V V |         |  |  |

|       | 何も配置されていません。"0"に固定してください。 |                                     |       |          |         |  |  |

| . –   | CNTFLG                    | 現在オートクロックセットアップ処理中かど                | R     | W        |         |  |  |

|       | オートクロックモニター               | うかが表示されます。                          |       |          |         |  |  |

|       |                           | 0: オートクロック処理終了またはクロック停              |       |          |         |  |  |

|       |                           | 止中                                  |       |          |         |  |  |

|       |                           | 1: オートクロック処理中                       |       |          |         |  |  |

| 11-10 | 何も配置されていません。"0"に固定して      | :ください。                              |       |          |         |  |  |

|       | PCSDIS                    | CS_N の立下りによる Low パワースリープ            | R/W   | R        |         |  |  |

|       |                           | モードからの復帰の禁止/許可を指定します。               |       |          |         |  |  |

|       | による復帰禁止                   | 0: CS_N による復帰許可                     |       |          |         |  |  |

|       |                           | 1: CS_N による復帰禁止                     |       |          |         |  |  |

| 8     | LPSME                     | クロック停止中に本コントローラーが Low パ             | R/W   | R        |         |  |  |

|       | Low パワースリープモード許可          | ワースリープモードへ遷移するかどうかの禁                |       |          |         |  |  |

|       |                           | 止/許可を指定します。                         |       |          |         |  |  |

|       |                           | 0: Low パワースリープモード禁止                 |       |          |         |  |  |

|       |                           | 1: Low パワースリープモード許可                 |       |          |         |  |  |

| 7     | HSE                       | Host Controller 機能選択時、PORT1 の       | R/W   | R        | Н       |  |  |

|       | PORT1 Hi-Speed 動作許可       | Hi-Speed 動作許可を行います。                 |       |          | (P 時    |  |  |

|       |                           | 0: Hi-Speed 動作禁止 Full-/Low-Speed)   |       |          | "0"を設   |  |  |

|       |                           | 1: Hi-Speed 動作許可(コントローラーが通信         |       |          | 定)      |  |  |

|       |                           | Speed を検出)                          |       |          |         |  |  |

| 6     | 何も配置されていません。"0"に固定して      | ください。                               |       |          | •       |  |  |

| 5     | DRPD                      | PORT1 の(Host Controller 機能用)D+/D-ライ | R/W   | R        | Н       |  |  |

|       | PORT1 D+/D-ライン抵抗制御        | ン Pull Down の禁止/許可を指定します。           |       |          | (P 時    |  |  |

|       |                           | 0: Pull Down 禁止                     |       |          | "0"を設   |  |  |

|       |                           | 1: Pull Down 許可                     |       |          | 定)      |  |  |

| 4-0   | 何も配置されていません。"0"に固定して      | ください。                               |       |          | '       |  |  |

#### <<Remarks>>

なし

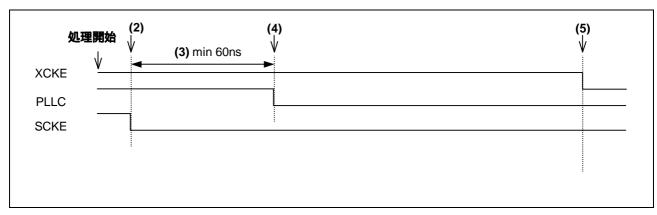

## 2.3.9 オートクロックモニタービット(CNTFLG)

本コントローラーがクロック復帰処理を行っている期間に"1"が表示されるビットです。

本ビットは、本コントローラーがクロック復帰処理を開始したときに"0"から"1"に変化し、クロック復帰が完了して"SCKE=1"の状態になったときに"1"から"0"に変化します。

## 2.3.10 CS\_N復帰禁止ビット(PCSDIS)

本コントローラーがLowパワースリープ状態から通常状態へ遷移するためのイベントとしてCS\_N端子の立下りエッジを許可するか、禁止するかを設定するためのビットです。

本ビットの設定値による復帰イベントの相違については表 2.7を参照ください。

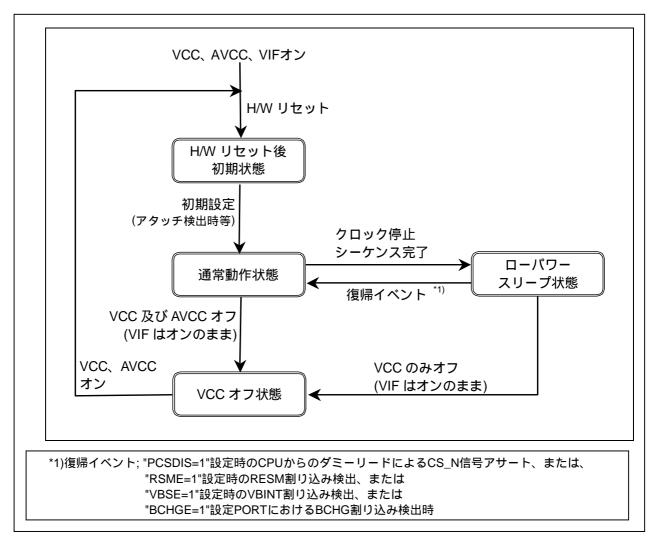

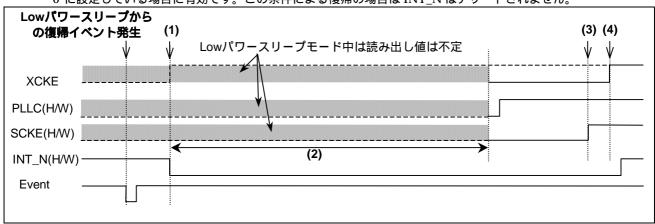

#### 2.3.11 Lowパワースリープモード許可ビット(LPSME)

"LPSME=1"設定時に発振バッファを停止 ("XCKE=0"設定) させた場合、 本コントローラーはLowパワースリープ 状態に遷移し、"LPSME=0"設定時の発振バッファ停止状態よりも待機電流を低減させることができます。

"LPSME=1"かつ"XCKE=0"によるLowパワースリープ状態から本コントローラが通常のクロック動作状態へ復帰 するためのイベントは以下の2種類です。

表 2.7 Lowパワースリープ状態 ("LPSME=1"かつ"XCKE=0") からの復帰イベント

| コントローラー機能<br>選択<br>(DCFMビット設定値) | 条件                | 復帰イベント                                                                                     |

|---------------------------------|-------------------|--------------------------------------------------------------------------------------------|

| Peripheral Controller<br>機能選択時  | "PCSDIS=0"<br>設定時 | (1) "RSME=1"設定時のRESM割り込み検出<br>(2) "VBSE=1"設定時のVBINT割り込み検出<br>(3) CPUからのダミーリードによるCS_N信号アサート |

|                                 | "PCSDIS=1"<br>設定時 | (1) "RSME=1"設定時のRESM割り込み検出<br>(2) "VBSE=1"設定時のVBINT割り込み検出                                  |

| Host Controller機能選択時            | "PCSDIS=0"<br>設定時 | (1) "BCHGE=1"設定PORTにおけるBCHG割り込み検出<br>(2) CPUからのダミーリードによるCS_N信号アサート                         |

|                                 | "PCSDIS=1"<br>設定時 | (1) "BCHGE=1"設定PORTにおけるBCHG割り込み検出                                                          |

"LPSME=1"設定は、"XCKE=1"の時に行ってください。

"LPSME=1"設定時に、"XCKE=0"設定によってLowパワースリープ状態に遷移させた場合、"XCKE=0"設定後10us 間は本コントローラーへのアクセスは禁止です。従ってCPUからのダミーリードによるLowパワースリープ状態から の復帰は、少なくとも"XCKE=0"設定後10us経過後に実施してください。

本コントローラーがLowパワースリープ状態に遷移した場合、FIFOバッファ内の値は失われます。"LPSME=1" 設定で本コントローラを使用する場合、"XCKE=0"を設定する前にFIFOの内容の読み出しを完了させるかもしくは かFIFOバッファのクリアを実施してください。

#### 2.3.12 Hi-Speed動作許可ピット (HSE)

本ビットを"1"に設定することにより、PORT1に対してHi-Speed動作を許可します。"HSE=1"を設定した場合、本 コントローラーはReset Handshakeの結果に従いPORT1をHi-SpeedまたはFull-Speed動作させます。

## 2.3.12.1 Host Controller 機能選択時

2.3.5.1を参照してください。

#### 2.3.12.2 Peripheral Controller 機能選択時

本ビットには"0"を設定してください。

Peripheral Controller機能選択時はPORT1を使用することはできません。

## 2.3.13 PORT1用D+,D-ライン抵抗制御ビット (DRPD)

表 2.8にPORT1のUSBデータバスの抵抗についての設定を示します。SYSCFG1レジスタのDRPDビットでUSB データバスの抵抗選択を行ってください。

表 2.8 PORT1 USBデータバス抵抗の制御

| DRPD | D- Line   | D+ Line    | Remarks                       |  |  |

|------|-----------|------------|-------------------------------|--|--|

| 0    | Open Open |            | PORT1 未使用時                    |  |  |

| 1    | Pull-Down | Pull- Down | Host Controller として動作中はこの状態に設 |  |  |

|      | II I      |            | 定してください                       |  |  |

Host Controller機能選択時に本ビットを"1"に設定すると、本コントローラーはPORT1のD+、D-ラインをPull Downします。

OVCMON

## 2.4 システムコンフィグレーションステータス

12

13

|   | システムコンフィ | グレーション | ステータスし | バスター  | I OZTZZVZ I |

|---|----------|--------|--------|-------|-------------|

| • | ンスノムコノノイ | ソレーション | スノーツスレ | ノンスツー | しつもつひょうひょ   |

10

| <アドレス:04H> |       |    |    |  |  |  |

|------------|-------|----|----|--|--|--|

| 3          | 2     | 1  | 0  |  |  |  |

|            | IDMON | LN | ST |  |  |  |

| ?          | ?     | Ο  | Ω  |  |  |  |

| Bit   | Name                            | Function                                                                                                                                                       | S/W | H/W | Remarks |

|-------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------|

| 15-14 | OVCMON<br>OVCUR0A,OVCUR0B端子モニター | OVCUR0A,OVCUR0B端子の入力状態が表示されます。<br>00:OVCUR0A=Low, OVCUR0B=Low<br>01:OVCUR0A=Low, OVCUR0B=High<br>10:OVCUR0A=High, OVCUR0B=Low<br>11:OVCUR0A=High, OVCUR0B=High | R   | W   |         |

| 13-6  | 何も配置されていません。"0"に固定して            | ください。                                                                                                                                                          |     |     |         |

| 5     | Port0 HOST SOFアクティブモニター         | Port0の動作に対しUACTビットの設定が反映<br>されたことを表示します。<br>0: (micro) SOFの発行を停止した<br>1: (micro) SOFの発行を継続している                                                                 | R   | W   |         |

| 4-2   | 何も配置されていません。"0"に固定して            | てください。                                                                                                                                                         |     |     |         |

| 2     | IDMON<br>ID0端子モニター              | ID0端子の入力状態が表示されます。<br>0: ID0=Low<br>1: ID0=High                                                                                                                | R   | W   |         |

|       | LNST<br>PORT0 USBデータラインステータスモ   | PORTOのUSBライン状態が表示されます。<br>詳細説明をご覧下さい。                                                                                                                          | R   | W   |         |

6

SOFEA

#### <<Remarks>>

ニター

なし

## 2.4.1 OVCUR0A、OVCUR0B端子モニタービット (OVCMON)

本コントローラーは、本レジスタのbit15にOVCUR0A端子の状態を、bit14にOVCUR0B端子の入力状態を表示します。

#### 2.4.2 Port0 HOST SOFアクティブモニタビット (SOFEA)

Host Controller機能選択時にソフトウェアがUACTビットを"1"に設定すると、本コントローラーは本ビットに"1"を表示し、PORTOをUSBバス許可状態にし、SOF出力を行います。

ソフトウェアがUACTビットを"0"に設定した場合、本コントローラーは、(micro) SOF出力後Idle状態に遷移し本ビットに"0"を表示します。

サスペンド実行時、ソフトウェアが**UACT**ビットを"0"にクリアした後に、本コントローラがPort0に最後のSOFを出力し終わっことを確認するために本ビットを使用します。

## 2.4.3 ID0端子モニタビット (IDMON)

本コントローラーは、本ビットにID0端子の入力状態を表示します。

#### 2.4.4 ラインステータスモニタピット (LNST)

表 2.9に本コントローラーのUSBデータバスラインステータス表を示します。本コントローラーは、**SYSSTS0**レジスタの**LNST**ビットにPORT0のUSBデータバスのラインステータス(D+ライン、及びD-ライン)をモニタします。

LNSTビットの参照は、Peripheral Controller機能選択時にはアタッチ処理("DPRPU=1"設定)以後、Host Controller機能選択時には、Pull Down許可("DRPD=1"設定)以後に行ってください。

## 表 2.9 USBデータパスラインステータス表

| LNST [1]    | ] LNST [0] Low-Speed 動作時<br>(Host Controller 機<br>能選択時のみ) |         |         | Hi-Speed 動作時 | Chirp 動作時 |

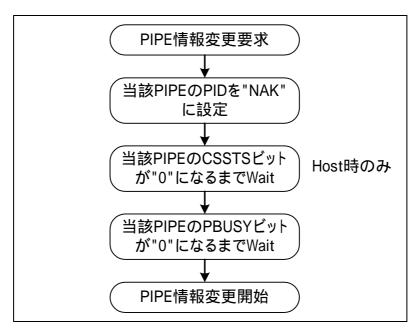

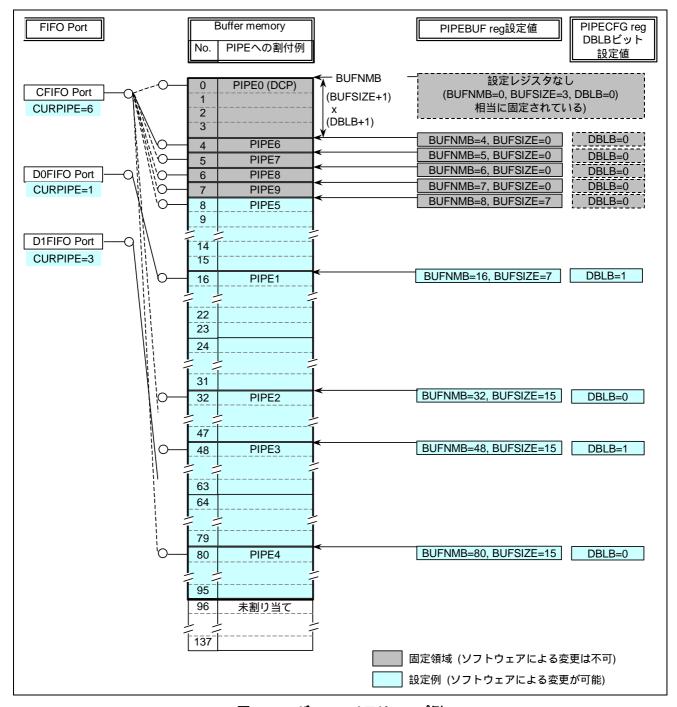

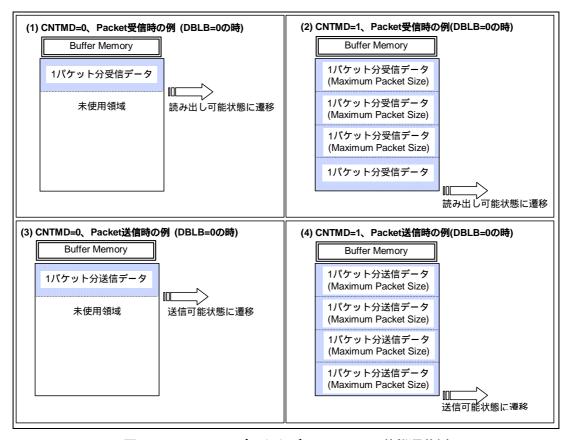

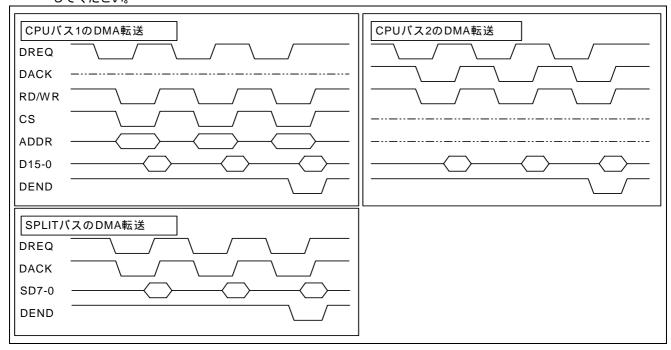

|-------------|-----------------------------------------------------------|---------|---------|--------------|-----------|