# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、<mark>誤</mark>りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害<mark>がお</mark>客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、<mark>船舶等)</mark> 交通用信号機器、防災・防犯装置、各種安全装置、生命維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載され<mark>た当社製品のご</mark>使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につ<mark>きまし</mark>ては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障<mark>および事故</mark>につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# R2A45005NP/HNP

# CDS/PGA&10 ビット A/D コンバータ

RJJ03F0251-0100 Rev.1.00 2008.06.19

#### 概要

R2A45005NP/HNP は CCD カメラデジタル信号処理システムに最適な CDS-PGA 間のアナログ処理 (CDS/PGA) および 10 ビット A/D コンバータを 1 チップに収めた CMOS IC です。

#### 機能

- 相関二重サンプリング

- PGA

- オフセット補償

- シリアルインタフェース制御

- 10 ビット A/D コンバータ

- 3V 単一動作

- 消費電力/動作周波数 (2.7V 動作時)

R2A45005HNP: 97mW(Typ)/最高周波数: 40MHz

R2A45005NP: 54mW(Typ)/最高周波数: 28MHz

- OFN 36 ピン パッケージ

## 特長

- S/H 方式相関二重サンプリングにより, CCD 出力低域雑音の良好な抑圧が可能

- リファレンスレベルの S/H 応答周波数特性は外付け定数および,レジスタに調整可能

- PG アンプによる高 S/N , 広カバーレンジ化により , 高感度化が可能

- PGA の Gain 変化による出力 DC オフセット および CCD オフセット等のすべての DC オフセットを CDS アンプ入力にフィードバックし,補償

- シリアルインタフェースにより、PGA、スタンバイモード, etc が可能

- A/D コンバータは 10 ビット分解能で高精度

- A/D 出力コードとして差分符号化グレイコードを選択可能 疑似輪郭 (波紋) の抑圧に効果的。弊社にて特許取得済み

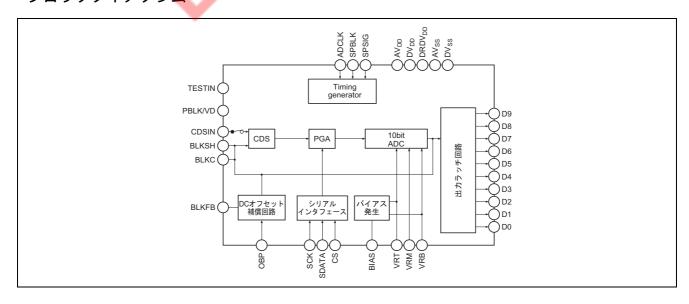

# ブロックダイアグラム

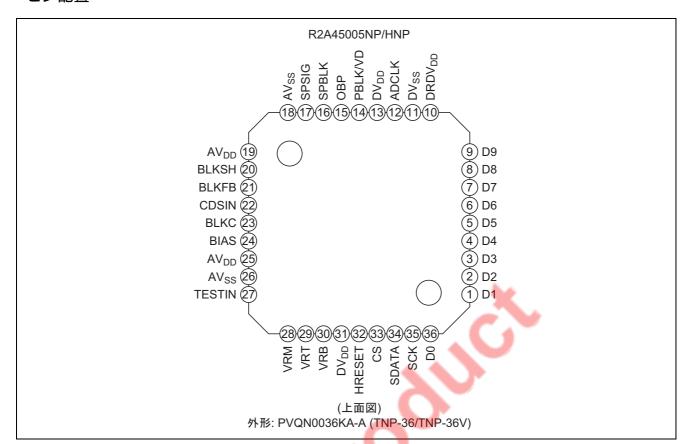

# ピン配置

# ピン説明

| ピン No. | ピン名                | 説明                                                        | I/O | アナログ(A)/<br>デジタル(D) |

|--------|--------------------|-----------------------------------------------------------|-----|---------------------|

| 1~9    | D1 ~ D9            | デジタル出力                                                    | 0   | D                   |

| 10     | DRDV <sub>DD</sub> | 出力バッファ用電源端子 (3V)                                          | _   | D                   |

| 11     | DV <sub>SS</sub>   | デジタルグランド (OV)                                             | _   | D                   |

| 12     | ADCLK              | ADC 変換クロック入力端子                                            | I   | D                   |

| 13     | $DV_DD$            | デジタル電源端子 (3V)                                             |     | D                   |

| 14     | PBLK/VD            | プリブランキング/VD 入力端子                                          | I   | D                   |

| 15     | OBP                | オプティカルブラックパルス入力端子                                         | I   | D                   |

| 16     | SPBLK              | 黒レベルサンプリングクロック入力端子                                        | I   | D                   |

| 17     | SPSIG              | 信号レベルサンプリングクロック入力端子                                       | I   | D                   |

| 18     | AV <sub>SS</sub>   | アナロググランド (OV)                                             |     | Α                   |

| 19     | AV <sub>DD</sub>   | アナログ電源端子 (3V)                                             |     | Α                   |

| 20     | BLKSH              | 黒レベル S/H 端子                                               |     | Α                   |

| 21     | BLKFB              | 黒レベル FB 端子                                                |     | Α                   |

| 22     | CDSIN              | CDS 入力端子                                                  | I   | Α                   |

| 23     | BLKC               | 黒レベル C 端子                                                 |     | Α                   |

| 24     | BIAS               | 内部バイアス端子                                                  |     | Α                   |

|        |                    | 33kΩの抵抗を AV <sub>SS</sub> との間に接続してください。                   |     |                     |

| 25     | AV <sub>DD</sub>   | アナログ電源端子 (3V)                                             |     | Α                   |

| 26     | AV <sub>SS</sub>   | アナロググランド (OV)                                             |     | Α                   |

| 27     | TESTIN             | TEST 入力端子                                                 |     | Α                   |

| 28     | VRM                | 基準電圧端子 1                                                  | _   | Α                   |

|        |                    | 0.1μF セラミックコンデンサ <mark>を AV<sub>SS</sub> との</mark> 間に接続。  |     |                     |

| 29     | VRT                | 基準電圧端子3                                                   | _   | Α                   |

|        |                    | 0.1μF セラミック <mark>コンデンサ</mark> を AV <sub>SS</sub> との間に接続。 |     |                     |

| 30     | VRB                | 基準電圧端子 2                                                  | _   | Α                   |

|        |                    | 0.1μF セラミックコンデンサを AV <sub>SS</sub> との間に接続。                |     |                     |

| 31     | DV <sub>DD</sub>   | デジタル電源端子 (3V)                                             |     | D                   |

| 32     | HRESET             | リセット端子                                                    | _   | D                   |

| 33     | CS                 | シリアルインタフェース制御入力端子                                         | I   | D                   |

| 34     | SDATA              | シリアルデータ入力端子                                               | I   | D                   |

| 35     | SCK                | シリアルクロック入力端子                                              | I   | D                   |

| 36     | D0                 | デジタル出力                                                    | 0   | D                   |

# 入出力等価回路

| ピン     | /名                                         | 等価回路                                                                    |

|--------|--------------------------------------------|-------------------------------------------------------------------------|

| デジタル出力 | D0 ~ D9                                    | DIN デジタル出力<br>STBY ボッカ                                                  |

| デジタル入力 | ADCLK OBP SPBLK SPSIG CS SCK SDATA PBLK/VD | デジタル入力<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・ |

| アナログ   | CDSIN                                      | 内部でVRT に接続<br>CDSIN                                                     |

|        | TESTIN                                     | AV <sub>DD</sub> 内部でVRM に接続                                             |

|        | BLKSH<br>BLKFB<br>BLKC                     | BLKFB BLKSH BLKSH BLKC                                                  |

|        | VRT<br>VRM<br>VRB                          | VRT VRM VRB AVDD                                                        |

|        | BIAS                                       | BIAS AV <sub>DD</sub> + W - IE                                          |

# 絶対最大定格

$(Ta = 25^{\circ}C)$

| 項目       | 記号                    | 定格値                        | 単位 |

|----------|-----------------------|----------------------------|----|

| 電源電圧     | V <sub>DD</sub> (max) | 4.1                        | V  |

| 許容損失     | Pt (max)              | 400                        | mW |

| 動作電源電圧   | Vopr                  | 2.7 ~ 3.45                 | V  |

| アナログ入力電圧 | V <sub>IN</sub> max)  | $-0.3 \sim AV_{DD} + 0.3$  | V  |

| デジタル入力電圧 | V <sub>I</sub> (max)  | $-0.3 \sim DV_{DD} + 0.3$  | V  |

| 動作温度     | Topr                  | <b>−20 ~ +85</b>           | °C |

| 保存温度     | Tstg                  | <b>−</b> 55 ~ <b>+</b> 125 | °C |

- 【注】 1.  $V_{DD}$ は,  $AV_{DD} \cdot DV_{DD} \cdot DRDV_{DD}$ を指します。

- 2. ノイズフィルタにより AVDD と DVDD・DRDVDD を分離する場合は,電源投入時の電位差を 0.3V 以下に,動作 時の電位差を 0.1V 以下にしてください。

# 電気的特性

# CDSIN 入力モード適用項目

(特記なき場合, Ta = 25°C,  $AV_{DD} = 3.0V$ ,  $DV_{DD} = 3.0V$ ,  $R_{BIAS} = 33k\Omega$ )

|                   |                       |                                                 | 仕様   |                                  |        |                                 |                                |

|-------------------|-----------------------|-------------------------------------------------|------|----------------------------------|--------|---------------------------------|--------------------------------|

| 項目                | 記号                    | Min                                             | Тур  | Max                              | 単位     | 測定条件                            | 備考                             |

| 電源電圧範囲            | $V_{DD}$              | 2.7                                             | 3.0  | 3.45                             | V      | A A A                           |                                |

| 变換周波数             | f <sub>CLK</sub> _hi  | 28                                              | _    | 40                               | MHz    | R2A45005HNP                     |                                |

|                   | f <sub>CLK</sub> _low | 5.5                                             | _    | 28                               | MHz    | R2A45005NP                      |                                |

| デジタル<br>入力電圧      | V <sub>IH</sub>       | $2.2 \times \frac{DV_{DD}}{3.0}$                | _    | $DV_{DD}$                        | V      | 5                               | CS, SCK, SDATA 以外のデ<br>ジタル入力ピン |

|                   | V <sub>IL</sub>       | 0                                               | l    | $0.8 \times \frac{DV_{DD}}{3.0}$ | >      |                                 |                                |

|                   | V <sub>IH2</sub>      | $2.25 \times \frac{\text{DV}_{\text{DD}}}{3.0}$ | -    | $DV_{DD}$                        | V      |                                 | CS, SCK, SDATA                 |

|                   | V <sub>IL2</sub>      | 0                                               |      | $0.6 	imes rac{DV_DD}{3.0}$     | ٧      |                                 |                                |

| デジタル              | V <sub>OH</sub>       | DVdd-0.5                                        | -    | _                                | V      | $I_{OH} = -1mA$                 |                                |

| 出力電圧              | V <sub>OL</sub>       |                                                 | J    | 0.5                              | V      | $I_{OL} = +1mA$                 |                                |

| デジタル              | I <sub>IH</sub>       | _                                               | Ì    | 50                               | μΑ     | V <sub>IH</sub> = 3.3V          |                                |

| 入力電流              | I <sub>IH2</sub>      | +                                               |      | 250                              | μΑ     | V <sub>IH</sub> = 3.3V          |                                |

|                   | I <sub>IL</sub>       | <b>-50</b>                                      | ]    | _                                | μΑ     | $V_{IL} = 0V$                   |                                |

| デジタル              | I <sub>OZH</sub>      | <u> </u>                                        | / —  | 50                               | μΑ     | $V_{OH} = V_{DD}$               |                                |

| 出力電流              | I <sub>OZL</sub>      | <b>-50</b>                                      |      | _                                | μΑ     | $V_{OL} = 0V$                   |                                |

| ADC 分解能           | RES                   | 10                                              | 10   | 10                               | bit    |                                 |                                |

| ADC 積分<br>リニアリティ  | INL                   |                                                 | (3)  | _                                | LSBp-p | f <sub>CLK</sub> = 20MHz        |                                |

| ADC 微分<br>リニアリティ+ | DNL+                  | _                                               | 0.3  | 0.9                              | LSB    | f <sub>CLK</sub> = 20MHz        | *1                             |

| ADC 微分<br>リニアリティ– | DNL-                  | -0.9                                            | -0.3 | _                                | LSB    | f <sub>CLK</sub> = 20MHz        | *1                             |

| スリープ電流            | I <sub>SLP</sub>      | -100                                            | 0    | 100                              | μА     | デジタル入力ピンは OV 固定, 出力ピンはオープン      |                                |

| スタンバイ電流           | I <sub>STBY</sub>     | _                                               | 3    | 5                                | mA     | デジタル入出力ピンは 0V<br>固定             |                                |

| デジタル出力            | t <sub>HZ</sub>       | _                                               |      | 100                              | ns     | $R_L = 2k\Omega$ , $C_L = 10pF$ |                                |

| Hi-Z 遅延時間         | t <sub>LZ</sub>       | _                                               | _    | 100                              | ns     | $R_L = 2k\Omega$ , $C_L = 10pF$ |                                |

|                   | t <sub>ZH</sub>       | _                                               | _    | 100                              | ns     | $R_L = 2k\Omega$ , $C_L = 10pF$ |                                |

|                   | t <sub>ZL</sub>       | _                                               | _    | 100                              | ns     | $R_L = 2k\Omega$ , $C_L = 10pF$ |                                |

【注】 1. 微分リニアリティは,隣り合うコード間のリニアリティ誤差の差を計算したものです。

# CDSIN 入力モード適用項目

(特記なき場合 ,  $Ta=25^{\circ}C$ ,  $AV_{DD}=3.0V$ ,  $DV_{DD}=3.0V$ ,  $R_{BIAS}=33k\Omega$ )

|                   |                    | 仕様                         |                              |                     |     |                          |               |

|-------------------|--------------------|----------------------------|------------------------------|---------------------|-----|--------------------------|---------------|

| 項目                | 記号                 | Min                        | Тур                          | Max                 | 単位  | 測定条件                     | 備考            |

| 消費電流              | I <sub>DD1</sub>   | 1                          | (36)                         | _                   | mA  | f <sub>CLK</sub> = 40MHz | Pwr-sel = "L" |

|                   | I <sub>DD2</sub>   | 1                          | (20)                         | _                   | mA  | f <sub>CLK</sub> = 28MHz | Pwr-sel = "H" |

| CCD オフセット<br>許容範囲 | V <sub>CCD</sub>   | (-100)                     |                              | (100)               | mV  |                          |               |

| タイミング仕様(1)        | t <sub>CDS1</sub>  | _                          | (1.5)                        | _                   | ns  |                          | 表 10 参照       |

| タイミング仕様(2)        | t <sub>CDS2</sub>  | Typ × 0.8                  | 1/4f <sub>CLK</sub>          | Typ × 1.2           | ns  |                          |               |

| タイミング仕様(3)        | t <sub>CDS3</sub>  | 1                          | (1.5)                        | _                   | ns  |                          |               |

| タイミング仕様(4)        | t <sub>CDS4</sub>  | Typ × 0.8                  | 1/4f <sub>CLK</sub>          | Typ × 1.2           | ns  |                          |               |

| タイミング仕様(5)        | t <sub>CDS5</sub>  | 1/2f <sub>CLK</sub> × 0.85 | 1/2f <sub>CLK</sub><br>× 0.9 | 1/2f <sub>CLK</sub> | ns  |                          |               |

| タイミング仕様(6)        | t <sub>CDS6</sub>  | _                          | (5)                          | _                   | ns  |                          |               |

| タイミング仕様(7)        | t <sub>CDS7</sub>  | 11                         | _                            | _                   | ns  |                          |               |

| タイミング仕様(8)        | t <sub>CDS8</sub>  | 11                         | _                            | _                   | ns  |                          |               |

| タイミング仕様(9)        | t <sub>CDS9</sub>  | 1                          | (7)                          | _                   | ns  | C <sub>L</sub> = 10pF    |               |

| タイミング仕様(10)       | t <sub>CDS10</sub> | 1                          | (16)                         | _                   | ns  | C <sub>L</sub> = 10pF    |               |

| クランプレベル           | CLP(00)            | _                          | (14)                         | _                   | LSB |                          | *1            |

|                   | CLP(09)            | _                          | (32)                         | _                   | LSB |                          |               |

|                   | CLP(31)            | _                          | (76)                         | _                   | LSB |                          |               |

| CDS 入力時           | PGA(0)             | -4.4                       | -2.4                         | -0.4                | dB  |                          |               |

| PGA ゲイン           | PGA(63)            | 4.1                        | 6.1                          | 8.1                 | dB  |                          |               |

|                   | PGA(127)           | 12.5                       | 14.5                         | 16.5                | dB  |                          |               |

|                   | PGA(191)           | 21.0                       | 23.0                         | 25.0                | dB  |                          |               |

|                   | PGA(255)           | 29.3                       | 31.3                         | 33.3                | dB  |                          |               |

【注】 1. ()内は参考値を示します。

#### 内蔵機能

#### 機能概要

- CDS 入力

- CDS (Correlated Double Sampling) による CCD 低域雑音の抑制

- OB 期間の信号レベルを 14~76LSB (レジスタにより設定: 5 ビット 2LSB ステップ制御) にクランプ\*<sup>1</sup>

- -2.36dB ~ 31.40dB 間で 8 ビット (0.132dB ステップ,レジスタ設定) の Gain 調整が可能\*<sup>2</sup>

- PGA, ADC の自動オフセットキャリブレーション機能

- CCD, CDS の DC オフセット補償フィードバック機能

- プリブランキング機能

- 過大入力信号から CDS 入力動作を切り放し保護 デジタル出力をクランプレベルに固定

- デジタル出力イネーブル機能

- 【注】 1. 14LSB 設定時は,保証範囲外。

- 2. 1V 入力でデジタル出力フルスケールを 0dB (1 倍) と定義。

#### 動作説明

図1にCDS/PGA+ADCの機能ブロックを示します。

义 1 R2A45005NP/HNP 機能ブロック図

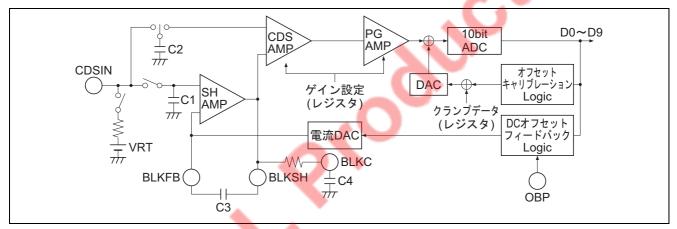

1. CDS (Correlated Double Sampling) 回路

CDS 回路は、黒レベルと黒レベルを含む信号との差電圧を取り出す回路です。

黒レベルは, SPBLK パルスにより C1 に直接サンプリングされ SHAMP によりバッファリングされた後, CDSAMP に供給されます。

信号レベルは, SPSIG パルスにより C2 に直接サンプリングされそのまま CDSAMP に供給されます (図1 参照)。

CDSAMP は上記 2 つの信号レベルの差をとると共に,前段のプログラマブルゲインアンプとして働きま す。

CDS 入力は, VRT(2V) にバイアスされます。

PBLK の期間,上記のサンプリング動作およびバイアス動作は停止します。

2. PGA 回路

PGAMP は後段のプログラマブルゲインアンプです。前段の CDSAMP と合わせて 8 ビットのレジスタで ゲインを設定します。

レジスタ値  $N=0\sim255$  に対し,下式のようにゲインが変化します。

CDSIN モード時: Gain = -2.36dB + 0.132dB × N (Log リニア) (1V 入力でデジタル出力フルスケールを 0dB (1 倍) と定義)

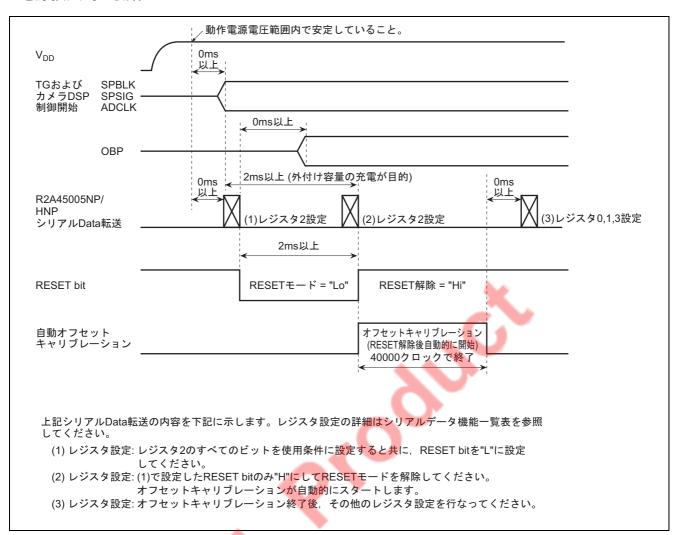

3. 自動オフセットキャリブレーション機能,黒レベル クランプデータ設定 自動オフセットキャリブレーションは,PGAMP の出力に加算する DAC の DC 電圧を調整します。 この DAC には , PGAMP の出力オフセットと ADC の入力オフセットをキャンセルするデータに , レジスタ設定によるクランプデータ ( $14LSB \sim 76LSB$ ) が加算されて与えられます。 自動オフセットキャリブレーションは , レジスタ設定による RESET モード解除後自動的にスタートし , 40000 クロック後に終了します (fclk = 40.0MHz の場合 , 1.0ms)。

### 4. DC オフセット補償フィードバック機能

DC オフセット補償フィードバックは QB 期間に入力された黒信号レベルを DC 基準とするためのフィー ドバックであり, CCD オフセット, CDSAMP オフセット等を含むすべてのオフセットを補償します。

DC オフセット補償フィードバックは, OB 期間に ADC 出力からオフセットを演算し,電流 DAC によっ て SHAMP の帰還容量 C3 にチャージします (図 1 参照)。

このフィードバックループの 1H 当たりのオープンループ微分ゲイン (ΔGain/ΔH) は下式によって与えら れます (1H は OBP の 1 周期です)。

△Gain/△H = 0.078/(fclk × C3) (fclk: ADCLK 周波数, C3: SHAMP の外付け帰還容量)

例: fclk = 20.0Hz,  $C3 = 1.0 \mu F$  $\Delta$ Gain/ $\Delta$ H = 0.039

1H 当たりの DC オフセット補正量 (LSB) =  $0.0039 \times オフセット誤差量 (LSB)<math>^{*1}$

## 【注】 1. 上記オフセット誤差量には上限値があります。

表1のレジスタ設定で指定した条件が生じると,クランプ高速引き込み動作に移行し,上記フィードバッ クループゲインが N 倍されます。ループゲインの倍率 N はレジスタによって 4,32,64,128 倍の 4 種類から選 択できます (表 2 参照 (オープンループ微分ゲイン ( $\Delta Gain/\Delta H$ ) が 2 以上になると発振します。1 以下の設定 で使用してください))。

クランプ高速引き込みを終了するオフセット誤差はレジスタによって 8.16LSB の 2 種類から選択します。 また ,クランプ高速引き込みを終了し通常のループゲインに戻すまでの時間<mark>はレジスタ</mark>によって 1, 8, 16, 32H の4種類から選択します (オフセット誤差がレジスタ設定の8,16LSB以上ある間は高速引き込み動作が継続 され,オフセット誤差が 8 もしくは 16LSB 以内に入った後,レジスタ設定の 1,8,16 もしくは 32H 後に通常 のループゲインに戻ります (表 3, 4 参照)。

表 1 クランプ高速引き込みの開始条件

| Hsclp-en<br>(レジスタ設定) | 開始条件        |

|----------------------|-------------|

| L                    | ゲイン設定の変更    |

| Н                    | VD のフロントエッジ |

表 3 クランプ高速引き込み終了のオフセット誤差

| Hsclp-th<br>(レジスタ設定) |        |

|----------------------|--------|

| L                    | 8 LSB  |

| Н                    | 16 LSB |

クランプ高速引き込み時,ループゲイン倍率 表 2

| HGair<br>(レジス | า-Nsel<br>夕設定) | . (O) Y |

|---------------|----------------|---------|

| [0]           | [1]            | 倍率 N    |

| L             | L              | 4倍      |

| Н             | L              | 64 倍    |

| L             | Н              | 128 倍   |

| Н             | Н              | 32 倍    |

表 4 クランプ高速引き込み解除時間

|     | p-Hsel<br>夕設定) |      |

|-----|----------------|------|

| [0] | [1]            | 解除時間 |

| L   | L              | 1H   |

| Н   | L              | 16H  |

| L   | Н              | 32H  |

| Н   | Н              | 8H   |

#### 5. プリブランキング機能

PBLK 入力期間,過大入力信号から CDS 入力動作を切り離し保護します $st^{-1}$ 。また,ADC のデジタル出力 をクランプデータ (14~76LSB) に固定します。

【注】 プリブランキング機能はレジスタ設定が PBLK-sel = "L"のときのみ使用可能です。

6. ADC デジタル出力コントロール機能 ADC デジタル出力には,出力イネーブル,コード変換,テストモードなどの機能があります。 表 5, 6, 7 に出力機能およびコード表を示します。

# 表 5 ADC デジタル出力機能表

| STBY | TEST0 | TEST1 | /NIN | NIN/ | PBLK | ADCデジタル出力 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 動作モード |

|------|-------|-------|------|------|------|-----------------------------------------------|

| Н    | Х     | Х     | Х    | Χ    | Х    | Hi-Z 低電力待機                                    |

| L    | L     | L     | L    | L    | Н    | 表6に従う   通常動作                                  |

|      |       |       | L    | Н    | Н    | 表6でD9が反転                                      |

|      |       |       | Н    | ∟    | Н    | 表6でD8~D0が反転                                   |

|      |       |       | Н    | Η    | Н    | 表6でD9~D0が反転                                   |

|      |       |       | Χ    | Χ    | L    | 出力コードをClamp Levelに固定 プリブランキング                 |

|      |       | Н     | L    | L    | Н    | 表7に従う 通常動作                                    |

|      |       |       | L    | Н    | Н    | 表7でD9が反転                                      |

|      |       |       | Н    | L    | Н    | 表7でD8~D0が反転                                   |

|      |       |       | Н    | Н    | Н    | 表7でD9~D0が反転                                   |

|      |       |       | Х    | Χ    | L    | 出力コードをClamp Levelに固定   プリブランキング               |

|      | Н     | Х     | Ĺ    | L    | Χ    | H L H L H L H L H L FAFE                      |

|      |       |       | Ĺ    | Η    | Х    |                                               |

|      |       |       | Н    | L    | Χ    | H   H   L   H   L   H   L   H                 |

|      |       |       | Н    | Н    | Х    | L   H   L   H   L   H   L   H   L   H         |

#### 表 6 ADC 出力コード表

|     | 出力端子   |   | D9 | D8  | D7  | D6 🥖 | D5  | D4  | D3  | D2  | D1  | D0  |

|-----|--------|---|----|-----|-----|------|-----|-----|-----|-----|-----|-----|

| 出力  | ステップ 0 |   | L  | L   | L   | L    | L   | L   | L   | L   | L   | L   |

| コード | 1      |   | L  | L   | L   |      | L   | L   | L   | L   | L   | H   |

|     | 2      | į | L  | L   | L   |      | L   | L   | L   | L   | Н   | L   |

|     | 3      | į | L  | L   | L_  | L    | L   | į L | L   | L   | H   | Н   |

|     | 4      |   | L  | ; L | LP. |      | ¦ L | ; L | L   | ; Н | ; L | L   |

|     | 5      | ; | L  | L   |     | L    | ¦ L | ; L | ; L | ; Н | ; L | ; H |

|     | 6      |   | L  |     | L L | L    | L   | ¦ L | ¦ L | l H | : н | : L |

|     | :      |   | :  |     |     |      | :   | 1 : | :   | :   | :   | :   |

|     | 511    |   | L  | H   | H   | Н    | Н   | H   | Н   | Н   | Н   | Н   |

|     | 512    | į | Н  |     | L   | L    | L   | L   | L   | L   | L   | L   |

|     | :      | į | :  |     |     |      |     |     |     | :   |     | : 1 |

|     | 1020   | į | H  | H   | T H | Н    | H   | ; H | H   | Н   | į L | L   |

|     | 1021   |   | H  | H   | Н   | Н    | H   | ; H | H   | H   | ; L | H   |

|     | 1022   |   | Н  | H   | Н   | Н    | ; Н | ; H | ; H | ; Н | ; H | ; L |

|     | 1023   |   | H  | Н   | Н   | Н    | Н   | ¦ H | Н   | Н   | H   | H   |

# 表 7 ADC 出力コード表 (TEST1)

|     | 出力端子   | D9 | D8  | D7  | D6       | D5  | D4  | D3 | D2       | D1  | D0  |

|-----|--------|----|-----|-----|----------|-----|-----|----|----------|-----|-----|

| 出力  | ステップ 0 | L  | L   | L   | L        | L   | L   | L  | L        | L   | L   |

| コード | 1      | L  | L   | L   | L        | L   | L   | L  | L        | L   | Н   |

|     | 2      | L  | L   | L   | L        | L   | L   | L  | L        | Н   | Н   |

|     | 3      | L  | L   | L   | L        | L   | L   | L  | L        | Н   | L   |

|     | 4      | L  | : L | ; L | ; L      | ; L | ; L | L  | ; H      | ; H | ; L |

|     | 5      | L  | ¦ L | ; L | ; L      | ¦ L | ¦ L | L  | ; H      | ; Н | ; H |

|     | 6      | L  | ¦ L | ¦ L | ; L      | ¦ L | ¦ L | L  | ; н      | ¦ L | : н |

|     | :      | ÷  | :   | :   | :        | :   | :   | :  | <u> </u> | :   |     |

|     | 511    | L  | Н   | L   | L        | L   | L   | L  | L        | L   | . L |

|     | 512    | Н  | Н   | L   | L        | L   | L   | L  | L        | L   | L   |

|     | :      | :  | :   |     |          |     |     |    |          |     | : 1 |

|     | 1020   | Н  | ; L | ; L | ; L      | ; L | ; L | L  | ; L      | ; Н | ; L |

|     | 1021   | Н  | ¦ L | ; L | ; L      | ¦ L | ¦ L | L  | ; L      | ; Н | ; H |

|     | 1022   | Н  | L   | L L | L        | L   | L   | L  | L L      | L   | H   |

|     | 1023   | Н  | L   | L   | <u> </u> | L   | L   | L  | <u> </u> | L   | L L |

<sup>【</sup>注】 1. STBY, TEST, LINV, MINVは、レジスタ設定です。 2. PBLK端子の極性はレジスタ設定がSPinv = "L"の設定です。

7. 黒レベルの S/H 応答 周波数特性の調整 黒レベルを S/H する CR 時定数は,レジスタ設定によって調整できます。 設定方法を表8に示します。

#### 表 8 SHSW CR 時定数設定表

|              | SHSW-fsel (レジスタ設定) |                                                                                                            |              |              |              |              |              |              |

|--------------|--------------------|------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|

|              | [0][1][2][3]       | 0][1][2][3][0][1][2][3][0][1][2][3][0][1][2][3][0][1][2][3][0][1][2][3][0][1][2][3][0][1][2][3][0][1][2][3 |              |              |              |              |              | [0][1][2][3] |

|              | L L L L            | H L L L                                                                                                    | L H L L      | H H L L      | L L H L      | H L H L      | L H H L      | HHHL         |

| CR時定数 (Typ)  | 2.20ns             | 2.30ns                                                                                                     | 2.51ns       | 2.64ns       | 2.93ns       | 3.11ns       | 3.52ns       | 3.77ns       |

| (カットオフ周波数換算) | (72MHz)            | (69MHz)                                                                                                    | (63MHz)      | (60MHz)      | (54MHz)      | (51MHz)      | (45MHz)      | (42MHz)      |

|              | SHSW-fsel (レジスタ設定) |                                                                                                            |              |              |              |              |              |              |

|              | [0][1][2][3]       | [0][1][2][3]                                                                                               | [0][1][2][3] | [0][1][2][3] | [0][1][2][3] | [0][1][2][3] | [0][1][2][3] | [0][1][2][3] |

|              | L L L H            | H L L H                                                                                                    | L H L H      | H H L H      | L L H H      | H L H H      | L H H H      | H H H H      |

| CR時定数 (Typ)  | 4.40ns             | 4.80ns                                                                                                     | 5.87ns       | 6.60ns       | 8.80 ns      | 10.6ns       | 17.6ns       | 26.4ns       |

| (カットオフ周波数換算) | (36MHz)            | (33MHz)                                                                                                    | (27MHz)      | (24MHz)      | (18MHz)      | (15MHz)      | (9MHz)       | (6MHz)       |

SHAMPの周波数特性は、レジスタ設定と31ピン外付けのC4によって調整できます。 設定方法を表9に示します。

表9に示す設定値以外は使用できません。

Cの推奨値は1000pF

**BLKC**

## 表 9 SHAMP 周波数特性設定表

| SHA-fsel (レジスタ設定) |                        |         |      |         |   |  |  |

|-------------------|------------------------|---------|------|---------|---|--|--|

| [0]               | 0] [1] [0] [1] [0] [1] |         |      |         |   |  |  |

| Н                 | L                      | L       | Н    | Η       | Н |  |  |

| 116               | MHz                    | 75N     | ЛHz  | 56MHz   |   |  |  |

| 10000pF           |                        | 13000pF |      | 18000pF |   |  |  |

| (270              | OpF)                   | (300    | )pF) | (360pF) |   |  |  |

【注】 上段 SHAMP カットオフ周波数 (Typ)

中段 C4の標準値 (最大値の規定はありません)

下段 C4の最小値 (この値以下にしないでください)

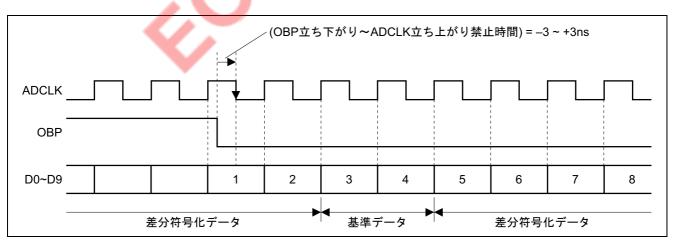

# 差分符号化タイミング仕様

表 10 シリアルデータ設定項目 1

|                                               | Low       | Hi       |

|-----------------------------------------------|-----------|----------|

| 出力モード設定 (TEST1)                               | バイナリコード   | グレイコード   |

| 出力モード設定 (TEST2) * <sup>1</sup>                | 差分符号化 OFF | 差分符号化 ON |

| Grayts[2]<br>OBP に対する ADCLK 極性 * <sup>2</sup> | ポジエッジ     | ネガエッジ    |

【注】 1. 表 12 参照

2. 図 2,3 参照

表 11 シリアルデータ設定項目 2

| grayts[1] | grayts[0] | 基準データ出力タイミング |

|-----------|-----------|--------------|

| Low       | Low       | 3番目と4番目      |

| Low       | Hi        | 4番目と5番目      |

| Hi        | Low       | 5番目と6番目      |

| Hi        | Hi        | 6番目と7番目      |

表 12 パイプラインディレイ数

| 出力モード TEST2 ビット設定 | パイプラインディレイ |

|-------------------|------------|

| TEST2 = "Lo"      | 13 clock   |

| TEST2 = "Hi"      | 14 clock   |

図 2 基準データの出力タイミング (レジスタ grayts[2] = Low, grayts[1:0] = ALL Low の場合)

図 3 基準データの出力タイミング (レジスタ grayts[2] = Hi, grayts[1:0] = ALL Low の場合)

# タイミングチャート

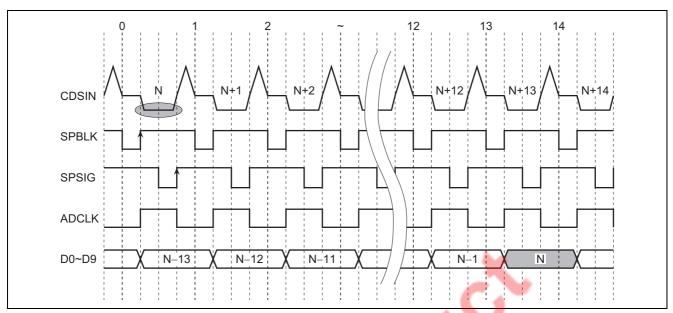

図4にCDSINから入力した場合の出力タイミング図を示します。

図4 CDSIN 端子から入力した場合の出力タイミング図

- ADC 出力 (D0 ~ D9) は ADCLK の立ち上がりエッジで出力されます。

- CDSIN 使用時のパイプラインディレイは 13 クロックとなります。

# 詳細タイミング仕様

#### CDSIN 使用時の詳細タイミング仕様

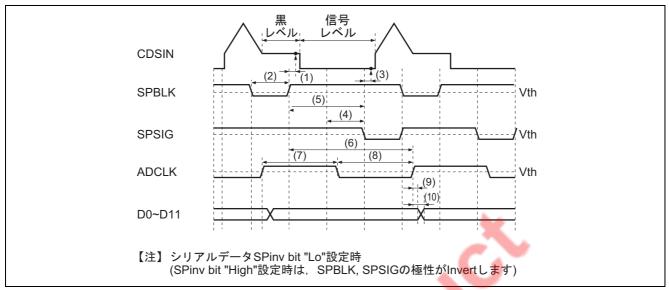

図 5 に CDSIN 使用時の詳細タイミング仕様を示し,表 13 に各タイミングの仕様を示します。

図 5 CDSIN 使用時の詳細タイミング仕様

表 13 CDSIN 使用時, 各タイミングの仕様

| No.      | タイミング                                                | 記号                   | Min                      | Тур                     | Max                 | 単位 |

|----------|------------------------------------------------------|----------------------|--------------------------|-------------------------|---------------------|----|

| (1)      | 黒レベル信号取り込み時間                                         | t <sub>CDS1</sub>    |                          | (1.5)                   | _                   | ns |

| (2)      | SPBLK "Lo"期間 * <sup>1</sup>                          | t <sub>CDS2</sub>    | Typ × 0.8                | 1/4f <sub>CLK</sub>     | Typ × 1.2           | ns |

| (3)      | 信号レベル取り込み時間                                          | t <sub>CDS3</sub>    |                          | (1.5)                   | _                   | ns |

| (4)      | SPSIG "Lo"期間 * <sup>1</sup>                          | t <sub>CDS4</sub>    | Typ × 0.8                | 1/4f <sub>CLK</sub>     | Typ × 1.2           | ns |

| (5)      | SPBLK 立ち上がり~SPSIG 立ち上がり時間 * <sup>1</sup>             | t <sub>CDS5</sub>    | $1/2f_{CLK} \times 0.85$ | $1/2f_{CLK} \times 0.9$ | 1/2f <sub>CLK</sub> | ns |

| (6)      | SPBLK 立ち上がり~ADCLK 立ち上がり禁止時間 * <sup>1</sup>           | t <sub>CDS6</sub>    | 1                        | 5                       | 11                  | ns |

| (7), (8) | ADCLK t <sub>WH</sub> min/t <sub>WL</sub> min        | t <sub>CDS7, 8</sub> | 11                       |                         | _                   | ns |

| (9)      | ADCLK 立ち上がり~デジ <mark>タ</mark> ル出力 <mark>保持</mark> 時間 | t <sub>CHLD9</sub>   | 3                        | 7                       | _                   | ns |

| (10)     | ADCLK 立ち上がり~デジ <mark>タル</mark> 出力 <mark>遅</mark> 延時間 | t <sub>COD10</sub>   | _                        | 16                      | 24                  | ns |

【注】 1. SPBLK, SPSIG の極性は,シリアルデータ Spinv bit "Lo"設定時で記述しています。

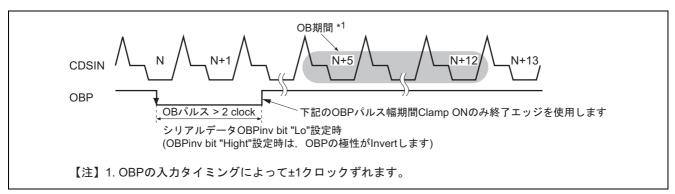

#### OBP の詳細タイミング仕様

図6にOBPの詳細タイミング仕様を示します。

OB パルス入力後,5 クロックから12 クロック目までがOB 期間です。

OB 期間に入力された8サイクル分の黒信号レベルが平均され,クランプレベル (DC 基準) となります。

図6 OBPの詳細タイミング仕様

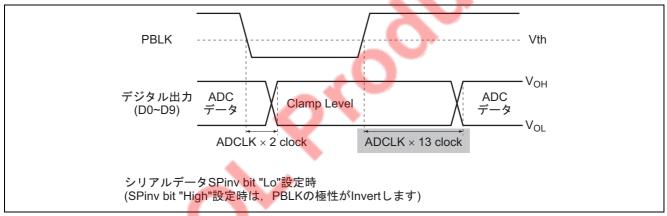

## プリブランキング時の詳細タイミング仕様

図7にプリブランキング時の詳細タイミング仕様を示します。

図7 プリブランキング時の詳細タイミング仕様

#### 表 14 一般シリアルデータ機能一覧表

#### 表14 一般シリアルデータ機能一覧表

|             | レジスタ0                              | レジスタ1                            | レジスタ2                               | レジスタ3                       | レジスタ4~7 * <sup>6</sup><br>テストモード (使用禁止) |

|-------------|------------------------------------|----------------------------------|-------------------------------------|-----------------------------|-----------------------------------------|

| DI 00 (LSB) | Lo                                 | Hi                               | Lo                                  | Hi                          | Lo → Hi                                 |

| DI 01       | Lo                                 | Lo                               | Hi                                  | Hi                          | Lo → Hi                                 |

| DI 02       | Lo                                 | Lo                               | Lo                                  | Lo                          | Hi                                      |

| DI 03       | 使用禁止                               | SLP Lo: 通常動作モード<br>Hi: スリープモード   | Clamp-level [0] (LSB)               | PBLK-sel Lo: PBLK<br>Hi: VD |                                         |

| DI 04       | all = "L"                          | STBY Lo: 通常動作モード<br>Hi: スタンバイモード | Clamp-level [1]                     | 出力モード設定 (TEST1)             |                                         |

| DI 05       | PGA Gain設定 (LSB)                   | 出力モード設定 (LINV)                   | Clamp-level [2]                     | 出力モード設定 (TEST2)             |                                         |

| DI 06       | PGA Gain設定                         | 出力モード設定 (MINV)                   | Clamp-level [3]                     | 0 使用禁止                      |                                         |

| DI 07       | PGA Gain設定                         | 出力モード設定 (TEST0)                  | Clamp-level [4] (MSB)               | Grayts [0]                  |                                         |

| DI 08       | PGA Gain設定                         | SHA-fsel [0] (LSB)               | HGstop-Hsel [0]                     | Grayts [1]                  |                                         |

| DI 09       | PGA Gain設定                         | SHA-fsel [1] (MSB)               | HGstop-Hsel [1]                     | Grayts [2]                  | 使用禁止                                    |

| DI 10       | PGA Gain設定                         | SHSW-fsel [0] (LSB)              | HGain-Nsel [0]                      | 0                           |                                         |

| DI 11       | PGA Gain設定                         | SHSW-fsel [1]                    | HGain-Nsel [1]                      | 0                           |                                         |

| DI 12       | PGA Gain設定 (MSB)                   | SHSW-fsel [2]                    | Pwr-sel Lo: ノーマルモード<br>Hi: ローパワーモード | 1                           |                                         |

| DI 13       | LPFSEL Lo: ローパワーモード<br>Hi: ノーマルモード | SHSW-fsel [3] (MSB)              | SPinv SPSIG/SPBLK/<br>PBLK/VD 反転    | 使用禁止                        |                                         |

| DI 14       | 使用禁止                               | Hsclp-th Lo: 8LSB<br>Hi: 16LSB   | OBPinv OB <mark>P反転</mark>          | 0                           |                                         |

| DI 15 (MSB) | all = "L"                          | Hsclp-en Lo: Gain変更<br>Hi: VD    | RESET Lo: リセットモード<br>Hi: 通常動作モード    | 1                           |                                         |

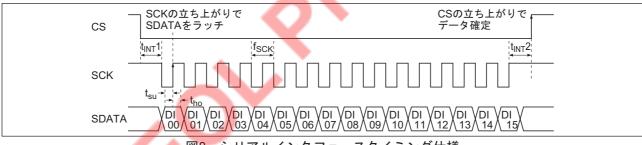

図8 シリアルインタフェースタイミング仕様

- 【注】 1. 通信は2Byte連続通信です。2. SDATAはSCKの立ち上がりでラッチして取り込みます。

- 3. SCKはCSがLoの期間中に16クロック入れてください。 4. データ送信を途中で中止した場合のデータは無効とします。

- 5. STBY: リファレンス電圧発生回路は動作状態。

- SLP: 全ての回路がスリープ状態。

- 6. このbitはICのテスト時に使用しますのでご使用になれません。 設定時は、ALL Low以外には設定しないでください。

#### タイミング仕様

| )   \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |      |      |  |  |

|-----------------------------------------|------|------|--|--|

|                                         | Min  | Max  |  |  |

| f <sub>SCK</sub>                        | _    | 5MHz |  |  |

| t <sub>INT</sub> 1, 2                   | 50ns | _    |  |  |

| t <sub>su</sub>                         | 50ns | _    |  |  |

| t <sub>ho</sub>                         | 50ns | _    |  |  |

# 電源投入時の動作シーケンス

図9 電源投入時の動作シーケンス

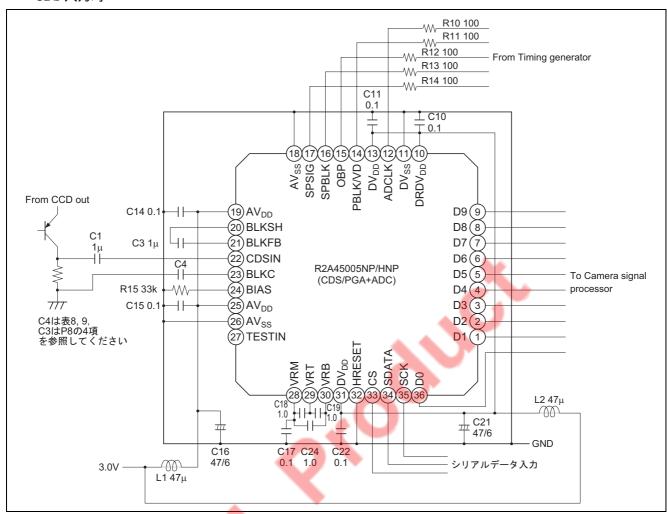

# 外付け回路例 (参考)

• CDS 入力時

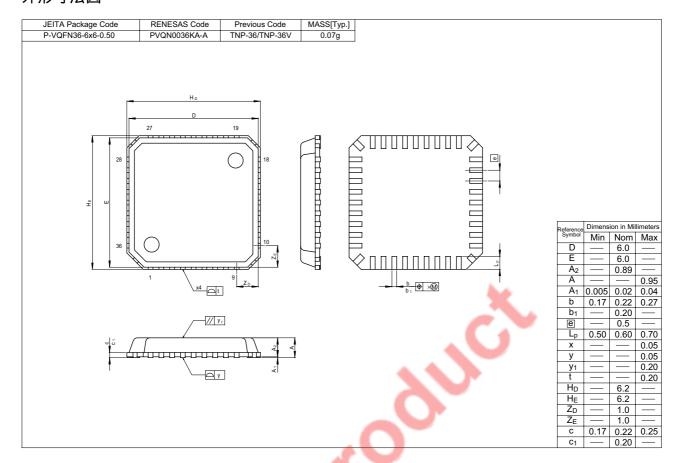

# 外形寸法図

#### 本資料ご利用に際しての留意事項

- 本資料は、お客様に用途に応じた適切な弊社製品をご購入いただくための参考資料であり、本資料中に記載の技術情報について弊社または第三者の知的財産権 その他の権利の実施、使用を許諾または保証するものではありません。 本資料に記載の製品データ、図、表、ブログラム、アルゴリズムその他応用回路例など全ての情報の使用に起因する損害、第三者の知的財産権その他の権利に 対する侵害に関し、弊社は責任を負いません。 本資料に記載の製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他軍事用途の目的で使用しないでください。また、輸出に際し

- 本資料に記載の製品のよび収削を入車板を共命の開光等の目的、車事利用の目的、あるいはていた単事用途の目的で使用しないでください。また、、輸出に除りては、「外国為替および外国貿易法」その他輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例などの全ての情報は本資料発行時点のものであり、弊社は本資料に記載した製品または仕様等を予告なしに変更することがあります。弊社の半導体製品のご購入およびご使用に当たりましては、事前に弊社営業窓口で最新の情報をご確認いただきますとともに、弊社ホームページ(http://www.renesas.com/などを通じて公開される情報に常にご注意ください。 本資料に記載した情報は、正確を期すため慎重に制作したものですが、万一本資料の記述の誤りに起因する損害がお客様に生じた場合においても、弊社はその

- 本資料に記載した情報は、止罐を期すため慎重に制作したものですが、カー本資料の記述の誤りに起因する損害がお客様に生じた場合においても、弊社はその責任を負いません。 本資料に記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの情報を流用する場合は、流用する情報を単独 で評価するだけでなく、システム全体で十分に評価し、お客様の責任において適用可否を判断してください。弊社は、適用可否に対する責任は負いません。 本資料に記載された製品は、各種安全装置や運輸・交通用、燃焼制御用、航空宇宙用、原子力、海底中継用の機器・システムなど、その故障や誤動作 が直接人命を脅かしあるいは人体に危害を及ぼすおそれのあるような機器・システムや特に高度な品質・信頼性が要求される機器・システムでの使用を意図し て設計、製造されたものではありません(弊社が自動車用と指定する製品を自動車に使用する場合を除きます)。これらの用途に利用されることをご検討の際 には、必ず事前に弊社営業窓口へご照会ください。なお、上記用途に使用されたことにより発生した損害等について弊社はその責任を負いかねますのでご了承

- 原います。 第7項にかかわらず、本資料に記載された製品は、下記の用途には使用しないでください。これらの用途に使用されたことにより発生した損害等につきましては、弊社は一切の責任を負いません。

- 任を負いません

- 12.本資料の全部または一部を弊社の文書による事前<mark>の承</mark>諾なしに転載または複製することを固くお断りいたします。 13.本資料に関する詳細についてのお問い合わせ、その<mark>他お気付きの点等</mark>がございましたら弊社営業窓口までご照会ください。

#### 営業お問合せ窓口 株式会社ルネサス販売

#### http://www.renesas.com

| 本 |     |    | 社 | 〒100-0004 | 千代田区大手町2-6-2 (日本ビル)                       | (03) 5201-5350  |

|---|-----|----|---|-----------|-------------------------------------------|-----------------|

| 西 | 東   | 京支 | 社 | 〒190-0023 | 立川市柴崎町2-2-23 (第二高島ビル)                     | (042) 524-8701  |

| 東 | 北   | 支  | 社 | 〒980-0013 | 仙台市青葉区花京院1-1-20 (花京院スクエア)                 | (022) 221-1351  |

| い | わ き | き支 | 店 | 〒970-8026 | いわき市平宇田町120番地ラトブ                          | (0246) 22-3222  |

| 茨 | 城   | 支  | 店 | 〒312-0034 | ひたちなか市堀口832-2 (日立システムプラザ勝田)               | (029) 271-9411  |

| 新 | 潟   | 支  | 店 | 〒950-0087 | 新潟市東大通1-4-2 (新潟三井物産ビル)                    | (025) 241-4361  |

| 松 | 本   | 支  | 社 | 〒390-0815 | 松本市深志1-2-11 (昭和ビル)                        | (0263) 33-6622  |

| 中 | 部   | 支  | 社 | ₹460-0008 | 名古屋市中区栄4-2-29 (名古屋広小路プレイス)                | (052) 249-3330  |

| 関 | 西   | 支  | 社 | 〒541-0044 | 大阪市中央区伏見町4-1-1 (明治安田生命大阪御堂筋ビル)            | (06) 6233-9500  |

| 北 | 陸   | 支  | 社 | 〒920-0031 | 金沢市広岡3-1-1 (金沢パークビル)                      | (076) 233-5980  |

| 鳥 | 取   | 支  | 店 | 〒680-0822 | 鳥取市今町2-251 (日本生命鳥取駅前ビル)                   | (0857) 21-1915  |

| 広 | 島   | 支  | 店 | 〒730-0036 | 広島市中区袋町5-25 (広島袋町ビルディング)                  | (082) 244-2570  |

| 九 | 州   | 支  | 社 | 〒812-0011 | 福岡市博多区博多駅前2-17-1 (博多プレステージ)               | (092) 481-7695  |

|   |     |    |   | 営業お問      | 引い合わせ窓口の住所・電話番号は変更になることがあります。最新情報につきましては. | 弊計ホームページをご覧ください |

■技術的なお問合せおよび資料のご請求は下記へどうぞ。

総合お問合せ窓口: コンタクトセンタ E-Mail: csc@renesas.com