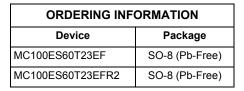

**DATASHEET**

# 3.3 V Dual Differential LVPECL to **LVTTL Translator**

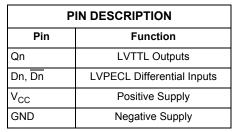

The MC100ES60T23 is a dual differential LVPECL-to-LVTTL translator. The low voltage PECL levels, small package, and dual gate design is ideal for clock translation applications.

#### **Features**

- Maximum Frequency 500 MHz

- **Differential LVPECL Inputs**

- LVPECL Operating Range: V<sub>CC</sub> = 3.0 V to 3.6 V

- Additive Phase Jitter, RMS: 0.18ps (typical)

- 24 mA LVTTL Compatible Outputs

- 8-Lead SOIC Package

- Ambient Temperature Range: -40°C to +85°C

- 8-Lead Pb-Free Package

- Use replacement part: ICS83023I

**Table 1. General Specifications**

| Characteristic                                         | Value                              |                   |

|--------------------------------------------------------|------------------------------------|-------------------|

| Internal Input Pulldown Resistor                       | <u>D</u>                           | 75 kΩ<br>112.5 kΩ |

| Internal Input Pullup Resistors                        |                                    | 75 kΩ             |

| ESD Protection                                         | Human Body Model<br>Machine Model  |                   |

| $\theta_{JA}$ Thermal Resistance (Junction to Ambient) | 0 LFPM, 8 SOIC<br>500 LFPM, 8 SOIC |                   |

Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test

Table 2. Absolute Maximum Ratings<sup>(1)</sup>

| Symbol              | Parameter                   | Conditions                                             | Rating                                         | Unit     |

|---------------------|-----------------------------|--------------------------------------------------------|------------------------------------------------|----------|

| V <sub>SUPPLY</sub> | Power Supply Voltage        | Difference between V <sub>CC</sub> and V <sub>EE</sub> | 3.9                                            | V        |

| V <sub>IN</sub>     | Input Voltage               | $V_{CC}$ – $V_{EE} \le 3.6 \text{ V}$                  | V <sub>CC</sub> + 0.3<br>V <sub>EE</sub> - 0.3 | V<br>V   |

| I <sub>OUT</sub>    | Output Current              | Continuous<br>Surge                                    | 50<br>100                                      | mA<br>mA |

| T <sub>A</sub>      | Operating Temperature Range |                                                        | -40 to +85                                     | °C       |

| T <sub>STG</sub>    | Storage Temperature Range   |                                                        | -65 to +150                                    | °C       |

<sup>1.</sup> Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied.

Table 3. LVPECL Input DC Characteristics ( $V_{CC}$  = 3.0 to 3.6 V;  $V_{EE}$  = 0 V); TA = 40°C to 85°C

| Symbol           | Characteristic                                  | Min                   | Тур | Max                   | Unit |

|------------------|-------------------------------------------------|-----------------------|-----|-----------------------|------|

| I <sub>CCH</sub> | Power Supply Current (Outputs set to HIGH)      |                       | 19  | 25                    | mA   |

| I <sub>CCL</sub> | Power Supply Current (Outputs set to LOW)       |                       | 6.0 | 33                    | mA   |

| V <sub>IH</sub>  | Input HIGH Voltage                              | V <sub>CC</sub> -1165 |     | V <sub>CC</sub> -880  | mV   |

| V <sub>IL</sub>  | Input LOW Voltage                               | V <sub>CC</sub> -1810 |     | V <sub>CC</sub> -1475 | mV   |

| V <sub>PP</sub>  | Differential Input Voltage <sup>(1)</sup>       | 0.15                  |     | 1.3                   | V    |

| V <sub>CMR</sub> | Differential Cross Point Voltage <sup>(2)</sup> | V <sub>EE</sub> +1.1  |     | V <sub>CC</sub> -0.65 | V    |

| I <sub>IH</sub>  | Input HIGH Current                              |                       |     | 150                   | μA   |

| I <sub>IL</sub>  | Input LOW Current                               | -150                  |     |                       | μΑ   |

<sup>1.</sup>  $V_{PP}$  (DC) is the minimum differential input voltage swing required to maintain device functionality.

<sup>2.</sup> V<sub>CMR</sub> (DC) is the crosspoint of the differential input signal. Functional operation is obtained when the crosspoint is within the V<sub>CMR</sub> (DC) range and the input swing lies within the V<sub>PP</sub> (DC) specification.

Table 4. LVTTL / LVCMOS Output DC Characteristics ( $V_{CC}$  = 3.0 to 3.6 V); TA = 40°C to 85°C

| Symbol          | Characteristic               | Condition                | Min  | Тур  | Max  | Unit |

|-----------------|------------------------------|--------------------------|------|------|------|------|

| V <sub>OH</sub> | Output HIGH Voltage          | I <sub>OH</sub> = -24 mA | 2.4  |      |      | V    |

| V <sub>OL</sub> | Output LOW Voltage           | I <sub>OL</sub> = 24 mA  |      |      | 0.5  | V    |

| Ios             | Output Short Circuit Current |                          | -140 | -185 | -275 | mA   |

Table 5. AC Characteristics (V<sub>CC</sub> = 3.0 to 3.6 V; V<sub>EE</sub> = 0 V)<sup>(1)</sup>; TA = 40°C to 85°C

| Symbol                                                               | Characteristic                                                                                                           |                                          | Test Conditions                                                                                        | Min                  | Тур                          | Max                      | Unit                 |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------|------------------------------|--------------------------|----------------------|

| f <sub>OUT</sub>                                                     | Output Toggle Frequency <sup>(2)</sup>                                                                                   |                                          |                                                                                                        |                      |                              | 500                      | MHz                  |

| t <sub>PD</sub>                                                      | Propagation Delay                                                                                                        |                                          |                                                                                                        | 0.95                 |                              | 1.75                     | ns                   |

| t <sub>SK++</sub> t <sub>SK</sub> t <sub>SKPP</sub> t <sub>SKP</sub> | Data Path Skew++ <sup>(3)</sup> Data Path Skew <sup>(3)</sup> Part-to-Part Skew <sup>(3)</sup> Pulse Skew <sup>(3)</sup> |                                          |                                                                                                        |                      |                              | 120<br>140<br>500<br>250 | ps<br>ps<br>ps<br>ps |

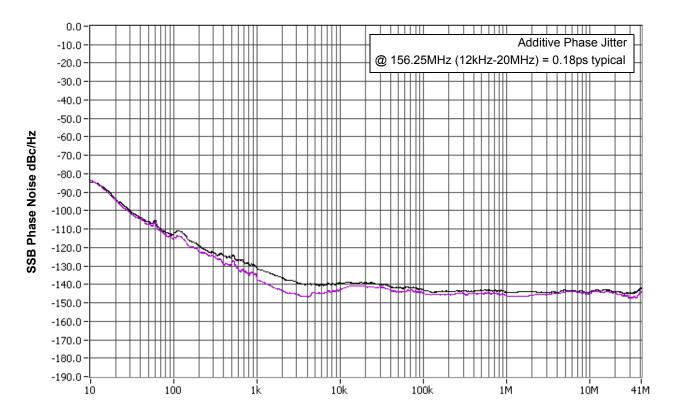

| t <sub>JIT</sub>                                                     | Buffer Additive Phase Jitter, RMS; refer to Additive Phase Jitter Section                                                | CLK0/Q0<br>CLK0/Q0<br>CLK1/Q1<br>CLK1/Q1 | 125MHz, 12kHz - 20MHz<br>156.25MHz, 12kHz - 20MHz<br>125MHz, 12kHz - 20MHz<br>156.25MHz, 12kHz - 20MHz |                      | 0.40<br>0.18<br>0.38<br>0.21 |                          | ps<br>ps<br>ps<br>ps |

| V <sub>PP</sub>                                                      | Input Voltage Swing (Differential) <sup>(4)</sup>                                                                        |                                          |                                                                                                        | 200                  |                              | 1300                     | mV                   |

| V <sub>CMR</sub>                                                     | Differential Cross Point Voltage                                                                                         |                                          |                                                                                                        | V <sub>EE</sub> +1.2 |                              | V <sub>CC</sub> -0.3     | V                    |

| t <sub>r</sub> / t <sub>f</sub>                                      | Output Rise/Fall Times (0.8 V – 2.0 V)                                                                                   |                                          |                                                                                                        | 50                   |                              | 250                      | ps                   |

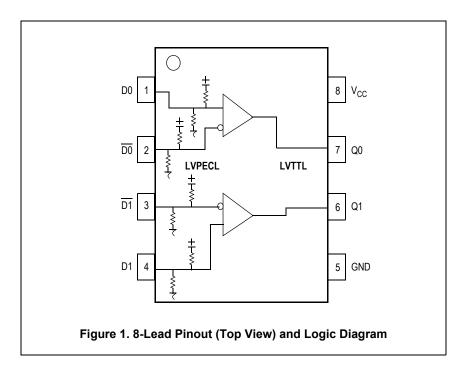

- 1. LVTTL output R<sub>L</sub> = 500  $\Omega$  to GND and C<sub>L</sub> = 20 pF to GND. Refer to Figure 2.

- 2.  $f_{max}$  guaranteed for functionality only.  $V_{OL}$  and  $V_{OH}$  levels are guaranteed at DC only. 3. Skews are measured between outputs under identical conditions.

- 4. 200 mV input guarantees AC Characteristics.

#### **CHARACTERISTIC TEST**

\*C<sub>L</sub> includes fixtures capacitance

Figure 2. TTL Output Loading Used for Device Evaluation

#### ADDITIVE PHASE JITTER

The spectral purity in a band at a specific offset from the fundamental compared to the power of the fundamental is called the dBc Phase Noise. This value is normally expressed using a Phase noise plot and is most often the specified plot in many applications. Phase noise is defined as the ratio of the noise power present in a 1Hz band at a specified offset from the fundamental frequency to the power value of the fundamental. This ratio is expressed in decibels (dBm) or a ratio of the power in the 1Hz band to the power in the

fundamental. When the required offset is specified, the phase noise is called a dBc value, which simply means dBm at a specified offset from the fundamental. By investigating jitter in the frequency domain, we get a better understanding of its effects on the desired application over the entire time record of the signal. It is mathematically possible to calculate an expected bit error rate given a phase noise plot.

Offset From Carrier Frequency (Hz)

As with most timing specifications, phase noise measurements have issues. The primary issue relates to the limitations of the equipment. Often the noise floor of the equipment is higher than the noise floor of the device. This is

illustrated above. The device meets the noise floor of what is shown, but can actually be lower. The phase noise is dependant on the input source and measurement equipment.

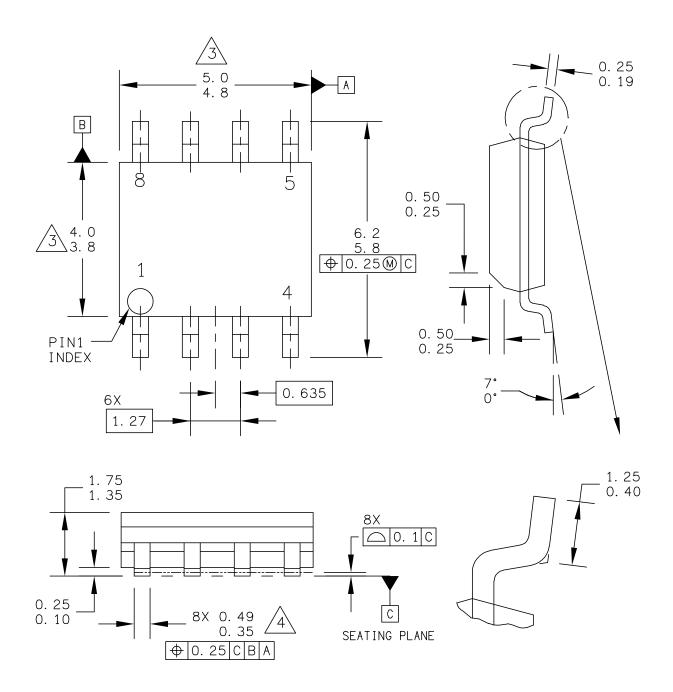

#### **PACKAGE DIMENSIONS**

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.  MECHANICA |      | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|-----------------------------------------------------------------|------|--------------|------------------|-------------|

| TITLE:                                                          |      | DOCUMENT NO  | ): 98ASB42564B   | REV: U      |

| 8LD SOIC NARROW                                                 | BODY | CASE NUMBER  | 2: 751–07        | 07 APR 2005 |

|                                                                 |      | STANDARD: JE | IDEC MS-012AA    |             |

PAGE 1 OF 2

CASE 751-07 ISSUE U 8-LEAD SOIC PACKAGE

## **Revision History Sheet**

#### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

3) DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 TOTAL IN EXCESS OF THE DIMENSION AT MAXIMUM MATERIAL CONDITION.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:                                               |           | DOCUMENT NO  | ): 98ASB42564B   | REV: U      |

| 8LD SOIC NARROW                                      | BODY      | CASE NUMBER  | R: 751–07        | 07 APR 2005 |

|                                                      |           | STANDARD: JE | DEC MS-012AA     |             |

**CASE 751-07 ISSUE U 8-LEAD SOIC PACKAGE**  PAGE 2 OF 2

| Rev | Table | Page | Description of Change                                                                             | Date     |

|-----|-------|------|---------------------------------------------------------------------------------------------------|----------|

| 10  |       | 1    | Product Discontinuance Notice - Last Time Buy Expires on (2/3/13) Use replacement part: ICS83023I | 12/14/12 |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.