### **ISL8278M**

Digital DC/DC PMBus 33A Module

FN8924 Rev.1.00 Aug 17, 2017

The <u>ISL8278M</u> is a 33A step-down, DC/DC power supply module with an integrated digital PWM controller, synchronous power switches, an inductor, and passives. Only bulk input and output capacitors are needed to finish the design. The 33A of continuous output current can be delivered without the need for airflow or a heatsink. The thermally enhanced HDA module is capable of dissipating heat directly into the PCB.

The ISL8278M uses ChargeMode™ control architecture, which responds to a transient load within a single switching cycle. The ISL8278M comes with a preprogrammed configuration for operating in a pin-strap mode. Output voltage, switching frequency, and the device SMBus address can be programmed with external resistors. More configurations, such as soft-start and fault limits can be easily programmed or changed using a PMBus compliant serial bus interface. PMBus can be used to monitor voltages, current, temperatures, and fault status. The ISL8278M is supported by the PowerNavigator™ software, a Graphical User Interface (GUI) that can be used to configure modules for a desired solution.

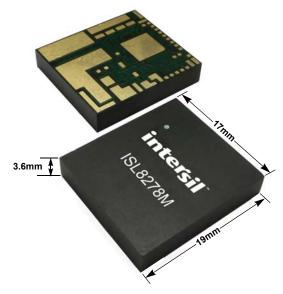

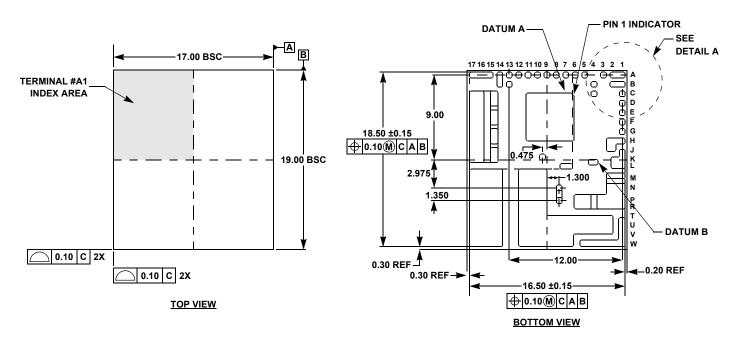

The ISL8278M is available in a 41 Ld compact 17mmx19mm HDA module with a very low profile height of 3.6mm, suitable for automated assembly by standard surface mount equipment. The ISL8278M is RoHS compliant by exemption.

### **Features**

- · Complete digital switch-mode power supply

- Wide VIN range: 4.5V to 14V

- Programmable VOUT range: 0.6V to 5V

- PMBus compliant I<sup>2</sup>C communication interface

- Programmable V<sub>OUT</sub>, margining, UV/OV, I<sub>OUT</sub> limit, soft-start/stop, sequencing, and external synchronization

- Monitor: V<sub>IN</sub>, V<sub>OUT</sub>, I<sub>OUT</sub>, temperature, duty cycle, switching frequency, and faults

- · ChargeMode control architecture

- ±1.0% V<sub>OUT</sub> accuracy over line, load, and temperature

- Power-good indicator

- · Over-temperature protection

- · Internal nonvolatile memory and fault logging

- · Patented thermally enhanced HDA package

- · Intuitive configuration using PowerNavigator

## Applications

- · Server, telecom, storage, and datacom

- · Industrial/ATE and networking equipment

- · General purpose power for ASIC, FPGA, DSP, and memory

### **Related Literature**

- · For a full list of related documents, visit our website

- ISL8278M product page

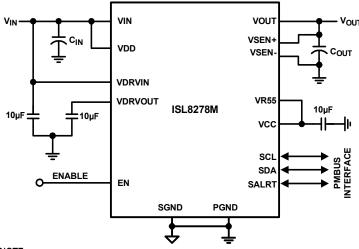

NOTE:

1. Only bulk input and output capacitors are required to finish the design.

FIGURE 1. A COMPLETE DIGITAL SWITCH-MODE POWER SUPPLY

FIGURE 2. A SMALL PACKAGE FOR HIGH POWER DENSITY

# **Table of Contents**

| Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                             | . 4                                                                              |

| Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                              | . 4                                                                              |

| ISL8278M Internal Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                               | . 6                                                                              |

| Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                      | . 7                                                                              |

| Thermal Information                                                                                                                                                                                                                                                                                                                                                                                                                           | . 7                                                                              |

| Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                              | . 7                                                                              |

| Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                     | . 7                                                                              |

| Typical Performance Curves                                                                                                                                                                                                                                                                                                                                                                                                                    | 10                                                                               |

| Efficiency PerformanceTransient Response Performance                                                                                                                                                                                                                                                                                                                                                                                          | 11                                                                               |

| Typical Application Circuit                                                                                                                                                                                                                                                                                                                                                                                                                   | 14                                                                               |

| Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                        | 16                                                                               |

| SMBus Communications. Output Voltage Selection Soft-Start Delay and Ramp Times. Power-Good Switching Frequency and PLL Loop Compensation Input Undervoltage Lockout (UVLO). SMBus Module Address Selection Output Overvoltage Protection Output Prebias Protection Output Prebias Protection Thermal Overload Protection Digital-DC Bus Phase Spreading Output Sequencing Fault Spreading Monitoring Through SMBus Snapshot Parameter Capture | 16<br>17<br>17<br>17<br>18<br>18<br>19<br>20<br>20<br>20<br>20<br>20<br>20<br>20 |

| Nonvolatile Memory                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

| Thermal Considerations                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

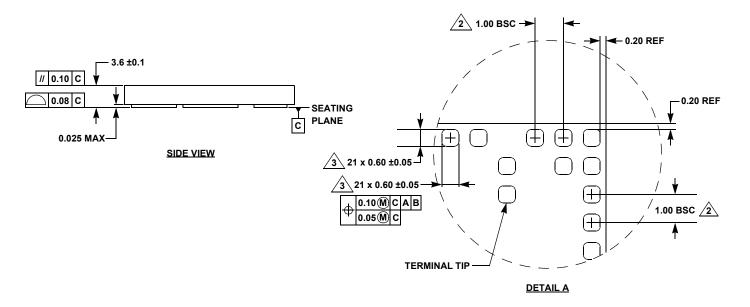

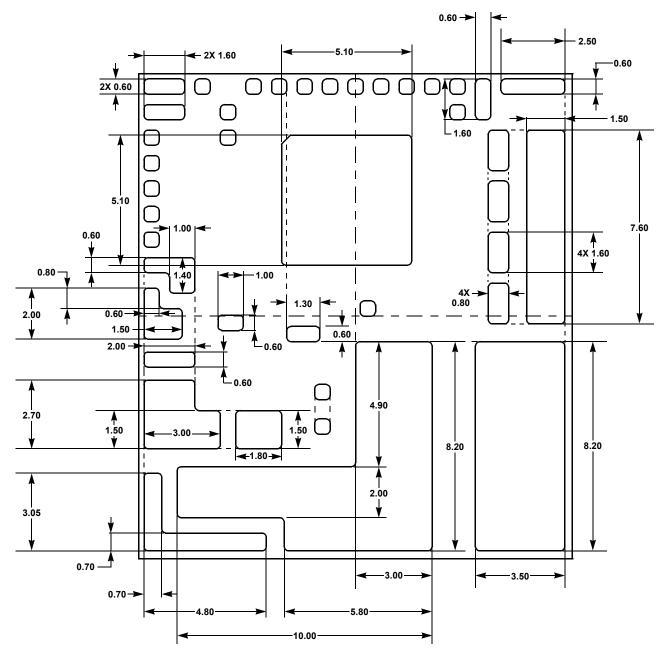

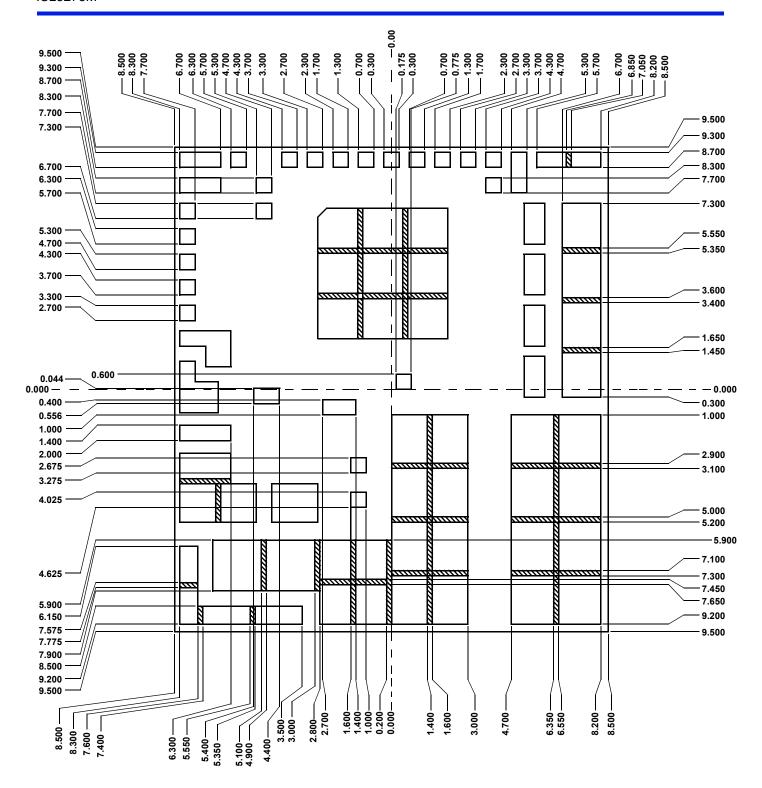

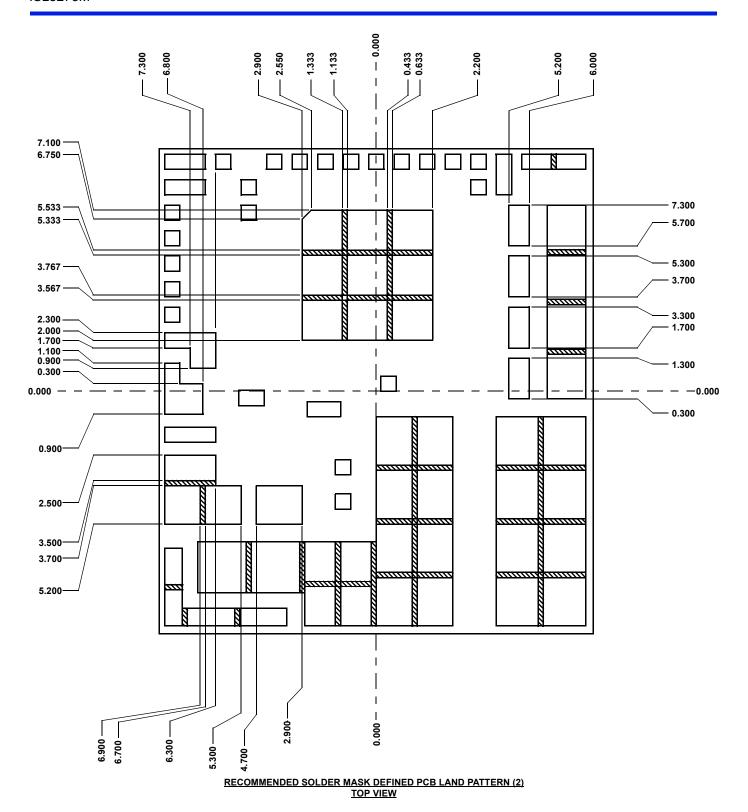

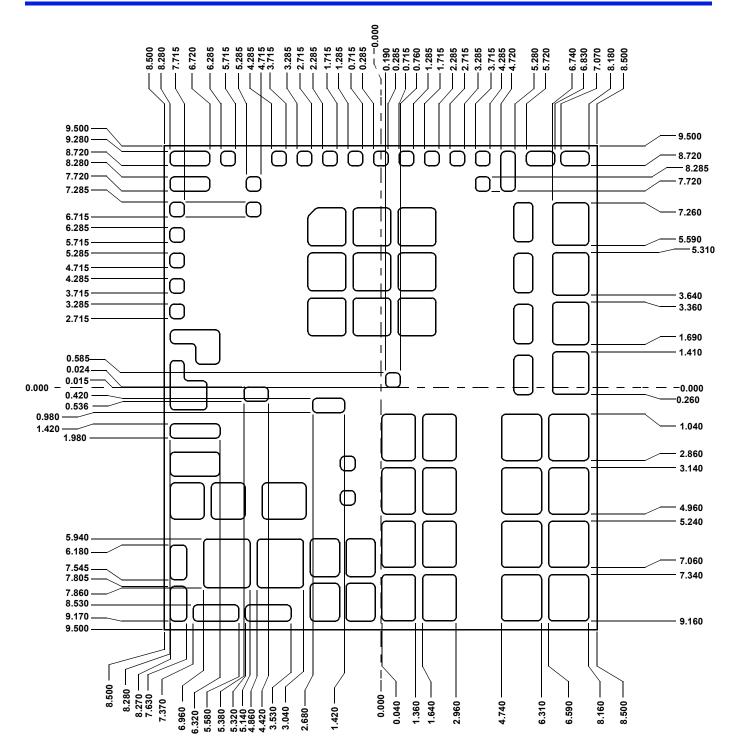

| Package Description PCB Layout Pattern Design Thermal Vias. Stencil Pattern Design Reflow Parameters                                                                                                                                                                                                                                                                                                                                          | 22<br>22<br>22<br>22                                                             |

| PMBus Command Summary                                                                                                                                                                                                                                                                                                                                                                                                                         | 23                                                                               |

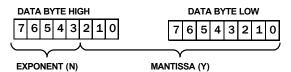

| PMBus Data Formats                                                                                                                                                                                                                                                                                                                                                                                                                            | 27                                                                               |

| PMBus Use Guidelines  Summary  PMBus Commands Description                                                                                                                                                                                                                                                                                                                                                                                     | 27                                                                               |

| Datasheet Revision History                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

| Firmware Revision History                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| About Intersil                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| Package Outline Drawing                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>50</b>                                                                        |

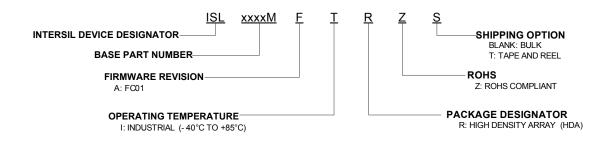

## **Ordering Information**

| PART NUMBER<br>(Notes 2, 3, 4) | PART TEMP RANGE MARKING (°C) |            | PACKAGE<br>(Rohs Compliant) | PKG.<br>DWG. # |  |

|--------------------------------|------------------------------|------------|-----------------------------|----------------|--|

| ISL8278MAIRZ                   | ISL8278MA                    | -40 to +85 | 41 Ld 17x19 HDA             | Y41.17x19      |  |

| ISL8278MEVAL1Z                 | Evaluation Board             |            |                             |                |  |

#### NOTES:

- 2. Add "-T" suffix for 500 unit or "-T1" suffix for 100 unit tape and reel options. Refer to TB347 for details on reel specifications.

- 3. These Intersil Pb-free plastic packaged products are RoHS compliant by EU exemption 7C-I and 7A. They employ special Pb-free material sets; molding compounds/die attach materials and NiPdAu plate-e4 termination finish, which is compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 4. For Moisture Sensitivity Level (MSL), please see the product information page for ISL8278M. For more information on MSL, see TB363.

**TABLE 1. TABLE OF DIFFERENCES AMONG THE FAMILY OF PARTS**

| PARAMETERS                  | ISL8278M | ISL8271M | ISL8270M | ISL8277M |

|-----------------------------|----------|----------|----------|----------|

| V <sub>IN</sub> (min) (V)   | 4.5      | 4.5      | 4.5      | 4.5      |

| V <sub>IN</sub> (max) (V)   | 14       | 14       | 14       | 14       |

| V <sub>OUT</sub> (min) (V)  | 0.6      | 0.6      | 0.6      | 0.6      |

| V <sub>OUT</sub> (max) (V)  | 5        | 5        | 5        | 5        |

| I <sub>OUT</sub> (max) (A)  | 33       | 33       | 25       | 25       |

| I <sub>Q</sub> (mA)         | 40       | 40       | 40       | 40       |

| Peak Efficiency (%)         | 96       | 96       | 96       | 96       |

| POR                         | Yes      | Yes      | Yes      | Yes      |

| Switching Freq. (min) (MHz) | 0.296    | 0.296    | 0.296    | 0.296    |

| Switching Freq. (max) MHz   | 1.067    | 1.067    | 1.067    | 1.067    |

| Control Type                | Digital  | Digital  | Digital  | Digital  |

| SYNCH Capability            | Yes      | Yes      | Yes      | Yes      |

| Current Sharing             | No       | No       | No       | No       |

| Tracking                    | No       | No       | No       | No       |

| Digital                     | Yes      | Yes      | Yes      | Yes      |

| Qualification Level         | Standard | Standard | Standard | Standard |

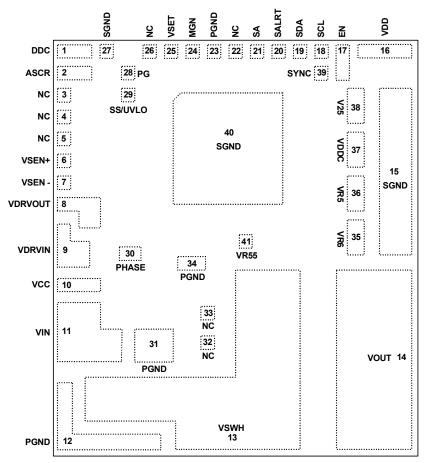

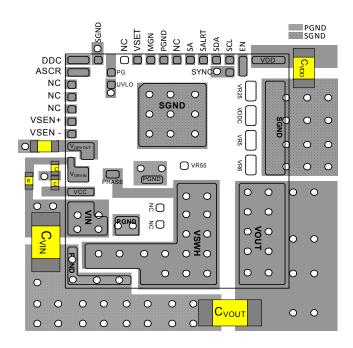

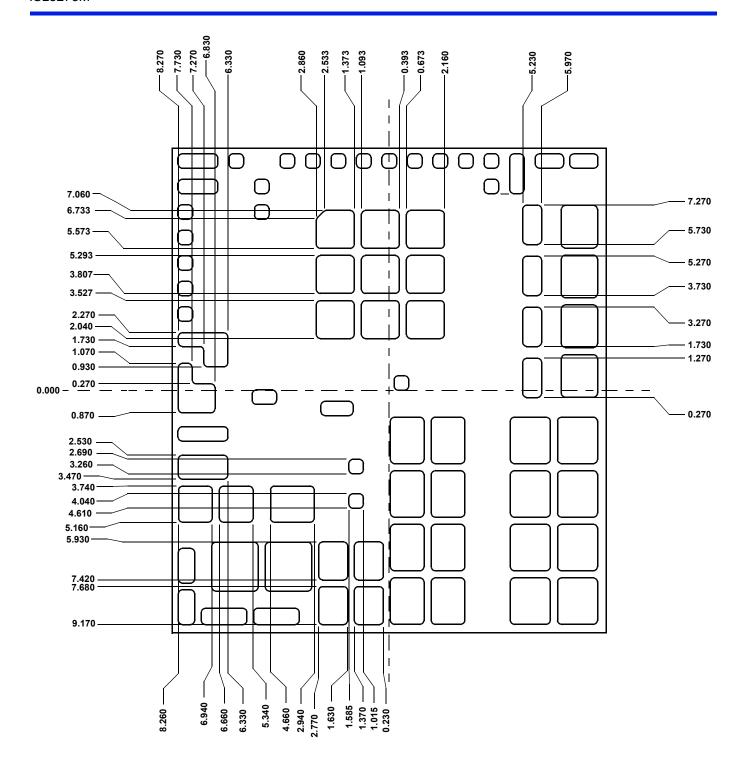

# **Pin Configuration**

ISL8278M (41 LD HDA) TOP VIEW

# **Pin Descriptions**

| PIN | LABEL   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                        |

|-----|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | DDC     | I/O  | A Digital-DC <sup>TM</sup> bus. This dedicated bus provides the communication channel between devices for features such as sequencing and fault spreading. The DDC pin on all Digital-DC devices should be connected together. A pull-up resistor is required for this application.                                                                |

| 2   | ASCR    | ı    | ChargeMode control ASCR parameters selection pin. Used to set ASCR gain and residual values.                                                                                                                                                                                                                                                       |

| 6   | VSEN+   | ı    | Differential output voltage sense feedback. Connect to the positive output regulation point.                                                                                                                                                                                                                                                       |

| 7   | VSEN-   | 1    | Differential output voltage sense feedback. Connect to the negative output regulation point.                                                                                                                                                                                                                                                       |

| 8   | VDRVOUT | PWR  | Output of internal regulator for powering internal MOSFET driver. Connect a 10µF bypass capacitor to this pin. The regulator output is dedicated to powering internal MOSFET drivers. Do not use this regulator for any other purpose. For applications with V <sub>IN</sub> less than 5.2V, use an external 5V supply or connect this pad to VIN. |

| 9   | VDRVIN  | PWR  | Input supply to internal regulator for powering internal MOSFET drivers. Connect this pad to VIN.                                                                                                                                                                                                                                                  |

| 10  | vcc     | PWR  | Bias pin for internal regulator. Connect VCC pad to VR55 pin directly with a short loop trace. Not recommended to power external circuit.                                                                                                                                                                                                          |

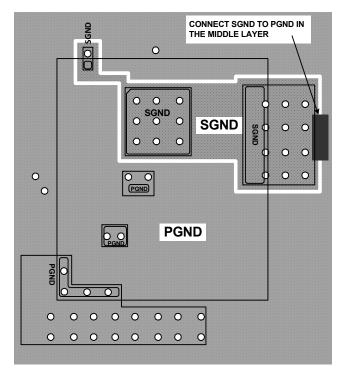

| 11  | VIN     | PWR  | Main input supply. Refer to <u>"PCB Layout Guidelines" on page 21</u> for the decoupling capacitors placement from VIN to PGND.                                                                                                                                                                                                                    |

# Pin Descriptions (Continued)

| PIN                        | LABEL   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12, 23, 31,<br>34          | PGND    | PWR  | Power ground. Refer to <u>"PCB Layout Guidelines" on page 21</u> for the PGND pad connections and decoupling capacitors placement.                                                                                                                                                                                                                                                                        |

| 13                         | VSWH    | PWR  | Switch node. Refer to "PCB Layout Guidelines" on page 21 for connecting VSWH pads to electrically isolated PCB copper island to dissipate internal heat.                                                                                                                                                                                                                                                  |

| 14                         | VOUT    | PWR  | Power supply output. Range: 0.6V to 5V. Refer to "Derating Curves" on page 12 for maximum recommended output current at various output voltages.                                                                                                                                                                                                                                                          |

| 15, 27, 40                 | SGND    | PWR  | Controller signal ground. Refer to "PCB Layout Guidelines" on page 21 for the SGND pad connections.                                                                                                                                                                                                                                                                                                       |

| 16                         | VDD     | PWR  | Input supply to digital controller. Connect VDD pad to VIN supply. Refer to <u>"PCB Layout Guidelines" on page 21</u> for the decoupling capacitors placement from VDD to SGND.                                                                                                                                                                                                                           |

| 17                         | EN      | ı    | External enable input. Logic high enables the module.                                                                                                                                                                                                                                                                                                                                                     |

| 18                         | SCL     | I/O  | Serial clock input. A pull-up resistor is required for this application.                                                                                                                                                                                                                                                                                                                                  |

| 19                         | SDA     | I/O  | Serial data. A pull-up resistor is required for this application.                                                                                                                                                                                                                                                                                                                                         |

| 20                         | SALRT   | 0    | Serial alert. A pull-up resistor is required for this application.                                                                                                                                                                                                                                                                                                                                        |

| 21                         | SA      | ı    | Serial bus address select pin. Refer to <u>Table 9 on page 18</u> for list of resistor values to set various serial bus address.                                                                                                                                                                                                                                                                          |

| 24                         | MGN     | I    | External V <sub>OUT</sub> margin control pin. Active high (>2V) signal at this pin sets V <sub>OUT</sub> margin high, active low (<0.8V) sets V <sub>OUT</sub> margin low, and high impedance (float) will bring V <sub>OUT</sub> back to nominal voltage. Factory default range for margining is nominal V <sub>OUT</sub> ±5%. When using PMBus to control margin command, leave this pin as no connect. |

| 25                         | VSET    | I    | Output voltage selection pin. Refer to <u>Table 4 on page 16</u> for list of resistor values to set various output voltages.                                                                                                                                                                                                                                                                              |

| 28                         | PG      | 0    | Power-good output. Power-good output can be an open drain that requires pull-up resistor or push-pull output that can drive a logic input.                                                                                                                                                                                                                                                                |

| 29                         | SS/UVLO | 1    | Soft-start/stop and undervoltage lockout selection pin. Used to set turn on/off delay and ramp time as well as input UVLO threshold levels. Refer to <u>Table 5 on page 17</u> and <u>Table 8 on page 18</u> for list of resistors.                                                                                                                                                                       |

| 30                         | PHASE   | PWR  | Switch node pad for DCR sensing. Electrically shorted inside to VSWH, but for higher current sensing accuracy connect PHASE pad to VSWH pad externally. Refer to <u>"PCB Layout Guidelines" on page 21</u> .                                                                                                                                                                                              |

| 35                         | VR6     | PWR  | 6V internal reference supply voltage.                                                                                                                                                                                                                                                                                                                                                                     |

| 36                         | VR5     | PWR  | 5V internal reference supply voltage.                                                                                                                                                                                                                                                                                                                                                                     |

| 37                         | VDDC    | PWR  | VDD clean. Noise at the VDD pin is filtered by an internal ferrite bead and capacitor. For VDD > 6V, leave this pin as no connect. For $5.5 \le VDD \le 6V$ , connect the VDDC pin to VR6 pin. For $4.5 \le VDD < 5.5V$ , connect the VDDC pin to VR6 and the VR5 pin.                                                                                                                                    |

| 38                         | V25     | PWR  | 2.5V internal reference supply voltage.                                                                                                                                                                                                                                                                                                                                                                   |

| 39                         | SYNC    | I/O  | The SYNC pin can be input to external clock for frequency synchronization or output to supply clock signal to other modules for synchronization. Refer to <a href="Table 6">Table 6</a> on page 17 for list of resistor values to program various switching frequencies.                                                                                                                                  |

| 41                         | VR55    | PWR  | Internal 5.5V bias for internal regulator use only. Connect VR55 pin directly to VCC pin. Not recommended to power external circuit.                                                                                                                                                                                                                                                                      |

| 3, 4, 5, 22,<br>26, 32, 33 | NC      |      | These are test pins and are not electrically isolated. Leave these pins as no connect.                                                                                                                                                                                                                                                                                                                    |

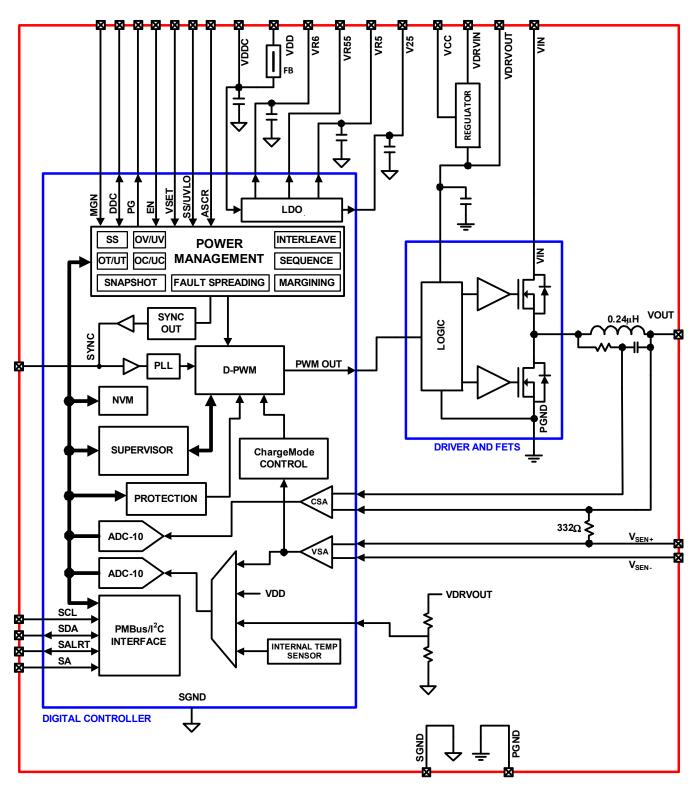

## **ISL8278M Internal Block Diagram**

FIGURE 3. ISL8278M INTERNAL BLOCK DIAGRAM

### **Absolute Maximum Ratings**

| Input Supply Voltage, VIN Pin                                     |

|-------------------------------------------------------------------|

| Input Supply Voltage for Controller, VDD, VDDC Pin0.3V to 17V     |

| Input Gate Driver Supply Voltage, VDRVIN Pin0.3V to 17V           |

| Output Gate Driver Supply Voltage, VDRVOUT Pin0.3V to 6V          |

| Output Voltage, VOUT Pin0.3V to 6.0V                              |

| Switch Node Referenced to PGND Pin, VSWH Pin0.3V to 25V           |

| Switch Node for DCR Sensing Referenced to                         |

| SGND Pin, PHASE Pin0.3V to 25V                                    |

| Input Bias Voltage for Internal Regulator, VCC Pin0.3V to 6.5V    |

| 6V Internal Reference Supply Voltage, VR6 Pin0.3V to 6.6V         |

| Internal Reference Supply Voltage, VR5, VR55 Pin0.3V to 6.5V      |

| 2.5V Internal Reference Supply Voltage, V25 Pin0.3V to 3V         |

| Logic I/O Voltage for DDC, EN, MGN, PG, ASCR,                     |

| SA, SCL, SDA, SALRT, SYNC, SS/UVLO, V <sub>SET</sub> 0.3V to 6.0V |

| Analog Input Voltages for                                         |

| V <sub>SEN+</sub> , X <sub>TEMP+</sub>                            |

| V <sub>SEN-</sub> , X <sub>TEMP-</sub>                            |

| ESD Rating                                                        |

| Human Body Model (Tested per JS-001-2014)2000V                    |

| Machine Model (Tested per JESD22-A115C) 200V                      |

| Charged Device Model (Tested per JS-002-2014)                     |

| Latch-Up (Tested per JESD78E; Class 2, Level A)                   |

|                                                                   |

### **Thermal Information**

| Thermal Resistance (Typical)              | $\theta_{JA}$ (°C/W)  | $\theta_{JC}$ (°C/W) |

|-------------------------------------------|-----------------------|----------------------|

| 41 LD HDA Package (Notes 5, 6)            | 7.5                   | 2.2                  |

| Maximum Junction Temperature (Plastic Pac | kage)                 | +125°C               |

| Storage Temperature Range                 |                       | 5°C to +150°C        |

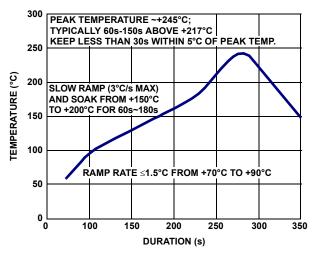

| Pb-Free Reflow Profile                    | efer to <u>Figure</u> | 31 on page 22        |

### **Recommended Operating Conditions**

| 4.5V to 14V |

|-------------|

| 4.5V to 14V |

| 0.6V to 5V  |

| 0A to 33A   |

| C to +125°C |

|             |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- θ<sub>JA</sub> is measured in free air with the module mounted on an evaluation board 3x4.5 inch in size with 2oz surface and 2oz buried planes and multiple via interconnects as specified in "ISL8278MEVAL12 Evaluation Board User Guide", on the <u>ISL8278M</u> product page.

- 6. For  $\theta_{\mbox{\scriptsize JC}},$  the "case temp" location is the center of the package underside.

**Electrical Specifications**  $V_{IN} = V_{DD} = 12V$ ,  $f_{SW} = 533$ kHz,  $C_{OUT} = 1340 \mu F$ ,  $T_A = -40 \,^{\circ}$ C to  $+85 \,^{\circ}$ C, unless otherwise noted. Typical values are at  $T_A = +25 \,^{\circ}$ C. Boldface limits apply across the operating temperature range,  $-40 \,^{\circ}$ C to  $+85 \,^{\circ}$ C.

| PARAMETER                                                                       | SYMBOL                    | TEST CONDITIONS                                                                                | MIN<br>(Note 7) | TYP    | MAX<br>( <u>Note 7</u> ) | UNIT |

|---------------------------------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------|-----------------|--------|--------------------------|------|

| INPUT AND SUPPLY CHARACTERISTICS                                                |                           |                                                                                                |                 |        | 1                        | l    |

| Input Supply Current for Controller                                             | I <sub>DD</sub>           | $V_{IN} = V_{DD} = 12V$ , $V_{OUT} = 0V$ , module not enabled                                  |                 | 40     | 50                       | mA   |

| 6V Internal Reference Supply Voltage                                            | V <sub>R6</sub>           |                                                                                                | 5.5             | 6.1    | 6.6                      | V    |

| Internal Regulator Output Voltage                                               | V <sub>DRVOUT</sub>       | V <sub>CC</sub> connected to V <sub>R55</sub>                                                  |                 | 5.2    |                          | V    |

| 5V Internal Reference Supply Voltage                                            | V <sub>R5</sub>           | I <sub>VR5</sub> < 5mA                                                                         | 4.5             | 5.2    | 5.5                      | ٧    |

| 2.5V Internal Reference Supply Voltage                                          | V <sub>25</sub>           |                                                                                                | 2.25            | 2.50   | 2.75                     | V    |

| 5.5V Internal Reference Supply Voltage                                          | V <sub>R55</sub>          | V <sub>DD</sub> > 6V; 0A to 80mA                                                               |                 | 5.7    |                          | V    |

| Input Supply Voltage for Controller<br>Read Back Resolution                     | V <sub>DD_READ_RES</sub>  |                                                                                                |                 | 10     |                          | Bits |

| Input Supply Voltage for Controller<br>Read Back Total Error ( <u>Note 10</u> ) | V <sub>DD_READ_ERR</sub>  | PMBus read                                                                                     |                 | ±2     |                          | %FS  |

| OUTPUT CHARACTERISTICS                                                          |                           |                                                                                                |                 | 1      | 1                        | 1    |

| Output Voltage Adjustment Range                                                 | V <sub>OUT_RANGE</sub>    | V <sub>IN</sub> > V <sub>OUT</sub> + 1.8V                                                      | 0.54            |        | 5.5                      | V    |

| Output Voltage Set-Point Range                                                  | V <sub>OUT_RES</sub>      | Configured using PMbus                                                                         |                 | ±0.025 |                          | %    |

| Output Voltage Set-Point Accuracy (Notes 8, 10)                                 | V <sub>OUT_ACCY</sub>     | Includes line, load, and temperature $(-20 ^{\circ}\text{C} \le T_A \le +85 ^{\circ}\text{C})$ | -1              |        | +1                       | %FS  |

| Output Voltage Readback Resolution                                              | V <sub>OUT_READ_RES</sub> |                                                                                                |                 | 10     |                          | Bits |

**Electrical Specifications**  $V_{IN} = V_{DD} = 12V$ ,  $f_{SW} = 533$ kHz,  $C_{OUT} = 1340 \mu$ F,  $T_A = -40 ^{\circ}$ C to  $+85 ^{\circ}$ C, unless otherwise noted. Typical values are at  $T_A = +25 ^{\circ}$ C. Boldface limits apply across the operating temperature range, -40  $^{\circ}$ C to  $+85 ^{\circ}$ C. (Continued)

| PARAMETER                                                 | SYMBOL                       | TEST CONDITIONS                                 | MIN<br>(Note 7)      | TYP                   | MAX<br>(Note 7)      | UNIT |

|-----------------------------------------------------------|------------------------------|-------------------------------------------------|----------------------|-----------------------|----------------------|------|

| Output Voltage Readback Total Error (Note 10)             | V <sub>OUT_READ_ERR</sub>    | PMBus read                                      | -2                   |                       | +2                   | %FS  |

| Output Current Readback Resolution                        | I <sub>OUT_READ_RES</sub>    |                                                 |                      | 10                    |                      | Bits |

| Output Current Range (Note 9)                             | I <sub>OUT_RANGE</sub>       |                                                 |                      |                       | 33                   | Α    |

| Output Current Readback Total Error                       | I <sub>OUT_READ_ERR</sub>    | PMBus read at max load                          |                      | ±2                    |                      | Α    |

| SOFT-START AND SEQUENCING                                 |                              |                                                 |                      |                       |                      |      |

| Delay Time From Enable to V <sub>OUT</sub> Rise           | ton_delay                    | Configured using PMBus                          | 2                    |                       | 5000                 | ms   |

| t <sub>ON_DELAY</sub> Accuracy                            | ton_delay_accy               |                                                 |                      | ±2                    |                      | ms   |

| Output Voltage Ramp-Up Time                               | t <sub>ON_RISE</sub>         | Configured using PMBus                          | 0.5                  |                       | 100                  | ms   |

| Output Voltage Ramp-Up Time<br>Accuracy                   | ton_rise_accy                |                                                 |                      | ±250                  |                      | μs   |

| Delay Time From Disable to V <sub>OUT</sub> Fall          | t <sub>OFF_DELAY</sub>       | Configured using PMBus                          | 2                    |                       | 5000                 | ms   |

| t <sub>OFF_DELAY</sub> Accuracy                           | toff_delay_accy              |                                                 |                      | ±2                    |                      | ms   |

| Output Voltage Fall Time                                  | t <sub>OFF_FALL</sub>        | Configured using PMBus                          | 0.5                  |                       | 100                  | ms   |

| Output Voltage Fall Time Accuracy                         | ton_fall_accy                |                                                 |                      | ±250                  |                      | μs   |

| POWER-GOOD                                                |                              |                                                 |                      |                       |                      |      |

| Power-Good Delay                                          | V <sub>PG_DELAY</sub>        | Configured using PMBus                          | 0                    |                       | 5000                 | ms   |

| TEMPERATURE SENSE                                         |                              |                                                 |                      |                       |                      |      |

| Temperature Sense Range                                   | T <sub>SENSE_RANGE</sub>     | Configurable using PMBus                        | -50                  |                       | 150                  | °C   |

| Internal Temperature Sensor Accuracy                      | INT_TEMP <sub>ACCY</sub>     | Tested at +100°C                                | -5                   |                       | +5                   | °C   |

| External Temperature Sensor Accuracy                      | XTEMP <sub>ACCY</sub>        | Using 2N3904 NPN transistor                     |                      | ±5                    |                      | °C   |

| FAULT PROTECTION                                          |                              |                                                 |                      |                       |                      |      |

| V <sub>DD</sub> Undervoltage Threshold Range              | V <sub>DD_UVLO_RANGE</sub>   | Measured internally                             | 4.18                 |                       | 16                   | ٧    |

| V <sub>DD</sub> Undervoltage Threshold Accuracy (Note 10) | V <sub>DD_UVLO_ACCY</sub>    |                                                 |                      | ±2                    |                      | %FS  |

| V <sub>DD</sub> Undervoltage Response Time                | V <sub>DD_UVLO_DELAY</sub>   |                                                 |                      | 10                    |                      | μs   |

| V <sub>OUT</sub> Overvoltage Threshold Range              | V <sub>OUT_OV_RANGE</sub>    | Factory default                                 |                      | V <sub>OUT</sub> + 15 |                      | %    |

|                                                           |                              | Configured using PMBus                          | V <sub>OUT</sub> + 5 |                       | V <sub>OUT_MAX</sub> | %    |

| V <sub>OUT</sub> Undervoltage Threshold Range             | V <sub>OUT_UV_RANGE</sub>    | Factory default                                 |                      | V <sub>OUT</sub> - 15 |                      | %    |

|                                                           |                              | Configured using PMBus                          | 0                    |                       | V <sub>OUT</sub> - 5 | %    |

| V <sub>OUT</sub> OV/UV Threshold Accuracy (Note 8)        | Vout_ov/uv_accy              |                                                 | -2                   |                       | +2                   | %    |

| V <sub>OUT</sub> OV/UV Response Time                      | V <sub>OUT_OV/UV_DELAY</sub> |                                                 |                      | 10                    |                      | μs   |

| Output Current Limit Set-Point<br>Accuracy (Note 10)      | ILIMIT_ACCY                  | Tested at I <sub>OUT</sub> OC_FAULT_LIMIT = 40A |                      | ±10                   |                      | %FS  |

| Output Current Fault Response Time (Note 11)              | ILIMIT_DELAY                 | Factory default                                 |                      | 3                     |                      | tsw  |

| Over-Temperature Protection                               | T <sub>JUNCTION</sub>        | Factory default                                 |                      | 125                   |                      | °C   |

| Threshold<br>(Controller Junction Temperature)            |                              | Configured using PMBus                          | -40                  |                       | 125                  | °C   |

| Thermal Protection Hysteresis                             | T <sub>JUNCTION_HYS</sub>    |                                                 |                      | 15                    |                      | °C   |

**Electrical Specifications**  $V_{IN} = V_{DD} = 12V$ ,  $f_{SW} = 533$ kHz,  $C_{OUT} = 1340 \mu$ F,  $T_A = -40 \,^{\circ}$ C to  $+85 \,^{\circ}$ C, unless otherwise noted. Typical values are at  $T_A = +25 \,^{\circ}$ C. Boldface limits apply across the operating temperature range,  $-40 \,^{\circ}$ C to  $+85 \,^{\circ}$ C. (Continued)

| PARAMETER                                                | SYMBOL                      | TEST CONDITIONS                                                                        | MIN<br>(Note 7) | TYP | MAX<br>( <u>Note 7</u> ) | UNIT |

|----------------------------------------------------------|-----------------------------|----------------------------------------------------------------------------------------|-----------------|-----|--------------------------|------|

| OSCILLATOR AND SWITCHING CHARACT                         | TERISTICS                   |                                                                                        |                 |     |                          |      |

| Switching Frequency Range                                | f <sub>SW_RANGE</sub>       |                                                                                        | 296             |     | 1067                     | kHz  |

| Switching Frequency Set-Point<br>Accuracy                | f <sub>SW_ACCY</sub>        |                                                                                        | -5              |     | +5                       | %    |

| Minimum Pulse Width Required from<br>External SYNC Clock | EXT_SYNC <sub>PW</sub>      | Measured at 50% amplitude                                                              | 150             |     |                          | ns   |

| Drift Tolerance for External SYNC Clock EXT_SYN          |                             | External SYNC clock equal to 500kHz is not supported                                   | -10             |     | +10                      | %    |

| LOGIC INPUT/OUTPUT CHARACTERISTIC                        | s                           |                                                                                        |                 |     |                          |      |

| Bias Current at the Logic Input Pins                     | I <sub>LOGIC_BIAS</sub>     | DDC, EN, MGN, PG, SA, SCL, SDA, SALRT, SYNC, UVLO, V <sub>MON</sub> , V <sub>SET</sub> | -100            |     | +100                     | nA   |

| Logic Input Low Threshold Voltage                        | V <sub>LOGIC_IN_LOW</sub>   |                                                                                        |                 |     | 0.8                      | V    |

| Logic Input High Threshold Voltage                       | V <sub>LOGIC_IN_HIGH</sub>  |                                                                                        | 2.0             |     |                          | V    |

| Logic Output Low Threshold Voltage                       | V <sub>LOGIC_OUT_LOW</sub>  | 2mA sinking                                                                            |                 |     | 0.5                      | V    |

| Logic Output High Threshold Voltage                      | V <sub>LOGIC_OUT_HIGH</sub> | 2mA sourcing                                                                           | 2.25            |     |                          | V    |

| PMBus INTERFACE TIMING CHARACTER                         | ISTIC                       | -                                                                                      | - 1             |     |                          |      |

| PMBus Operating Frequency                                | f <sub>SMB</sub>            |                                                                                        | 100             |     | 400                      | kHz  |

#### NOTES:

- 7. Compliance to datasheet limits is assured by one or more methods: Production test, characterization, and/or design.

- 8.  $V_{\mbox{\scriptsize OUT}}$  measured at the termination of the  $V_{\mbox{\scriptsize SEN+}}$  and  $V_{\mbox{\scriptsize SEN-}}$  sense points.

- 9. The MAX load current is determined by the thermal "Derating Curves" on page 12.

- 10. "FS" stand for Full Scale of recommended maximum operation range.

- 11. " $t_{SW}$ " stands for time period of operation switching frequency.

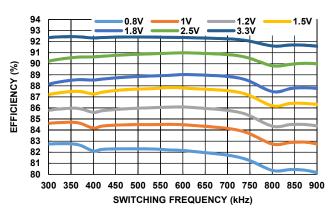

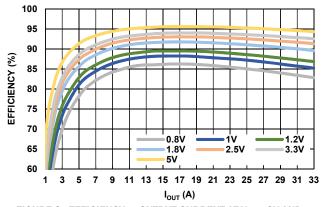

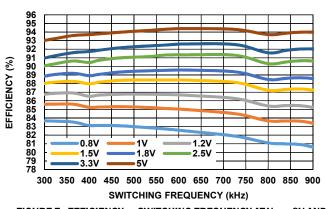

## **Typical Performance Curves**

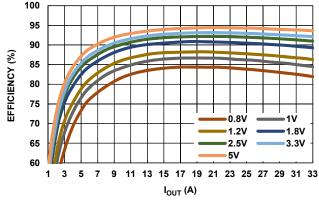

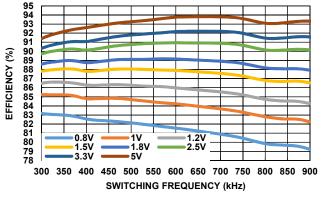

FIGURE 4. EFFICIENCY vs OUTPUT CURRENT AT  $V_{IN} = 5V$  AND  $f_{SW} = 533 \text{kHz}$  FOR VARIOUS OUTPUT VOLTAGES

FIGURE 5. EFFICIENCY vs SWITCHING FREQUENCY AT  $V_{IN}$  = 5V AND  $I_{OUT}$  = 33A FOR VARIOUS OUTPUT VOLTAGES

FIGURE 6. EFFICIENCY vs OUTPUT CURRENT AT  $V_{IN}$  = 9V AND  $f_{SW}$  = 533kHz FOR VARIOUS OUTPUT VOLTAGES

FIGURE 7. EFFICIENCY vs SWITCHING FREQUENCY AT  $V_{IN}$  = 9V AND  $I_{OUT}$  = 33A FOR VARIOUS OUTPUT VOLTAGES

FIGURE 8. EFFICIENCY vs OUTPUT CURRENT AT  $V_{\rm IN}$  = 12V AND  $f_{\rm SW}$  = 533kHz FOR VARIOUS OUTPUT VOLTAGES

FIGURE 9. EFFICIENCY vs SWITCHING FREQUENCY AT  $V_{\rm IN}$  = 12V AND  $I_{\rm OLIT}$  = 33A FOR VARIOUS OUTPUT VOLTAGES

## Typical Performance Curves (Continued)

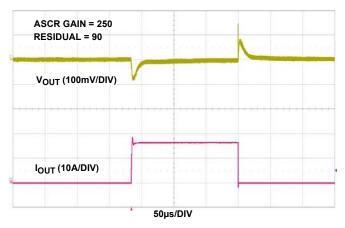

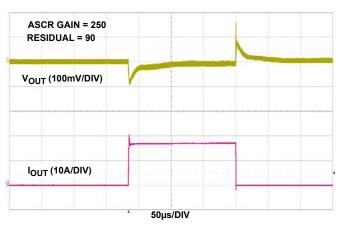

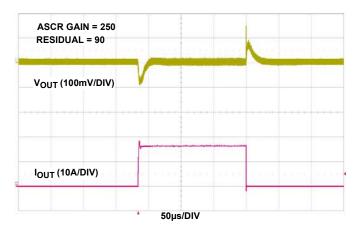

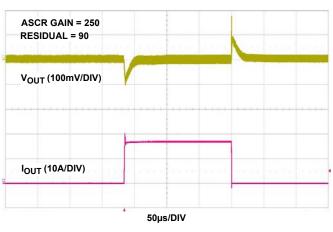

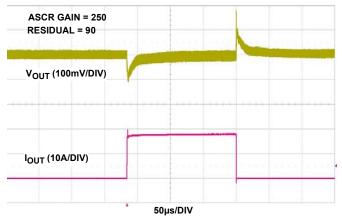

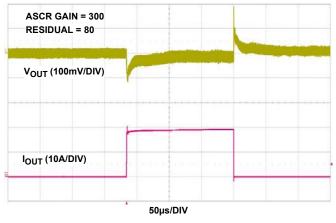

**Transient Response Performance** Operating conditions:  $I_{OUT} = 0/16.5A$ ,  $I_{OUT}$  slew rate >20A/ $\mu$ s,  $T_A = +25$ °C, OLFM airflow. Typical values are used unless otherwise noted.

FIGURE 10.  $5V_{IN}$  TO  $1V_{OUT}$  TRANSIENT RESPONSE,  $f_{SW}$  = 533kHz,  $C_{OUT}$  =  $4x100\mu F$  CERAMIC +  $2x470\mu F$  POSCAP

FIGURE 11.  $5V_{IN}$  TO 1.8 $V_{OUT}$  TRANSIENT RESPONSE,  $f_{SW}$  = 615kHz,  $C_{OUT}$  = 3×100 $\mu$ F CERAMIC + 2×470 $\mu$ F POSCAP

FIGURE 12. 12V<sub>IN</sub> TO 1V<sub>OUT</sub> TRANSIENT RESPONSE,  $f_{SW}$  = 533kHz,  $C_{OUT}$  = 4x100 $\mu$ F CERAMIC + 2x470 $\mu$ F POSCAP

FIGURE 13. 12V<sub>IN</sub> TO 1.8V<sub>OUT</sub> TRANSIENT RESPONSE,  $f_{SW}$  = 615kHz,  $c_{OUT}$  = 3×100 $\mu$ F CERAMIC + 2×470 $\mu$ F POSCAP

FIGURE 14.  $12V_{IN}$  TO  $3.3V_{OUT}$  TRANSIENT RESPONSE,  $f_{SW}$  = 615kHz,  $C_{OUT}$  =  $3\times100\mu F$  CERAMIC +  $2\times470\mu F$  POSCAP

FIGURE 15. 12V $_{\rm IN}$  TO 5V $_{\rm OUT}$  TRANSIENT RESPONSE, f $_{\rm SW}$  = 727kHz, C $_{\rm OUT}$  = 3x100 $\mu$ F CERAMIC + 2x470 $\mu$ F POSCAP

## **Typical Performance Curves (Continued)**

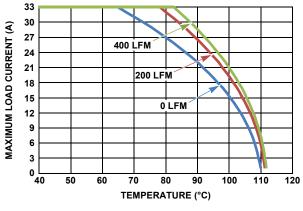

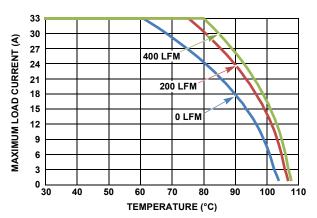

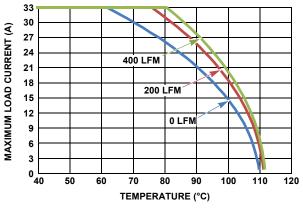

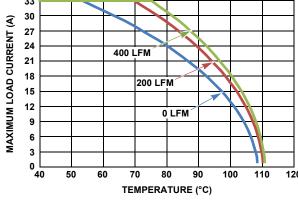

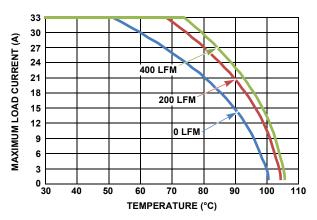

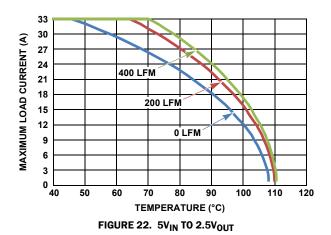

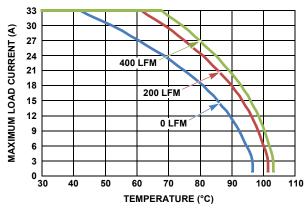

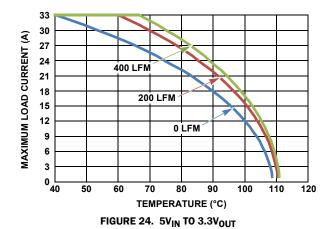

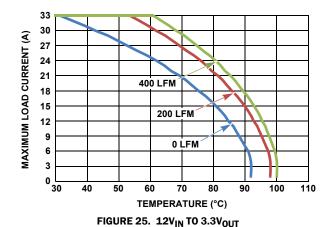

**Derating Curves** All of the following curves were plotted at  $T_J = +115$  °C,  $f_{SW} = 533$ kHz

FIGURE 16. 5V<sub>IN</sub> TO 1V<sub>OUT</sub>

FIGURE 17. 12V<sub>IN</sub> TO 1V<sub>OUT</sub>

FIGURE 18. 5V<sub>IN</sub> TO 1.2V<sub>OUT</sub>

FIGURE 19. 12V<sub>IN</sub> TO 1.2V<sub>OUT</sub>

FIGURE 20. 5V<sub>IN</sub> TO 1.8V<sub>OUT</sub>

FIGURE 21. 12V<sub>IN</sub> TO 1.8V<sub>OUT</sub>

## Typical Performance Curves (Continued)

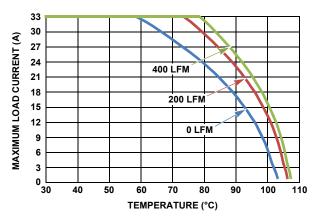

**Derating Curves** All of the following curves were plotted at  $T_J$  = +115 °C,  $f_{SW}$  = 533kHz

FIGURE 23.  $12V_{IN}$  TO  $2.5V_{OUT}$

FIGURE 26. 12 $V_{\mathrm{IN}}$  TO  $5V_{\mathrm{OUT}}$ , 700kHz

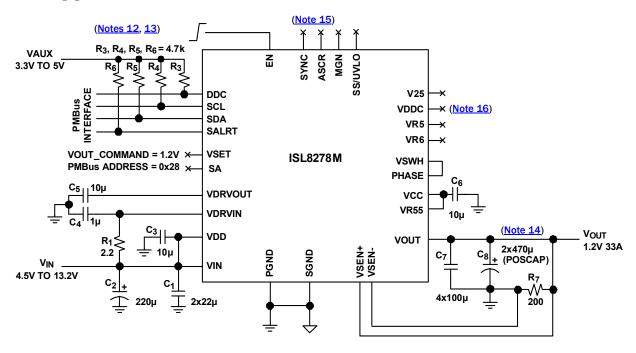

## **Typical Application Circuit**

#### NOTES:

- 12. R<sub>4</sub> and R<sub>5</sub> are not required if the PMBus host already has I<sup>2</sup>C pull-up resistors.

- 13. Only one R<sub>3</sub> per DDC bus is required when DDC bus is shared with other modules.

- 14. R<sub>7</sub> is optional but recommended to sink possible ~100μA back-flow current from the V<sub>SEN+</sub> pin. Back-flow current is present only when the module is in a disabled state with power still available at the VDD pin.

- 15. Unused pins (SYNC, ASCR, MGN, SS/UVLO) can be no connect.

- 16. Internal reference supply pins (V25, VDDC, VR5, VR6) do not need external capacitors and can be no connect. Refer to "PCB Layout Guidelines" on page 21 for more information.

FIGURE 27. TYPICAL SINGLE-PHASE APPLICATION CIRCUIT FOR 1.2V/33A OUTPUT

TABLE 2. ISL8278M DESIGN GUIDE MATRIX AND OUTPUT VOLTAGE RESPONSE

| V <sub>IN</sub> | V <sub>OUT</sub> | C <sub>IN</sub><br>(BULK)<br>(Note 17) | C <sub>IN</sub><br>(CERAMIC) | C <sub>OUT</sub> (BULK) | C <sub>OUT</sub><br>(CERAMIC) | ASCR<br>GAIN<br>(Note 18) | ASCR<br>RESIDUAL<br>(Note 18) | FREQUENCY | V <sub>OUT</sub><br>DEVIATION<br>(mV) | RECOVERY<br>TIME<br>(µS) | STEP<br>LOAD<br>(A)<br>(Note 19) |

|-----------------|------------------|----------------------------------------|------------------------------|-------------------------|-------------------------------|---------------------------|-------------------------------|-----------|---------------------------------------|--------------------------|----------------------------------|

| 5               | 0.8              | 2x150μF                                | 3x22µF                       | 2x470μF                 | 4x100μF                       | 120                       | 90                            | 364       | 140                                   | 35                       | 16.5A                            |

| 5               | 0.8              | 2x150μF                                | 3x22µF                       | 2x470μF                 | 4x100μF                       | 200                       | 90                            | 533       | 100                                   | 30                       | 16.5A                            |

| 5               | 0.9              | 2x150μF                                | 3x22µF                       | 2x470μF                 | 4x100μF                       | 120                       | 90                            | 364       | 130                                   | 40                       | 16.5A                            |

| 5               | 1                | 2x150μF                                | 3x22µF                       | 2x470μF                 | 4x100μF                       | 120                       | 90                            | 364       | 110                                   | 35                       | 16.5A                            |

| 5               | 1                | 2x150μF                                | 3x22µF                       | 2x470μF                 | 4x100μF                       | 250                       | 90                            | 533       | 80                                    | 20                       | 16.5A                            |

| 5               | 1.05             | 2x150μF                                | 3x22µF                       | 2x470μF                 | 4x100μF                       | 160                       | 90                            | 421       | 90                                    | 30                       | 16.5A                            |

| 5               | 1.1              | 2x150μF                                | 3x22µF                       | 2x470μF                 | 4x100μF                       | 200                       | 90                            | 471       | 90                                    | 25                       | 16.5A                            |

| 5               | 1.2              | 2x150μF                                | 3x22µF                       | 2x470μF                 | 4x100μF                       | 250                       | 90                            | 533       | 80                                    | 20                       | 16.5A                            |

| 5               | 1.3              | 2x150μF                                | 3x22µF                       | 2x470μF                 | 4x100μF                       | 250                       | 90                            | 533       | 80                                    | 25                       | 16.5A                            |

| 5               | 1.5              | 2x150μF                                | 3x22µF                       | 2x470μF                 | 4x100μF                       | 250                       | 90                            | 533       | 80                                    | 30                       | 16.5A                            |

| 5               | 1.8              | 2x150μF                                | 3x22µF                       | 2x470μF                 | 3x100µF                       | 250                       | 90                            | 615       | 80                                    | 50                       | 16.5A                            |

| 5               | 2.5              | 2x150μF                                | 3x22µF                       | 2x470μF                 | 3x100μF                       | 200                       | 90                            | 615       | 90                                    | 70                       | 16.5A                            |

| 5               | 3.3              | 2x150μF                                | 3x22µF                       | 2x470μF                 | 3x100μF                       | 200                       | 90                            | 615       | 90                                    | 90                       | 16.5A                            |

| 5               | 1.8              | 2x150μF                                | 3x22µF                       | 1x470μF                 | 3x100μF                       | 160                       | 90                            | 615       | 125                                   | 60                       | 16.5A                            |

#### TABLE 2. ISL8278M DESIGN GUIDE MATRIX AND OUTPUT VOLTAGE RESPONSE

| 5  | 2.5  | 2x150μF | 3x22µF | 1x470µF | 3x100µF | 160 | 90 | 615 | 120 | 70 | 16.5A |

|----|------|---------|--------|---------|---------|-----|----|-----|-----|----|-------|

| 5  | 3.3  | 2x150μF | 3x22µF | 1x470µF | 3x100µF | 160 | 70 | 615 | 120 | 70 | 16.5A |

| 12 | 0.8  | 2x150µF | 3x22µF | 2x470µF | 4x100μF | 120 | 90 | 364 | 140 | 35 | 16.5A |

| 12 | 0.8  | 2x150µF | 3x22µF | 2x470µF | 4x100μF | 200 | 90 | 533 | 100 | 35 | 16.5A |

| 12 | 0.9  | 2x150µF | 3x22µF | 2x470μF | 4x100μF | 120 | 90 | 364 | 130 | 32 | 16.5A |

| 12 | 1    | 2x150µF | 3x22µF | 2x470µF | 4x100μF | 120 | 90 | 364 | 110 | 25 | 16.5A |

| 12 | 1    | 2x150µF | 3x22μF | 2x470μF | 4x100μF | 250 | 90 | 533 | 85  | 20 | 16.5A |

| 12 | 1.05 | 2x150µF | 3x22µF | 2x470μF | 4x100μF | 160 | 70 | 421 | 90  | 15 | 16.5A |

| 12 | 1.1  | 2x150µF | 3x22µF | 2x470µF | 4x100μF | 160 | 90 | 471 | 95  | 25 | 16.5A |

| 12 | 1.2  | 2x150µF | 3x22μF | 2x470μF | 4x100μF | 250 | 90 | 533 | 85  | 17 | 16.5A |

| 12 | 1.3  | 2x150µF | 3x22µF | 2x470µF | 4x100μF | 250 | 90 | 533 | 85  | 17 | 16.5A |

| 12 | 1.5  | 2x150µF | 3x22μF | 2x470μF | 4x100μF | 200 | 90 | 533 | 90  | 20 | 16.5A |

| 12 | 1.8  | 2x150µF | 3x22μF | 2x470μF | 3x100μF | 250 | 90 | 615 | 90  | 20 | 16.5A |

| 12 | 2.5  | 2x150µF | 3x22µF | 2x470µF | 3x100μF | 250 | 90 | 615 | 90  | 15 | 16.5A |

| 12 | 3.3  | 2x150µF | 3x22µF | 2x470µF | 3x100µF | 250 | 90 | 615 | 90  | 20 | 16.5A |

| 12 | 5    | 2x150µF | 3x22µF | 2x470μF | 3x100μF | 300 | 80 | 727 | 90  | 12 | 16.5A |

| 12 | 1.8  | 2x150µF | 3x22µF | 1x470µF | 3x100µF | 160 | 90 | 615 | 160 | 20 | 16.5A |

| 12 | 2.5  | 2x150μF | 3x22μF | 1x470µF | 3x100μF | 160 | 90 | 615 | 150 | 20 | 16.5A |

| 12 | 3.3  | 2x150μF | 3x22μF | 1x470μF | 3x100μF | 160 | 90 | 615 | 160 | 20 | 16.5A |

| 12 | 5    | 2x150μF | 3x22μF | 1x470μF | 3x100μF | 160 | 90 | 727 | 180 | 50 | 16.5A |

#### NOTES:

- 17.  $C_{\mbox{\scriptsize IN}}$  bulk capacitor is optional only for energy buffer from the long input power supply cable.

- 18. ASCR gain and residual are selected to ensure that the phase margin is higher than 60° and gain margin is higher than 6dB at -40°C, +25°C, +85°C, and full load (33A).

- 19. Output voltage response is tested with load step slew rate higher than 20A/ $\mu s$ .

### TABLE 3. RECOMMENDED I/O CAPACITOR IN Table 2

| VENDORS                    | VALUE             | PART NUMBER        |

|----------------------------|-------------------|--------------------|

| Murata, Input Ceramic      | 47μF, 16V, 1210   | GRM32ER61C476ME15L |

| Murata, Input Ceramic      | 22μF, 16V, 1210   | GRM32ER61E226KE15L |

| Taiyo Yuden, Input Ceramic | 47μF, 16V, 1210   | EMK325BJ476MM-T    |

| Taiyo Yuden, Input Ceramic | 22μF, 25V, 1210   | TMK325BJ226MM-T    |

| Murata, Output Ceramic     | 100μF, 6.3V, 1210 | GRM32ER60J107M     |

| TDK, Output Ceramic        | 100μF, 6.3V, 1210 | C3225X5R0J107M     |

| AVX, Output Ceramic        | 100μF, 6.3V, 1210 | 12106D107MAT2A     |

| Sanyo POSCAP, Input Bulk   | 150μF, 16V        | 16TQC150MYF        |

| Sanyo POSCAP, Output Bulk  | 470µF, 4V         | 4TPE470MCL         |

| Sanyo POSCAP, Output Bulk  | 470μF, 6.3V       | 6TPF470MAH         |

## **Functional Description**

### **SMBus Communications**

The ISL8278M provides an SMBus digital interface that enables the user to configure all aspects of the module operation as well as monitor the input and output parameters. The ISL8278M can be used with any SMBus host device. In addition, the module is compatible with PMBus Power System Management Protocol Specification Parts I and II version 1.2. The ISL8278M accepts most standard PMBus commands. When controlling the device with PMBus commands, it is recommended that the enable pin be tied to SGND.

The SMBus device address is the only parameter that must be set by external pins. All other device parameters can be set with PMBus commands.

### **Output Voltage Selection**

The output voltage can be set to a voltage between 0.6V and 5V provided that the input voltage is higher than the desired output voltage by an amount sufficient to maintain regulation.

The VSET pin is used to set the output voltage to levels as shown in <u>Table 4</u>. The  $R_{SET}$  resistor is placed between the VSET pin and SGND. A standard 1% resistor is recommend.

**TABLE 4. OUTPUT VOLTAGE RESISTOR SETTINGS**

| V <sub>OUT</sub> (V) | R <sub>SET</sub><br>(kΩ) |

|----------------------|--------------------------|

| 0.60                 | 10                       |

| 0.65                 | 11                       |

| 0.70                 | 12.1                     |

| 0.75                 | 13.3                     |

| 0.80                 | 14.7                     |

| 0.85                 | 16.2                     |

| 0.90                 | 17.8                     |

| 0.95                 | 19.6                     |

| 1.00                 | 21.5 or connect to SGND  |

| 1.05                 | 23.7                     |

| 1.10                 | 26.1                     |

| 1.15                 | 28.7                     |

| 1.20                 | 31.6 or OPEN             |

| 1.25                 | 34.8                     |

| 1.30                 | 38.3                     |

| 1.40                 | 42.2                     |

| 1.50                 | 46.4                     |

| 1.60                 | 51.1                     |

| 1.70                 | 56.2                     |

| 1.80                 | 61.9                     |

| 1.90                 | 68.1                     |

| 2.00                 | 75                       |

TABLE 4. OUTPUT VOLTAGE RESISTOR SETTINGS (Continued)

| V <sub>OUT</sub><br>(V) | R <sub>SET</sub><br>(kΩ) |

|-------------------------|--------------------------|

| 2.10                    | 82.5                     |

| 2.20                    | 90.9                     |

| 2.30                    | 100                      |

| 2.50                    | 110, or connect to V25   |

| 2.80                    | 121                      |

| 3.00                    | 133                      |

| 3.30                    | 147                      |

| 4.00                    | 162                      |

| 5.00                    | 178                      |

The output voltage can also be set to any value between 0.6V and 5V using a PMBus command VOUT\_COMMAND.

By default, V<sub>OUT\_MAX</sub> is set 110% higher than V<sub>OUT</sub> set by the pin-strap resistor, which can be changed to any value up to 5.5V with PMBus Command VOUT\_MAX.

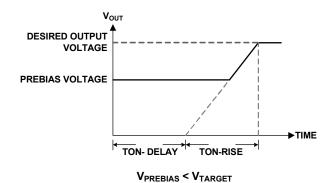

### **Soft-Start Delay and Ramp Times**

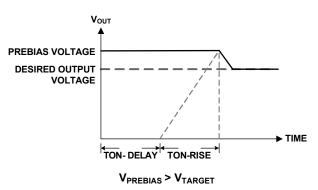

The ISL8278M follows an internal start-up procedure after power is applied to the VDD pin. The module requires approximately 60ms to 70ms to check for specific values stored in its internal memory and programmed by pin-strap resistors. After this process is complete, the device is ready to accept commands through the PMBus interface and the module is ready to be enabled. If the module is to be synchronized to an external clock source, the clock frequency must be stable before asserting the EN pin.

It may be necessary to set a delay from when an enable signal is received until the output voltage starts to ramp to its target value. In addition, the designer may want to precisely set the time required for  $V_{OUT}$  to ramp to its target value after the delay period has expired. These features can be used as part of an overall inrush current management strategy or to precisely control how fast a load IC is turned on. The ISL8278M gives the system designer several options for precisely and independently controlling both the delay and ramp time periods. The soft-start delay period begins when the EN pin is asserted and ends when the delay time expires.

The soft-start delay and ramp times can be programmed to custom values with PMBus commands TON\_DELAY and TON\_RISE. When the delay time is set to 0ms, the device begins its ramp-up after the internal circuitry has initialized (approximately 2ms). When the soft-start ramp period is set to 0ms, the output ramps up as quickly as the output load capacitance and loop settings allow. It is generally recommended to set the soft-start ramp to a value greater than 500µs to prevent inadvertent fault conditions due to excessive inrush current.

Similar to the soft-start delay and ramp-up time, the delay and ramp-down time for soft-stop/off can be programmed with PMBus commands TOFF\_DELAY and TOFF\_FALL. In addition, the module can be configured as "immediate off" with the command

ON\_OFF\_CONFIG, such that the internal MOSFETs are turned off immediately after the delay time expires.

The SS/UVLO pin can be used to program the soft-start/stop delay time and ramp time to some typical values as shown in Table 5.

**TABLE 5. SOFT-START/STOP RESISTOR SETTINGS**

| DELAY TIME<br>(ms) | RAMP TIME<br>(ms) | R <sub>SET</sub><br>(kΩ)             |

|--------------------|-------------------|--------------------------------------|

| 5                  | 2                 | 12.1, 26.1, 56.2, or connect to SGND |

| 10                 | 2                 | 16.2, 34.8, 75                       |

| 5                  | 5                 | 13.3, 28.7, 61.9, or<br>OPEN         |

| 10                 | 5                 | 17.8, 38.3, 82.5                     |

| 20                 | 5                 | 21.5, 46.4, 100                      |

| 5                  | 10                | 14.7, 31.6, 68.1                     |

| 10                 | 10                | 19.6, 42.2, 90.9, or connect to V25  |

| 20                 | 10                | 23.7, 51.1, 110                      |

#### **Power-Good**

The ISL8278M provides a Power-Good (PG) signal that indicates the output voltage is within a specified tolerance of its target level and no fault condition exists. By default, the PG pin asserts if the output is within 10% of the target voltage. These limits and the polarity of the pin can be changed with PMBus command POWER\_GOOD\_ON.

A PG delay period is defined as the time from when all conditions within the ISL8278M for asserting PG are met to when the PG pin is actually asserted. This feature is commonly used instead of using an external reset controller to control external digital logic. A PG delay can be programmed with PMBus command POWER\_GOOD\_DELAY.

### **Switching Frequency and PLL**

The device's switching frequency is set from 296kHz to 1067kHz using the pin-strap method as shown in Table 6, or by using a PMBus command FREQUENCY\_SWITCH. The ISL8278M incorporates an internal Phase-Locked Loop (PLL) to clock the internal circuitry. The PLL can be driven by an external clock source connected to the SYNC pin. When using the internal oscillator, the SYNC pin can be configured as a clock source that is an external sync to other modules. Refer to "SYNC CONFIG (E9h)" on page 46 for more information.

**TABLE 6. SWITCHING FREQUENCY RESISTOR SETTINGS**

| fsw<br>(V) | R <sub>SET</sub><br>(kΩ) |

|------------|--------------------------|

| 296        | 14.7 or connect to SGND  |

| 320        | 16.2                     |

| 364        | 17.8                     |

| 400        | 19.6                     |

TABLE 6. SWITCHING FREQUENCY RESISTOR SETTINGS (Continued)

| f <sub>SW</sub><br>(V) | R <sub>SET</sub><br>(κΩ) |

|------------------------|--------------------------|

| 421                    | 21.5                     |

| 471                    | 23.7                     |

| 533                    | 26.1 or OPEN             |

| 571                    | 28.7                     |

| 615                    | 31.6                     |

| 727                    | 34.8                     |

| 800                    | 38.3                     |

| 842                    | 42.2                     |

| 889                    | 46.4                     |

| 1067                   | 51.1 or connect to V25   |

### **Loop Compensation**

The module loop response is programmable through PMBus command ASCR\_CONFIG or by using the pin-strap method (ASCR pin) according to <a href="Table 7">Table 7</a>. The ISL8278M uses the ChargeMode control algorithm that responds to output current changes within a single PWM switching cycle, achieving a smaller total output voltage variation with less output capacitance than traditional PWM controllers.

**TABLE 7. ASCR RESISTOR SETTINGS**

| ASCR GAIN | ASCR RESIDUAL | R <sub>SET</sub> (kΩ) |

|-----------|---------------|-----------------------|

| 120       | 90            | 10                    |

| 160       | 90            | 11 or connect to SGND |

| 200       | 90            | 12.1                  |

| 250       | 90            | 13.3 or OPEN          |

| 300       | 90            | 14.7                  |

| 350       | 90            | 16.2                  |

| 400       | 90            | 17.8                  |

| 500       | 90            | 19.6                  |

| 600       | 90            | 21.5                  |

| 120       | 80            | 23.7                  |

| 160       | 80            | 26.1                  |

| 200       | 80            | 28.7                  |

| 250       | 80            | 31.6                  |

| 300       | 80            | 34.8                  |

| 350       | 80            | 38.3                  |

| 400       | 80            | 42.2                  |

| 80        | 70            | 46.4                  |

| 120       | 70            | 51.1                  |

| 160       | 70            | 56.2                  |

| 200       | 70            | 61.9                  |

TABLE 7. ASCR RESISTOR SETTINGS (Continued)

| 250 | 70  | 68.1                   |

|-----|-----|------------------------|

| 300 | 70  | 75                     |

| 120 | 100 | 82.5                   |

| 160 | 100 | 90.9                   |

| 200 | 100 | 100                    |

| 250 | 100 | 110, or Connect to V25 |

| 300 | 100 | 121                    |

| 350 | 100 | 133                    |

| 400 | 100 | 147                    |

| 500 | 100 | 162                    |

| 600 | 100 | 178                    |

### Input Undervoltage Lockout (UVLO)

The Input Undervoltage Lockout (UVLO) prevents the ISL8278M from operating when the input falls below a preset threshold, indicating the input supply is out of its specified range. The UVLO threshold (V<sub>UVLO</sub>) can be set between 4.18V and 16V using the pin-strap method as shown in <u>Table 8</u>, or by using a PMBus command VIN\_UV\_FAULT\_LIMIT.

Fault response to an input undervoltage fault can be programmed with PMBus command VIN UV FAULT RESPONSE.

**TABLE 8. UVLO RESISTOR SETTINGS**

| UVLO<br>(V) | R <sub>UVLO</sub><br>(kΩ)                                                     |

|-------------|-------------------------------------------------------------------------------|

| 4.5         | 12.1, 13.3, 14.7, 16.2, 17.8, 19.6, 21.5, 23.7, OPEN, connect to V25 and SGND |

| 4.3         | 26.1                                                                          |

| 4.59        | 28.7                                                                          |