# コンパクトな同期整流型降圧コンバータ

## ISL80020, ISL80020A, ISL80015, ISL80015A

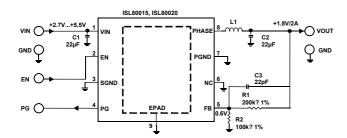

ISL80020、ISL80020A、ISL80015、ISL80015Aは、高効率のモノリシック同期整流型降圧 DC/DC コンバータです。2.7V~5.5Vの入力電源によって最大2Aの連続出力電流を供給できます。ピーク電流モード制御アーキテクチャを使用し、極めて低いデューティ・サイクルでの動作が可能です。1MHz または2MHz のいずれかのスイッチング周波数で動作するため、優れた過渡応答特性を有し、低インダクタンスのインダクタを使用できます。安定性にも優れています。

ISL80020、ISL80020A、ISL80015、ISL80015A は、効率を最大化するために、 $r_{DS(ON)}$  が極めて小さい MOSFET を内蔵しています。さらに、ハイサイド MOSFET が PMOS であるため、ブート・コンデンサが不要であり、外付け部品点数が削減されます。本製品は 100% のデューティ・サイクルでも動作可能です(@1MHz 品)。

高速負荷応答を実現するため、製品はPWM(パルス幅変調)で構成され、これは出力ノイズとRF干渉の低減にも役立ちます。

これらの製品は、熱性能を向上するエキスポーズド・パッドを備えた省スペース型の 8 ピン  $2mm \times 2mmTDFN$  鉛フリー・パッケージで供給されます。コンバータ全体の占有面積は  $64mm^2$  未満です。

## 特長

- V<sub>IN</sub> 範囲: 2.7V ∼ 5.5V

- 最大 I<sub>OUT</sub>: 1.5A または 2A (2 ページの表 1 参照)

- スイッチング周波数: 1MHz または 2MHz (2ページの表 1 参照)

- 過電流および短絡保護

- 過熱保護 / サーマル・プロテクション

- 負電流保護

- パワーグッドおよびイネーブル

- 100% デューティ・サイクル (1MHz 品)

- 内部ソフトスタートおよびソフトストップ

- $V_{IN}$  アンダーボルテージ・ロックアウトおよび  $V_{OUT}$  過電圧保護

- 最大 95% のピーク効率

## アプリケーション

- 汎用 POL

- 産業用、計装用、医療用機器

- 通信およびネットワーク用機器

- ゲーム・コンソール

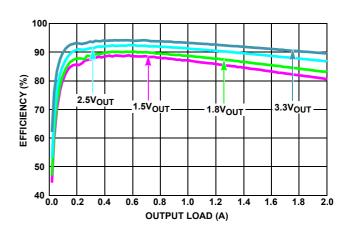

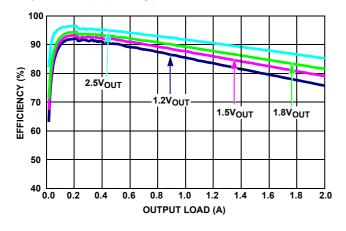

図 2. 効率 vs 負荷、f<sub>SW</sub> = 2MHz、V<sub>IN</sub> = 5V、T<sub>A</sub> = +25 ℃

# ISL80020、ISL80020A、ISL80015、ISL80015A

### 表 1. 主な相違点一覧

| 製品型番      | I <sub>OUT</sub> (MAX)<br>(A) | f <sub>SW</sub><br>(MHz) | V <sub>IN</sub> 範囲<br>(V) | V <sub>OUT</sub> 範囲<br>(V) | パッケージ<br>寸法       |  |

|-----------|-------------------------------|--------------------------|---------------------------|----------------------------|-------------------|--|

| ISL80015  | 1.5                           | 1                        |                           | 0.6 <b>~</b> 5.5           |                   |  |

| ISL80015A | 1.5                           | 2                        | 07.55                     |                            | o.i.s. o TDEN     |  |

| ISL80020  | 2                             | 1                        | 2.7 ~ 5.5                 |                            | 8ピン2mm x 2mm TDFN |  |

| ISL80020A | 2                             | 2                        |                           |                            |                   |  |

NOTE: 本データシートでは、表内に示した各製品型番をまとめて「製品」と呼びます。

### 表 2. 部品値の選択表

| V <sub>OUT</sub> (V) | C1<br>(µF) | C2<br>(μF) | C3<br>(pF) | L1<br>(µH) | R1<br>(kΩ) | R2<br>(kΩ) |

|----------------------|------------|------------|------------|------------|------------|------------|

| 0.8                  | 22         | 22         | 22         | 1.0~2.2    | 33         | 100        |

| 1.2                  | 22         | 22         | 22         | 1.0~2.2    | 100        | 100        |

| 1.5                  | 22         | 22         | 22         | 1.0~2.2    | 150        | 100        |

| 1.8                  | 22         | 22         | 22         | 1.0~3.3    | 200        | 100        |

| 2.5                  | 22         | 22         | 22         | 1.5~3.3    | 316        | 100        |

| 3.3                  | 22         | 22         | 22         | 1.5~4.7    | 450        | 100        |

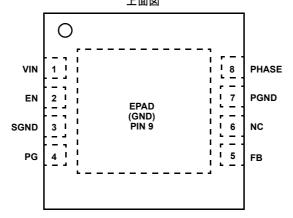

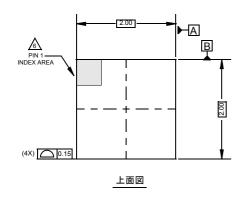

# ピン配置

ISL80020、ISL80020A、ISL80015、ISL80015A (8 LD 2x2 TDFN) 上面図

# ピンの説明

| ピン番号 | ピン名称  | ピンの説明                                                                                                                                                       |

|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | VIN   | PWM レギュレータのパワー段の入力電源および IC のバイアスを供給する内部リニア・レギュレータの電源です。デカップリングのために、VIN と GND の間には $10\mu F$ 以上のセラミック・コンデンサを接続し、かつ IC のできるだけ近くに配置します。                        |

| 2    | EN    | イネーブル入力です。このピンの電圧が 1.4V を上回ると、製品がイネーブルされます。このピンをグラウンドにプルダウンすると、製品はディスエーブルされます。ディスエーブルすると、100Ω の抵抗が PHASE ピンを介して出力を放電します。詳細については、4ページの「機能ブロック図」の図3を参照してください。 |

| 3    | SGND  | ピン3はエキスポーズド・パッドに接続します。                                                                                                                                      |

| 4    | PG    | パワーグッド出力は、ソフトスタート期間中、および出力電圧がレギュレーションのリミット値を下回る場合にグラウンドにプルダウンされます。このピンには製品内部で 5MΩ のプルアップ抵抗が接続されています。                                                        |

| 5    | FB    | レギュレータの帰還ピンです。FB は、電圧ループ誤差アンプへの負入力です。出力電圧は、FB に接続された外付け抵抗分圧回路によって設定されます。また、パワーグッド PWM レギュレータのパワーグッドおよびアンダーボルテージ保護回路も FB を使って出力電圧をモニタリングします。                 |

| 6    | NC    | NC ピンはエキスポーズド・パッドに接続します。                                                                                                                                    |

| 7    | PGND  | 電源およびアナログ・グラウンド接続です。基板のグラウンド層に直接接続します。                                                                                                                      |

| 8    | PHASE | 出力電圧レギュレーションのためのパワー段のスイッチング・ノードです。出力インダクタに接続します。<br>製品をディスエーブルすると、このピンは $100\Omega$ の抵抗によって放電されます。詳細については、 $4$ ページ の「機能ブロック図」の図 3 を参照してください。                |

| 9    | E PAD | エキスポーズド・パッドは適切な電気的性能を得るために PGND ピンに接続する必要があります。熱性能を最適化するために、パッド下には PGND 層に接続するビアをできるだけ多く配置してください。                                                           |

Submit Document Feedback

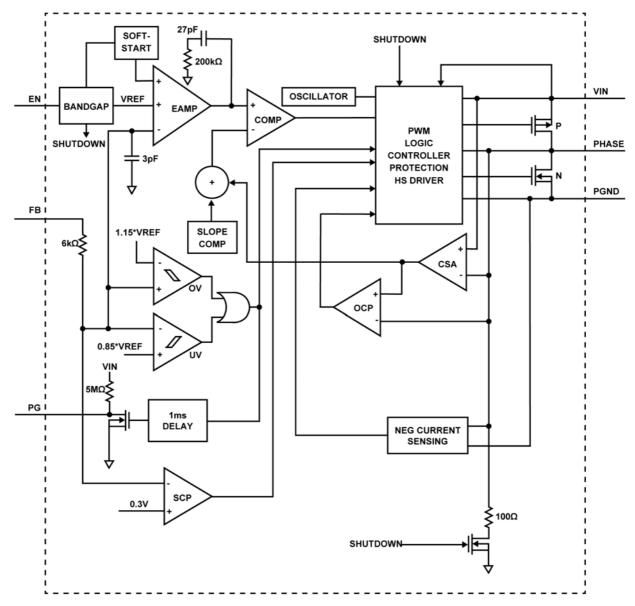

# 機能ブロック図

図 3. 機能ブロック図

## 注文情報

| 製品型番<br>(Note 1, 2, 3) | テープ・アンド・<br>リール<br>数量 | 製品<br>マーキング | 技術仕様       | 温度範囲<br>(°C)      | パッケージ<br>テープ・アンド・<br>リール<br>(RoHS 準拠) | パッケージの<br>外形図 |

|------------------------|-----------------------|-------------|------------|-------------------|---------------------------------------|---------------|

| ISL80020IRZ-T          | 1000                  | 020         | 2A, 1MHz   | -40 <b>~</b> +85  | 8 Ld TDFN                             | L8.2x2C       |

| ISL80020IRZ-T7A        | 250                   | 020         | 2A, 1MHz   | -40 <b>~</b> +85  | 8 Ld TDFN                             | L8.2x2C       |

| ISL80020AIRZ-T         | 1000                  | 20A         | 2A, 2MHz   | -40 <b>~</b> +85  | 8 Ld TDFN                             | L8.2x2C       |

| ISL80020AIRZ-T7A       | 250                   | 20A         | 2A, 2MHz   | -40 <b>~</b> +85  | 8 Ld TDFN                             | L8.2x2C       |

| ISL80015IRZ-T          | 1000                  | 015         | 1.5A, 1MHz | -40 <b>~</b> +85  | 8 Ld TDFN                             | L8.2x2C       |

| ISL80015IRZ-T7A        | 250                   | 015         | 1.5A, 1MHz | -40 <b>~</b> +85  | 8 Ld TDFN                             | L8.2x2C       |

| ISL80015AIRZ-T         | 1000                  | A15         | 1.5A, 2MHz | -40 <b>~</b> +85  | 8 Ld TDFN                             | L8.2x2C       |

| ISL80015AIRZ-T7A       | 250                   | A15         | 1.5A, 2MHz | -40 <b>~</b> +85  | 8 Ld TDFN                             | L8.2x2C       |

| ISL80020FRZ-T          | 1000                  | 20F         | 2A, 1MHz   | -40 ~ +125        | 8 Ld TDFN                             | L8.2x2C       |

| ISL80020FRZ-T7A        | 250                   | 20F         | 2A, 1MHz   | -40 <b>~</b> +125 | 8 Ld TDFN                             | L8.2x2C       |

| ISL80020AFRZ-T         | 1000                  | 0AF         | 2A, 2MHz   | -40 <b>~</b> +125 | 8 Ld TDFN                             | L8.2x2C       |

| ISL80020AFRZ-T7A       | 250                   | 0AF         | 2A, 2MHz   | -40 <b>~</b> +125 | 8 Ld TDFN                             | L8.2x2C       |

| SL80015FRZ-T           | 1000                  | 15F         | 1.5A, 1MHz | -40 <b>~</b> +125 | 8 Ld TDFN                             | L8.2x2C       |

| SL80015FRZ-T7A         | 250                   | 15F         | 1.5A, 1MHz | -40 <b>~</b> +125 | 8 Ld TDFN                             | L8.2x2C       |

| SL80015AFRZ-T          | 1000                  | 5AF         | 1.5A, 2MHz | -40 <b>~</b> +125 | 8 Ld TDFN                             | L8.2x2C       |

| SL80015AFRZ-T7A        | 250                   | 5AF         | 1.5A, 2MHz | -40 <b>~</b> +125 | 8 Ld TDFN                             | L8.2x2C       |

#### NOTE:

- 1. リールの詳細仕様については、TB347を参照してください。

- 2. インターシルのこれらの鉛フリー・プラスチック・パッケージ製品には、専用の鉛フリー素材セット、モールド材料 / ダイ・アタッチ素材を使用するとともに、錫 100% の梨地メッキとアニーリングを実施しています (RoHS 指令に準拠するとともに SnPb ハンダ付け作業と鉛フリー・ハンダ付け作業とも互換性のある e3 端子仕上げ)。インターシルの 鉛フリー製品は、鉛フリー・ピークリフロー温度でMSL 分類に対応し、IPC/JEDEC J STD-020 の鉛フリー要件と同等か上回るものです。

- 3. 吸湿性レベル (MSL) については  $\underline{ISL80020}$ 、  $\underline{ISL80020A}$ 、  $\underline{ISL80015}$ 、  $\underline{ISL80015A}$  の製品情報ページを参照してください。 MSL の詳細については、テクニカル・ブリーフ  $\underline{TB363}$  を参照してください。

## ISL80020、ISL80020A、ISL80015、ISL80015A

### 絶対最大定格

| ıs)          |

|--------------|

| ıs)          |

| 3V           |

| 7V           |

| $^{\circ}$ C |

|              |

| ٤V           |

| V            |

| ٤V           |

| シ)           |

| 2)           |

| 37.          |

### 温度情報

| 熱抵抗 (代表値、 $\underline{Note 4}$ 、 $\underline{5}$ ) | $\theta_{JA}$ ( °C /W) | $\theta_{JC}$ (°C/W) |

|----------------------------------------------------|------------------------|----------------------|

| 2 x 2 TDFN パッケージ                                   | . 71                   | 7                    |

| ジャンクション温度範囲                                        | 55 °                   | °C ~ +125 °C         |

| 保存温度範囲                                             |                        |                      |

| 鉛フリー・リフロープロファイル                                    |                        | TB493 参照             |

|                                                    |                        |                      |

| 推奨動作条件                                             |                        |                      |

| VIN 電源電圧範囲                                         |                        | $2.7V \sim 5.5V$     |

| 負荷電流範囲                                             |                        |                      |

|                                                    |                        |                      |

ジャンクション温度範囲.....-40  $\mathbb{C}$ ~ +125  $\mathbb{C}$

注意:過度に長い時間にわたって最大定格点または最大定格点付近で動作させないでください。そのような動作条件を課すと製品の信頼性 に悪影響が及ぶ恐れがあるとともに、保証の対象とはならない可能性があります。

#### NOTE:

- 4.  $\theta_{\mathrm{JA}}$  は、デバイスを放熱効率の高い「ダイレクト・アタッチ」機能対応の試験基板に実装し、自由大気中で測定した値です。詳細は、テ クニカル・ブリーフ <u>TB379</u> を参照してください。

- 5.  $\theta_{JC}$ の測定における「ケース温度」位置は、パッケージ下面のエキスポーズド金属パッドの中心です。

**電気的特性** 特記のない限り、T<sub>J</sub> = -40 ℃~ +125 ℃、V<sub>IN</sub> = 2.7V ~ 5.5V に対する値です。代表値は T<sub>A</sub> = +25 ℃に対する値で す。太字のリミット値は動作温度範囲 -40 ℃~ +85 ℃に対して適用されます。

| PARAMETER                                      | SYMBOL            | TEST CONDITIONS                                                                                    | MIN<br>(Note 6) | TYP    | MAX<br>(Note 6) | UNITS |

|------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------|-----------------|--------|-----------------|-------|

| INPUT SUPPLY                                   |                   |                                                                                                    |                 |        |                 |       |

| V <sub>IN</sub> Undervoltage Lockout Threshold | V <sub>UVLO</sub> | Rising, no load                                                                                    |                 | 2.5    | 2.7             | V     |

|                                                |                   | Falling, no load                                                                                   | 2.2             | 2.4    |                 | V     |

| Quiescent Supply Current                       | I <sub>VIN</sub>  | f <sub>SW</sub> = 1MHz, no load at the output                                                      |                 | 7      | 15              | mA    |

|                                                |                   | f <sub>SW</sub> = 2MHz, no load at the output                                                      |                 | 10     | 22              | mA    |

| Shutdown Supply Current                        | I <sub>SD</sub>   | V <sub>IN</sub> = 5.5V, EN = low                                                                   |                 | 1.2    | 10              | μA    |

| OUTPUT REGULATION                              |                   |                                                                                                    | '               |        |                 |       |

| Feedback Voltage                               | V <sub>FB</sub>   |                                                                                                    | 0.594           | 0.600  | 0.606           | V     |

|                                                | 10                | T <sub>J</sub> = -40 °C to +125 °C                                                                 | 0.589           |        | 0.606           | v     |

| VFB Bias Current                               | I <sub>VFB</sub>  | V <sub>FB</sub> = 2.7V, T <sub>J</sub> = -40°C to +125°C                                           | -350            | 50     | 350             | nA    |

| Line Regulation                                |                   | V <sub>IN</sub> = V <sub>O</sub> + 0.5V to 5.5V (nominal 3.6V)<br>T <sub>J</sub> = -40°C to +125°C | -0.32           | -0.05  | 0.28            | %/V   |

| Load Regulation                                |                   | See (Note 7)                                                                                       |                 | < -0.2 |                 | %/A   |

| Soft-start Ramp Time Cycle (Note 7)            |                   |                                                                                                    |                 | 1      |                 | ms    |

| PROTECTIONS                                    |                   |                                                                                                    |                 |        |                 |       |

| Positive Peak Current Limit                    | IPLIMIT           | 2A application (V <sub>IN</sub> = 3.6V)                                                            | 2.8             | 3.18   | 3.6             | Α     |

|                                                |                   | 1.5A application (V <sub>IN</sub> = 3.6V)                                                          | 2.1             | 2.5    | 2.9             | Α     |

| Thermal Shutdown                               |                   | Temperature rising                                                                                 |                 | 150    |                 | °C    |

| Thermal Shutdown Hysteresis (Note 7)           |                   | Temperature falling                                                                                |                 | 25     |                 | °C    |

| COMPENSATION                                   |                   |                                                                                                    |                 |        |                 |       |

| Error Amplifier Transconductance (Note 7)      |                   |                                                                                                    |                 | 40     |                 | μA/V  |

| Transresistance                                | RT                |                                                                                                    | 0.24            | 0.3    | 0.40            | Ω     |

| PHASE                                          | 10.               | <del>.</del>                                                                                       |                 |        |                 |       |

| P-channel MOSFET ON-resistance                 |                   | V <sub>IN</sub> = 5V, I <sub>O</sub> = 200mA                                                       |                 | 117    |                 | mΩ    |

| N-channel MOSFET ON-resistance                 |                   | V <sub>IN</sub> = 5V, I <sub>O</sub> = 200mA                                                       |                 | 86     |                 | mΩ    |

Submit Document Feedback intersil FN6692.2 2015年4月1日

## ISL80020, ISL80020A, ISL80015, ISL80015A

**電気的特性** 特記のない限り、T<sub>J</sub> = -40 °C ~ +125 °C、V<sub>IN</sub> = 2.7V ~ 5.5V に対する値です。代表値は T<sub>A</sub> = +25 °Cに対する値です。**太字のリミット値は動作温度範囲 -40 °C ~ +85 °Cに対して適用されます。(続き)**

| PARAMETER                       | SYMBOL          | TEST CONDITIONS      | MIN<br>(Note 6) | TYP  | MAX<br>(Note 6) | UNITS |

|---------------------------------|-----------------|----------------------|-----------------|------|-----------------|-------|

| OSCILLATOR                      |                 |                      |                 |      |                 |       |

| Nominal Switching Frequency     | fsw             | ISL80020, ISL80015   | 800             | 1000 | 1200            | kHz   |

|                                 |                 | ISL80020A, ISL80015A | 1640            | 2000 | 2360            | kHz   |

| PG                              | *               |                      |                 |      |                 |       |

| Output Low Voltage              |                 | 1mA sinking current  |                 |      | 0.3             | V     |

| Delay Time (Rising Edge)        |                 |                      | 0.5             | 1    | 2.5             | ms    |

| PGOOD Delay Time (Falling Edge) |                 |                      |                 | 5    |                 | μs    |

| PG Pin Leakage Current          |                 | PG = V <sub>IN</sub> |                 | 0.01 | 0.1             | μΑ    |

| OVP PG Rising Threshold         |                 |                      | 110             | 115  | 125             | %     |

| OVP PG Hysteresis               |                 |                      |                 | 2    |                 | %     |

| UVP PG Rising Threshold         |                 |                      | 80              | 85   | 90              | %     |

| UVP PG Hysteresis               |                 |                      |                 | 5    |                 | %     |

| EN LOGIC                        |                 |                      |                 |      |                 |       |

| Logic Input Low                 |                 |                      |                 |      | 0.4             | V     |

| Logic Input High                |                 |                      | 1.4             |      |                 | V     |

| Logic Input Leakage Current     | I <sub>EN</sub> | Pulled up to 5.5V    |                 | 0.1  | 1               | μA    |

#### NOTE:

- 6. MIN パラメータと MAX パラメータは、特記のない限り +25 ℃で全数試験を行っています。温度のリミット値は特性評価によって定められたものであり、製造時テストは行われていません。

- 7. 製造時テストは実施していません。評価用ボードを用いた特性評価による値です。負荷レギュレーションのグラフ (図  $8\sim11$ ) を参照してください。 105  $^{\circ}$   $^{\circ}$

## 代表的な性能曲線

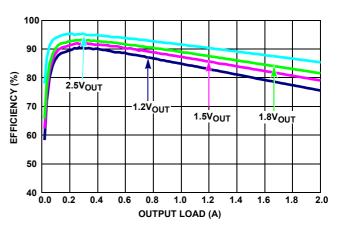

図 5. 効率 vs 負荷、f<sub>SW</sub> = 2MHz、V<sub>IN</sub> = 3.3V、T<sub>A</sub> = +25 ℃

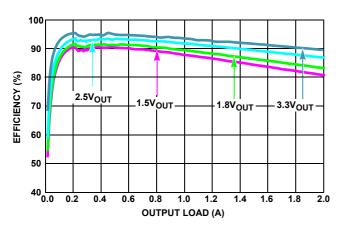

図 6. 効率 vs 負荷、f<sub>SW</sub> = 1MHz、V<sub>IN</sub> = 5V、T<sub>A</sub> = +25 ℃

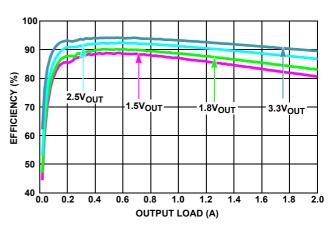

図 7. 効率 vs 負荷、f<sub>SW</sub> = 2MHz、V<sub>IN</sub> = 5V、T<sub>A</sub> = +25 ℃

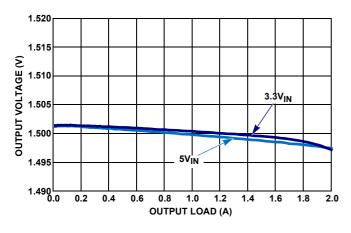

図 8. V<sub>OUT</sub> レギュレーション vs 負荷、f<sub>SW</sub> = 2MHz、 V<sub>OUT</sub> = 1.5V、T<sub>A</sub> = +25 ℃

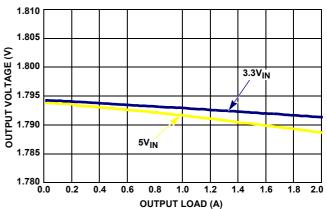

図 9. V<sub>OUT</sub> レギュレーション vs 負荷、f<sub>SW</sub> = 2MHz、 V<sub>OUT</sub> = 1.8V、T<sub>A</sub> = +25 ℃

## 代表的な性能曲線(続き)

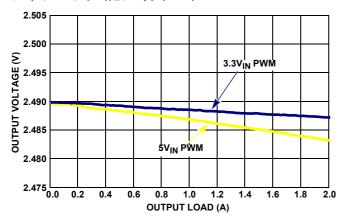

図 10. V<sub>OUT</sub> レギュレーション vs 負荷、f<sub>SW</sub> = 2MHz、 V<sub>OUT</sub> = 2.5V、T<sub>A</sub> = +25 ℃

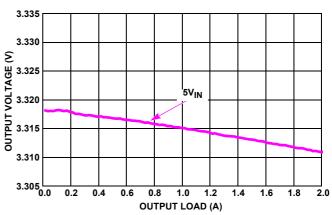

図 11. V<sub>OUT</sub> レギュレーション vs 負荷、f<sub>SW</sub> = 2MHz、 V<sub>OUT</sub> = 3.3V、T<sub>A</sub> = +25 ℃

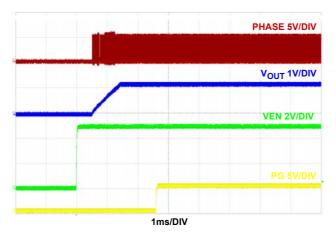

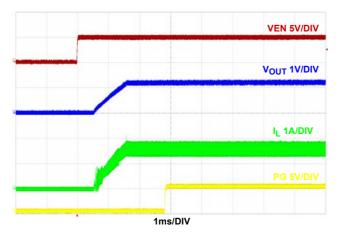

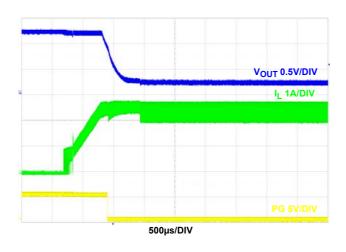

図 12. 無負荷時のスタートアップ、f<sub>SW</sub> = 2MHz、V<sub>IN</sub> = 5V、 T<sub>A</sub> = +25 <sup>°</sup>C

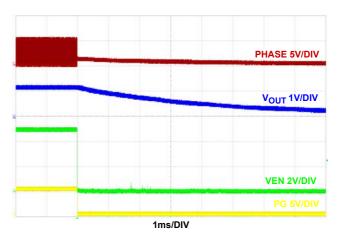

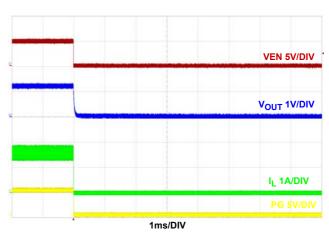

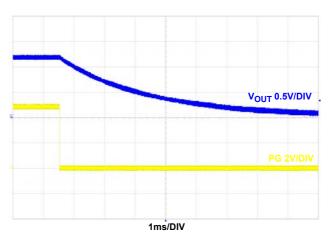

図 13. 無負荷時のシャットダウン、f<sub>SW</sub> = 2MHz、V<sub>IN</sub> = 5V、 T<sub>A</sub> = +25 ℃

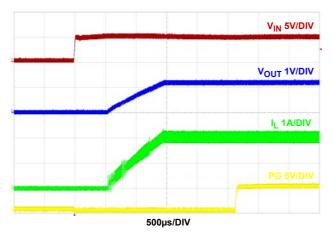

図 14. 2A 負荷時のスタートアップ、f<sub>SW</sub> = 2MHz、V<sub>IN</sub> = 5V、 T<sub>A</sub> = +25 ℃

図 15. 2A 負荷時のシャットダウン、f<sub>SW</sub> = 2MHz、V<sub>IN</sub> = 5V、 T<sub>A</sub> = +25 ℃

## 代表的な性能曲線(続き)

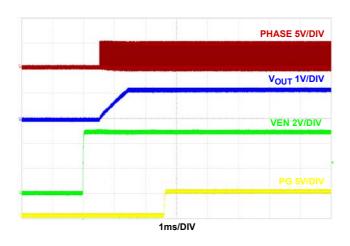

図 16. 1.5A 負荷時のスタートアップ、f<sub>SW</sub> = 2MHz、  $V_{IN} = 5V$ ,  $T_A = +25$  °C

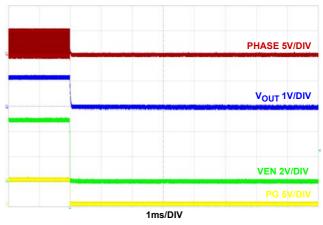

図 17. 1.5A 負荷時のシャットダウン、f<sub>SW</sub> = 2MHz、  $V_{IN} = 5V$ ,  $T_A = +25$  °C

図 18. 2A 負荷時のスタートアップ V<sub>IN</sub>、f<sub>SW</sub> = 2MHz、 V<sub>IN</sub> = 5V, T<sub>A</sub> = +25 ℃

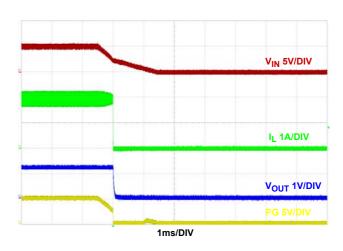

図 19. 2A 負荷時のシャットダウン V<sub>IN</sub>、f<sub>SW</sub> = 2MHz、  $V_{IN} = 5V$ ,  $T_A = +25$  °C

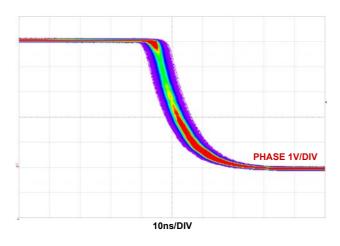

図 20. 無負荷時のジッタ、f<sub>SW</sub> = 2MHz、V<sub>IN</sub> = 5V、T<sub>A</sub> = +25 ℃

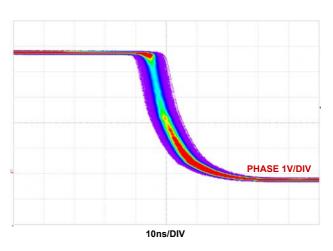

図 21. フル負荷時のジッタ、f<sub>SW</sub> = 2MHz、V<sub>IN</sub> = 5V、T<sub>A</sub> = +25 ℃

FN6692.2 Submit Document Feedback intersil

# 代表的な性能曲線(続き)

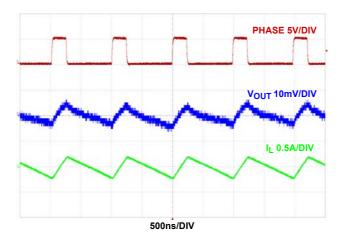

図 22. 無負荷時の定常状態、f<sub>SW</sub> = 2MHz、V<sub>IN</sub> = 5V、 T<sub>A</sub> = +25 ℃

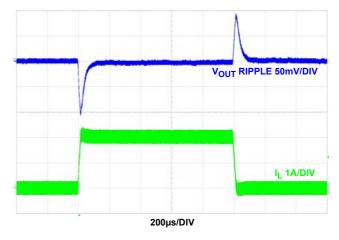

図 23. 負荷変動、f<sub>SW</sub> = 2MHz、V<sub>IN</sub> = 5V、T<sub>A</sub> = +25 ℃

図 24. 過電流保護、f<sub>SW</sub> = 2MHz、V<sub>IN</sub> = 5V、T<sub>A</sub> = +25 ℃

図 25. 過熱保護、 $f_{SW}$  = 2MHz、 $V_{IN}$  = 5V、 $T_A$  = +163  $^{\circ}$ C

## 動作原理

この製品はバッテリ駆動のアプリケーションに対して最適化された降圧スイッチング・レギュレータです。高いスイッチング周波数 (1MHz または 2MHz) で動作するため、より低インダクタンスのインダクタを使用でき、外形寸法の縮小と同時に高い効率を実現します。レギュレータがシャットダウンされているときの標準的な静止電流はわずか 1.2μA です。

#### PWM 制御方式

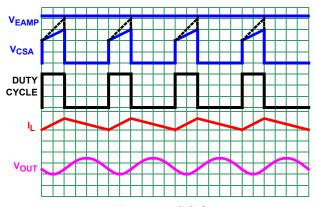

高速負荷応答とパルスごとの電流リミットを実現するため、本製品は電流モード・パルス幅変調 (PWM) 制御方式を採用しています。4ページの「機能ブロック図」を参照してください。電流ループは、発振器、PWM コンパレータ、電流検出回路、電流ループを安定させるための傾き補償回路によって構成されています。傾き補償は900mV/Tsです。この値は周波数に従って変化します。電流検出回路のゲインは通常300mV/Aです。電流ループの制御リファレンスは、誤差アンプ (EAMP)の出力によって供給されます。

PWM 動作は、発振器からのクロックによって初期化されます。PWM サイクルの開始時に P チャネル MOSFET がターンオンし、MOSFET 内の電流がランプアップしはじめます。電流アンプ (CSA) と傾き補償の和が電流ループの制御リファレンスに達すると、PWM コンパレータ (COMP) は PWM ロジックに信号を送り、P-FET をターンオフ、N チャネル MOSFET をターンオンします。N-FET は PWM サイクルの終りまでオンのままです。図 26 に、PWM 動作中の代表的な動作波形を示します。点線は、傾き補償ランプと電流検出アンプ (CSA)の出力の和を表します。

図 26. PWM 動作波形

リファレンス電圧は 0.6V です。この電圧は誤差アンプの出力 VEAMP を調整するために帰還回路で使用します。誤差アンプは、電圧誤差信号を電流出力に変換するトランスコンダクタンス・アンプです。電圧ループは 27pF および  $200k\Omega$  のRC ネットワークにより内部補償されています。 EAMP の最大出力電圧は、高精度で 1.6V にクランプされます。

#### 過電流保護

4ページの「機能ブロック図」に示すとおり、過電流保護は OCP コンパレータによって CSA 出力をモニタリングすることで実現しています。電流検出回路による、P-FET 電流から CSA 出力へのゲインは 300mV/A です。CSA 出力がスレッショルドに達すると、OCP コンパレータがトリップして、ただちに P-FET をターンオフします。過電流機能は、上側の MOSFET を通して流れる電流をモニタリングすることで、出力短絡からスイッチング・コンバータを保護します。

過電流状態を検出すると、上側 MOSFET がただちにターン オフし、次のスイッチング・サイクルまでは再ターンオンし ません。過電流状態が解消されると、出力はレギュレーショ ン・ポイントに復帰します。

#### 短絡保護

短絡保護 (SCP) コンパレータは出力短絡から製品を保護するために VFB ピンの電圧をモニタリングします。VFB が 0.3V を下回ると、SCP コンパレータは PWM 発振器の周波数を強制的に通常動作時の値の 1/3 に低下させます。このコンパレータは、スタートアップ時または出力短絡時に有効になります。

### 負電流保護

過電流と同様に、負電流保護は、ローサイド N-FET を流れる電流をモニタリングすることで実現されます (4 ページの「機能ブロック図」参照 )。インダクタ電流の最小値 (谷底点) が連続する 2 つのサイクルで -1.5A に達すると、P-FET と N-FET の両方が遮断されます。 N-FET に並列接続された  $100\Omega$  の抵抗が出力をレギュレーション値に放電しはじめます。出力がレギュレーション範囲内に入ると、制御回路がスイッチングを開始します。

### PG

PG は降圧型レギュレータの出力電圧を連続的にモニタリングするウィンドウ・コンパレータの出力です。PG は EN が Low の期間、および降圧型レギュレータのソフトスタートの期間、アクティブに Low に保持されます。 ソフトスタート期間から Ims の遅延が経過すると、出力電圧が VFB によって設定される公称レギュレーション電圧内にある限り、PG はハイ・インピーダンスになります。 VFB が公称レギュレーション電圧から 15% 低下するか、上回ると PG が Low に引き下げられます。すべてのフォルト状態は、ソフトスタートによってクリアされるまで、PG を強制的に Low に引き下げます。ほとんどのアプリケーションに適した5M $\Omega$ のプルアップ抵抗が内蔵されています。 PG から VIN に外付けの抵抗を追加することでプルアップ力を強化できます。

#### **UVLO**

入力電圧がアンダーボルテージ・ロックアウト (UVLO) スレッショルドを下回ると、レギュレータがディスエーブルされます。

#### イネーブル、ディスエーブル、ソフト・スタートアップ

VINピンが立ち上がりPORトリップ・ポイント(公称値2.5V)を超えると、本製品は動作を開始します。ENピンが外部的にLowに維持されている場合は、ENピンが解放されるまで動作は開始されません。ENが解放され、論理スレッショルドを上回った後の内部ソフトスタート時間のデフォルト値は1msです。

Submit Document Feedback 12 intersil\* FN6692.2 2015 年 4 月 1 日

### 放電モード(ソフトストップ)

シャットダウン・モードへの遷移または VIN~UVLO~ が発生すると、内部の  $100\Omega~$  スイッチを介して出力が GND~ に放電されます。

#### サーマル・シャットダウン

本製品は、サーマル・プロテクションを内蔵しています。内部温度が+150℃に達すると、レギュレータは完全にシャットダウンされます。温度が+125℃を下回ると、ソフトスタートの手順を経て製品は動作を再開します。

### 電力ディレーティング特性

製品が最高ジャンクション温度を超えないように、何らかの 熱解析が必要です。温度上昇は<u>式 2</u>で表されます。

$$T_{RISE} = (PD)(\theta_{JA})$$

(式2)

ここで、PD はレギュレータの電力損失、 $\theta_{JA}$  はダイのジャンクションから周囲温度への熱抵抗です。ジャンクション温度  $(T_J)$  は式 3 で求められます。

$$T_{J} = (T_A + T_{RISE}) \tag{33}$$

ここで、 $T_A$  は周囲温度です。DFN パッケージの  $\theta_{JA}$  は  $+71\,^{\circ}$  C /W です。

温度設計を行うとき、実際のジャンクション温度は絶対最高 ジャンクション温度の+125℃を上回ってはなりません。

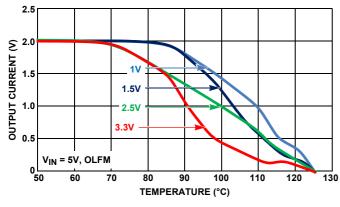

サーマルパッドからの熱インピーダンスによってジャンクション温度がサーマル・シャットダウン・レベルよりも低く抑えられていれば、製品は最高周囲温度 85℃まで、入力電圧/出力電圧の組み合わせおよびスイッチング周波数に応じたフル電流を供給します。ジャンクション温度をサーマル・シャットダウン・レベル以下に維持するには、製品の電力損失を小さくする必要があります。図 27に、ISL80020EVAL1Zキットを使用した場合の、周囲温度に対するおおよその出力電流ディレーティング曲線を示します。

図 27. ディレーティング曲線 vs 温度

## アプリケーション情報

### 出力インダクタおよびコンデンサの選択

定常状態と過渡動作を考慮して、ISL80020A と ISL80015A には通常  $1.2\mu H$  が必要です。一方、ISL80020 と ISL80015 は、通常  $2.2\mu H$  の出力インダクタを必要とします。コンバータ・システムの総合性能を最適化するために、これらより高いまたは低いインダクタ値を使用することも可能です。例えば、出力電圧がより高い 3.3V のアプリケーションの場合、インダクタのリップル電流と出力電圧リップルを低減するために、出力インダクタの値を大きくできます。最適性能を得るために、インダクタ・リップル電流は最大出力電流の約 30%に設定することを推奨します。インダクタ・リップル電流は、式 4によって表されます。

$$\Delta I = \frac{V_O \cdot \left(1 - \frac{V_O}{V_{IN}}\right)}{L \cdot f_{SW}} \tag{\pm 4}$$

インダクタの飽和電流定格は、少なくともピーク電流より大きくなければなりません。

製品は内部補償ネットワークを使用しており、出力コンデンサの値は出力電圧に依存します。セラミック・コンデンサは X5R または X7R を推奨します。

#### 出力電圧の選択

レギュレータの出力電圧は外付けの抵抗分圧回路を使用して 設定できます。抵抗分圧回路は内部リファレンス電圧を基準 に出力電圧をスケーリングし、その電圧を誤差アンプの反転 入力に帰還します。

出力電圧設定抵抗  $R_1$  は、帰還抵抗およびレギュレータの目標出力電圧として選択した値に依存します。帰還抵抗は<u>式 5</u>, に示すとおり、通常は  $10k\Omega\sim 100k\Omega$  の間の値です。

$$R_1 = R_2 \left( \frac{V_O}{VFB} - 1 \right) \tag{£5}$$

目標出力電圧が 0.6V の場合、 $R_2$  には抵抗を接続せず、 $R_1$  は 短絡します。 VIN から PHASE にはリーク電流が流れます。 出力には、あらかじめ  $10\mu A$  以上の負荷を接続しておくことを推奨します。性能を向上するには、 $R_1$  に並列に 22pF を追加します。.

### 入力コンデンサの選択

入力コンデンサの主な機能は、寄生インダクタンスのデカップリングと、スイッチング電流のバッテリ・レールへの逆流を防ぐフィルタリングです。入力コンデンサの選択では、最低 2 個の  $22\mu F$  の X5R または X7R セラミック・コンデンサから検討を始めるとよいでしょう。

Submit Document Feedback 13 intersil\* FN6692.2 2015 年 4 月 1 日

### 出力コンデンサの選択

出力コンデンサはインダクタ電流のフィルタリングに必要 です。出力コンデンサの選択肢を検討する場合、出力リップ ル電圧と過渡応答の2つが重要な要因となります。電流モー ド制御ループであることから低 ESR のセラミック・コンデ ンサを使用でき、ボード・レイアウトが縮小されます。電解 コンデンサやポリマ・コンデンサも使用可能です。

セラミック・コンデンサにはそのほかにも考慮事項がありま す。セラミック・コンデンサは優れた総合性能と信頼性を示 しますが、回路内での実際の容量値を考慮する必要がありま す。セラミック・コンデンサの定格は、大きなピーク・ツー・ ピーク電圧振幅とDCバイアスなしの条件で規定されていま す。DC/DC コンバータ・アプリケーションの場合、このよ うな条件は実情に即していません。その結果、実際の容量値 が公称値より著しく低くなる場合があります。アプリケー ション内での実際の容量値を判断するには、メーカーのデー タシートを参照してください。ほとんどのメーカーが DC バ イアスに対する容量値の特性を公開しているため、この効果 には簡単に対処できます。AC 電圧による効果が公開される ことはまれですが、通常さらに約20%容量値が減少するも のと仮定すれば十分です。このような検討では、実効的な容 量値がすぐに定格値より 50% 減少してしまう場合がありま す。それでも、信頼性が高く、ESR が極めて低いことから、 セラミック・コンデンサは多くのアプリケーションにとって 優れた選択肢です。

式 6 と 1 から、目標リップル電圧レベルを満たすために必要 な容量値を計算できます。容量の追加も可能です。

セラミック・コンデンサ(低ESR)の場合:

$$V_{OUTripple} = \frac{\Delta I}{8*f_{SW}*C_{OUT}}$$

(式 6)

ここで、AI はインダクタのピークツーピーク・リップル電 流、 $f_{SW}$  はスイッチング周波数、 $C_{OUT}$  は出力コンデンサの 容量値です。

電解コンデンサを使用する場合は、次式で計算します。

$$V_{OUTripple} = \Delta I^*ESR$$

(式 7)

過渡応答の要件についての検討は、負荷が突然取り去られ た場合に許容される  $V_{OUT}$  のオーバーシュートを決定する ことから始めるとよいでしょう。この場合、インダクタに 蓄えられたエネルギーは COUT に転送され、その電圧が上 昇します。リップルおよび過渡応答の両方の要件から必要 な容量値を計算し、その結果の大きい方を選択します。 式 8 から、レギュレート電圧に対する目標オーバーシュー トを実現するために必要なコンデンサの値が決まります。

$$C_{OUT} = \frac{I_{OUT}^{2} \cdot L}{V_{OUT}^{2} \cdot (V_{OUTMAX}/V_{OUT})^{2} - 1)}$$

(式 8)

ここで、VOUTMAX/VOUTは、負荷切り離し時に許容される 最大オーバーシュートの相対値です。オーバーシュートが 5% の場合の式は、次の通りです。<u>式 9</u>:

$$C_{OUT} = \frac{I_{OUT}^{2*L}}{V_{OUT}^{2*(1.05^2 - 1)}}$$

(式 9)

### レイアウトに関する考慮事項

設計するコンバータの適切な動作を保証する上で、PCB レイ アウトは極めて重要な設計段階となります。パワー・ループ は、出力インダクタの L、出力コンデンサの COUT、PHASE ピン、PGND ピンから構成されます。パワー・ループはでき るだけ小さくし、短く太いトレースで直接接続する必要があ ります。コンバータのスイッチング・ノード、PHASE ピン、 ノードに接続するトレースには大きなノイズが乗るため、電 圧帰還のトレースは、これらのノイズの多いトレースから離 します。入力コンデンサは VIN ピンと入力のグラウンドので きるだけ近くに配置し、出力コンデンサはできるだけ近くに 接続する必要があります。ICの熱は主にサーマルパッドを 介して放熱されます。サーマルパッドに接続する銅エリアを 最大化することを推奨します。さらに、ベタグラウンド層は EMI 性能の向上に役立ちます。放熱を最適化するために、 パッド内に4個以上のビアによるグラウンド接続を追加する ことを推奨します。

FN6692.2

Submit Document Feedback intersil 2015年4月1日

## ISL80020、ISL80020A、ISL80015、ISL80015A

## 改訂履歴

この改訂履歴は参考情報として掲載するものであり、正確を期すように努めていますが、内容を保証するものではありません。最新 のデータシートは、インターシルのウェブサイトでご確認ください。

| 日付         | レビジョン    | <b>変更点</b>                                                                                                   |

|------------|----------|--------------------------------------------------------------------------------------------------------------|

| 2015年4月1日  | FN6692.2 | 12 ページの「動作原理」で、標準的な静止電流値を「5μA」から「1.2μA」に変更。<br>12 ページの「イネーブル、ディスエーブル、ソフト・スタートアップ」で、公称値を「2.7V」から<br>「2.5V」に変更 |

| 2015年2月17日 | FN6692.1 | 電気的特性の表の VFB Bias Current の MIN 値を -120 から -350 に変更。                                                         |

| 2015年2月5日  | FN6692.0 | 初版                                                                                                           |

## インターシルについて

インターシルは、革新的なパワーマネジメントと高精度アナログ・ソリューションのプロバイダとして世界をリードしてい ます。インターシルの製品は、産業用機器 / インフラ、モバイル・コンピューティング、ハイエンド・コンシューマの分野で 特に規模の大きな市場向けに開発されています。

最新のデータシート、アプリケーション・ノート、関連ドキュメント、関連製品については、www.intersil.com の各製品情報 ページを参照してください。

本データシートに対するご意見は www.intersil.com/ask にお寄せください。

信頼性に関するデータも www.intersil.com/support に掲載されています。

そのほかの製品については www.intersil.com/product\_tree/を参照してください。

インターシルは、www.intersil.com/design/quality/に記載の品質保証のとおり、ISO9000 品質システムに基づいて、製品の製造、組み立て、試験を行っています。

インターシルは、製品を販売するにあたって、製品情報のみを提供します。インターシルは、いかなる時点においても、予告なしに、回路設計、ソフ トウェア、仕様を変更する権利を有します。製品を購入されるお客様は、必ず、データシートが最新であることをご確認くださいますようお願いいた します。インターシルは正確かつ信頼に足る情報を提供できるよう努めていますが、その使用に関して、インターシルおよび関連子会社は責を負いま せん。また、その使用に関して、第三者が所有する特許または他の知的所有権の非侵害を保証するものではありません。インターシルおよび関連子会 社が所有する特許の使用権を暗黙的または他の方法によって与えるものではありません。

インターシルの会社概要については www.intersil.com をご覧ください。

Submit Document Feedback intersil FN6692.2 2015年4月1日

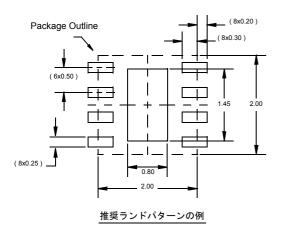

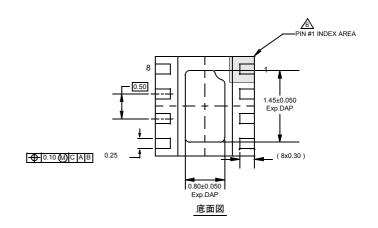

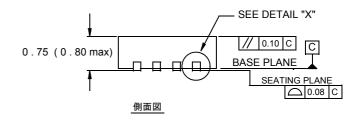

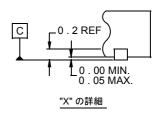

## パッケージ寸法図

### L8.2x2C

# 8 LEAD THIN DUAL FLAT NO-LEAD PLASTIC PACKAGE (TDFN) WITH E-PAD Rev 0, 07/08

### NOTE:

- 1. 寸法の単位は mm です。 ()内の寸法は参考値です。

- 2. 寸法と公差は AMSE Y14.5m-1994 に従っています。

- 3. 特記のない限り、公差は DECIMAL± 0.05 です。

- 4. 寸法 b は金属端子に適用され、端子先端から 0.15mm ~ 0.30mm のポイントで計測した値です。

- 5. タイバー(示されている場合)は非機能性です。

- 6. 1 ピンの識別子はオプションですが、表示されている ゾーン内に配置されます。1 ピンの識別子はモールド またはマーキングで示されます。

Submit Document Feedback 16 intersil