## ISL71043M, ISL71041M

Radiation Tolerant Single-Ended Current Mode PWM Controllers

The ISL71043M and ISL71041M are PWM controllers suitable for a wide range of power conversion applications including boost, flyback, and isolated output configurations. Fast signal propagation and output switching characteristics make these ideal products for existing and new designs.

Features include up to 13.2V operation, 2.9mA operating current, 90µA typical start-up current, adjustable operating frequency to 1MHz and, 1A current drive capability with 35ns rise and 29ns fall times.

The ISL71041M and ISL71043M are available in an 8 LD TDFN package and the ISL71043M is also available in an 8 LD SOIC package. Both packages are specified across the extended temperature range of -55°C to +125°C.

### **Applications**

- Current mode switching power supplies

- Isolated buck and flyback regulators

- Boost regulators

- Direction and speed control in motors

- Control of high current FET drivers

#### **Features**

- Qualified to Renesas Rad Tolerant Screening and QCI Flow (R34TB0004EU)

- 1A MOSFET gate driver

- 90µA typical start-up current, 500µA maximum

- 35ns propagation delay current sense to output

- Fast transient response with Peak Current mode control

- 9V to 13.2V operation

- Adjustable switching frequency to 1MHz

- 35ns rise time and 29ns fall time with 1nF output load

- Trimmed timing capacitor discharge current for accurate dead time/maximum duty cycle control

- 1.5MHz bandwidth error amplifier

- Tight tolerance voltage reference over line, load, and temperature

- ±3% current limit threshold

- Ni/Pd/Au-Ag lead finish (Sn-free, Pb-free)

- TID Radiation Lot Acceptance Testing (LDR: ≤10mrad(Si)/s)

- ISL71041M30 and ISL71043M30: 30krad(Si)

- ISL71041M50 and ISL71043M50: 50krad(Si)

- SEE Characterization

- No DSEE for VDD = 14.7V and 43MeV•cm<sup>2</sup>/mg

- · SET only lasted one PWM pulse

Table 1. Key Differences Between Family of Parts

| Part Number | Rising UVLO (V) | Maximum Duty Cycle (%) | Packages Available   |

|-------------|-----------------|------------------------|----------------------|

| ISL71041M   | 7.0             | 50                     | 8 Ld TDFN            |

| ISL71043M   | 8.4             | 100                    | 8 Ld TDFN, 8 Ld SOIC |

# **Contents**

| 1. | Over       | rview      |                                                   | 3    |

|----|------------|------------|---------------------------------------------------|------|

|    | 1.1<br>1.2 | ٠.         | Application Schematics                            |      |

| 2. |            |            | on                                                |      |

|    | 2.1        |            | ignments                                          |      |

|    | 2.2        |            | scriptions                                        |      |

| 3. | Spec       | cification | 's                                                | 7    |

|    | 3.1        |            | e Maximum Ratings                                 |      |

|    | 3.2        |            | Specifications                                    |      |

|    | 3.3        | Therma     | Specifications                                    | 7    |

|    | 3.4        | Recomm     | mended Operating Conditions                       | 8    |

|    | 3.5        | Electric   | al Specifications                                 | 8    |

|    |            | 3.5.1      | ISL71041M Radiation Acceptance Test Limits        | . 10 |

| 4. | Турі       | cal Perfo  | rmance Curves                                     | . 11 |

| 5. | Fund       | ctional D  | escription                                        | . 13 |

|    | 5.1        | Feature    | es                                                | . 13 |

|    | 5.2        | Oscillat   | or                                                | . 13 |

|    | 5.3        | Soft-Sta   | art Operation                                     | . 13 |

|    | 5.4        | Gate Dr    | rive                                              | . 13 |

|    | 5.5        | •          | Compensation                                      |      |

|    | 5.6        |            | onditions                                         |      |

|    | 5.7        | Ground     | Plane Requirements                                | . 16 |

| 6. | Radi       | ation Tol  | lerance                                           | . 17 |

|    | 6.1        | Total lo   | nizing Dose (TID) Testing                         | . 17 |

|    |            | 6.1.1      | Introduction                                      | . 17 |

|    |            | 6.1.2      | Results                                           |      |

|    |            | 6.1.3      | Typical Radiation Performance                     |      |

|    |            | 6.1.4      | Conclusion                                        |      |

|    | 6.2        | •          | Event Effects Testing                             |      |

|    |            | 6.2.1      | SEE Test Facility                                 |      |

|    |            | 6.2.2      | SEE Test Setup                                    |      |

|    |            | 6.2.3      | Single Event Burnout and Latch-Up (SEB/L) Results |      |

|    |            | 6.2.4      | SET Results                                       |      |

|    |            | 6.2.5      | Conclusion                                        |      |

| 7. |            | •          | line Drawings                                     |      |

| 8. | Orde       | ering Info | ormation                                          | . 26 |

| 9. | Revi       | sion Hist  | tory                                              | . 27 |

R34DS0003EU0505 Rev.5.05 Dec 17, 2025

## 1. Overview

# 1.1 Typical Application Schematics

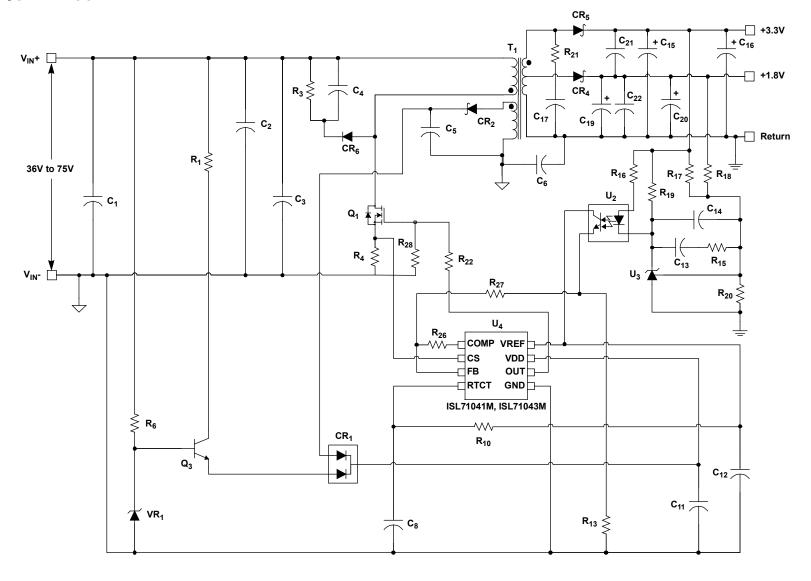

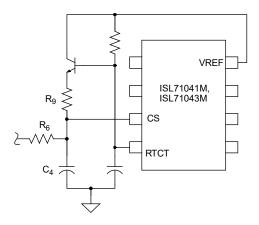

Figure 1. 48V Input Dual Output Flyback

ISL71043M, ISL71041M Datasheet

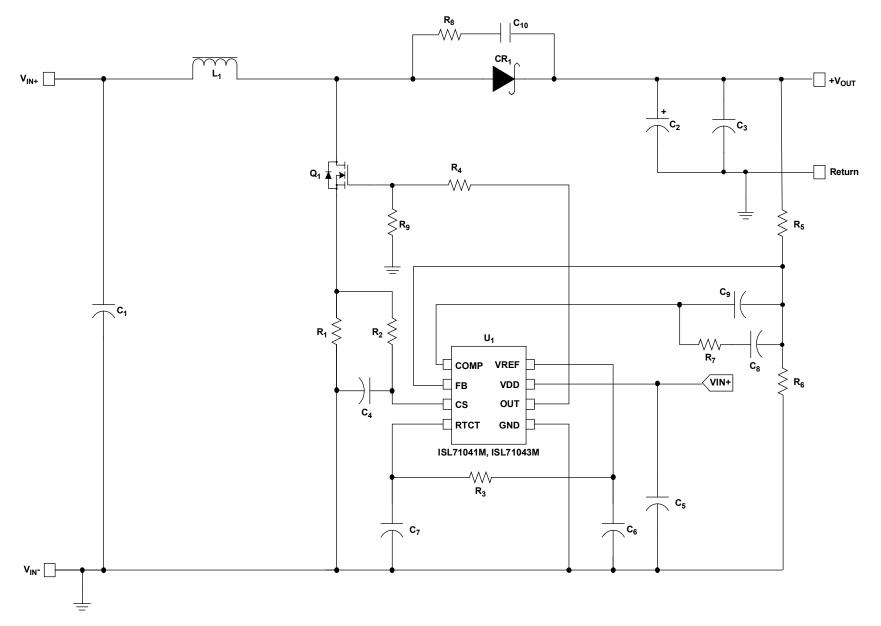

Figure 2. Boost Converter

# 1.2 Functional Block Diagram

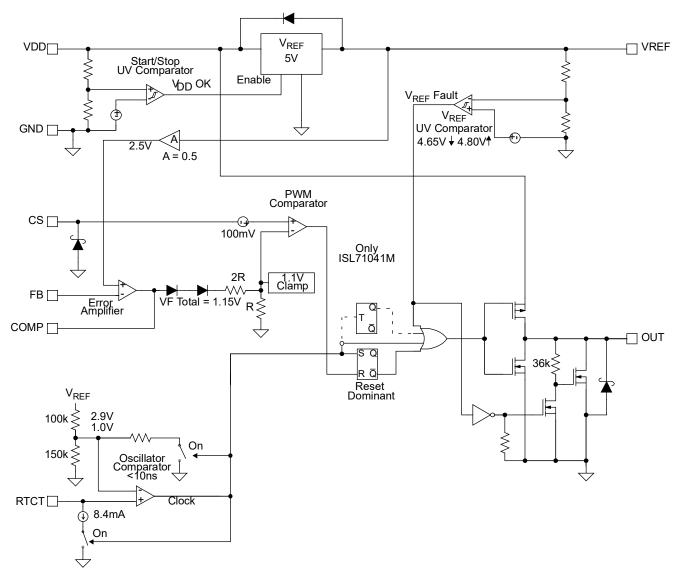

Figure 3. Block Diagram

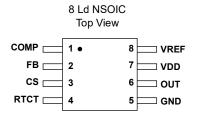

# 2. Pin Information

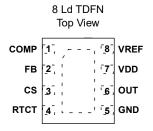

# 2.1 Pin Assignments

# 2.2 Pin Descriptions

| Pin # | Pin<br>Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | COMP        | The output of the error amplifier and the input of the PWM comparator. The control loop frequency compensation network is connected between the COMP and FB pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2     | FB          | The output voltage feedback is connected to the inverting input of the error amplifier through this pin. The noninverting input of the error amplifier is internally tied to a reference voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3     | CS          | The current sense input to the PWM comparator. The range of the input signal is nominally 0V to 1.0V and has an internal offset of 100mV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

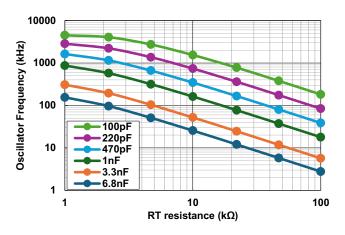

| 4     | RTCT        | The oscillator timing control pin. Set the operational frequency and maximum duty cycle by connecting a resistor, RT, between VREF and this pin and a timing capacitor, CT, from this pin to GND. The oscillator produces a sawtooth waveform with a programmable frequency range up to 1.0MHz. The charge time, $t_C$ , the discharge time, $t_D$ , the RTCT oscillator frequency, f, and the maximum duty cycle, $D_{MAX}$ , can be approximated using Equation 1 through Equation 4: $(EQ.\ 1) \qquad t_C \approx 0.56 \times RT \times CT$ $(EQ.\ 2) \qquad t_D \approx 30 \times 10^{-9} + \frac{1.8 \times CT}{0.008 - \frac{3.125}{RT}}$ $(EQ.\ 3) \qquad f = 1/(t_C + t_D)$ $(EQ.\ 4) \qquad D = t_C \times f$ The equations have increased error at higher frequencies due to propagation delays. Figure 4 can be used as a guideline in selecting the capacitor and resistor values required for a given oscillator frequency for the ISL71041M and ISL71043M. Use the spreadsheet calculator tool on the product page to estimate the switching frequency from typical bench test data. |

| 5     | GND         | GND is the power and small signal reference ground for all functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6     | OUT         | The drive output to the power switching device. This high current output is able to drive the gate of a power MOSFET with peak currents of 1.0A. This GATE output is actively held low when V <sub>DD</sub> is below the UVLO threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7     | VDD         | The power connection for the device. The total supply current depends on the load applied to OUT. The total $I_{DD}$ current is the sum of the operating current and the average output current. Use the operating frequency, f, and the MOSFET gate charge, Qg, to calculate the average output current using Equation 5: $(EQ. 5) \qquad I_{OUT} = Qg \times f$ To optimize noise immunity, bypass VDD to GND with a ceramic capacitor as close to the VDD and GND pins as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8     | VREF        | The 5.00V reference voltage output. ±2% tolerance over line, load, and operating temperature. The recommended bypass to GND capacitor is in the range 0.1µF to 0.22µF. A typical value of 0.15µF can be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| -     | EPAD        | Applicable to TDFN package only.  The exposed pad should be connected externally to GND. Put as many vias as possible in this pad connecting to other PCB layers to improve heat dissipation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

# 3. Specifications

## 3.1 Absolute Maximum Ratings

**Caution:** Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

| Parameter                                                 | Minimum   | Maximum               | Unit |

|-----------------------------------------------------------|-----------|-----------------------|------|

| V <sub>DD</sub>                                           | GND - 0.3 | +30.0                 | V    |

| V <sub>DD</sub> [1]                                       | GND - 0.3 | +14.7                 | V    |

| OUT                                                       | GND - 0.3 | V <sub>DD</sub> + 0.3 | V    |

| Signal Pins                                               | -         | 6.0                   | V    |

| Peak Current on OUT                                       | -         | 1                     | Α    |

| Maximum Junction Temperature                              | -         | +150                  | °C   |

| Maximum Storage Temperature Range                         | -65       | +150                  | °C   |

| Human Body Model (Tested per JS-001-2017)                 | -         | 1.5                   | kV   |

| Machine Model (Tested per JESD22-A115C)                   | -         | 200                   | V    |

| Charged Device Model (Tested per JS-002-2014)             | -         | 1                     | kV   |

| Latch-Up (Tested per JESD-78E; Class 2, Level A) at 125°C | -         | 100                   | mA   |

<sup>1.</sup> Tested in a heavy ion environment at LET = 43MeV•cm<sup>2</sup>/mg at +125°C (TC) for SEB.

# 3.2 Outgas Specifications

| Specification (Tested per ASTM E595, 1.5)              | Value | Unit |

|--------------------------------------------------------|-------|------|

| Total Mass Loss <sup>[1]</sup>                         | 0.06  | %    |

| Collected Volatile Condensible Material <sup>[1]</sup> | <0.01 | %    |

| Water Vapor Recovered                                  | 0.03  | %    |

<sup>1.</sup> Outgassing results meet NASA requirement soft total mass loss <1% and collected volatile condensible material of <0.1%.

# 3.3 Thermal Specifications

| Parameter          | Package               | Symbol                         | Conditions          | Typical<br>Value | Unit |

|--------------------|-----------------------|--------------------------------|---------------------|------------------|------|

|                    | 8 Ld SOIC Package     | θ <sub>JA</sub> [1]            | Junction to ambient | 105              |      |

| Thermal Resistance | o Eu SOIO Fackage     | θ <sub>JC</sub> <sup>[2]</sup> | Junction to case    | 50               | °C/W |

| memai Resistance   | 8 Ld 4x4 TDFN Package | θ <sub>JA</sub> [3]            | Junction to ambient | 41               | C/VV |

|                    | 0 Lu 4X4 TDFN Fackage | θ <sub>JC</sub> <sup>[4]</sup> | Junction to case    | 2.5              |      |

<sup>1.</sup>  $\theta_{JA}$  is measured in free air with the component mounted on a high-effective thermal conductivity test board in free air. See <u>TB379</u>.

<sup>2.</sup> For  $\theta_{\text{JC}}$ , the case temperature location is the package top center.

θ<sub>JA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with direct attach features.

See TB379.

<sup>4.</sup> For  $\theta_{JC}$ , the case temperature location is the center of the exposed metal pad on the package underside.

# 3.4 Recommended Operating Conditions

| Parameter   | Minimum | Maximum | Unit |

|-------------|---------|---------|------|

| $V_{DD}$    | 9       | 13.2    | V    |

| Temperature | -55     | +125    | °C   |

# 3.5 Electrical Specifications

Recommended operating conditions unless otherwise noted.  $V_{DD}$  = 13.2V,  $R_{T}$  = 10k $\Omega$ ,  $C_{T}$  = 3.3nF,  $T_{A}$  = -55°C to +125°C. Typical values are at  $T_{A}$  = +25°C. **Boldface limits apply across the operating temperature range, -55°C to +125°C.**

| Parameter                                        | Symbol                  | Test Conditions                                                 | Min <sup>[1]</sup> | Тур  | Max <sup>[1]</sup> | Unit |

|--------------------------------------------------|-------------------------|-----------------------------------------------------------------|--------------------|------|--------------------|------|

| Undervoltage Lockout                             |                         | ,                                                               | 1                  |      | 1                  |      |

| Start Threshold                                  | 10/10/1/                | ISL71041M                                                       | 6.5                | 7.0  | 7.5                | V    |

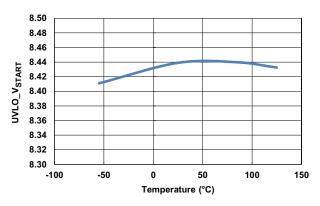

| Start Threshold                                  | UVLO_V <sub>START</sub> | ISL71043M                                                       | 8.0                | 8.4  | 9.0                | V    |

| Stop Threshold                                   | 111/1/07/1/             | ISL71041M                                                       | 6.1                | 6.7  | 6.9                | V    |

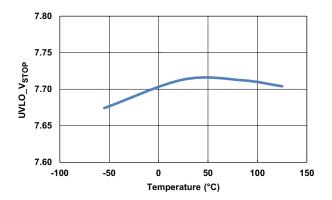

| Stop Threshold                                   | UVLO_V <sub>STOP</sub>  | ISL71043M                                                       | 7.3                | 7.6  | 8.0                | V    |

| Hysteresis                                       | LIV/LO Hyot             | ISL71041M                                                       | -                  | 0.4  | -                  | V    |

| Hysteresis                                       | UVLO_Hyst               | ISL71043M                                                       | -                  | 0.8  | -                  | V    |

| Start-Up Current, I <sub>DD</sub>                | I <sub>DDSu</sub>       | V <sub>DD</sub> < Start Threshold                               | -                  | 90   | 500                | μA   |

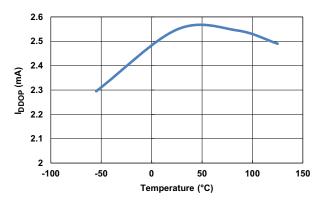

| Operating Current, I <sub>DD</sub>               | I <sub>DDOp</sub>       |                                                                 | -                  | 2.9  | 4.0                | mA   |

| Operating Supply Current, I <sub>D</sub>         | IDO <sub>p_LOAD</sub>   | Includes 1nF GATE loading                                       | -                  | 4.7  | 5.5                | mA   |

| Operating Supply Current, ID                     | I <sub>DDq</sub>        | [2]                                                             | -                  | 2.9  | 4.0                | mA   |

| Reference Voltage                                |                         |                                                                 |                    |      |                    |      |

| Overall Accuracy V <sub>REF</sub>                |                         | Over line (V <sub>DD</sub> = 9V to 13.2V), load of 1mA and 10mA | 4.925              | 5.0  | 5.050              | V    |

| Long Term Stability [3]                          | V <sub>REF_ST</sub>     | T <sub>A</sub> = +125°C, 1000 hours                             | -                  | 5    | -                  | mV   |

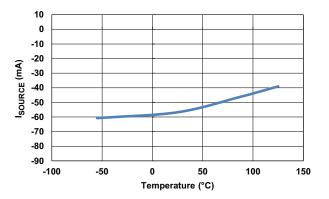

| Current Limit, Sourcing                          | I <sub>SOURCE</sub>     |                                                                 | -20                | -40  | -                  | mA   |

| Current Limit, Sinking                           | I <sub>SINK</sub>       |                                                                 | 5                  | 20   | -                  | mA   |

| Current Sense                                    |                         |                                                                 |                    |      |                    |      |

| Input Bias Current                               | CS_I <sub>BIAS</sub>    | V <sub>CS</sub> = 1V                                            | -1.0               | -    | 1.0                | μA   |

| Input Signal, Maximum                            | VMAX_IN                 |                                                                 | 0.97               | 1.00 | 1.03               | V    |

| Gain, $A_{CS} = \Delta V_{COMP} / \Delta V_{CS}$ | COMP_Gain               | 0 < V <sub>CS</sub> < 910mV, V <sub>FB</sub> = 0V               | 2.75               | 2.82 | 3.15               | V/V  |

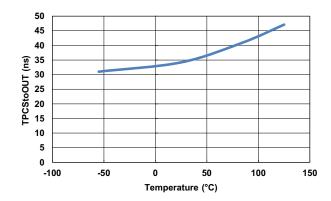

| CS to OUT Delay                                  | TPCStoOUT               |                                                                 | -                  | 35   | 60                 | ns   |

| Error Amplifier                                  |                         |                                                                 |                    |      |                    |      |

| Open Loop Voltage Gain                           | AVOL                    |                                                                 | -                  | 90   | -                  | dB   |

| Unity Gain Bandwidth                             | UGB                     |                                                                 | -                  | 1.5  | -                  | MHz  |

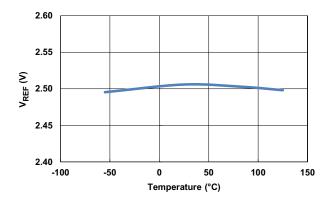

| Reference Voltage, V <sub>REF</sub>              | EA_V <sub>REF</sub>     | $V_{FB} = V_{COMP}$                                             | 2.475              | 2.5  | 2.530              | V    |

| FB Input Bias Current, FBI <sub>IB</sub>         | FB_I <sub>BIAS</sub>    | V <sub>FB</sub> = 0V                                            | -1.5               | -0.2 | 1.5                | μΑ   |

| COMP Sink Current                                | COMP_I <sub>OL</sub>    | V <sub>COMP</sub> = 1.5V, V <sub>FB</sub> = 2.7V                | 1.0                | 5    | -                  | mA   |

| COMP Source Current                              | COMP_I <sub>OH</sub>    | V <sub>COMP</sub> = 1.5V, V <sub>FB</sub> = 2.3V                | -0.4               | -0.5 | -                  | mA   |

| COMP V <sub>OH</sub>                             | COMP_V <sub>OH</sub>    | V <sub>FB</sub> = 2.3V                                          | 4.80               | -    | V <sub>REF</sub>   | V    |

Recommended operating conditions unless otherwise noted.  $V_{DD}$  = 13.2V,  $R_{T}$  = 10k $\Omega$ ,  $C_{T}$  = 3.3nF,  $T_{A}$  = -55°C to +125°C. Typical values are at  $T_{A}$  = +25°C. **Boldface limits apply across the operating temperature range, -55°C to +125°C. (Cont.)**

| Parameter                                | Symbol                | Test Conditions                                   | Min <sup>[1]</sup> | Тур  | Max <sup>[1]</sup> | Unit |

|------------------------------------------|-----------------------|---------------------------------------------------|--------------------|------|--------------------|------|

| COMP V <sub>OL</sub>                     | COMP_V <sub>OL</sub>  | V <sub>FB</sub> = 2.7V                            | 0.4                | -    | 1.0                | V    |

| Power Supply Rejection Ratio             | PSRR                  | Frequency = 120Hz, V <sub>DD</sub> = 9V to 13.2V  | -                  | 80   | -                  | dB   |

| Oscillator                               | •                     |                                                   | '                  |      |                    | !    |

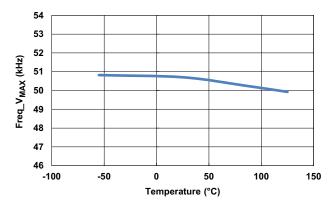

| Frequency Accuracy                       | Freq_V <sub>MAX</sub> | Initial, T <sub>A</sub> = +25°C                   | 48                 | 51   | 54                 | kHz  |

| Frequency Variation with V <sub>DD</sub> | Freq_PSRR             | $T_A$ = +25°C, $(f_{13.2V} - f_{9V})/f_{12V}$     | -1.0               | 0.2  | 1.0                | %    |

| Temperature Stability <sup>[3]</sup>     |                       |                                                   | -                  | 5    | -                  | %    |

| Amplitude, Peak-to-Peak                  | RTCTVpp               | Static Test -                                     |                    | 1.75 | -                  | V    |

| RTCT Valley Voltage                      | RTCTV <sub>DIS</sub>  | Static Test                                       | -                  | 1.0  | -                  | V    |

| Discharge Current                        | RTCTI <sub>DIS</sub>  | RTCT = 2.0V                                       | 6.5                | 7.8  | 8.5                | mA   |

| Output                                   | •                     |                                                   | '                  |      |                    |      |

| Gate V <sub>OH</sub> <sup>[4]</sup>      | V <sub>OH</sub>       | V <sub>DD</sub> to OUT, I <sub>OUT</sub> = -100mA | -                  | 0.5  | 1.0                | V    |

| Gate V <sub>OL</sub> <sup>[4]</sup>      | V <sub>OL</sub>       | OUT to GND, I <sub>OUT</sub> = 100mA              | -                  | 0.5  | 1.0                | V    |

| Gate V <sub>OH</sub> <sup>[4]</sup>      | V <sub>OH</sub>       | V <sub>DD</sub> to OUT, I <sub>OUT</sub> = -8mA   | -                  | 40   | 80                 | mV   |

| Gate V <sub>OL</sub> <sup>[4]</sup>      | V <sub>OL</sub>       | OUT to GND, I <sub>OUT</sub> = 8mA                | -                  | 40   | 80                 | mV   |

| Peak Output Current <sup>[3]</sup>       | I <sub>OPK</sub>      | C <sub>OUT</sub> = 1nF                            | -                  | 1.0  | -                  | Α    |

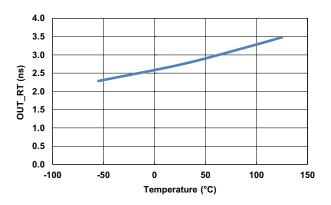

| Rise Time                                | OUT_RT                | C <sub>OUT</sub> = 1nF                            | -                  | 35   | 60                 | ns   |

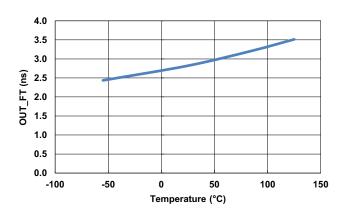

| Fall Time                                | OUT_FT                | C <sub>OUT</sub> = 1nF                            | -                  | 29   | 40                 | ns   |

| Output Off State Leakage                 | IDoff                 | V <sub>DD</sub> = 5V                              | -                  | -    | 50                 | μΑ   |

| PWM                                      | •                     |                                                   | '                  | !    | !                  | !    |

| Maximum Duty Cycle                       | MAX Duty              | COMP = V <sub>REF</sub> (ISL71041M)               | 47                 | 48   | 50                 | %    |

| waximum buty Cycle                       | IVIAA_Duty            | COMP = V <sub>REF</sub> (ISL71043M)               | <b>94</b> 96 -     |      | -                  | 70   |

| Minimum Duty Cycle                       | MIN_Duty              | COMP = GND                                        | -                  |      | 0                  | %    |

<sup>1.</sup> Parameters with Min and/or Max limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

<sup>2.</sup> This is the  $V_{DD}$  current consumed when the device is active but not switching. Does not include gate drive current.

<sup>3.</sup> Compliance to limits is assured by characterization and design.

<sup>4.</sup> See ISL71041M Radiation Acceptance Test Limits for the ISL71043M test limits for this specification.

#### 3.5.1 **ISL71041M Radiation Acceptance Test Limits**

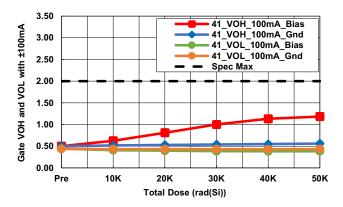

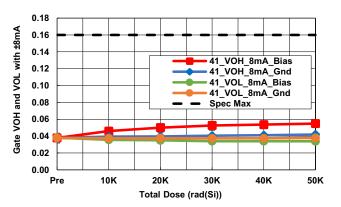

ISL71041M LDR acceptance testing is held to the same electrical specifications as the Electrical Specifications, except for the expanded limits below. Typical values of key parameters after 50krad(Si) are shown in Table 4.

Recommended operating conditions unless otherwise noted.  $V_{DD}$  = 13.2V,  $R_T$  = 10k $\Omega$ ,  $C_T$  = 3.3nF. Typical values are at  $T_A$  = +25°C. Boldface limits apply over a total ionizing dose of 50krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s

| Parameter            | Symbol          | Test Conditions                                   | Min <sup>[1]</sup> ) | Тур | Max <sup>[1]</sup> | Uni<br>t |

|----------------------|-----------------|---------------------------------------------------|----------------------|-----|--------------------|----------|

| Output               |                 |                                                   |                      |     |                    |          |

| Gate V <sub>OH</sub> | V <sub>OH</sub> | V <sub>DD</sub> to OUT, I <sub>OUT</sub> = -100mA |                      | 0.8 | 2.0                | V        |

| Gate V <sub>OL</sub> | V <sub>OL</sub> | OUT to GND, I <sub>OUT</sub> = 100mA              |                      | 0.5 | 2.0                | V        |

| Gate V <sub>OH</sub> | V <sub>OH</sub> | V <sub>DD</sub> to OUT, I <sub>OUT</sub> = -8mA   |                      | 50  | 160                | mV       |

| Gate V <sub>OL</sub> | V <sub>OL</sub> | OUT to GND, I <sub>OUT</sub> = 8mA                |                      | 40  | 160                | mV       |

<sup>1.</sup> Parameters with Min and/or Max limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

# 4. Typical Performance Curves

95% 90% RTCT Frequency (kHz) 85% 80% 75% 70% 3.3nF 1nF 65% 470pF 60% 220pF 55% 100pF 50% 100 10 RT resistance ( $k\Omega$ )

100%

Figure 4. Oscillator Frequency versus RT and CT values

Figure 5. Maximum Oscillator Duty Cycle versus RT and CT values

Figure 6. Start Threshold Over Temperature

Figure 7. Stop Threshold Over Temperature

Figure 8. Rise Time Over Temperature

Figure 9. Fall Time Over Temperature

Figure 10. Frequency Accuracy Over Temperature

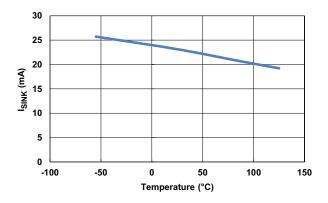

Figure 12. Current Limit, Sinking Over Temperature

Figure 14. Reference Voltage Over Temperature

**Figure 11. Operating Current Over Temperature**

Figure 13. Current Limit, Sourcing Over Temperature

Figure 15. CS to Out Delay Over Temperature

#### 5. **Functional Description**

#### 5.1 **Features**

The ISL71041M and ISL71043M current mode PWM makes them an ideal choice for low-cost flyback and forward topology applications.

#### 5.2 Oscillator

The ISL71041M and ISL71043M devices have a sawtooth oscillator with a programmable frequency range to 1MHz that can be programmed with a resistor from VREF and a capacitor to GND on the RTCT pin (see Figure 4 for the resistor and capacitance required for a given frequency).

#### 5.3 Soft-Start Operation

Soft-start must be implemented externally. Figure 16 shows one method that clamps the voltage on COMP.

Figure 16. Soft-Start

The COMP pin is clamped to the voltage on capacitor C<sub>1</sub> plus a base-emitter junction by transistor Q<sub>1</sub>. C<sub>1</sub> is charged from VREF through resistor R<sub>1</sub> and the base current of Q<sub>1</sub>. At power-up, C<sub>1</sub> is fully discharged, COMP is at ~0.7V, and the duty cycle is zero. As C<sub>1</sub> charges, the voltage on COMP increases and the duty cycle increases in proportion to the voltage on C<sub>1</sub>. When COMP reaches the steady-state operating point, the control loop takes over and soft-start is complete. C<sub>1</sub> continues to charge up to V<sub>REF</sub> and no longer affects COMP. During power-down, diode D<sub>1</sub> quickly discharges C<sub>1</sub> so that the soft-start circuit is properly initialized before the next power-on sequence.

#### 5.4 **Gate Drive**

The ISL71041M and ISL71043M devices are capable of sourcing and sinking 1A peak current. An optional external resistor can be placed between the totem-pole output of the IC (OUT pin) and the gate of the MOSFET to limit the peak current through the IC. This small series resistor also damps any oscillations caused by the resonant tank of the parasitic inductances in the traces of the board and the FET's input capacitance.

#### 5.5 Slope Compensation

For applications where the maximum duty cycle is less than 50%, slope compensation can be used to improve noise immunity, particularly at lighter loads. The amount of slope compensation required for noise immunity is determined empirically, but is generally about 10% of the full scale current feedback signal. For applications where the duty cycle is greater than 50%, slope compensation is required to prevent instability.

Slope compensation can be accomplished by adding an external ramp to the current feedback signal or by subtracting the external ramp from the voltage feedback error signal. Adding the external ramp to the current feedback signal is the more popular method.

The small signal current-mode model<sup>[1]</sup> shows that the naturally-sampled modulator gain, Fm, without slope compensation is calculated in Equation 6:

(EQ. 6)

$$Fm = \frac{1}{S_n t_{SW}}$$

where  $S_n$  is the slope of the sawtooth signal and  $t_{SW}$  is the duration of the half-cycle. When an external ramp is added, the modulator gain becomes Equation 7:

(EQ. 7)

$$Fm = \frac{1}{(S_n + S_e)t_{SW}} = \frac{1}{m_c S_n t_{SW}}$$

where S<sub>e</sub> is the slope of the external ramp and becomes Equation 8:

(EQ. 8)

$$m_c = 1 + \frac{S_e}{S_n}$$

The criteria for determining the correct amount of external ramp can be determined by appropriately setting the damping factor of the double-pole located at the switching frequency. The double-pole is critically damped if the Q-factor is set to 1, over-damped for Q < 1, and under-damped for Q > 1. An under-damped condition can result in current loop instability.

(EQ. 9)

$$Q = \frac{1}{\pi(m_c(1-D)-0.5)}$$

where D is the percent of on-time during a switching cycle. Setting Q = 1 and solving for Se yields Equation 10:

**(EQ. 10)**

$$S_e = S_n \left( \left( \frac{1}{\pi} + 0.5 \right) \frac{1}{1 - D} - 1 \right)$$

Because  $S_n$  and  $S_e$  are the on-time slopes of the current ramp and the external ramp, respectively, they can be multiplied by  $t_{ON}$  to obtain the voltage change that occurs during  $t_{ON}$ .

(EQ. 11)

$$V_e = V_n \left( \left( \frac{1}{\pi} + 0.5 \right) \frac{1}{1 - D} - 1 \right)$$

V

where  $V_n$  is the change in the current feedback signal ( $\Delta I$ ) during the on-time and  $V_e$  is the voltage that must be added by the external ramp.

For a flyback converter,  $V_n$  can be solved in terms of input voltage, current transducer components, and primary inductance, yielding Equation 12:

(EQ. 12)

$$V_e = \frac{D \cdot t_{SW} \cdot V_{IN} \cdot R_{CS}}{L_D} \left( \left( \frac{1}{\pi} + 0.5 \right) \frac{1}{1 - D} - 1 \right)$$

$V_e = \frac{D \cdot t_{SW} \cdot V_{IN} \cdot R_{CS}}{L_D} \left( \frac{1}{\pi} + 0.5 \right) \frac{1}{1 - D} - 1 \right)$

where  $R_{CS}$  is the current sense resistor,  $t_{SW}$  is the switching period,  $L_p$  is the primary inductance,  $V_{IN}$  is the minimum input voltage, and D is the maximum duty cycle.

The current sense signal at the end of the ON time for CCM operation is Equation 13:

(EQ. 13)

$$V_{CS} = \frac{N_S \cdot R_{CS}}{N_p} \left( I_O + \frac{(1-D) \cdot V_O \cdot t_{sw}}{2L_s} \right)$$

V

<sup>1.</sup> Ridley, R., A New Continuous-Time Model for Current Mode Control, IEEE Transactions on Power Electronics, Vol. 6, No. 2, April 1991.

where  $V_{CS}$  is the voltage across the current sense resistor,  $L_s$  is the secondary winding inductance, and  $I_O$  is the output current at current limit. Equation 13 assumes the voltage drop across the output rectifier is negligible.

Because the peak current limit threshold is 1V, the total current feedback signal plus the external ramp voltage must sum to this value when the output load is at the current limit threshold as shown in Equation 14:

(EQ. 14)

$$V_e + V_{CS} = 1V$$

Substituting Equation 12 and Equation 13 into Equation 14 and solving for R<sub>CS</sub> yields Equation 15:

(EQ. 15)

$$R_{CS} = \frac{1}{\frac{D \cdot T_{sw} \cdot V_{IN}}{L_{p}} \cdot \left(\frac{\frac{1}{\pi} + 0.5}{1 - D} - 1\right) + \frac{N_{s}}{N_{p}} \cdot \left(I_{O} + \frac{(1 - D) \cdot V_{O} \cdot t_{sw}}{2L_{s}}\right)}$$

Add slope compensation in the ISL71041M and ISL71043M devices using an external buffer transistor and the RTCT signal. A typical application sums the buffered RTCT signal with the current sense feedback and applies the result to the CS pin as shown in Figure 17.

Figure 17. Slope Compensation

Assuming the designer has selected values for the RC filter ( $R_6$  and  $C_4$ ) placed on the CS pin, the value of  $R_9$  required to add the appropriate external ramp can be found by superposition.

(EQ. 16)

$$V_e = \frac{2.05D \cdot R_6}{R_6 + R_0}$$

V

The factor of 2.05 in Equation 16 arises from the peak amplitude of the sawtooth waveform on RTCT minus a base-emitter junction drop. That voltage multiplied by the maximum duty cycle is the voltage source for the slope compensation. Rearranging to solve for  $R_9$  yields Equation 17:

(EQ. 17)

$$R_9 = \frac{(2.05D - V_e) \cdot R_6}{V_e}$$

$\Omega$

The value of  $R_{CS}$  determined in Equation 15 must be rescaled so that the current sense signal presented at the CS pin is that predicted by Equation 13. The divider created by  $R_6$  and  $R_9$  makes this necessary.

(EQ. 18)

$$R'_{CS} = \frac{R_6 + R_9}{R_9} \cdot R_{CS}$$

Example:

$V_{IN}$  = 12V,  $V_{O}$  = 48V,  $L_{s}$  = 800 $\mu$ H, Ns/Np = 10, Lp = 8.0 $\mu$ H,  $I_{O}$  = 200mA, switching frequency,  $f_{SW}$  = 200kHz duty cycle, D = 28.6%,  $R_{6}$  = 499 $\Omega$

Solve for the current sense resistor, R<sub>CS</sub>, using Equation 15.

$R_{CS} = 295 m\Omega$

Determine the amount of voltage, V<sub>e</sub>, that must be added to the current feedback signal using Equation 12.

$V_{e} = 92.4 \text{mV}$

Use Equation 17 to solve for the summing resistor, R<sub>9</sub>, from CT to CS.

$R_9 = 2.67k\Omega$

Determine the new value of R<sub>CS</sub> (R'<sub>CS</sub>) using Equation 18.

$R'_{CS} = 350 m\Omega$

Additional slope compensation may be considered for design margin. The previous discussion determines the minimum external ramp that is required. The buffer transistor that creates the external ramp from RTCT should have a sufficiently high gain (>200) to minimize the required base current. Whatever base current is required reduces the charging current into RTCT and reduces the oscillator frequency.

#### 5.6 Fault Conditions

A Fault condition occurs if  $V_{REF}$  falls below 4.65V. When a Fault is detected, OUT is disabled. When  $V_{REF}$  exceeds 4.80V, the Fault condition clears and OUT is enabled.

## 5.7 Ground Plane Requirements

Careful layout is essential for satisfactory operation of the device. A good ground plane must be used. A unique section of the ground plane must be designated for high di/dt currents associated with the output stage. Bypass VDD directly to GND with good high frequency capacitors.

### 6. Radiation Tolerance

The ISL71041M and ISL71043M are radiation tolerant devices for commercial space applications, Low Earth Orbit (LEO) applications, high altitude avionics, launch vehicles, and other harsh environments. The response of these devices to Total Ionizing Dose (TID) radiation effects and Single-Event Effects (SEE) have been measured, characterized, and reported as described in the following sections. The TID performance of the ISL71043MBZ, ISL71043MRTZ and the ISL71041MRTZ are not guaranteed through radiation acceptance testing. The ISL71041M30RTZ and ISL71043M30BZ are radiation lot acceptance tested (RLAT) to 30krad(Si). The ISL71041M50RTZ and ISL71043M50BZ are RLAT to 50krad(Si).

## 6.1 Total Ionizing Dose (TID) Testing

#### 6.1.1 Introduction

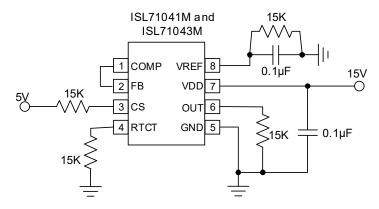

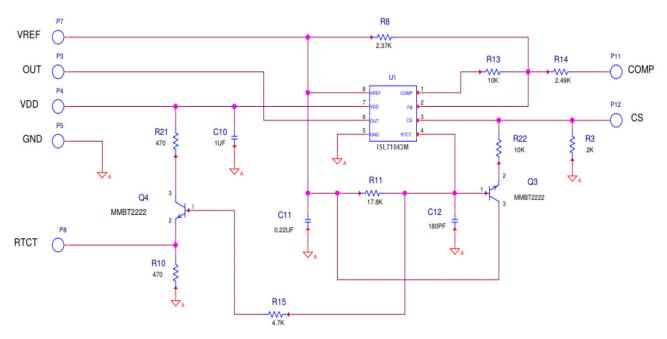

These tests were conducted to determine the sensitivity of the parts to the total dose environment. Total dose testing was performed using a Hopewell Designs N40 panoramic irradiator. Irradiations were performed at 0.00875rad(Si)/s. A PbAI box was used to shield the test fivgure and devices under test against low energy secondary gamma radiation. Test downpoints for both part-types were 0krad(Si), 10krad(Si), 20krad(Si), 30krad(Si), 40krad(Si), and 50krad(Si). The characterization matrix for the ISL71041M consisted of 7 samples irradiated under bias and 7 samples irradiated with all pins grounded. The characterization matrix for the ISL71043M consisted of 24 samples irradiated under bias and 12 samples irradiated with all pins grounded for downpoints 0krad(Si), 10krad(Si), 20krad(Si), and 30krad(Si); 5 samples irradiated under bias, and 5 samples irradiated with all pins grounded for the 50krad(Si) downpoint, with no downpoints between 0krad(Si) and 50krad(Si). Four control units for each part were used to ensure repeatable data. Two different wafers for each part were used. The bias configuration is shown in Figure 18.

Figure 18. Irradiation Bias Configuration

All electrical testing was performed outside the irradiator using the production Automated Test Equipment (ATE), with data logging at each downpoint (including anneal). Downpoint electrical testing was performed at room temperature.

#### 6.1.2 Results

Table 2 and Table 3 summarize the attributes data. Bin 1 indicates a device that passes all device specification limits.

Table 2. ISL71041M Total Dose Test Attributes Data

| Dose Rate (mrad(Si)/s) | Bias      | Sample Size | Downpoint  | Bin1 | Rejects |

|------------------------|-----------|-------------|------------|------|---------|

|                        |           |             | Pre-rad    | 7    | 0       |

|                        |           |             | 10krad(Si) | 7    | 0       |

| 8.75                   | Figure 18 | 7           | 20krad(Si) | 7    | 0       |

|                        | Figure 16 | ,           | 30krad(Si) | 7    | 0       |

|                        |           |             | 40krad(Si) | 7    | 0       |

|                        |           |             | 50krad(Si) | 7    | 0       |

|                        | Grounded  | 7           | Pre-rad    | 7    | 0       |

|                        |           |             | 10krad(Si) | 7    | 0       |

| 8.75                   |           |             | 20krad(Si) | 7    | 0       |

| 0.75                   |           |             | 30krad(Si) | 7    | 0       |

|                        |           |             | 40krad(Si) | 7    | 0       |

|                        |           |             | 50krad(Si) | 7    | 0       |

Table 3. ISL71043M Total Dose Test Attributes Data

| Dose Rate (mrad(Si)/s) | Bias      | Sample Size | Downpoint  | Bin1 | Rejects |

|------------------------|-----------|-------------|------------|------|---------|

|                        |           |             | Pre-rad    | 24   | 0       |

|                        |           | 24          | 10krad(Si) | 24   | 0       |

| 8.75                   | Figure 18 | 24          | 20krad(Si) | 24   | 0       |

|                        |           |             | 30krad(Si) | 24   | 0       |

|                        |           | 5           | 50krad(Si) | 5    | 0       |

|                        | Grounded  |             | Pre-rad    | 12   | 0       |

|                        |           | 12          | 10krad(Si) | 12   | 0       |

| 8.75                   |           | 12          | 20krad(Si) | 12   | 0       |

|                        |           |             | 30krad(Si) | 12   | 0       |

|                        |           | 5           | 50krad(Si) | 5    | 0       |

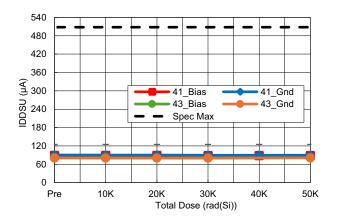

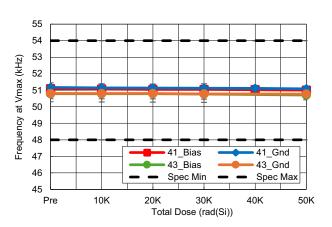

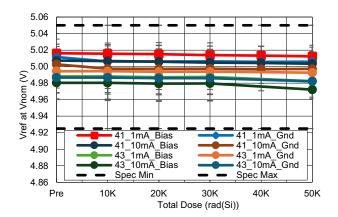

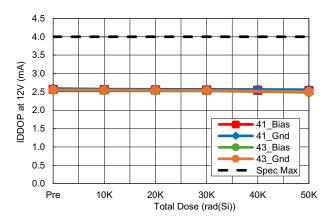

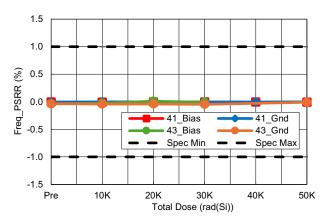

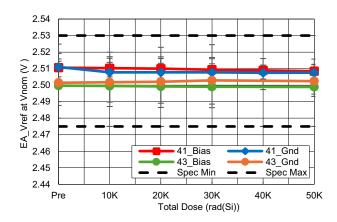

Figure 19 through Figure 26 show data for key parameters at all downpoints. The plots show the average as a function of total dose for each of the irradiation conditions. Error bars show the minimum and maximum tested values. All parts showed excellent stability over irradiation.

### 6.1.3 Typical Radiation Performance

Figure 19. Start-Up Current vs TID

Figure 21. Frequency Accuracy vs TID

Figure 23. Reference Voltage Accuracy vs TID

Figure 20. Operating Current vs TID

Figure 22. Frequency Variation with  $V_{DD}$  vs TID

Figure 24. Error Amplifier Reference Voltage vs TID

Figure 25. 100mA Gate Drive vs TID

Figure 26. 8mA Gate Drive vs TID

### 6.1.4 Conclusion

ATE characterization testing showed no rejects to the datasheet limits at all downpoints. Variables data for selected parameters is presented in Figure 19 through Figure 26. No differences between biased and unbiased irradiation were noted, and the part is not considered bias sensitive.

Table 4. ISL71041M Response of Key Parameters vs TID

| Parameter             | Symbol            | Condition | Bias   | 0krad(Si) | 10krad(Si) | 20krad(Si) | 30krad(Si) | 40krad(Si) | 50krad(Si) | Unit  |   |

|-----------------------|-------------------|-----------|--------|-----------|------------|------------|------------|------------|------------|-------|---|

| Start-Up              |                   |           | Bias   | 89.016    | 88.940     | 88.789     | 88.618     | 88.449     | 88.185     | μA    |   |

| Current               | I <sub>DDSu</sub> | -         | GND    | 90.447    | 90.059     | 90.020     | 89.939     | 89.866     | 89.655     | μA    |   |

|                       |                   | 9V        | Bias   | 2.523     | 2.515      | 2.511      | 2.505      | 2.499      | 2.492      | mA    |   |

|                       |                   |           | GND    | 2.547     | 2.528      | 2.525      | 2.523      | 2.518      | 2.514      | mA    |   |

| Operating             | 1                 | 12V       | Bias   | 2.568     | 2.560      | 2.556      | 2.550      | 2.544      | 2.537      | mA    |   |

| Current               | I <sub>DDOp</sub> | 120       | GND    | 2.592     | 2.574      | 2.570      | 2.568      | 2.564      | 2.559      | mA    |   |

|                       |                   | 13.2V     | Bias   | 2.579     | 2.571      | 2.567      | 2.561      | 2.555      | 2.548      | mA    |   |

|                       |                   | 10.20     | GND    | 2.604     | 2.585      | 2.582      | 2.579      | 2.575      | 2.570      | mA    |   |

| Frequency             | Freq              | 13.2V     | Bias   | 51.093    | 51.068     | 51.053     | 51.046     | 51.032     | 51.004     | kHz   |   |

| Accuracy              | rieq              | 13.20     | GND    | 51.172    | 51.141     | 51.134     | 51.124     | 51.113     | 51.086     | kHz   |   |

| Frequency             | Freq_             |           | Bias   | -0.005    | -0.006     | -0.005     | -0.003     | -0.004     | -0.006     | %     |   |

| Variation<br>with VDD | PSRR              | -         | GND    | -0.005    | -0.002     | -0.001     | -0.005     | -0.005     | -0.003     | %     |   |

|                       |                   | 1mA       | Bias   | 5.016     | 5.016      | 5.015      | 5.014      | 5.013      | 5.012      | V     |   |

| Voltage               | V                 | IIIIA     | GND    | 5.012     | 5.006      | 5.006      | 5.006      | 5.006      | 5.006      | V     |   |

| Reference             | $V_{REF}$         | 10mA      | Bias   | 5.007     | 5.007      | 5.006      | 5.005      | 5.004      | 5.004      | V     |   |

|                       |                   |           | TOTTIA | GND       | 5.003      | 4.997      | 4.997      | 4.997      | 4.997      | 4.997 | V |

| Error Amp             | EA_               | EA_       | 12V    | Bias      | 2.511      | 2.510      | 2.510      | 2.509      | 2.509      | 2.508 | V |

| Reference             | VREF              | 120       | GND    | 2.511     | 2.508      | 2.508      | 2.508      | 2.507      | 2.508      | V     |   |

|                       |                   | -100mA    | Bias   | 0.501     | 0.625      | 0.810      | 1.001      | 1.132      | 1.183      | V     |   |

| Cata                  | V <sub>OH</sub>   |           | GND    | 0.500     | 0.517      | 0.530      | 0.540      | 0.548      | 0.561      | V     |   |

| Gate V <sub>OH</sub>  | V OH              | -8mA      | Bias   | 0.038     | 0.046      | 0.050      | 0.053      | 0.054      | 0.055      | V     |   |

|                       |                   | -011174   | GND    | 0.038     | 0.039      | 0.040      | 0.040      | 0.041      | 0.042      | V     |   |

Table 4. ISL71041M Response of Key Parameters vs TID (Cont.)

| Parameter            | Symbol          | Condition | Bias | 0krad(Si) | 10krad(Si) | 20krad(Si) | 30krad(Si) | 40krad(Si) | 50krad(Si) | Unit  |       |       |   |

|----------------------|-----------------|-----------|------|-----------|------------|------------|------------|------------|------------|-------|-------|-------|---|

| Gate V <sub>OL</sub> | V <sub>OL</sub> | 100mA     | Bias | 0.442     | 0.409      | 0.396      | 0.386      | 0.382      | 0.383      | V     |       |       |   |

|                      |                 |           | GND  | 0.439     | 0.432      | 0.431      | 0.429      | 0.428      | 0.434      | V     |       |       |   |

|                      |                 | ▼ OL      | *OL  | VOL.      | 8mA        | Bias       | 0.038      | 0.036      | 0.035      | 0.034 | 0.034 | 0.034 | V |

|                      |                 |           |      | OITIA     | GND        | 0.038      | 0.037      | 0.037      | 0.037      | 0.037 | 0.038 | V     |   |

Table 5. ISL71043M Response of Key Parameters vs TID

| Parameter     | Symbol            | Condition | Bias     | 0krad(Si) | 10krad(Si) | 20krad(Si) | 30krad(Si) | 50krad(Si) | Unit  |       |       |       |   |

|---------------|-------------------|-----------|----------|-----------|------------|------------|------------|------------|-------|-------|-------|-------|---|

| Start-Up      |                   | 13.2V     | Biased   | 80.799    | 80.613     | 80.451     | 80.350     | 81.132     | μA    |       |       |       |   |

| Current       | I <sub>DDSu</sub> | 13.20     | Grounded | 80.546    | 80.406     | 80.282     | 80.212     | 81.280     | μA    |       |       |       |   |

|               |                   | 0)/       | Biased   | 2.555     | 2.548      | 2.543      | 2.539      | 2.444      | mA    |       |       |       |   |

|               |                   | 9V        | Grounded | 2.565     | 2.560      | 2.556      | 2.552      | 2.465      | mA    |       |       |       |   |

| Operating     |                   | 12V       | Biased   | 2.543     | 2.536      | 2.531      | 2.527      | 2.484      | mA    |       |       |       |   |

| Current       | I <sub>DDOp</sub> | 120       | Grounded | 2.554     | 2.548      | 2.544      | 2.540      | 2.505      | mA    |       |       |       |   |

|               |                   | 13.2V     | Biased   | 3.249     | 3.249      | 3.246      | 3.232      | 2.494      | mA    |       |       |       |   |

|               |                   | 13.20     | Grounded | 3.263     | 3.259      | 3.263      | 3.243      | 2.514      | mA    |       |       |       |   |

| Frequency I   | Freq              | 13.2V     | Biased   | 50.783    | 50.787     | 50.787     | 50.770     | 50.709     | kHz   |       |       |       |   |

|               | Fieq              | 13.20     | Grounded | 50.803    | 50.805     | 50.802     | 50.782     | 50.770     | kHz   |       |       |       |   |

| Frequency     | Freq_             |           | Biased   | -0.039    | -0.025     | 0.010      | -0.007     | 0.014      | %     |       |       |       |   |

| Accuracy PSRR | PSRR              | -         | Grounded | -0.035    | -0.042     | -0.039     | -0.047     | 0.009      | %     |       |       |       |   |

|               |                   | 1mA       | Biased   | 4.988     | 4.988      | 4.987      | 4.988      | 4.982      | V     |       |       |       |   |

| Voltage       | \ \ <u>\</u>      | 1mA       | Grounded | 4.994     | 4.994      | 4.993      | 4.994      | 4.993      | V     |       |       |       |   |

| Reference     | V <sub>REF</sub>  | 10mA      | Biased   | 4.980     | 4.980      | 4.979      | 4.979      | 4.972      | V     |       |       |       |   |

|               |                   | TOITIA    | Grounded | 4.987     | 4.987      | 4.986      | 4.986      | 4.982      | V     |       |       |       |   |

| Error Amp     | EA_               | 12V       | Biased   | 2.500     | 2.499      | 2.499      | 2.499      | 2.499      | V     |       |       |       |   |

| Reference     | V <sub>REF</sub>  | _         | _        | _         | _          | 120        | Grounded   | 2.501      | 2.502 | 2.502 | 2.502 | 2.502 | V |

# 6.2 Single-Event Effects Testing

The intense heavy ion environment encountered in space applications can cause a variety of Single-Event Effects (SEE). SEE can lead to system-level performance issues including disruption, degradation, and destruction. For predictable and reliable space system operation, individual electronic components should be characterized to determine their SEE response. SEE testing was performed on the ISL71043M only and the results extend to include the ISL71041M because the differences between the parts are so slight. Any differences between the parts were determined to be benign in previous testing. The following is a summary of the ISL71043M SEE testing.

### 6.2.1 SEE Test Facility

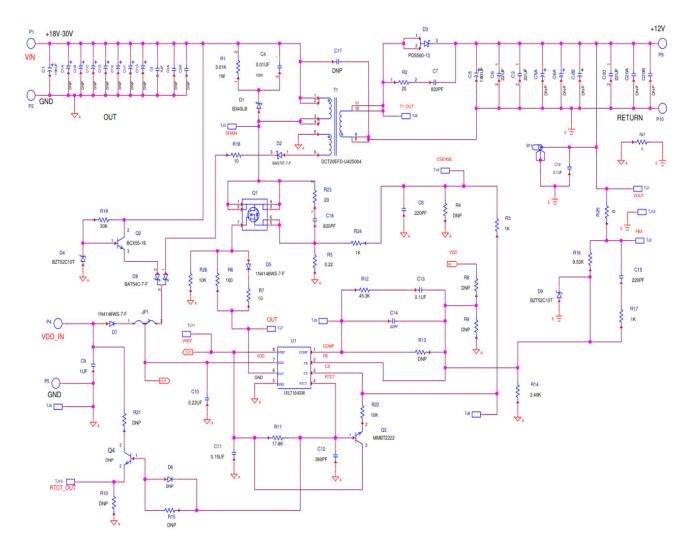

Testing was performed at the Texas A&M University (TAMU) Cyclotron Institute heavy ion facility on April 4, 2019. The overall test setup includes the test jig containing four evaluation boards mounted and wired through a 20ft cable to the data room. The end of the 20ft cable in the data room was connected to a switchboard. The switchboard was wired to the power supplies and monitoring equipment/scopes. The signals from the switchboard were connected to two LeCroy oscilloscopes, one set to capture transients due to pulse-width change and the

other to capture on period change. The switchboard at the end of the 20ft cabling was found to require termination to keep the noise on the waveforms to a minimum. OUT and RTCT was terminated with a series combination of 1000pF and 5100 and the VOUT and VREF signals with a 10nF0 capacitor to ground.

#### 6.2.2 SEE Test Setup

The SEB/L evaluation board was wired up in the open loop configuration as shown in Figure 27. The biasing used for the SEB/L test runs was  $V_{DD}$  = 14.7V. The SET board was wired up in the closed loop configuration shown in Figure 28. The biasing for the SET test runs was  $V_{DD}$  = 14.7V.

A SET occurs when a perturbation is detected. This can be a change in pulse-width, which can cause missing pulses. Scope 1 was set to trigger to pulse-width variations of around the nominal value. Measurements on Scope 1 are CH1 = OUT, CH2 = VOUT, CH3 = RTCT, CH4 = VREF, and TRIG = OUT PW. Scope 2 is set to trigger to missing pulse events. This setting triggers when two rising edges deviate from the nominal period by ±20%. Measurements on Scope 2 are CH1 = OUT, CH2 = VOUT, CH3 = RTCT, CH4 = VREF, and TRIG = OUT period.

Figure 27. SEB/L Evaluation Board Schematic

Figure 28. Schematic of SET Evaluation Board

### 6.2.3 Single Event Burnout and Latch-Up (SEB/L) Results

No SEB was observed for the device LET of  $43 \text{MeV} \cdot \text{cm}^2/\text{mg}$  (+125°C) and  $V_{DD}$  = 14.7V. No SEL events were observed for the device at LET value of  $43 \text{MeV} \cdot \text{cm}^2/\text{mg}$  (+125°C, VREF Cap = 0.22 $\mu$ F). A destructive event occurs when the supply current of the device increases greater than 5%.

#### 6.2.4 SET Results

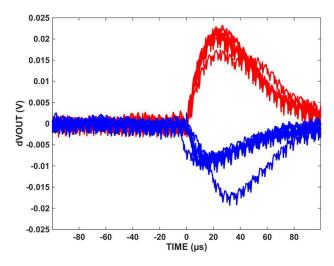

The device is sensitive to soft errors with a LET of 43MeV•cm²/mg. No soft error was observed, which caused more than one PWM output pulse dropout at LET value of 43MeV•cm²/mg. Extreme pulse-width waveforms are

shown in Figure 29 through Figure 32, while Figure 33 is a composite of the 10 greatest positive and negative  $V_{OUT}$  transients observed during testing.

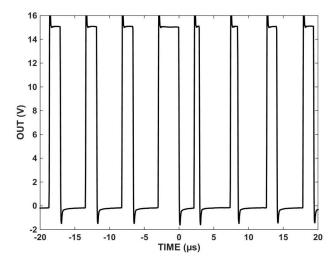

Figure 29. Extreme SET captures from DUT2 with 43MeV·cm<sup>2</sup>/mg on the OUT signal with a ±20% pulse-width trigger, maximum pulse-width high

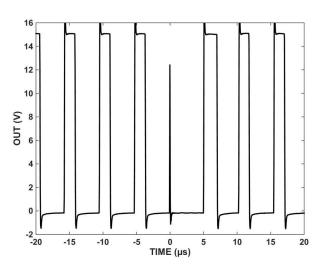

Figure 30. Extreme SET captures from DUT2 with 43MeV·cm<sup>2</sup>/mg on the OUT signal with a ±20% pulse-width trigger, maximum pulse-width low

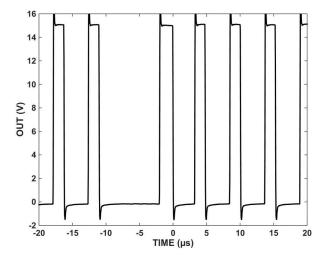

Figure 31. Extreme SET captures from DUT2 with 43MeV·cm<sup>2</sup>/mg on the OUT signal with a ±20% pulse-width trigger, minimum pulse-width high

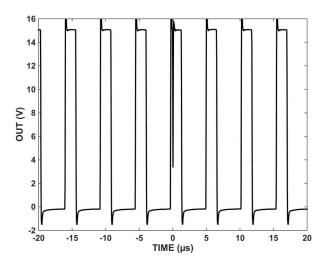

Figure 32. Extreme SET captures from DUT2 with 43MeV·cm<sup>2</sup>/mg on the OUT signal with a ±20% pulse-width trigger, minimum pulse-width low

Figure 33. Composite of Ten Greatest Positive and Negative V<sub>OUT</sub> Transients

#### 6.2.5 Conclusion

The device is sensitive to soft errors with a LET of 43MeV•cm²/mg. No soft error was observed which caused more than one missing PWM output pulse at LET value of 43MeV•cm²/mg.

| Test <sup>[1]</sup>        | Missed<br>Pulses<br>(Typical) | Missed<br>Pulses<br>(Maximum) | Temp | LET<br>(MeV•cm <sup>2</sup> /mg) | Remarks                                                                                                                                                                                               |

|----------------------------|-------------------------------|-------------------------------|------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEB/L <sup>[2][3][4]</sup> | -                             | -                             | +125 | 43                               | No destructive single event burnouts or latch-up events occurred at V <sub>DD</sub> = 14.7V at 43MeV·cm <sup>2</sup> /mg and 0° incidence at a fluence of 4x10 <sup>7</sup> particles/cm <sup>2</sup> |

| SET                        | -                             | 1                             | +25  | 43                               |                                                                                                                                                                                                       |

- 1. SEE tests performed at a switching frequency of 200kHz, RT = 17.8k, CT = 390pF. SEB/L tests are done in a standalone open loop configuration and the SET tests are done in a closed loop configuration.

- SEB occurs if an increase in the I<sub>DD</sub> of greater than 5% is measured after exposure to the beam. A 0.22μF capacitor was connected from the VREF pin to GND for the purpose of bypass.

- 3. SEL results: No latch-up conditions were observed, a SEL is categorized by an increase in the I<sub>DD</sub> current greater than 5% during exposure. A 0.22µF capacitor was used from VREF pin to GND for bypass.

- 4. The recommended highest operating  $V_{DD}$  for the device is 13.2V, which is below the single event breakdown survival voltage of 14.7V for normal incidence LET = 43MeV·cm<sup>2</sup>/mg.

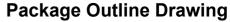

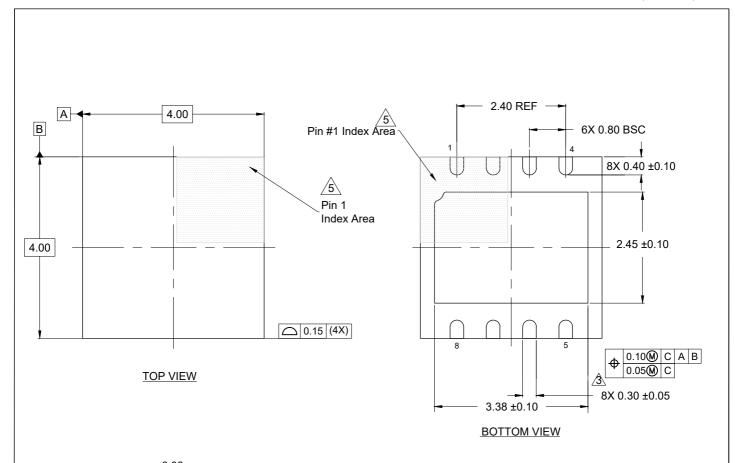

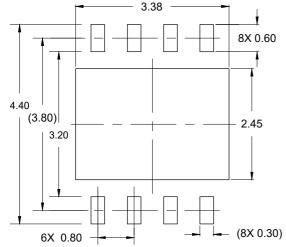

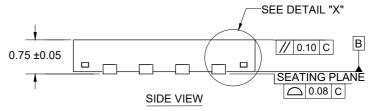

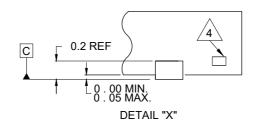

# 7. Package Outline Drawings

The package outline drawings are located at the end of this document and are accessible from the Renesas website. The package information is the most current data available and is subject to change without revision of this document.

# 8. Ordering Information

| Part Number <sup>[1][2]</sup> | Part<br>Marking                                                          | Radiation Lot<br>Acceptance<br>Testing | TID Data<br>Pack<br>Included | Package<br>Description <sup>[3]</sup><br>(RoHS<br>Compliant) | Pkg.<br>Dwg. # | Carrier<br>Type <sup>[4]</sup> | Temp<br>Range    |  |

|-------------------------------|--------------------------------------------------------------------------|----------------------------------------|------------------------------|--------------------------------------------------------------|----------------|--------------------------------|------------------|--|

| ISL71043MBZ                   |                                                                          |                                        |                              |                                                              |                | Tube                           |                  |  |

| ISL71043MBZ-T                 | 71043<br>MB <i>Z</i>                                                     | N/A                                    | No                           | 8 Ld NSOIC                                                   | M8.15          | Reel, 1k                       | -55 to<br>+125°C |  |

| ISL71043MBZ-T7A               |                                                                          |                                        |                              |                                                              |                | Reel, 250                      |                  |  |

| ISL71043M30BZ                 | _,,,,,                                                                   |                                        |                              |                                                              |                | Tube                           |                  |  |

| ISL71043M30BZ-T               | 71043<br>MBZ                                                             | 30krad(Si)                             |                              | 8 Ld NSOIC                                                   | M8.15          | Reel, 1k                       | -55 to<br>+125°C |  |

| ISL71043M30BZ-T7A             |                                                                          |                                        | Yes                          |                                                              |                | Reel, 250                      |                  |  |

| ISL71043M50BZ                 |                                                                          |                                        | - res                        | 8 Ld NSOIC                                                   |                | Tube                           | -55 to<br>+125°C |  |

| ISL71043M50BZ-T               | 71043<br>MBZ                                                             | 50krad(Si)                             |                              |                                                              | M8.15          | Reel, 1k                       |                  |  |

| ISL71043M50BZ-T7A             |                                                                          |                                        |                              |                                                              |                | Reel, 250                      |                  |  |

| ISL71043MRTZ                  |                                                                          | N/A                                    | No                           | 8 Ld TDFN                                                    | L8.4x4B        | Tube                           | -55 to<br>+125°C |  |

| ISL71043MRTZ-T                | 710<br>43MRTZ                                                            |                                        |                              |                                                              |                | Reel, 1k                       |                  |  |

| ISL71043MRTZ-T7A              |                                                                          |                                        |                              |                                                              |                | Reel, 250                      |                  |  |

| ISL71041MRTZ                  |                                                                          | N/A                                    | No                           | 8 Ld TDFN                                                    | L8.4x4B        | Tube                           | -55 to<br>+125°C |  |

| ISL71041MRTZ-T                | 710<br>41MRTZ                                                            |                                        |                              |                                                              |                | Reel, 1k                       |                  |  |

| ISL71041MRTZ-T7A              | _                                                                        |                                        |                              |                                                              |                | Reel, 250                      |                  |  |

| ISL71041M30RTZ                |                                                                          |                                        |                              |                                                              | L8.4x4B        | Tube                           |                  |  |

| ISL71041M30RTZ-T              | 710<br>41MRTZ                                                            | 30krad(Si)                             |                              | 8 Ld TDFN                                                    |                | Reel, 1k                       | -55 to<br>+125°C |  |

| ISL71041M30RTZ-T7A            |                                                                          |                                        | Yes                          |                                                              |                | Reel, 250                      | . 120 0          |  |

| ISL71041M50RTZ                |                                                                          | 50krad(Si)                             | res                          |                                                              | L8.4x4B        | Tube                           | -55 to<br>+125°C |  |

| ISL71041M50RTZ-T              | 710<br>41MRTZ                                                            |                                        |                              | 8 Ld TDFN                                                    |                | Reel, 1k                       |                  |  |

| ISL71041M50RTZ-T7A            |                                                                          |                                        |                              |                                                              |                | Reel, 250                      |                  |  |

| ISL71043MEVAL1Z               | Flyback Power Supply Evaluation Board using the ISL71043M and ISL71040M. |                                        |                              |                                                              |                |                                |                  |  |

<sup>1.</sup> These Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and NiPdAu-Ag plate - e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J-STD-020.

<sup>2.</sup> For Moisture Sensitivity Level (MSL), see the ISL71043M and ISL71041M device pages. For more information about MSL, see TB363.

<sup>3.</sup> For the Pb-Free Reflow Profile, see TB493.

<sup>4.</sup> See TB347 for details about reel specifications.

# 9. Revision History

| Rev. | Date         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.05 | Dec 17, 2025 | Updated Features bullets. Updated the Start-Up Current (IDDSU) from 125µA to 500µA Added references to ISL71043M30 and ISL71043M50 throughout. Updated Table 3. Updated section 6.1.1 Introduction. Updated Figures 19 to 24. Updated Table 5. Updated Ordering Information table. Updated PODs.                                                                                                                                                 |

| 5.04 | Jan 31, 2025 | Updated Features bullets. Added references to ISL71041M30 and ISL71041M50 throughout. Edited oscillator frequency equations. Updated Figure 4 and added Figure 5. Updated Table 3. Updated Figures 17, 24, and 25. Updated Table 4. Removed Table 6. Updated Ordering Information table.                                                                                                                                                         |

| 5.03 | Sep 29, 2023 | Updated M8.15 POD to the latest revision (corrected typo).                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.02 | Aug 11, 2023 | Applied the latest template throughout. Updated Features bullets. Updated block diagram. Added Maximum Duty Cycle minimum specification. Added ISL71043M Radiation Acceptance Test Limits section. Added Table 6. Updated Tables 4 and 5. Updated Figures 18 through 23. Added Figures 24 and 25. Removed Reference section as reference is now a footnote on the applicable page.                                                               |

| 5.01 | Feb 23, 2023 | Added EPAD description to the Pin Descriptions table. Removed Related Literature section. Updated ordering information table formatting. Updated POD M8.15 to the latest revision, changes are as follows:  Added the coplanarity spec into the drawing.                                                                                                                                                                                         |

| 5.00 | Sep 30, 2020 | Added ISL71041 throughout                                                                                                                                                                                                                                                                                                                                                                                                                        |