# V850ES/JF3-L、RX231 グループ

# V850ES/JF3-L から RX231 グループへの移行ガイド

#### 要旨

本アプリケーションノートは、V850ES/JF3-LからRX231グループへの置き換えを行う場合の注意点、並びに相違点などを説明しています。なお、各機能の詳細な情報は最新のユーザーズマニュアル ハードウェア編にてご確認ください。

本文中では、V850ES/JF3-L は $\mu$ PD70F3736の仕様を代表として記載しています。その他の V850ES/JF3-L 製品も、メモリ容量の違いはありますが、機能としては $\mu$ PD70F3736と同等ですので本資料を活用いただけます。また、RX231 グループは R5F52318A(チップバージョン A)の仕様を代表として記載しています。

なお、RX231 グループは、ドライバ/ミドルウェア(Firmware Integration Technology) およびドライバ生成 ツール(スマート・コンフィグレータ内に同梱)に対応しているため、ソフトウェア開発の負担を軽減できます。

# 目次

| 1. 柞    | 既要                       | 4  |

|---------|--------------------------|----|

| 1.1     | ラインアップ                   | 4  |

| 1.2     | 機能置き換え可否                 | 4  |

|         |                          |    |

| 2. F    | 内蔵機能                     | 6  |

| 2.1     | CPU 機能                   | 6  |

| 2.1.1   | 仕様比較                     | 6  |

| 2.1.2   | メモリ・マップ                  | 6  |

| 2.2     | ポート機能                    | 8  |

| 2.2.1   | 仕様比較                     | 8  |

| 2.2.2   | 注意事項                     | 8  |

| 2.2.2.  | 1 存在しないポート               | 8  |

| 2.3     | 外部バス制御機能                 | 9  |

| 2.3.1   | 仕様比較                     | 9  |

| 2.4     | クロック発生機能                 | 11 |

| 2.4.1   | 仕様比較                     | 11 |

| 2.4.2   | 注意事項                     | 11 |

| 2.4.2.  | 1 クロック発生回路に関する注意事項       | 11 |

| 2.4.2.2 | 2 発振停止検出機能               | 12 |

| 2.4.2.3 | 3 サブクロックの初期化             | 12 |

| 2.5     | タイマ機能(TMP、TMQ)           | 13 |

| 2.5.1   | 搭載ユニット                   | 13 |

| 2.5.2   | 仕様比較                     | 13 |

| 2.6     | 16 ビット・インターバル・タイマ M(TMM) | 15 |

| 2.6.1   | 仕様比較                     | 15 |

| 2.6.2   | 注意事項                     | 15 |

| 2.6.2.  | 1 タイマカウンタの初期化            | 15 |

| 2.7     | 時計タイマ機能                  | 16 |

| 2.7.1   | 仕様比較                     | 16 |

| 2.7.2   | 注意事項                     | 16 |

| 2.7.2.  | 1 RTC の初期化               | 16 |

| 2.8     | ウォッチドッグ・タイマ 2 機能         | 17 |

| 2.8.1   | 搭載ユニット                   | 17 |

| 2.8.2   | 仕様比較                     | 17 |

| 2.8.3   | 注意事項                     | 17 |

| 2.8.3.  | 1 カウント動作について             | 17 |

| 2.8.3.2 | 2 カウントスタート               | 18 |

| 2.8.3.  | 3 使用しない場合の設定             | 18 |

| 2.9     | リアルタイム出力機能(RTO)          | 19 |

| 2.9.1   | 仕様比較                     | 19 |

| 2.10    | A/D コンバータ                | 20 |

| 2.10.1  | 仕様比較                     | 20 |

| 2.10.2  | 注意事項                     | 20 |

| 2.10.2  | 1 A/D コンバータの動作状態         | 20 |

| 2.11    | D/A コンバータ                | 21 |

|         |                          |    |

| 2.11.1 仕様比較                        | 21 |

|------------------------------------|----|

| 2.12 アシンクロナス・シリアル・インタフェース A(UARTA) | 22 |

| 2.12.1 仕様比較                        | 22 |

| 2.12.2 注意事項                        | 22 |

| 2.12.2.1 0 パリティ                    | 22 |

| 2.13 3線式可変長シリアル I/O(CSIB)          | 23 |

| 2.13.1 搭載ユニット                      | 23 |

| 2.13.2 仕様比較                        | 23 |

| 2.14 I <sup>2</sup> C バス           | 24 |

| 2.14.1 搭載ユニット                      | 24 |

| 2.14.2 仕様比較                        | 24 |

| 2.15 DMA 機能(DMA コントローラ)            | 25 |

| 2.15.1 仕様比較                        | 25 |

| 2.16 割り込み/例外処理機能                   | 26 |

| 2.16.1 仕様比較                        | 26 |

| 2.16.2 注意事項                        | 26 |

| 2.16.2.1 チップバージョンによる差異             | 26 |

| 2.17 スタンバイ機能                       | 27 |

| 2.17.1 仕様比較                        | 27 |

| 2.18 クロック・モニタ                      | 30 |

| 2.18.1 仕様比較                        | 30 |

| 2.18.2 注意事項                        | 30 |

| 2.18.2.1 発振停止検出機能の停止               | 30 |

| 2.19 低電圧検出回路(LVI)                  | 31 |

| 2.19.1 仕様比較                        | 31 |

| 2.19.2 注意事項                        | 31 |

| 2.19.2.1 再度電圧検出を設定する際の注意事項         | 31 |

| 2.20 CRC 機能                        | 32 |

| 2.20.1 仕様比較                        | 32 |

|                                    |    |

| 3. サンプルプログラムの説明                    | 33 |

| 3.1 動作確認環境                         | 33 |

| 3.2 プロジェクト構成                       | 34 |

| 3.3 関数一覧                           | 35 |

| 3.4 関数仕様                           | 35 |

| 3.5 フローチャート                        | 37 |

| 3.5.1 メイン                          | 37 |

| 3.5.2 外部割り込み処理                     | 37 |

| 3.5.3 ワンショットパルス出力機能の MTU0 割り込み処理   | 38 |

| 3.5.4 リアルタイム出力機能の TMR0 割り込み処理      | 38 |

|                                    |    |

| 4. プロジェクトをインポートする方法                | 39 |

| 4.1 e² studio での手順                 | 39 |

| 4.2 CS+での手順                        | 40 |

|                                    |    |

| 5. 参考ドキュメント                        | 41 |

# 1. 概要

# 1.1 ラインアップ

V850ES/JF3-L と RX231 グループの製品ラインアップ(コードサイズおよびピン数)を表 1.1 に示します。

表 1.1 V850ES/JF3-L、RX231 グループのコードサイズおよびピン数一覧

| V850ES/JF3-L         |       | RX231          |                    |

|----------------------|-------|----------------|--------------------|

| Code Flash/RAM Pin 数 |       | Code Flash/RAM | Pin 数              |

| 128K/8K              | 80pin | 128K/32K       | 48pin,64pin,100pin |

| 256K/16K             | 80pin | 256K/32K       | 48pin,64pin,100pin |

| _                    | _     | 384K/64K       | 48pin,64pin,100pin |

| _                    | _     | 512K/64K       | 48pin,64pin,100pin |

# 1.2 機能置き換え可否

V850ES/JF3-L の機能に対して RX231 グループでの機能置き換え可否を表 1.2 に示します。

表 1.2 機能置き換え可否

| V850ES/JF3-L の機能                 | RX231 グループによる置き換え可否                                                                            |

|----------------------------------|------------------------------------------------------------------------------------------------|

| ポート機能                            | 可能                                                                                             |

| 外部バス制御機能                         | 可能<br>ただし、バス・ホールド機能によるバス権の<br>調停なし                                                             |

| クロック発生機能                         | 可能                                                                                             |

| タイマ機能(TMP、TMQ)                   | マルチファンクションタイマパルスユニット<br>(MTU2a)または 16 ビットタイマパルスユニット(TPUa)で実現可能<br>ただし、一部機能は CPU 割り込みを介在させる必要あり |

| 16 ビット・インターバル・タイマ M<br>(TMM)     | コンペアマッチタイマ(CMT)で実現可能                                                                           |

| 時計タイマ機能                          | リアルタイムクロック(RTCe)で実現可能                                                                          |

| ウォッチドッグ・タイマ2機能                   | ウォッチドッグタイマ(WDTA)または独立<br>ウォッチドッグタイマ(IWDTa)で実現可能                                                |

| リアルタイム出力機能(RTO)                  | イベントリンクコントローラ(ELC)と任意の<br>タイマ機能で再現可能<br>ただし、一部機能は CPU 割り込みを介在さ<br>せる必要あり                       |

| A/D コンバータ                        | 12 ビット A/D コンバータ (S12ADE)で<br>実現可能                                                             |

| D/A コンバータ                        | 12 ビット D/A コンバータ(R12DAA)で<br>実現可能                                                              |

| アシンクロナス・シリアル・インタフェース<br>A(UARTA) | シリアルコミュニケーションインタフェース<br>(SClg, SClh)で実現可能                                                      |

| 3線式可変長シリアル I/O(CSIB)             | シリアルペリフェラルインタフェース<br>(RSPIa)またはシリアルコミュニケーション<br>インタフェース(SCIg, SCIh)で実現可能                       |

| I <sup>2</sup> C バス              | シリアルコミュニケーションインタフェース<br>(SClg, SClh)または I <sup>2</sup> C バスインタフェース<br>(RIICa)で実現可能             |

| V850ES/JF3-L の機能   | RX231 グループによる置き換え可否                    |

|--------------------|----------------------------------------|

| DMA 機能(DMA コントローラ) | 可能                                     |

| 割り込み/例外処理機能        | 可能<br>ただし、外部割り込みや周辺モジュールに依<br>存する仕様は除く |

| スタンバイ機能            | 可能                                     |

| クロック・モニタ           | 発振停止検出機能で実現可能                          |

| 低電圧検出回路(LVI)       | 電圧検出回路(LVDAb)で実現可能                     |

| CRC 機能             | 可能                                     |

### 2. 内蔵機能

#### 2.1 CPU 機能

#### 2.1.1 仕様比較

V850ES/JF3-L と RX231 グループ の CPU 機能の仕様比較を表 2.1 に示します。

表 2.1 V850ES/JF3-L、RX231 グループの CPU 機能

| 項目      | V850ES/JF3-L | RX231 |

|---------|--------------|-------|

| 最大動作周波数 | 20MHz        | 54MHz |

#### 2.1.2 メモリ・マップ

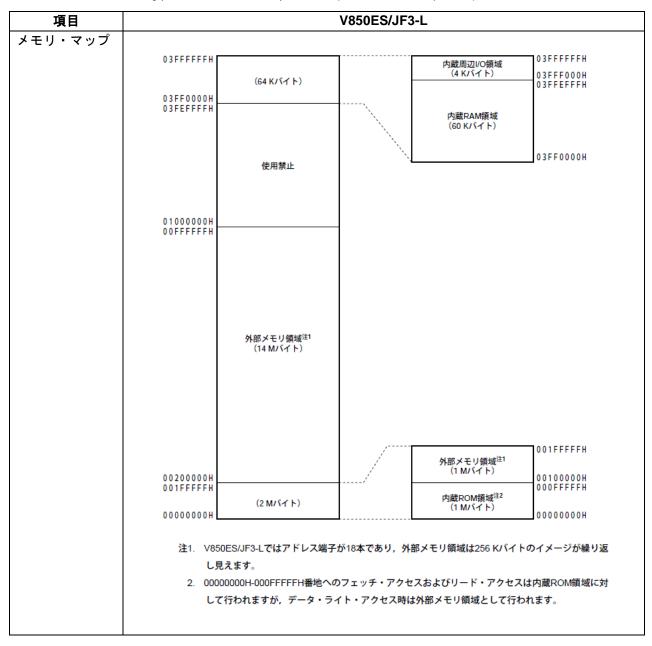

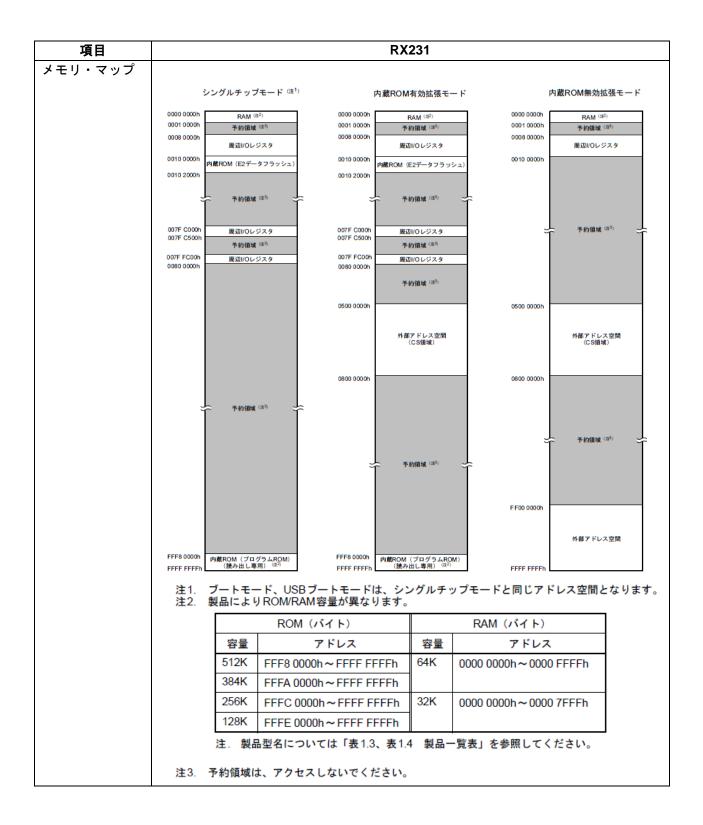

V850ES/JF3-L と RX231 グループ のメモリ・マップを表 2.2 に示します。

表 2.2 V850ES/JF3-L、RX231 グループのメモリ・マップ

#### 2.2 ポート機能

#### 2.2.1 仕様比較

V850ES/JF3-L のポート機能の仕様に対応する RX231 グループの I/O ポート機能の仕様を表 2.3 ポート機能に示します。

表 2.3 ポート機能置き換え可否

| 項目                       | V850ES/JF3-L | RX231     |

|--------------------------|--------------|-----------|

| CMOS 出力/ N-ch オープンドレイン出力 | 可能           | 可能        |

| 内蔵プルアップ/プルダウン機能          | 可能(プルダウン)    | 可能(プルアップ) |

| 5V トレラント入力               | 可能           | 可能        |

#### 2.2.2 注意事項

#### 2.2.2.1 存在しないポート

RX231 グループでは製品のピン数の違いによって存在しないポートがあります。存在しないポートの方向制御は RX230 グループ、RX231 グループ ユーザーズマニュアル ハードウェア編「21.4 ポート方向レジスタ(PDR) の初期化」に従って設定する必要があります。

V850ES/JF3-L ではポート n モード・レジスタ (PMn)の設定に相当します。ポート n モード・レジスタ (PMn)の設定の詳細は V850ES/JF3-L ユーザーズマニュアル ハードウェア編「4 章 ポート機能」を参照してください。

#### 2.3 外部バス制御機能

#### 2.3.1 仕様比較

V850ES/JF3-L に搭載された外部バス・インタフェース機能の仕様に対応する RX231 グループの外部バス機能の仕様を表 2.4 に示します。また、外部バス制御機能の端子比較を表 2.5 に示します。

表 2.4 外部バス・インタフェース機能の対応

| 項目                                        | V850ES/JF3-L     | RX231                           |

|-------------------------------------------|------------------|---------------------------------|

| 切口 リー・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 外部バス・インタフェース機能   | 外部バス                            |

| バスサイズ                                     | 8 ビット / 16 ビット   | 8 ビット / 16 ビット                  |

| バス空間                                      | 4 ブロック           | 4 ブロック                          |

|                                           | (ブロックサイズ:2~8MB)  | (ブロックサイズ:16MB)                  |

| ウエイト機能                                    | データ・ウエイト         | サイクルウェイト、アサートウェイト               |

|                                           |                  | データ出カウェイト設定で可能 <sup>(注 1)</sup> |

|                                           | アドレス・セットアップ・     | CS アサートウェイト設定で可能                |

|                                           | ウエイト             |                                 |

|                                           | アドレス・ホールド・       | アドレスサイクルウェイト設定で可能               |

|                                           | ウエイト             |                                 |

|                                           | 端子による外部ウエイト      | WAIT#端子により可能                    |

| マルチプロセッサ構                                 | バス・ホールド機能によるバス権の | なし                              |

| 成における                                     | 調停               |                                 |

| バスの調停                                     |                  |                                 |

| バスモード                                     | マルチ・プレクス・バス・モード  | マルチプレクスバスモード                    |

|                                           |                  | セパレートバスモード                      |

注1. リード時:サイクルウェイト設定(CSRWAIT)と RD アサートウェイト(RDON)で同等の設定可能 ライト時:サイクルウェイト設定(CSRWAIT)とアサートウェイト(WDON)、データ出力ウェイト (WDON)で同等設定可能

# 表 2.5 外部バス・インタフェース機能関連端子比較

| V850ES/JF3-L |     |            | RX231 <sup>(注 1)</sup> |     |                |

|--------------|-----|------------|------------------------|-----|----------------|

| 端子名          | 入出力 | 機能         | 端子名                    | 入出力 | 機能             |

| AD0-AD15     | 入出力 | アドレス/データバス | A15/D15-               | 入出力 | アドレス/データバス     |

|              |     |            | A0/D0                  |     | (マルチプレクスバスモード) |

| A16, A17     | 入出力 | アドレスバス     | A23-A9                 | 出力  | アドレスバス         |

| WAIT         | 入力  | 外部ウエイト制御   | WAIT#                  | 入力  | 外部ウエイト制御       |

| CLKOUT       | 出力  | 内部システム     | BCLK                   | 出力  | 外部バスクロック       |

|              |     | ・クロック出力    |                        |     |                |

| WR0 <b>±</b> | 出力  | ライト・ストローブ  | WR1#、                  | 出力  | ライトストローブ       |

| ラー! ブッ       |     |            | WR0#/WR#               |     |                |

| クマーク         |     |            |                        |     |                |

| が定義さ         |     |            |                        |     |                |

| れていま         |     |            |                        |     |                |

| せん。          |     |            |                        |     |                |

| WR1          |     |            |                        |     |                |

| RD           | 出力  | リード・ストローブ  | RD#                    | 出力  | リード・ストローブ      |

| ASTB         | 出力  | アドレス・ストローブ | ALE                    | 出力  | アドレス・ラッチ・      |

|              |     |            |                        |     | イネーブル          |

|              |     |            |                        |     | (マルチプレクスバスモード) |

| HLDRQ        | 入力  | バス・ホールド制御  |                        |     | _              |

| HLDAK        | 出力  |            | _                      | _   | _              |

注1. RX231 グループでは 100 ピンパッケージのみ外部バス機能をサポートしています。

# 2.4 クロック発生機能

#### 2.4.1 仕様比較

V850ES/JF3-L に搭載されたクロック発生機能の仕様に対応する RX231 グループのクロック発生回路機能の仕様を表 2.6 に示します。

表 2.6 クロック発生機能の対応

| 項目             | V850ES/JF3-L                                                                                                                                                                                 | RX231                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | クロック発生機能                                                                                                                                                                                     | クロック発生回路                                                                                                                                                                                                                                                                                                                                                                    |

| CPU<br>クロックソース | 以下 3 種類から選択 ・メインクロック ・PLL クロック(4 逓倍固定) ・サブクロック ・内蔵発振クロック                                                                                                                                     | 以下 5 種類から選択 ・メインクロック(1~20MHz) (発振子と外部クロックを選択可能) ・PLL クロック (4~13.5 逓倍、1/2/4 分周) ・サブクロック(32.768kHz)(注1) ・高速オンチップオシレータ(HOCO)(54MHz、32MHz から選択) ・低速オンチップオシレータ(LOCO)(4MHz)                                                                                                                                                                                                       |

| 動作周波数(max)     | 機能ごとに規定 CPU クロック周波数: fCPU: 20MHz(max) 内部システム・クロック周波数: 数: fCLK: 20MHz(max) 周辺クロック周波数: 20MHz(max) タイマ M クロック: 20MHz(max) 時計用タイマ・クロック: 32.768kHz ウォッチドッグ・タイマ 2 クロック: 約 39kHz(max) 内蔵発振器: 220kHz | 機能ごとに異なるクロックを生成 ・ICLK: 54MHz (max) ・PCLKA: 54MHz (max) ・PCLKB: 32MHz (max) ・PCLKD: 54MHz (max) ・PCLKD: 54MHz (max) ・FCLK: 1MHz~32MHz (ROM、E2 データフラッシュ P/E 時) 32MHz (max) (E2 データフラッシュ読み出し時) ・BCLK: 32MHz (max) ・BCLK: 32MHz (max) ・BCLK: 48MHz (max) ・UCLK: 48MHz (max) ・CACCLK: 各発振器のクロックと同じ ・RTCSCLK: 32.768kHz ・IWDTCLK: 15kHz ・CANMCLK: 20MHz(max) ・SSISCK: 20MHz (max) |

- 注1. 48 ピンの製品にサブクロック端子はありません。

- 注2. チップバージョン C に CANMCLK はありません。

#### 2.4.2 注意事項

#### 2.4.2.1 クロック発生回路に関する注意事項

RX231 グループでは、システムクロック(ICLK)、各周辺モジュールに供給されるクロック(PCLK など)の 周波数関係に制限があります。詳細は RX230 グループ、RX231 グループユーザーズマニュアル ハードウェア編「9.8.1 クロック発生回路に関する注意事項」を参照してください。

#### 2.4.2.2 発振停止検出機能

RX231 グループでは、メインクロック発振器の停止を検出し、システムクロックのクロックソースとしてメインクロックの代わりに LOCO が出力する低速クロックを供給する機能があります。詳細は RX230 グループ、RX231 グループ ユーザーズマニュアル ハードウェア編「9.5 発振停止検出機能」を参照してください。

### 2.4.2.3 サブクロックの初期化

RX231 グループではサブクロックの使用の有無にかかわらず、コールドスタート時にはサブクロック制御回路を初期化する必要があります。詳細は RX230 グループ、RX231 グループ ユーザーズマニュアル ハードウェア編「9.8.5 サブクロックに関する注意事項」を参照してください。

# 2.5 タイマ機能 (TMP、TMQ)

#### 2.5.1 搭載ユニット

V850ES/JF3-L と RX231 グループに内蔵されたタイマ機能のユニット一覧を表 2.7 に示します。

表 2.7 V850ES/JF3-L、RX231 グループのタイマ機能一覧

| 項目      | V850ES/JF3-L      | RX231             |

|---------|-------------------|-------------------|

| 多機能タイマ/ | ・16 ビット・タイマ/イベント・ | ・マルチファンクションタイマ    |

| カウンタ    | カウンタ P(TMP)       | パルスユニット 2 (MTU2a) |

| 統合モジュール | ・16 ビット・タイマ/イベント・ | ・16 ビットタイマパルスユニット |

|         | カウンタ Q(TMQ)       | (TPUa)            |

#### 2.5.2 仕様比較

V850ES/JF3-L に搭載されたタイマ機能(16 ビット・タイマ/イベント・カウンタ P 、16 ビット・タイマ/イベント・カウンタ Q )の仕様に対応する RX231 グループのタイマ機能(MTU2a、TPUa)の機能の仕様を表 2.8 に示します。

表 2.8 タイマ機能の対応

| 項目          | V850ES/JF3-L                                                                                                                                             | RX231                                                                                                                             |                                                                                                 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

|             | TMP、TMQ                                                                                                                                                  | MTU2a                                                                                                                             | TPUa                                                                                            |

| タイマ<br>カウンタ | 5本<br>TMP01:4本<br>TMQ:1本                                                                                                                                 | 8本<br>(MTU0~4 : 各 1本<br>MTU5 : 3本)                                                                                                | 6本<br>(TPU0~5:各1本)                                                                              |

| モード         | インターバルタイマ<br>任意周期での割り込み発生と<br>方形波出力<br>最大5チャネル動作<br>(TMP:4本、TMQ:1本)                                                                                      | MTU0~4 のノーマルモードで<br>可能<br>カウントタイマ:5 チャネ<br>ル(MTU0~4)<br>出力端子:<br>MTU0,MTU3,MTU4:各 4<br>本、<br>MTU1,MUT2:各 2 本                      | TPU0~5 ノーマルモードで可能<br>出力端子<br>TPU0,TPU3:各4本<br>TPU1,TPU2,TPU4,TPU5:各<br>2本                       |

|             | 外部イベントカウント<br>外部イベントカウント入力の<br>有効エッジをカウントし、任<br>意のカウント数をカウントす<br>るごとに割り込み発生<br>最大5チャネル動作<br>(TMP:4本、TMQ:1本)                                              | 外部クロック入力が可能な<br>MTU0~4 の最大 5 チャネルで<br>可能<br>入力端子: 各1本                                                                             | 外部クロック入力が可能な<br>TPU0~5の6チャネルで可能<br>入力端子:各1本                                                     |

|             | 外部トリガパルス出力<br>外部トリガによりカウンタ動作/PWM 波形出力<br>最大 5 本出力(TMP: 4 本、<br>TMQ: 1 本)<br>ワンショットパルス出力<br>外部トリガによりカウンタ動作/ワンショットパルス出力<br>最大 5 本出力(TMP: 4 本、<br>TMQ: 1 本) | ハードで同等の機能はなし <sup>(注1)</sup><br>ただし、MTU0~4 の PWM<br>モードと外部入力割り込みを<br>使用して実現可能<br>波形出力: PWM モード<br>1、2 組み合わせで最大 12<br>本の PWM 出力が可能 | ハードで同等の機能はなし(注1)<br>ただし、TPU0~5 の PWM<br>モードと外部入力割り込みを<br>使用して実現可能<br>波形出力:最大 15 本の PWM<br>出力が可能 |

|             | PWM 出力<br>最大 5 本出力(TMP: 4 本、<br>TMQ: 1 本)                                                                                                                | PWM モード 1、2 組み合わせ<br>で最大 12 本の PWM 出力が可<br>能                                                                                      | 最大 15 本の PWM 出力が可能                                                                              |

# V850ES/JF3-L、RX231 グループ V850ES/JF3-L から RX231 グループへの移行ガイド

| 項目  | V850ES/JF3-L                                        | R                                                                                                                | X231                                                                             |

|-----|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|     | TMP、TMQ                                             | MTU2a                                                                                                            | TPU                                                                              |

| モード | フリーランニングタイマ<br>最大 5 チャネル動作<br>(TMP : 4 本、TMQ : 1 本) | ノーマルモード(フリーランニングカウント動作)<br>最大 5 チャネル<br>8 つのカウントリソース<br>(MTU0~4:各 1 本、MTU5:<br>3 本)                              | ノーマルモード(フリーランニ<br>ングカウント動作)<br>最大 6 チャネル<br>(TPU0~5:各 1 本)                       |

|     | パルス幅測定<br>最大 5 本測定<br>(TMP:4 本、TMQ:1 本)             | 以下 2 つの方法が可能 ・各チャネルのインプット キャプチャを使用 (MTU0~4:各 1 本、 MTU5:3 本) ・MTU5 のパルス幅測定機能 を使用 最大 3 本の外部パルス入力 幅測定が可能 (MTU5 を使用) | 各チャネルのインプットキャ<br>プチャを使用<br>入力端子:<br>TPU0,TPU3:各4本<br>TPU1,TPU2,TPU4,TPU5:各<br>2本 |

注1. RX231 とハードウェア互換のない、外部トリガモードとワンショットパルスモードについては、 ソフトウェアで同等の機能を再現したサンプルプログラムを用意しております。詳細は「3.サ ンプルプログラムの説明」を参照してください。

#### 2.6 16 ビット・インターバル・タイマ M (TMM)

#### 2.6.1 仕様比較

V850ES/JF3-L に搭載された 16 ビット・インターバル・タイマ M (TMM)機能の仕様に対応する RX231 グループのコンペアマッチタイマ (CMT)機能の仕様を表 2.9 に示します。

表 2.9 16 ビット・インターバル・タイマ機能の対応

| 項目          | V850ES/JF3-L                                               | RX231                                               |

|-------------|------------------------------------------------------------|-----------------------------------------------------|

|             | ТММ                                                        | CMT                                                 |

| チャネル数       | 1 チャネル                                                     | 4 チャネル                                              |

| カウンタビット     | 16 ビット                                                     | 16 ビット                                              |

| 選択可能な分周クロック | 8通り                                                        | 4通り                                                 |

|             | fxx、fxx/2、fxx/4、fxx/64、fxx/512、<br>INTWT、fR/8、FXT の中から選択可能 | PCLK/8、PCLK/32、PCLK/128、PCLK/512<br>の中からチャネルごとに選択可能 |

#### 2.6.2 注意事項

#### 2.6.2.1 タイマカウンタの初期化

V850ES/JF3-L では 16 ビット・インターバル・タイマ M が動作停止するとカウンタはカウントクロックとは非同期にリセットされます。16 ビット・カウンタはリード/ライトできません。RX231 グループのコンペアマッチタイマでは、カウント停止後は値を保持します。コンペアマッチタイマのカウンタレジスタは初期値を自由に変更できます。

# 2.7 時計タイマ機能

#### 2.7.1 仕様比較

V850ES/JF3-L に搭載された時計タイマ機能の仕様に対応する RX231 グループのリアルタイムクロック (RTCe)機能の仕様を表 2.10 に示します。

表 2.10 時計タイマ機能の対応

| 項目             | V850ES/JF3-L                          | RX231                                                              |

|----------------|---------------------------------------|--------------------------------------------------------------------|

|                | 時計タイマ機能                               | リアルタイムクロック(RTCe) <sup>(注 1)</sup>                                  |

| モード            | <ul><li>時計モード</li><li>-基準時間</li></ul> | 周期割り込みで可能                                                          |

|                | (0.5 秒,025 秒間隔で割り込み出力)                | 割り込み周期<br>2秒、1秒、1/2秒、1/4秒、1/8秒、1/16秒、1/32秒、<br>1/64秒、1/128秒、1/256秒 |

|                | インターバルタイマモード                          | p                                                                  |

| 時計モードと         | 基準時間専用のインターバルタイマ                      | 時刻情報をカウント                                                          |

| カレンダ           | として動作                                 | 例:hh:mm:ss など                                                      |

| カウントモード<br>の相違 |                                       |                                                                    |

| カウント           | サブクロック                                | サブクロック                                                             |

| クロック           | メインクロック                               |                                                                    |

| 割り込み           | 時計タイマ割り込み                             | 周期割り込み                                                             |

|                | インターバル・タイマ割り込み                        | アラーム割り込み桁上げ割り込み                                                    |

注1. 48 ピンパッケージではサポートされていません。

#### 2.7.2 注意事項

#### 2.7.2.1 RTC の初期化

RX231 グループのリアルタイムクロックは、RTC 内のレジスタがリセットによる初期化が行われないため、リアルタイムクロックの使用の有無に関わらず初期化を行う必要があります。詳細は RX230 グループ、RX231 グループユーザーズマニュアル ハードウェア編「28.3 動作説明」および、「28.6.7 リアルタイムクロックを使用しない場合の初期化手順」を参照してください。

サブクロックを実装していない場合のみ、初期化は不要です。

# 2.8 ウォッチドッグ・タイマ 2 機能

#### 2.8.1 搭載ユニット

V850ES/JF3-L と RX231 グループに内蔵されたウォッチドッグ・タイマ機能のユニット一覧を表 2.11 に示します。

表 2.11 V850ES/JF3-L、RX231 グループのウォッチドッグ・タイマ機能一覧

| 項目      | V850ES/JF3-L   | RX231                |

|---------|----------------|----------------------|

| ウォッチドック | ウォッチドッグ・タイマ2機能 | ・ウォッチドッグタイマ(WDTA)    |

| タイマ機能   |                | ・独立ウォッチドッグタイマ(IWDTa) |

#### 2.8.2 仕様比較

V850ES/JF3-L に搭載されたウォッチドッグ・タイマ 2 機能の仕様に対応する RX231 グループの WDTA 機能, IWDTa 機能の仕様を表 2.12 に示します。

表 2.12 ウォッチドッグ・タイマ機能の対応

| 項目              | V850ES/JF3-L                                                                | RX231          |                      |

|-----------------|-----------------------------------------------------------------------------|----------------|----------------------|

|                 | ウォッチドッグ・タイマ 2                                                               | WDTA           | IWDTa                |

| カウンタ            | 16 ビット                                                                      | 14 ビット         | 14 ビット               |

| ビット長            |                                                                             |                |                      |

| カウント            | サブクロック                                                                      | 周辺クロック(PCLKB)  | IWDT 専用クロック(IWDTCLK) |

| クロックソース         | メインクロック 内蔵発振クロック                                                            |                | オンチップオシレータで生成        |

|                 |                                                                             |                |                      |

| オーバフロー時間        | ・サブクロック:                                                                    | 4 分周~8192 分周   | 1 分周~256 分周          |

| 選択              | 2 <sup>9</sup> /f <sub>XT</sub> ~2 <sup>16</sup> /f <sub>XT</sub>           |                |                      |

|                 | ・メインクロック:                                                                   |                |                      |

|                 | $2^{18}/f_{xx} \sim 2^{25}/f_{xx}$                                          |                |                      |

|                 | ・内蔵発振器:<br>2 <sup>12</sup> /f <sub>R</sub> ~2 <sup>19</sup> /f <sub>R</sub> |                |                      |

| 7111 - 13       | ノンマスカブル割り込み要求モー                                                             |                | - 1 - 2              |

| 動作モード           | ド/リセットモードから選択可能                                                             | ノンマスカブル割り込み要求出 | ノンマスカブル割り込み要求出力      |

| thu 1127 - 7. / |                                                                             | カ/リセット出力を選択可能  | /リセット出力を選択可能         |

| 割り込み/           | ・オーバフロー割り込み                                                                 | ・アンダフロー割り込み    | ・アンダフロー割り込み          |

| リセット発生要因        |                                                                             | ・リフレッシュエラー     | ・リフレッシュエラー           |

#### 2.8.3 注意事項

#### 2.8.3.1 カウント動作について

V850ES/JF-3 グループのウォッチドッグ・タイマ 2 はアップカウントですが、RX231 グループのウォッチドッグタイマおよび、独立ウォッチドッグタイマはダウンカウントになります。

# 2.8.3.2 カウントスタート

RX231 グループのウォッチドッグタイマおよび、独立ウォッチドッグタイマのカウント開始方法はレジスタスタートモードとオートスタートモードの 2 種類があります。

#### 2.8.3.3 使用しない場合の設定

V850ES/JF-3 グループではウォッチドッグ・タイマ 2 はリセット解除後に自動的にリセット・モードでスタートします。使用しない場合、一度ウォッチドッグ・タイマ 2 をクリアした後、次のインターバル時間内で停止する必要があります。RX231 グループではウォッチドッグタイマおよび、独立ウォッチドッグタイマを使用しない場合、設定は不要です。

#### 2.9 リアルタイム出力機能(RTO)

RX231 グループには、リアルタイム出力機能(RTO)に相当する機能は実装されていません。ただし、下記留意事項が問題とならない場合、イベントリンクコントローラ(ELC)のポートグループ出力機能と連携可能な任意のタイマ機能を組み合わせて使用することでリアルタイム出力機能と同等の波形を出力することが出来ます。

#### 【留意事項】

- タイマ機能とイベントリンクコントローラの動作クロックの差などによって意図しているタイミングで出力が切り替わらない場合があります。

- 意図しているタイミングで出力が切り替わらない場合、マルチファンクションタイマパルスユニット 2(MTU2a)や 16 ビットタイマパルスユニット(TPUa)のタイマ出力機能をご使用ください。

#### 2.9.1 仕様比較

V850ES/JF3-L に搭載されたリアルタイム出力機能に対する RX231 のイベントリンクコントローラのポートグループ出力機能の対応を表 2.13 に示します。

| 項目    | V850ES/JF3-L                                       | RX231                                                                  |

|-------|----------------------------------------------------|------------------------------------------------------------------------|

|       | RTO                                                | ELC のポートグループ出力機能<br>+任意のタイマ機能 <sup>注 1)</sup>                          |

| チャネル  | 2 チャネル                                             | 2 チャネル                                                                 |

| 出力端子数 | 最大: 6 本                                            | 最大 16 本                                                                |

|       | 1 チャネル 6 本出力または<br>2 チャネル 4+2 本出力可能                | 1 チャネル辺り最大 8 本出力可能                                                     |

| 動作    | バッファレジスタにあらかじめ設定したデータを、タ<br>イマ割り込みの発生と同時にハードウェアで出力 | バッファレジスタにあらかじめ設定したデータを指定<br>した割り込み要求の発生をトリガにあらかじめ設定し<br>た端子からハードウェアで出力 |

表 2.13 リアルタイム出力機能の対応

注1. イベントリンクコントローラに連携可能なタイマモジュールは RX230 グループ、RX231 グループユーザーズマニュアル ハードウェア編「表 20.2 ELSRn レジスタと周辺モジュールの対応」を確認してください。

ハードウェアとして互換のないリアルタイム出力機能はソフトウェアで同等の機能を再現したサンプルプログラムを用意しております。詳細は「3.サンプルプログラムの説明」を参照してください。

#### 2.10 A/D コンバータ

#### 2.10.1 仕様比較

V850ES/JF3-L に搭載された A/D コンバータの仕様に対応する RX231 グループの 12 ビット A/D コンバータ(S12ADE)機能の仕様を表 2.14 に示します。

表 2.14 A/D コンバータ機能の対応

| 項目                  | V850ES/JF3-L       | RX231                                               |  |

|---------------------|--------------------|-----------------------------------------------------|--|

| <b>サロ</b>           | A/D コンバータ          | S12ADE                                              |  |

| アナログ入力              | 8 チャネル             | 24 チャネル                                             |  |

| 分解能                 | 10 ビット             | 12 ビット                                              |  |

| A/D 変換方式            | 逐次比較方式             | 逐次比較方式                                              |  |

|                     | 連続セレクト・モード         | 連続スキャンモードで可能                                        |  |

| │<br>│ A/D 変換動作モード  | 連続スキャン・モード         | 医                                                   |  |

| 八0 変換動作 こード         | ワンショット・セレクト・モード    | シングリフセルンエードで可能                                      |  |

|                     | ワンショット・スキャン・モード    | シングルスキャンモードで可能<br>                                  |  |

|                     | ソフトウェアトリガ          | ソフトウェアトリガ                                           |  |

| A/D 変換トリガ・モード       | タイマトリガ             | 同期トリガ(MTU タイマ機能など<br><sup>(注 1)</sup> からのトリガ受け付けで可能 |  |

|                     | 外部トリガ              | 非同期トリガ(ADTRG0#端子) で<br>可能                           |  |

|                     | 立ち下がりエッジ           |                                                     |  |

| 外部トリガエッジ            | 立ち上りエッジ            | 立ち下がりエッジ                                            |  |

|                     | 両エッジ               |                                                     |  |

|                     | パワーフェイル検出機能        | コンペア機能により結果比較の                                      |  |

| <br>  変換結果比較        | A/D 変換結果とレジスタの設定値の | 実現可能。ただし、割り込みは                                      |  |

| <b>交</b> 沃州不比·大     | 大小比較条件と合致した場合に割    | なく、イベントリンク機能との                                      |  |

|                     | り込み発生              | 連携のみ                                                |  |

| 変換時間                | 2.6μs              | 0.83μs                                              |  |

| 割り込み要因/<br>DMA 起動要因 | A/D 変換終了           | スキャン終了割り込みで可能                                       |  |

注1. タイマなどとは具体的には以下のモジュールを指しています。 マルチファンクションタイマパルスユニット 2 (MTU2a) 16 ビットタイマパルスユニット(TPUa) イベントリンクコントローラ(ELC)

### 2.10.2 注意事項

# 2.10.2.1 A/D コンバータの動作状態

V850ES/JF3-L には A/D コンバータが変換動作中かを示すステータスフラグがあります。RX231 グループの 12 ビット A/D コンバータにはステータスフラグはありませんが、A/D コントロールレジスタの A/D 変換スタートビットで確認できます。

# 2.11 D/A コンバータ

#### 2.11.1 仕様比較

V850ES/JF3-L に搭載された D/A コンバータ機能の仕様に対応する RX231 グループの 12 ビット D/A コンバータ(R12DAA)機能の仕様を表 2.15 に示します。

表 2.15 D/A コンバータ機能の対応

| 香口       | V850ES/JF3-L                 | RX231                              |

|----------|------------------------------|------------------------------------|

| 項目       | D/A コンバータ                    | R12DAA                             |

| チャネル数    | 1 チャネル                       | 2 チャネル                             |

| 分解能      | 10 ビット                       | 12 ビット                             |

| 変換時間     | セトリングタイム 3us(MAX)            | 変換時間 30μs                          |

|          | AVREF1=2.7~3.6V, 外部負荷 20pF 時 |                                    |

|          |                              |                                    |

| アナログ出力電圧 | AVREF1×m/256                 | Min: 0.35V, Max: AVCC0 - 0.47      |

|          | (m=0-255 ; DA0CS0 レジスタに設定    | 基準電圧は以下の3パターンから選択可能                |

|          | した値)                         | • (AVCC0-AVSS0) × m/4096、          |

|          |                              | ・(内部基準電圧-AVSS0)×m/4096             |

|          |                              | · (VREFH-VREFL) × m/4096           |

|          |                              | (m=0-4095 ; レジスタの値)                |

| 動作モード    | <ul><li>通常モード</li></ul>      | ・通常モード                             |

|          | (レジスタ書き換えによる D/A 変換)         | (レジスタ書き換えによる D/A 変換)               |

|          | ・タイマ割り込み(INTTP2CC0 信号)に      | ・タイマ割り込み、イベントリンク機能 <sup>(注1)</sup> |

|          | よる D/A 変換                    | を組み合わせることで可能                       |

注1. イベントリンク機能の詳細については RX230 グループ、RX231 グループユーザーズマニュアル ハードウェア編「20. イベントリンクコントローラ(ELC)」を参照してください。

# 2.12 アシンクロナス・シリアル・インタフェース A (UARTA)

#### 2.12.1 仕様比較

V850ES/JF3-L に搭載されたアシンクロナス・シリアル・インタフェース A(UARTA)機能の仕様に対応する RX231 グループのシリアルコミュニケーションインタフェース (SCIg, SCIh)の調歩同期式モードの仕様を表 2.16 に示します。

表 2.16 アシンクロナス・シリアル・インタフェース機能の対応

| 1E D       | V850ES/JF3-L        | RX231                   |

|------------|---------------------|-------------------------|

| 項目         | UARTA               | SCIg, SCIh(調歩同期式モード)    |

| チャネル数      | 3 チャネル              | 7 チャネル                  |

|            |                     | チャネルごとにモジュールストップ        |

|            |                     | 状態の設定が可能                |

| 通信速度 (MAX) | 625kbps (fxx=20MHz) | 3.75Mbps(PCLKB = 30MHz) |

| 全二重通信      | 可能                  | 可能                      |

| キャラクタ長     | 7/8 ビットから選択         | 7/8/9 ビットから選択           |

| ストップビット    | 1 ビット/2 ビットから選択     | 1 ビット/2 ビットから選択         |

| パリティ       | 奇数/偶数/なし/0 から選択     | 奇数/偶数/なしから選択            |

| データ転送順     | MSB/LSB ファーストから選択   | MSB/LSB ファーストから選択       |

| データ反転出力    | 可能                  | 可能                      |

| ノイズ・フィルタ   | ノイズ・フィルタ回路により除去     | デジタルフィルタでノイズ除去可能        |

|            |                     | フィルタの有効/無効をソフトウェア       |

|            |                     | で設定可能                   |

| 受信エラー検出    | ・パリティエラー            | ・パリティエラー                |

|            | ・オーバーランエラー          | ・オーバーランエラー              |

|            | ・フレーミングエラー          | ・フレーミングエラー              |

|            |                     |                         |

| 割り込み要因     | ・受信完了/受信エラー         | ・受信データフル                |

|            | - 送信許可              | ・送信終了                   |

|            |                     | ・受信エラー                  |

|            |                     | ・送信データエンプティ             |

| DMA 起動要因   | ・受信完了               | ・受信データフル                |

|            | ・送信許可               | ・送信データエンプティ             |

|            |                     |                         |

|            |                     |                         |

#### 2.12.2 注意事項

#### 2.12.2.1 0 パリティ

V850ES/JF3-L にはパリティの種類に 0 パリティという設定があります。RX231 グループには 0 パリティに相当する設定はありません。

# 2.13 3 線式可変長シリアル I/O (CSIB)

#### 2.13.1 搭載ユニット

V850ES/JF3-L と RX231 グループに内蔵された 3 線式可変長シリアル I/O 機能のユニット一覧を表 2.19 に示します。

表 2.17 V850ES/JF3-L、RX231 の 3 線式可変長シリアル I/O 機能一覧

| 項目      | V850ES/JF3-L         | RX231                           |

|---------|----------------------|---------------------------------|

| 3線式シリアル | 3線式可変長シリアル I/O(CSIB) | ・シリアルペリフェラルインタフェース(RSPla)       |

|         |                      | ・シリアルコミュニケーションインタフェース           |

|         |                      | (SCIg, SCIh)の簡易 SPI モード/クロック同期式 |

|         |                      | モード                             |

#### 2.13.2 仕様比較

V850ES/JF3-L に搭載された 3 線式可変長シリアル I/O 機能の仕様に対応する RX231 グループのシリアルペリフェラルインタフェース (RSPIa)機能およびシリアルコミュニケーションインタフェースのクロック同期式モードの仕様を表 2.18 に示します。

表 2.18 3 線式可変長シリアル I/O 機能の対応

|                                   | V850ES/JF3-L                             | RXX                                                                 | 231                                                            |

|-----------------------------------|------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------|

| 項目                                | CSIB                                     | RSPIa                                                               | SClg, SClh<br>(簡易 SPI モード/<br>クロック同期式モード)                      |

| チャネル数                             | 3 チャネル                                   | 1 チャネル                                                              | 7チャネル                                                          |

| 通信クロック周波数<br>(MAX)                | マスタ/スレーブ共通:8MHz                          | マスタ動作時:16MHz<br>スレーブ動作時:4MHz<br>(PCLKB = 32MHz)                     | マスタ動作時:7.5MHz<br>スレーブ動作時:5MHz<br>(PCLKB = 30MHz)               |

| 動作モード                             | マスタ/スレーブ                                 | マスタ/スレーブ                                                            | マスタ/スレーブ                                                       |

| シリアル・クロックと<br>データのフェーズ切り<br>替えが可能 | シリアル·クロックとデータの<br>フェーズ切り替えが可能            | RSPCK の位相、極性を変更可<br>能                                               | クロックの位相、極性を設定<br>可能                                            |

| データ長                              | 8 ビット~16 ビット                             | 8-16,20,24,32 ビット<br>(1 ビット単位指定可能)                                  | 8ビット                                                           |

| データ転送順                            | MSB/ LSB ファーストを切り替え<br>可能                | MSB/LSB ファーストを<br>切り替え可能                                            | MSB/ LSB ファーストを<br>切り替え可能                                      |

| 送受信モード                            | シングル転送モード(送信, 受信,<br>送受信モード)             | シングル転送可能                                                            | シングル転送可能                                                       |

|                                   | 連続転送モード(送信, 受信,<br>送受信モード)               | 送信/受信バッファはそれぞれダ<br>ブルバッファ構造により連続転<br>送可能                            | 送信/受信バッファはそれぞれ<br>ダブルバッファ構造により連<br>続転送可能                       |

| 端子                                | シリアル・データ出力<br>シリアル・データ入力<br>シリアル・クロック入出力 | マスタ送出データ入出力<br>スレーブ送出データ入出力<br>クロック入出力<br>スレーブセレクト入出力<br>(SPI 動作のみ) | クロック入出力<br>送信データの出力<br>受信データの入力<br>送受信開始制御用入出力/<br>チップセレクト入力端子 |

| 割り込み要因                            | 連続送信書き込み許可<br>受信終了/受信エラー                 | 受信バッファフル<br>送信バッファエンプティ<br>RSPI エラー<br>RSPI アイドル                    | 送信終了<br>送信データエンプティ<br>受信データフル<br>受信エラー                         |

| DMA 起動要因                          | 連続送信書き込み許可<br>受信終了/受信エラー                 | 受信バッファフル<br>送信バッファエンプティ                                             | 送信データエンプティ<br>受信データフル                                          |

#### 2.14 I<sup>2</sup>C バス

#### 2.14.1 搭載ユニット

V850ES/JF3-L と RX231 グループに内蔵された I<sup>2</sup>C バス機能のユニット一覧を表 2.19 に示します。

表 2.19 V850ES/JF3-L、RX231 の I<sup>2</sup>C バス機能一覧

| 項目                  | V850ES/JF3-L        | RX231                                |

|---------------------|---------------------|--------------------------------------|

| I <sup>2</sup> C 機能 | I <sup>2</sup> C バス | ・I <sup>2</sup> C バスインタフェース(RIICa)   |

|                     |                     | ・シリアルコミュニケーションインタフェース                |

|                     |                     | (SCIg, SCIh)の簡易 I <sup>2</sup> C モード |

#### 2.14.2 仕様比較

V850ES/JF3-L に搭載された I<sup>2</sup>C バス機能の仕様に対応する RX231 グループの I<sup>2</sup>C バスインタフェース機能および、シリアルコミュニケーションインタフェースの簡易 I<sup>2</sup>C モードの仕様を表 2.20 に示します。

表 2.20 I<sup>2</sup>C バス機能の対応

|          | V850ES/JF3-L              | RX231                              |                                         |  |  |

|----------|---------------------------|------------------------------------|-----------------------------------------|--|--|

| 項目       | I²C バス                    | RIICa                              | SCIg, SCIh の<br>簡易 I <sup>2</sup> C モード |  |  |

| チャネル数    | 2 チャネル                    | 1 チャネル                             | 7チャネル                                   |  |  |

| 通信速度     | 標準モード:                    | スタンダードモード:                         | スタンダードモード:                              |  |  |

|          | ~100kbps                  | ~100kbps                           | ~100kbps                                |  |  |

|          | 高速モード:                    | ファストモード:                           | ファストモード:                                |  |  |

|          | ~350kbps                  | ~400kbps                           | ~350kbps                                |  |  |

| 通信       | I <sup>2</sup> C バスフォーマット | I <sup>2</sup> C バスフォーマット          | I <sup>2</sup> C バスフォーマット               |  |  |

| フォーマット   |                           | SMBus フォーマット                       |                                         |  |  |

| 通信動作     | マルチマスタ対応                  | マルチマスタ対応                           | シングルマスタ動作のみ                             |  |  |

|          | スレーブ動作                    | スレーブ動作                             |                                         |  |  |

| ディジタル・   | 高速モード時のみ使用可能              | ノイズ除去幅をソフトウェアで                     | ノイズ除去幅をソフトウェアで                          |  |  |

| フィルタ     |                           | 調整可能                               | 調整可能                                    |  |  |

| 消費電力低減   | 動作停止モード                   | モジュールストップ機能で                       | モジュールストップ機能で                            |  |  |

|          |                           | 実現可能                               | 実現可能                                    |  |  |

| 割り込み     | 1 種類                      | 4種類                                | 3種類                                     |  |  |

|          | ・シリアルクロックの                | EEI割り込み                            | RXI割り込み                                 |  |  |

|          | 8または9クロック目の立ち下が           | ・通信エラー/通信イベント発生                    | ・ACK 検出/受信                              |  |  |

|          | Ŋ                         | アービトレーション検出                        | TXI割り込み                                 |  |  |

|          | - ストップ・コンディション検出          | NACK 検出                            | ・NACK 検出/送信                             |  |  |

|          |                           | タイムアウト検出                           | STI 割り込み                                |  |  |

|          |                           | スタートコンディション検出                      | ・開始条件、再開始条件、                            |  |  |

|          |                           | (リスタートコンディション含む)<br>ストップコンディション検出  | 停止条件生成終了                                |  |  |

|          |                           | RXI 割り込み                           |                                         |  |  |

|          |                           | - 代代 副 9 <u>2</u> 007<br>- 受信データフル |                                         |  |  |

|          |                           | (スレーブアドレスー致時含む)                    |                                         |  |  |

|          |                           | TXI割り込み                            |                                         |  |  |

|          |                           | ・送信データエンプティ                        |                                         |  |  |

|          |                           | (スレーブアドレスー致時含む)                    |                                         |  |  |

|          |                           | TEI 割り込み                           |                                         |  |  |

|          |                           | •送信終了                              |                                         |  |  |

| DMA 起動要因 | IICn の転送終了                | 受信データフル割り込み                        | 受信割り込み                                  |  |  |

|          |                           | 送信データエンプティ割り込み                     | 送信割り込み                                  |  |  |

|          |                           |                                    |                                         |  |  |

# 2.15 DMA 機能 (DMA コントローラ)

#### 2.15.1 仕様比較

V850ES/JF3-L に搭載された DMA(Direct Memory Access)コントローラ(DMAC)機能の仕様に対応する RX231 グループの DMA コントローラ(DMACA)機能の仕様を表 2.21 に示します。

表 2.21 DMA コントローラ機能の対応

| 項目         | V850ES/JF3-L                                                                               | RX231                                              |

|------------|--------------------------------------------------------------------------------------------|----------------------------------------------------|

| 次ロ         | DMAC                                                                                       | DMACA                                              |

| チャネル数      | 4 チャネル                                                                                     | 4 チャネル                                             |

| 転送モード      | シングル転送モード                                                                                  | ノーマル転送モードで可能                                       |

|            |                                                                                            | ただし、2サイクル転送不可                                      |

| 転送単位       | 8/16 ビット                                                                                   | 8/16/32 ビット                                        |

| 最大転送回数     | 65535 回                                                                                    | 65535 回                                            |

| 転送要求       | 内蔵周辺機能割り込み                                                                                 | 周辺モジュールの割り込み                                       |

|            | 外部割り込み端子                                                                                   | 外部割り込み端子                                           |

|            | ソフトウェアトリガ                                                                                  | ソフトウェアトリガ                                          |

| 転送対象       | 内蔵周辺 I/O←→内蔵周辺 I/O<br>内蔵周辺 I/O←→内蔵 RAM<br>内蔵周辺 I/O←→外部メモリ<br>内蔵 RAM←→外部メモリ<br>外部メモリ←→外部メモリ | 予約領域を除く全領域が対象                                      |

| アドレスカウント方式 | インクリメント<br>デクリメント<br>固定                                                                    | インクリメント<br>デクリメント<br>固定<br>オフセット加算 <sup>(注1)</sup> |

| 割り込み       | DMA 転送完了割り込み                                                                               | 転送終了割り込み<br>転送エスケープ終了割り込み                          |

注1. オフセット加算設定は DMAC0 のみ設定可能です。

# 2.16 割り込み/例外処理機能

#### 2.16.1 仕様比較

V850ES/JF3-L に搭載された割り込み/例外処理機能の仕様に対応する RX231 グループの割り込みコントローラ(ICUb)/例外処理機能の仕様を表 2.22 に示します。

表 2.22 割り込み/例外処理機能の対応

| 項目        | V850ES/JF3-L                       | RX231                        |

|-----------|------------------------------------|------------------------------|

| <b>坝口</b> | 割り込み/例外処理機能                        | ICUb/例外処理                    |

| ノンマスカブル   | ・ウォッチドック・タイマ2の                     | ・NMI 端子割り込み                  |

| 割り込み      | オーバフロー                             | <ul><li>発振停止検出割り込み</li></ul> |

|           | ・NMI 端子割り込み                        | ・WDTA アンダフロー/                |

|           |                                    | リフレッシュエラー                    |

|           |                                    | ・IWDTa アンダフロー/               |

|           |                                    | リフレッシュエラー                    |

|           |                                    | ・電圧監視 1                      |

|           |                                    | ・電圧監視 2                      |

|           |                                    | ・VBATT 電圧監視                  |

| マスカブル割り込み | ・外部端子割り込み:8要因                      | ・外部端子割り込み:8要因                |

|           | <ul><li>内蔵周辺割り込み</li></ul>         | ・周辺モジュール割り込み                 |

|           |                                    | ・ソフトウェア割り込み:1要因              |

| 優先順位制御    | 8レベル                               | 16 レベル                       |

| 外部端子ノイズ除去 | ・アナログ・ディレイによるノイ                    | ・デジタルフィルタ:                   |

|           | ズ除去回路:NMI 端子、                      | NMI 端子、IRQ0~7 端子             |

|           | INTP0~7 端子                         | ・サンプリング周期3回                  |

|           | ・デジタル・ノイズ除去                        | ・サンプリング周波数:PCLK,             |

|           | ・サンプリング・クロック                       | PCLK/8, PCLK/32, PCLK/64 から選 |

|           | fxx/64, fxx/128, fxx/256, fxx/512, | 択                            |

|           | fxx/1024, fxтから選択                  | ・デジタルフィルタ                    |

|           |                                    | 有効/無効選択可能                    |

| 外部端子      | ・エッジ検出                             | ・エッジ検出                       |

| 割り込み検出    | 立ち上がり                              | 立ち上がり(NMI,IRQ0~7)            |

|           | 立ち下がり                              | 立ち下がり(NMI,IRQ0~7)            |

|           | 両エッジ                               | 両エッジ(IRQ0~7)                 |

|           | ・エッジ検出なし                           | ・Low レベル検出(IRQ0~7)           |

| ソフトウェア例外  | TRAP1n 命令、TRAP0n 命令                | INT 命令、BRK 命令                |

|           | (専用ベクタ:32 要因)                      | (無条件トラップ:16 要因)              |

| 不正命令コード例外 | あり                                 | あり(未定義命令例外)                  |

### 2.16.2 注意事項

### 2.16.2.1 チップバージョンによる差異

RX231 グループではチップバージョンの違いによって以下の仕様差があります。

- ・SDHI割り込み(ベクタ番号 40~43)はチップバージョン A、C にはありません。

- ・RSCANO割り込み(ベクタ番号52~56)はチップバージョンCにはありません。

- ・セキュリティ割り込み(ベクタ番号 111~113) はチップバージョン A、C にはありません。

# 2.17 スタンバイ機能

# 2.17.1 仕様比較

V850ES/JF3-L のスタンバイ機能と RX231 グループの対応を表 2.23 に示し、各モード遷移時の動作状態を表 2.24 に示します。

表 2.23 スタンバイ機能の対応

| 項目           | V850ES/JF3-L                                                      | RX231                                     |  |

|--------------|-------------------------------------------------------------------|-------------------------------------------|--|

| HALT<br>モード  | CPU の動作クロックのみを停止                                                  | スリープモードで実現可能<br>ただし、ウォッチドッグタイマ(WDT)は      |  |

|              | <解除要因>                                                            | 使用不可                                      |  |

|              | ・ノンマスカブル割り込み要求信号                                                  | <解除要因>                                    |  |

|              | ・マスクされていないマスカブル割り込<br>み割り込み要求信号                                   | ・全ての割り込み                                  |  |

|              | ・リセット信号                                                           | ・リセット                                     |  |

|              | (RESET 端子入力、WDT2RES 信号、低<br>電圧検出回路(LVI)、クロック・モニタ<br>(CLM)によるリセット) | (RST#端子リセット、パワーオンリセット、電圧監視リセット、IWDT リセット) |  |

| IDLE1<br>モード | クロック発振回路、PLL 動作、フラッシュ・メモリは動作を継続                                   | スリープモードとモジュールストップ機能<br>で実現可能              |  |

|              | <解除要因>                                                            | <解除要因>                                    |  |

|              | ・ノンマスカブル割り込み要求信号                                                  | ・全ての割り込み                                  |  |

|              | ・マスクされていないマスカブル割り込                                                | ・リセット                                     |  |

|              | み割り込み要求信号<br>・リセット信号                                              | (RST#端子リセット、パワーオンリセット、電圧監視リセット、IWDT リセット) |  |

|              | (RESET 端子入力、WDT2RES 信号、低電圧検出回路(LVI)、クロック・モニタ(CLM)によるリセット)         |                                           |  |

| IDLE2<br>モード | クロック発振回路、PLL 動作、フラッ<br>シュ・メモリは動作を継続                               | スリープモードとモジュールストップ機能<br>で実現可能              |  |

|              | PLL は IDLE2 モード遷移前の状態に復帰                                          | ただし PLL は通常の手順で動作/停止させ                    |  |

|              | <解除要因>                                                            | る必要あり                                     |  |

|              | ・ノンマスカブル割り込み要求信号                                                  | 。 <b>427</b> 除 亩 中、                       |  |

|              | ・マスクされていないマスカブル割り込<br>み割り込み要求信号                                   | <解除要因><br>・全ての割り込み                        |  |

|              | ・リセット信号                                                           | ・リセット                                     |  |

|              | (RESET 端子入力、WDT2RES 信号、低<br>電圧検出回路(LVI)、クロック・モニタ<br>(CLM)によるリセット) | (RST#端子リセット、パワーオンリセット、電圧監視リセット、IWDT リセット) |  |

# V850ES/JF3-L、RX231 グループ V850ES/JF3-L から RX231 グループへの移行ガイド

| 項目                                         | V850ES/JF3-L                                                                                                                           | RX231                                                                                                                                                 |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| STOP<br>モード/<br>低電圧 STOP<br>モード            | 内部回路の動作を全て停止させるモード  <解除要因> ・ノンマスカブル割り込み要求信号 ・マスクされていないマスカブル割り込み要求信号 ・リセット信号 (RESET 端子入力、WDT2RES 信号、低電圧検出回路(LVI)、クロック・モニタ (CLM)によるリセット) | ソフトウェアスタンバイモードで実現可能<br>ただし一部を除く周辺モジュールの動作は<br>不可<br><解除要因> ・ソフトウェアスタンバイで動作可能な周<br>辺モジュールによる割り込み<br>・リセット<br>(RES#端子リセット、パワーオンリセット、電圧監視リセット、IWDT リセット) |

| サブクロック<br>動作モード/<br>低電圧<br>サブクロック<br>動作モード | システム全体がサブクロックのみで動作するモード                                                                                                                | システムクロックをサブクロックに設定、および低速動作モードで実現可能                                                                                                                    |

#### 表 2.24 各モード遷移時の動作状態

|                                |      |          | V        | 350ES/JI | F3-L     |          |        |           | RX231     |             |

|--------------------------------|------|----------|----------|----------|----------|----------|--------|-----------|-----------|-------------|

| 機能                             | HALT | IDLE1    | IDLE2    | STOP     | 低電圧      | 動作サブクロック | クロック動作 | スリープ      | スリープ      | スタンバイソフトウェア |

| メインク<br>ロック                    | 0    | 0        | 0        | ×        | ×        | 0        | 0      | 0         | 0         | ×           |

| サブクロック                         | 0    | 0        | 0        | 0        | 0        | 0        | 0      | 0         | 0         | 0           |

| 内蔵発振器/<br>HOCO<br>LOCO         | 0    | 0        | 0        | 0        | 0        | 0        | 0      | 0         | 0         | ×           |

| PLL                            | 0    | ×        | ×        | ×        | ×        | 0        | 0      | 0         | 0         | ×           |

| CPU                            | ×    | ×        | ×        | ×        | ×        | 0        | 0      | ×<br>(保持) | ×<br>(保持) | ×<br>(保持)   |

| DMA                            | 0    | ×        | ×        | ×        | ×        | 0        | 0      | O<br>注1   | ×<br>(保持) | ×<br>(保持)   |

| 時計用タイマ/<br>RTC                 | 0    | 0        | 0        | O<br>注 2 | O<br>注2  | 0        | 0      | 0         | 0         | 0           |

| ウォッチドック・タイマ 2/<br>独立ウォッチドッグタイマ | 0    | 0        | 0        | 0        | 0        | 0        | 0      | 〇<br>注3   | 〇<br>注3   | O<br>注3     |

| ポート機能                          | 保持   | 保持       | 保持       | 保持       | 保持       | 0        | 0      | 0         | 0         | ×<br>(保持)   |

| 割り込み<br>コントローラ                 | 0    | ×<br>注 4 | ×<br>注 4 | ×<br>注 4 | ×<br>注 4 | 0        | 0      | 0         | 0         | 0           |

| 低電圧検出回路/<br>電圧検出回路             | 0    | 0        | 0        | 0        | 0        | 0        | 0      | 0         | 0         | 0           |

| RAM                            | 保持   | 保持       | 保持       | 保持       | 保持       | 保持       | 保持     | ×<br>(保持) | ×<br>(保持) | ×<br>(保持)   |

| レジスタ                           | 保持   | 保持       | 保持       | 保持       | 保持       | 保持       | 保持     | 保持        | 保持        | 保持          |

| その他周辺<br>モジュール                 | 注 5  | 注 5      | 注 5      | 注 5      | 注 5      | 注 5      | 注 5    | 0         | 0         | ×<br>(保持)   |

〇:動作可能、×:停止

保持は、内部レジスタ値保持、内部状態は動作中断を示します。

- 注1. スリープモード中は、システム制御関連のレジスタへの書き込みは禁止です。詳細は RX230 グループ、RX231 グループユーザーズマニュアル ハードウェア編「表 5.1 I/O レジスタアドレス一覧」を参照してください。

- 注2. サブクロックがある場合動作可能。

- 注3. ウォッチドックタイマは動作停止。

- 注4. スタンバイモードの解除のみ可能。

- 注5. 各モードによって動作可能な条件やモジュールが異なります。詳細は V850ES/JF3-L ユーザーズマニュアル ハードウェア編「21章 スタンバイ機能」を参照してください。

# 2.18 クロック・モニタ

#### 2.18.1 仕様比較

V850ES/JF3-L に搭載されたクロック・モニタ機能の仕様に対応する RX231 グループのクロック発生回路 の発振停止検出機能の仕様を表 2.25 に示します。

表 2.25 クロック・モニタ機能の対応

| 項目             | V850ES/JF3-L                                                                                          | RX231                                                                |

|----------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|                | クロック・モニタ                                                                                              | 発振停止検出機能                                                             |

| 監視対象           | メインクロック                                                                                               | メインクロック                                                              |

| 発振停止検出時の<br>動作 | リセット                                                                                                  | システムクロックに<br>メインクロックを選択時:<br>低速オンチップオシレータに切り替え、発<br>振停止検出割り込み(注1)を発生 |

|                |                                                                                                       | システムクロックに PLL を選択時:<br>PLL が自励発振に切り替わり、発振停止検<br>出割り込みを発生             |

|                |                                                                                                       | USB 専用 PLL を選択時:<br>USB 専用 PLL が自励発振に切り替わり、<br>発振停止検出割り込みを発生         |

| 機能の自動停止        | ・STOP モード~発振安定期間<br>・サンプリングクロック<br>(内蔵発振クロック)停止中<br>・CPU が内蔵発振クロック動作中<br>・メイン・クロック停止中 <sup>(注2)</sup> | なし                                                                   |

- 注1. 発振停止検出割り込みはノンマスカブル割り込みです。

- 注2. メイン・クロック発振回路の制御ビット(PCC. MCK)を使用して、ユーザソフトウェアが意図的にメイン・クロックを停止させた場合の状態

#### 2.18.2 注意事項

#### 2.18.2.1 発振停止検出機能の停止

RX231 グループの発振停止検出機能は外部要因によるメインクロックの停止に備えた機能です。そのためソフトウェアでメインクロックを停止させる場合や、ソフトウェアスタンバイモードに遷移する場合、あらかじめ発振停止検出機能を停止する必要があります。詳細は RX230 グループ、RX231 グループユーザーズマニュアル ハードウェア編「9.5.1 発振停止検出と検出後の動作」を参照してください。

#### 2.19 低電圧検出回路(LVI)

#### 2.19.1 仕様比較

V850ES/JF3-L に搭載された低電圧検出回路(LVI)機能の仕様に対応する RX231 グループの電圧検出回路 (LVDAb) 機能の仕様を表 2.26 に示します。

表 2.26 低電圧検出機能の対応

|          | V850ES/JF3-L                                                                                                                         |                                         | RX231                                                                                                                      |                                                                                                                                     |

|----------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 項目       | 低電圧検出回路(LVI)                                                                                                                         | LVDAb の<br>電圧監視 0                       | LVDAb の<br>電圧監視 1                                                                                                          | LVDAb<br>電圧監視 2                                                                                                                     |

| 電圧検出時の動作 | ・V <sub>DD</sub> < V <sub>LVI</sub> または<br>V <sub>DD</sub> < V <sub>LVI</sub> 検出で<br>マスカブル割り込みまた<br>は、リセットを要求<br>・割り込みとリセット<br>を選択可能 | ・Vdet0>VCC で<br>リセット                    | ・Vdet1>VCCで<br>リセット<br>・Vdet1>VCC、<br>VCC>Vdet1の両方、ま<br>たはどちらかで割り込み<br>要求<br>・マスカブル割り込みと<br>ノンマスカブル割り込み<br>を選択可能           | ・Vdet2>VCC または CMPA2 端子でリセット ・Vdet2>(VCC または CMPA2 端子)、 (VCC または CMPA2 端子)>Vdet2 の両 方、またはどちらかで 割り込み要求 ・マスカブル割り込みとノ ンマスカブル割り込みを選 択可能 |

| 検出電圧     | 2通り<br>2.30V<br>2.80V                                                                                                                | 4通り<br>1.90V<br>2.51V<br>2.82V<br>3.84V | 14 通り<br>1.86V<br>1.96V<br>2.20V<br>2.48V<br>2.58V<br>2.68V<br>2.79V<br>2.90V<br>3.00V<br>3.10V<br>3.84V<br>4.02V<br>4.14V | 4通り<br>3.84V<br>4.02V<br>4.14V<br>4.29V                                                                                             |

- 注1. 動作許可かつ、動作モードを「電源電圧<検出電圧時に内部リセット信号を発生」に設定した場合、低電圧検出回路によるリセット以外のリセット要求が発生するまで低電圧検出回路(LVI)は停止できません。

- 注2. フラッシュメモリの書き込みまたは削除中はノンマスカブル割り込みを発生させないでください。

#### 2.19.2 注意事項

# 2.19.2.1 再度電圧検出を設定する際の注意事項

RX231 グループでは 1 度電圧検出を行った後、検出フラグのクリア等の再設定が必要です。詳細は RX230 グループ、RX231 グループユーザーズマニュアル ハードウェア編「8.電圧検出回路(LVDAb)」を参照してください。

# 2.20 CRC 機能

# 2.20.1 仕様比較

V850ES/JF3-L に搭載された CRC 機能の仕様に対応する RX231 グループの CRC 演算器(CRC)機能の仕様を表 2.27 に示します。

表 2.27 CRC 機能の対応

| 項目    | V850ES/JF3-L            | RX231                   |

|-------|-------------------------|-------------------------|

|       | CRC 機能                  | CRC                     |

| データ単位 | 8bit                    | 8bit                    |

| 方式    | CRC-16-CCITT (16bitCRC) | CRC-16-CCITT (16bitCRC) |

|       | $X^{16}+X^{12}+X^{5}+1$ | $X^{16}+X^{12}+X^5+1$   |

|       |                         | CRC-16-IBM (16bitCRC)   |

|       |                         | $X^{16}+X^{15}+X^2+1$   |

|       |                         | CRC-8-ATM (8bitCRC)     |

|       |                         | $X^8 + X^2 + X + 1$     |

| データ転送 | LSB 固定                  | MSB/LSB から選択可能          |

# 3. サンプルプログラムの説明

本アプリケーションノートでは RX231 とハードウェア互換のない機能をソフトウェアで再現したサンプルプログラムを同梱しています。

サンプルプログラムはルネサスエレクトロニクスホームページから最新バージョンを入手してください。

# 3.1 動作確認環境

表 3.1 に本サンプルプログラムの動作確認環境を示します。

表 3.1 動作確認環境

| 項目                  | 内容                                                       |

|---------------------|----------------------------------------------------------|

| 使用マイコン              | R5F52318ADFP                                             |

| 動作周波数               | ・メインクロック: 8MHz                                           |

|                     | ·PLL: 54MHz (メインクロック 2 分周 13.5 逓倍)                       |

|                     | ·HOCO: 停止                                                |

|                     | ·LOCO: 4MHz                                              |

|                     | ·システムクロック (ICLK): 54MHz (PLL 1 分周)                       |

|                     | ·周辺モジュールクロック A (PCLKA): 54MHz(PLL 1 分周)                  |

|                     | ·周辺モジュールクロック B (PCLKB): 27MHz (PLL 2 分周)                 |

|                     | ·周辺モジュールクロック D (PCLKD): 54MHz(PLL1 分周)                   |

|                     | ·FlashIF クロック(FCLK): 27MHz(PLL 2 分周)                     |

|                     | ·外部バスクロック(BCLK): 27MHz(PLL 2 分周)                         |

| 動作電圧                | 3.3V                                                     |

| 統合開発環境              | ルネサスエレクトロニクス製                                            |

|                     | e <sup>2</sup> studio Version 2021-10                    |

| コンパイラ               | ルネサスエレクトロニクス製                                            |

|                     | C/C++ Compiler Package for RX Family V.3.03.00           |

|                     | 統合開発環境のデフォルト設定を使用しています。                                  |

| lodefine.h のバージョン   | 1.01                                                     |

| エンディアン              | リトルエンディアン                                                |

| 動作モード               | シングルチップモード                                               |

| プロセッサモード            | スーパバイザモード                                                |

| サンプルプログラムの<br>バージョン | Version 1.00                                             |

| 使用ボード               | Renesas Starter Kit for RX231 (製品型名: RTK5005231SxxxxxBE) |

# 3.2 プロジェクト構成

本アプリケーションノートのサンプルプロジェクト一覧を表 3.2 に、コード生成機能によって生成されたソースコードに変更を加えているファイルを表 3.3 に示します。

表 3.2 プロジェクト一覧

| 機能             | プロジェクト名              | 内容                                                                                                                                                          |

|----------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 外部トリガ PWM 出力機能 | external_input_rx231 | V850ES/JF3-L での外部トリガ入<br>力によるカウント開始と PWM<br>出力を RX231 グループでの IRQ<br>外部入力割り込み <sup>(注1)</sup> と マルチ<br>ファンクションタイマパルスユ<br>ニットの PWM モード 1 で再現<br>したプロジェクト      |

| 1ショットパルス出力機能   | one_shot_pulse_rx231 | V850ES/JF3-L での外部トリガ入<br>カによるカウント開始とワン<br>ショット・パルス出力を RX231<br>グループでの IRQ 外部入力割り<br>込み <sup>(注1)</sup> と マルチファンクショ<br>ンタイマパルスユニットの PWM<br>モード 1 で再現したプロジェクト |

| リアルタイム出力機能     | rto_output_rx231     | V850ES/JF3-L でのリアルタイム<br>出力機能をイベントリンクコン<br>トローラ のポートグループ出力<br>機能と TMR で再現したプロジェ<br>クト                                                                       |

注1. RSK ボードの SW1(タクタイルスイッチ)と接続しています。

#### 表 3.3 コード生成機能によって生成されたソースコードに変更を加えているファイル

| プロジェクト               | フォルダ       | ファイル名              | 概要            |

|----------------------|------------|--------------------|---------------|

| external_input_rx231 | Config_ICU | Config_ICU_user.c  | ユーザ実装用の割り込み処理 |

| one_shot_pulse_rx231 | Config_ICU | Config_ICU_user.c  | ユーザ実装用の割り込み処理 |

|                      | Config_MTU | Config_MTU0_user.c | ユーザ実装用の割り込み処理 |

| rto_output_rx231     | Config_ICU | Config_ICU_user.c  | ユーザ実装用の割り込み処理 |

|                      | Config_TMR | Config_TMR0_user.c | ユーザ実装用の割り込み処理 |

追加処理の詳細は「3.5 フローチャート」を参照してください。スマートコンフィグレータのコード生成機能によって生成されたソースコードをそのまま使用している部分については省略します。

# 3.3 関数一覧

表 3.4 にサンプルプログラムで使用する関数を示します。

表 3.4 サンプルプログラムで使用する関数

| 関数名                           | 概要                       |  |  |

|-------------------------------|--------------------------|--|--|

| main                          | メイン処理                    |  |  |

| r_Config_ICU_irq1_interrupt   | 外部割り込み処理                 |  |  |

| r_Config_MTU0_tgib0_interrupt | MTU0 のコンペアマッチ割り込み処理      |  |  |

|                               | (1 ショットパルス出力機能のサンプルのみ使用) |  |  |

| r_Config_TMR0_cmia0_interrupt | TMR0 のコンペアマッチ割り込み処理      |  |  |

|                               | (リアルタイム出力機能のサンプルのみ使用)    |  |  |

スマートコンフィグレータのコード生成機能によって生成されたソースコードをそのまま使用している部分については省略します。

# 3.4 関数仕様

サンプルプログラムの関数仕様を以下に示します。

| main  |                  |

|-------|------------------|

| 概要    | メイン処理            |

| ヘッダ   | なし               |

| 宣言    | void main (void) |

| 説明    | 初期設定を行います。       |

| 引数    | なし               |

| リターン値 | なし               |

| r_Config_ICU_irq1_interrupt |                                                       |  |  |

|-----------------------------|-------------------------------------------------------|--|--|

| 概要                          | IRQ1 割り込み処理                                           |  |  |

| ヘッダ                         | Config_ICU.h                                          |  |  |

| 宣言                          | static void r_Config_ICU_irq1_interrupt (void)        |  |  |

| 説 明 IRQ1の割り込み処理を行います。       |                                                       |  |  |

|                             | IRQ1 の割り込み処理では MTU0 のカウントを開始させます。                     |  |  |

| 引数                          | なし                                                    |  |  |

| リターン値なし                     |                                                       |  |  |

| 備考                          | 本関数はスマートコンフィグレータのコード生成機能によって生成されます。                   |  |  |

|                             | external_input_rx231 と one_shot_pulse_rx231 でのみ使用します。 |  |  |

| r_Config_MTU0_tgib0_interrupt       |                                                  |  |  |

|-------------------------------------|--------------------------------------------------|--|--|

| 概要                                  | MTU0 コンペアマッチ B 割り込み処理                            |  |  |

| ヘッダ                                 | Config_MTU0.h                                    |  |  |

| 宣言                                  | static void r_Config_MTU0_tgib0_interrupt (void) |  |  |

| 説明                                  | MTUOのコンペアマッチ割り込み処理を行います。                         |  |  |

|                                     | MTU0 のコンペアマッチ割り込み処理では MTU0 のカウントを停止させます。         |  |  |

| 引数                                  | なし                                               |  |  |

| リターン値                               | リターン値なし                                          |  |  |

| 備考本は関数はスマートコンフィグレータのコード生成機能によって生成され |                                                  |  |  |

|                                     | one_shot_pulse_rx231 でのみ使用します。                   |  |  |

| r_Config_TMR0_cmia0_interrupt |                                                     |  |  |  |

|-------------------------------|-----------------------------------------------------|--|--|--|

| 概要                            | TMRO コンペアマッチ A 割り込み処理                               |  |  |  |

| ヘッダ                           | ヘッダ Config_TMR0.h                                   |  |  |  |

| 宣言                            | 宣言 static void r_Config_TMR0_cmia0_interrupt (void) |  |  |  |

| 説明                            | TMROのコンペアマッチ割り込み処理を行います。                            |  |  |  |

|                               | TMR0 のコンペアマッチ割り込み処理では PDBF1 レジスタを設定します。             |  |  |  |

| 引数                            | なし                                                  |  |  |  |

| リターン値                         | なし                                                  |  |  |  |

| 備考                            | 本関数はスマートコンフィグレータのコード生成機能によって生成されます。                 |  |  |  |

|                               | rto_output_rx231 でのみ使用します。                          |  |  |  |

# 3.5 フローチャート

本サンプルプログラムはコード生成機能を使用しています。本章ではハードウェア互換のない機能を再現するうえで e<sup>2</sup> studio から生成されるプログラムに変更を加えた関数のフローチャートを示します。その他各周辺機能などの詳細は、スマートコンフィグレータの設定画面や生成コードを参照してください。

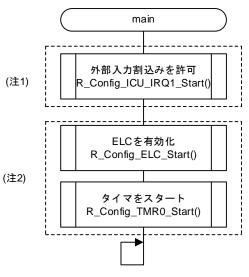

#### 3.5.1 メイン

図 3.1 にメイン処理のフローチャートを示します。

図 3.1 メイン処理

- 注1. one\_shot\_pulse\_rx231、external\_input\_rx231 のみ存在する処理。

- 注2. rto\_output\_rx231 のみ存在する処理。

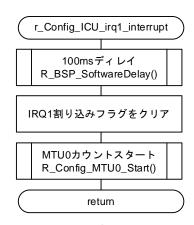

#### 3.5.2 外部割り込み処理

図 3.2 に外部割り込み処理のフローチャートを示します。

図 3.2 外部割り込み処理

100ms ディレイは SW1(タクタイルスイッチ)のチャタリング対策処理です。

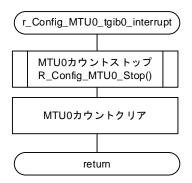

### 3.5.3 ワンショットパルス出力機能の MTU0 割り込み処理

図 3.3 にワンショットパルス出力機能のタイマ割り込み処理のフローチャートを示します。

図 3.3 ワンショットパルス出力機能のタイマ割り込み処理

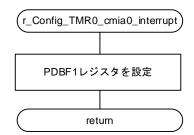

#### 3.5.4 リアルタイム出力機能の TMR0 割り込み処理

図 3.4 にリアルタイム出力機能のタイマ割り込み処理のフローチャートを示します。

図 3.4 リアルタイム出力機能のタイマ割り込み処理

### 4. プロジェクトをインポートする方法

サンプルプログラムは  $e^2$  studio のプロジェクト形式で提供しています。本章では、 $e^2$  studio ヘプロジェクトをインポートする方法を示します。インポート完了後、ビルドおよびデバッグの設定を確認してください。

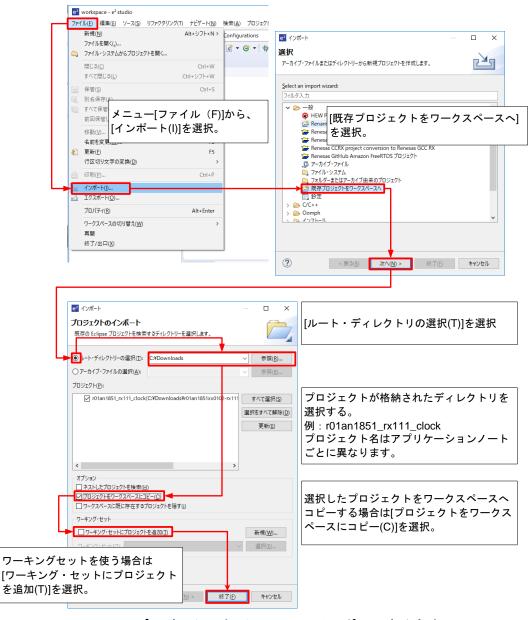

#### 4.1 e<sup>2</sup> studio での手順

$e^2$  studio でご使用になる際は、下記の手順で  $e^2$  studio にインポートしてください。

(使用する e<sup>2</sup> studio のバージョンによっては画面が異なる場合があります)

図 4.1 プロジェクトを e² studio にインポートする方法

注. e2 studio で管理するプロジェクトのフォルダ名、およびそのフォルダに至るファイルパスには、 空白文字の他、半角カナ文字、全角文字、半角記号(特に'\$','#','%') が混じらないようにしてください。

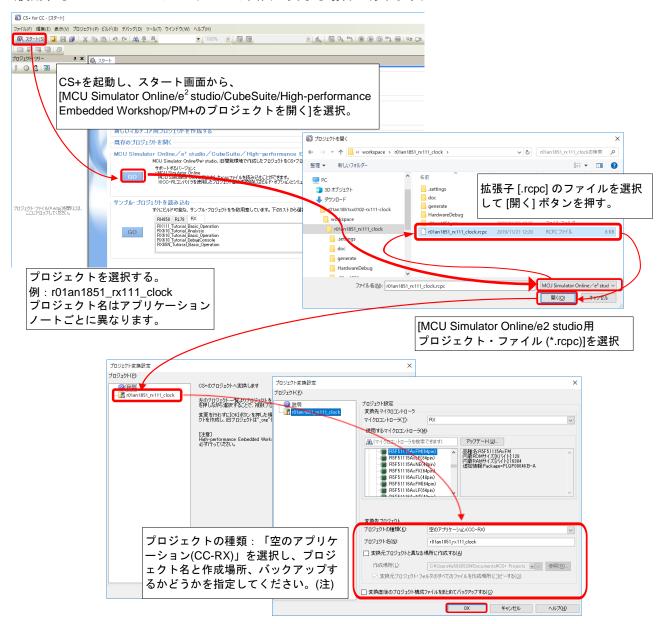

### 4.2 CS+での手順

CS+でご使用になる際は、下記の手順で CS+にインポートしてください。

(使用する CS+のバージョンによっては画面が異なる場合があります)

図 4.2 プロジェクトを CS+にインポートする方法

注. CS+で管理するプロジェクトのフォルダ名、およびそのフォルダに至るファイルパスには、空白文字の他、半角カナ文字、全角文字、半角記号(特に'\$','#','%') が混じらないようにしてください。

# 5. 参考ドキュメント

ユーザーズマニュアル: ハードウェア

RX230 グループ、RX231 グループユーザーズマニュアル ハードウェア編 (R01UH0496)

V850ES/JF3-L ユーザーズマニュアル ハードウェア編 (R01UH0017)

(最新版をルネサス エレクトロニクスホームページから入手してください)

テクニカルアップデート/テクニカルニュース

(最新版をルネサス エレクトロニクスホームページから入手してください)

ユーザーズマニュアル: 開発環境

RX ファミリ CC-RX コンパイラユーザーズマニュアル (R20UT3248)

(最新版をルネサス エレクトロニクスホームページから入手してください)

# V850ES/JF3-L、RX231 グループ V850ES/JF3-L から RX231 グループへの移行ガイド

# 改訂記録

|      |           | 改訂内容 |      |

|------|-----------|------|------|

| Rev  | 発行日       | ページ  | ポイント |

| 1.00 | Dec.29.21 | -    | 初版発行 |

|      |           |      |      |

#### 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意事項については、本ドキュメントおよびテクニカルアップデートを参照してください。

#### 1. 静電気対策

CMOS 製品の取り扱いの際は静電気防止を心がけてください。CMOS 製品は強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、当社が出荷梱包に使用している導電性のトレーやマガジンケース、導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。また、CMOS 製品を実装したボードについても同様の扱いをしてください。

#### 2. 電源投入時の処置

電源投入時は、製品の状態は不定です。電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。外部 リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の状態は保証できません。同様に、内蔵パワーオン リセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

#### 3. 電源オフ時における入力信号

当該製品の電源がオフ状態のときに、入力信号や入出力プルアップ電源を入れないでください。入力信号や入出力プルアップ電源からの電流注入により、誤動作を引き起こしたり、異常電流が流れ内部素子を劣化させたりする場合があります。資料中に「電源オフ時における入力信号」についての記載のある製品は、その内容を守ってください。

#### 4. 未使用端子の処理

未使用端子は、「未使用端子の処理」に従って処理してください。CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。

#### 5. クロックについて

リセット時は、クロックが安定した後、リセットを解除してください。プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子(または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

#### 6. 入力端子の印加波形