U2A-EVA, U2A16, U2A8, U2A6 Switching voltage regulator(SVR) guideline

Revision : 1.6 Document Number : LLWEB-10029051 Date : May 30, 2023 Automotive MCU technology department Renesas Electronics Corporation

All information described in this document is current as of the date of publication. Renesas Electronics may make changes to the products or specifications described in this document without notice. Please check the latest information released by Renesas Electronics website etc.

### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc. Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10.Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14.Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.5.0-1 October 2020)

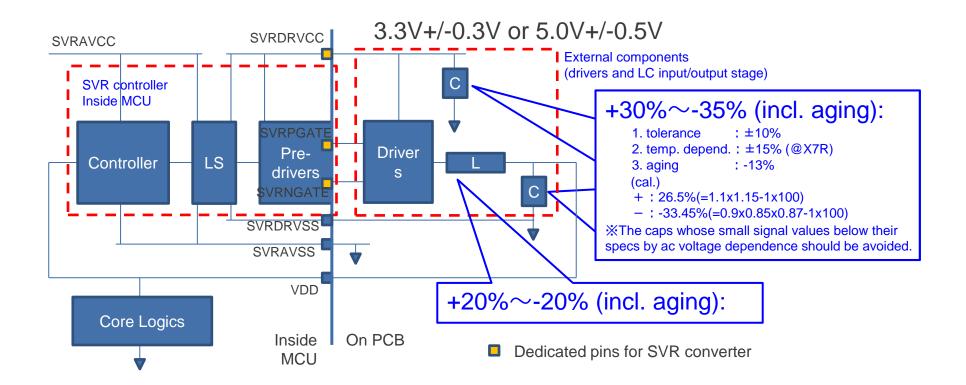

### U2A-EVA, U2A16, U2A8, U2A6 SVR circuit Case1: SVRDRVCC=5V and SYSVCC=VCC=SVRAVCC=3.3V

Comply with the guidelines below in mounting to obtain a VDD within the specified range if you are using a Target MOSFETs as an SVR drivers to handle the VDD power supply. However, the guidelines specifically apply when the SVR is that stated above. Using a different transistor will require separate detailed consideration.

Updated on ver1.5

RENESAS

|                              | SVRDRVCC                       |           | 5V             | Item                                               | # | Reference<br>value (typ.) | Note                                                                                                                                                                      | Placement                                                                                                                             |

|------------------------------|--------------------------------|-----------|----------------|----------------------------------------------------|---|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| <b>_</b> _                   | SVRAVCC                        | <b>4</b>  | 3.3V(SYSVCC)   | MOSFET                                             | 1 | See page 5                | Target MOSFETs is shown<br>on the next page.                                                                                                                              | Close to SVRPGATE and SVRNGATE<br>pin of MCU. Connect Pch MOSFET's<br>source to SVRDRVCC. Connect Nch<br>MOSFET's source to SVRDRVSS. |

| SVR controller<br>Inside MCU | SVRPGAT                        | 3<br>E 1  |                | Inductor                                           | 2 | See page 6<br>and 7       | Recommend parts is shown on pages 6 and 7. When using other parts, select parts with the same inductance value and close DC resistance(DCR) value as the recommend parts. | Close to MOSFET                                                                                                                       |

| Controller – LS              |                                |           |                | Capacitor<br>(between<br>SVRAVCC and<br>SVRAVSS)   | 3 | 1uF                       | Capacitance tolerance: $\pm 10\%$ ,<br>Temperature characteristics: X7R, X8R,<br>ESR: <50 m $\Omega$                                                                      | Close to SVRAVCC and SVRAVSS pin of MCU                                                                                               |

| -                            | SVRNGAT<br>SVRDRVSS<br>SVRAVSS |           | bint grounding | Capacitor<br>(between<br>SVRDRVCC and<br>SVRDRVSS) | 4 | ≥ 14uF                    | Capacitance tolerance: $\pm 10\%$ ,<br>Temperature characteristics: X7R, X8R,<br>ESR <10 m $\Omega$ (@0.1MHz to 5MHz, total value of parts)                               | Close to SVRDRVCC and<br>SVRDRVSS pin of MCU                                                                                          |

|                              | VDD                            | for SVRDF | DRVSS *5       | Capacitor<br>(between VDD and<br>SVRDRVSS)         | 5 | See page 6<br>and 7       | Capacitance tolerance: $\pm 10\%$ ,<br>Temperature characteristics: X7R, X8R,<br>ESR <10 m $\Omega$ (@0.1MHz to 5MHz, total value of parts)                               | Close to Inductor                                                                                                                     |

| Logic                        | VSS                            |           |                | Capacitor<br>(between VDD and<br>VSS)              | 6 | 0.1uF x 8                 | Capacitance tolerance: $\pm 10\%$ ,<br>Temperature characteristics: X7R, X8R,<br>ESR: <50 m $\Omega$                                                                      | Close to thermal ball of MCU (opposite side of MCU of PCB)                                                                            |

|                              | Inside MCU                     | PCB       |                |                                                    |   |                           |                                                                                                                                                                           |                                                                                                                                       |

#### CAUTION

- 1. Load transient current of VDD (dl) should be kept the specification. Please refer the user's manual.

- 2. SVRDRVCC and SVRDRVSS should be separated from other power/ground for EMC improving. (e.g. single point grounding)

- 3. Output resistance and dead time of SVRPGATE and SVRNGATE can be configured by option byte settings. Please refer the user's manual.

### U2A-EVA, U2A16, U2A8, U2A6 SVR circuit Case2: SVRDRVCC=SYSVCC=VCC=SVRAVCC=3.3V/5V

Comply with the guidelines below in mounting to obtain a VDD within the specified range if you are using a Target MOSFETs as an SVR drivers to handle the VDD power supply. However, the guidelines specifically apply when the SVR is that stated above. Using a different transistor will require separate detailed consideration.

Updated on ver1.5

**KENESAS**

| 1                                             |                                                    |   |                        |                                                                                                                                                                           |                                                                                                                                       |

|-----------------------------------------------|----------------------------------------------------|---|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| SVRDRVCC                                      | ltem                                               | # | Reference value (typ.) | Note                                                                                                                                                                      | Placement                                                                                                                             |

| SVRAVCC                                       | MOSFET                                             | 1 | See page 5             | Target MOSFETs is shown on the next page.                                                                                                                                 | Close to SVRPGATE and SVRNGATE<br>pin of MCU. Connect Pch MOSFET's<br>source to SVRDRVCC. Connect Nch<br>MOSFET's source to SVRDRVSS. |

| 3<br>SVR controller<br>Inside MCU<br>SVRPGATE | Inductor                                           | 2 | See page 6<br>and 7    | Recommend parts is shown on pages 6 and 7. When using other parts, select parts with the same inductance value and close DC resistance(DCR) value as the recommend parts. | Close to MOSFET                                                                                                                       |

| Controller LS Pre-<br>drivers                 | Capacitor<br>(between<br>SVRAVCC and<br>SVRAVSS)   | 3 | 1uF                    | Capacitance tolerance: $\pm 10\%$ ,<br>Temperature characteristics: X7R, X8R,<br>ESR: <50 m $\Omega$                                                                      | Close to SVRAVCC and SVRAVSS pin of MCU                                                                                               |

| SVRDRVSS<br>SVRAVSS single point grounding    | Capacitor<br>(between<br>SVRDRVCC and<br>SVRDRVSS) | 4 | ≥ 14uF                 | Capacitance tolerance: $\pm 10\%$ ,<br>Temperature characteristics: X7R, X8R,<br>ESR <10 m $\Omega$ (@0.1MHz to 5MHz, total value of parts)                               | Close to SVRDRVCC and<br>SVRDRVSS pin of MCU                                                                                          |

| VDD                                           | Capacitor<br>(between VDD and<br>SVRDRVSS)         | 5 | See page 6<br>and 7    | Capacitance tolerance: $\pm 10\%$ ,<br>Temperature characteristics: X7R, X8R,<br>ESR <10 m $\Omega$ (@0.1MHz to 5MHz, total value of parts)                               | Close to Inductor                                                                                                                     |

| Logic 5                                       | Capacitor<br>(between VDD and<br>VSS)              | 6 | 0.1uF x 8              | Capacitance tolerance: $\pm 10\%$ ,<br>Temperature characteristics: X7R, X8R,<br>ESR: <50 m $\Omega$                                                                      | Close to thermal ball of MCU (opposite side of MCU of PCB)                                                                            |

| Inside MCU PCB                                |                                                    |   |                        |                                                                                                                                                                           |                                                                                                                                       |

#### CAUTION

- 1. Load transient current of VDD (dl) should be kept the specification. Please refer the user's manual.

- 2. SVRDRVCC and SVRDRVSS should be separated from other power/ground for EMC improving. (e.g. single point grounding)

- 3. Output resistance and dead time of SVRPGATE and SVRNGATE can be configured by option byte settings. Please refer the user's manual.

The following table shows the combinations used for evaluation.

| Supplier | Nch/Pch |                |          |      |        |          |          |

|----------|---------|----------------|----------|------|--------|----------|----------|

|          |         |                | Rdson[m0 | Dhm] | Vth[V] | Ciss[pF] | Crss[pF] |

|          |         |                | Typ Max  |      | Max    | Тур      | Тур      |

| ROHM     | Nch     | RTR040N03HZGTL | 36       | 50   | 1.5    | 475      | 70       |

|          | Pch     | RTR030P02HZGTL | 60       | 85   | -2.0   | 840      | 100      |

For details of MOSFET, please contact each supplier.

#### Note:

If prefer using the different transistor other than the above, please choose the transistor as equivalent as the above each specification, and fully evaluate and judge by customer liability.

# **25Configuration of Lout and Cout for U2AEVA, U2A16**

The following table shows the two combinations (a,b) used for evaluation.

|                                      | Value | Recommended parts, Supplier | а            | b            |

|--------------------------------------|-------|-----------------------------|--------------|--------------|

| Switching frequency<br>(Option byte) | -     | -                           | 434kHz       | 868kHz       |

| 2 Inductor                           | 4.7uH | SPM5030VT-4R7M-D, TDK       | $\checkmark$ | N/A          |

| (Lout)                               | 2.2uH | SPM5030VT-2R2M-D, TDK       | N/A          | $\checkmark$ |

|                                      | 22uF  | GCM32ER71A226KE12, Murata   | $\checkmark$ | $\checkmark$ |

|                                      | 22uF  | GCM32ER71A226KE12, Murata   | $\checkmark$ | $\checkmark$ |

|                                      | 22uF  | GCM32ER71A226KE12, Murata   | $\checkmark$ | $\checkmark$ |

| 5 Capacitor                          | 22uF  | GCM32ER71A226KE12, Murata   | $\checkmark$ | $\checkmark$ |

| (between VDD and VSS)                | 22uF  | GCM32ER71A226KE12, Murata   | $\checkmark$ | $\checkmark$ |

| (Cout)                               | 22uF  | GCM32ER71A226KE12, Murata   | $\checkmark$ | N/A          |

|                                      | 22uF  | GCM32ER71A226KE12, Murata   | $\checkmark$ | N/A          |

|                                      | 22uF  | GCM32ER71A226KE12, Murata   | $\checkmark$ | N/A          |

|                                      |       | Total                       | 176uF        | 110uF        |

For details of Inductor and Capacitor, please contact each supplier.

# **2 5 Configuration of Lout and Cout for U2A8, U2A6**

The following table shows the two combinations (a,b) used for evaluation.

|                                      | Value | Recommended parts, Supplier | а            | b            |

|--------------------------------------|-------|-----------------------------|--------------|--------------|

| Switching frequency<br>(Option byte) | -     | -                           | 434kHz       | 868kHz       |

| ②Inductor                            | 10uH  | SPM6545VT-100M-D, TDK       | $\checkmark$ | N/A          |

| (Lout)                               | 4.7uH | SPM5030VT-4R7M-D, TDK       | N/A          | $\checkmark$ |

| 5 Capacitor                          | 47uF  | GCM32ER70J476ME19, Murata   | $\checkmark$ | $\checkmark$ |

| (between VDD and VSS)                | 47uF  | GCM32ER70J476ME19, Murata   | $\checkmark$ | N/A          |

| (Cout)                               |       | Total                       | 94uF         | 47uF         |

For details of Inductor and Capacitor, please contact each supplier.

### L,C variations acceptable for SVR

### **Option byte settings for U2A-EVA [1/3]**

Table 1: Option byte settings are fixed values for each configurations (SVRDRVCC, Fsw, Cout, Lout). Table 2:

Table1 Option byte for PID internal ADC and output pulse width setting

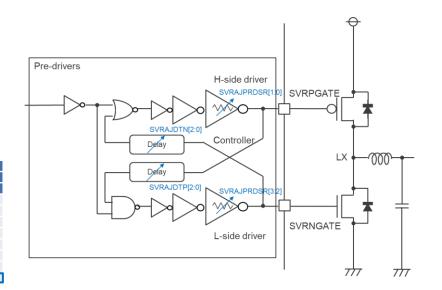

- Basically, set SVRAJPRDSR [3:0] with 4'b1111. However, adjustment for EMC noise reduction is possible. When adjusting, efficiency will worse, so please consider the trade-off between efficiency and noise reduction.

- Adjusting SVRAJDTP [2:0] and SVRAJDTN [2:0] to match the MOSFET can optimize efficiency. Please refer to the following page.

|                                    |           |           |           |                 |                    | byte for tib, inter |                    |                | <u>un soung</u>  |                   |                     |                 | 10 |

|------------------------------------|-----------|-----------|-----------|-----------------|--------------------|---------------------|--------------------|----------------|------------------|-------------------|---------------------|-----------------|----|

| Configurations Option byte setting |           |           |           |                 |                    |                     |                    |                |                  |                   |                     |                 |    |

| SVRDRVCC [V]                       | Fsw [MHz] | Cout [uF] | Lout [uH] | SVRFSWMODE[1:0] | SVRKPVSCL[13:0]    | SVRKIVSCL[13:0]     | SVRKDVSCL[13:0]    | SVRADNSMP[7:0] | SVRADTHRESH[7:0] | SVRADTHRESHE[7:0] | SVRMINSKIPDUTY[1:0] | SVRMAXDUTY[7:0] |    |

| 5                                  | 0.434     | 176       | 4.7       | 2'b00           | 14'b00001110000101 | 14'b00010010111000  | 14'b00001111101100 | 8'b00010010    | 8'b01111101      | 8'b11111001       | 2'b11               | 8'b11111100     |    |

| 5                                  | 0.868     | 110       | 2.2       | 2'b01           | 14'b00010000011111 | 14'b00010110000110  | 14'b00010010010111 | 8'b00010010    | 8'b01111101      | 8'b01111001       | 2'b11               | 8'b01111100     |    |

| 3.3                                | 0.434     | 176       | 4.7       | 2'b00           | 14'b00010101100001 | 14'b00011100110110  | 14'b00010111111110 | 8'b00010010    | 8'b01111101      | 8'b11111001       | 2'b11               | 8'b11111100     |    |

| 3.3                                | 0.868     | 110       | 2.2       | 2'b01           | 14'b00011001001100 | 14'b00100001110001  | 14'b00011100000011 | 8'b00010010    | 8'b01111101      | 8'b01111001       | 2'b11               | 8'b01111100     |    |

#### Table2 Option byte for gate driver

| Opti            | Option byte setting |               |  |  |  |  |  |  |  |  |

|-----------------|---------------------|---------------|--|--|--|--|--|--|--|--|

| SVRAJPRDSR[3:0] | SVRAJDTP[2:0]       | SVRAJDTN[2:0] |  |  |  |  |  |  |  |  |

| 4'b1111         | 3'b111              | 3'b111        |  |  |  |  |  |  |  |  |

## **Option byte settings for U2A16 [2/3]**

Table 1: Option byte settings are fixed values for each configurations (SVRDRVCC, Fsw, Cout, Lout). Table 2:

Table1 Option byte for PID internal ADC and output pulse width setting

- Basically, set SVRAJPRDSR [3:0] with 4'b1111. However, adjustment for EMC noise reduction is possible. When adjusting, efficiency will worse, so please consider the trade-off between efficiency and noise reduction.

- Adjusting SVRAJDTP [2:0] and SVRAJDTN [2:0] to match the MOSFET can optimize efficiency. Please refer to the following page.

|              |           |           |           |                 |                    | byte for file, inter |                    |                | an soung         |                   |                     |                 |

|--------------|-----------|-----------|-----------|-----------------|--------------------|----------------------|--------------------|----------------|------------------|-------------------|---------------------|-----------------|

|              | Configur  | ration    | s         |                 |                    |                      | Option byte s      | etting         |                  |                   |                     |                 |

| SVRDRVCC [V] | Fsw [MHz] | Cout [uF] | Lout [uH] | SVRFSWMODE[1:0] | SVRKPVSCL[13:0]    | SVRKIVSCL[13:0]      | SVRKDVSCL[13:0]    | SVRADNSMP[7:0] | SVRADTHRESH[7:0] | SVRADTHRESHE[7:0] | SVRMINSKIPDUTY[1:0] | SVRMAXDUTY[7:0] |

| 5            | 0.434     | 176       | 4.7       | 2'b00           | 14'b00001110000101 | 14'b00010010111000   | 14'b00001111101100 | 8'b00010000    | 8'b10101010      | 8'b11111001       | 2'b11               | 8'b11111100     |

| 5            | 0.868     | 110       | 2.2       | 2'b01           | 14'b00010000011111 | 14'b00010110000110   | 14'b00010010010111 | 8'b00010000    | 8'b00101010      | 8'b01111001       | 2'b11               | 8'b01111100     |

| 3.3          | 0.434     | 176       | 4.7       | 2'b00           | 14'b00010101100001 | 14'b00011100110110   | 14'b00010111111110 | 8'b00010000    | 8'b10101010      | 8'b11111001       | 2'b11               | 8'b11111100     |

| 3.3          | 0.868     | 110       | 2.2       | 2'b01           | 14'b00011001001100 | 14'b00100001110001   | 14'b00011100000011 | 8'b00010000    | 8'b00101010      | 8'b01111001       | 2'b11               | 8'b01111100     |

#### Table2 Option byte for gate driver

| Opti            | on byte se    | tting         |  |

|-----------------|---------------|---------------|--|

| SVRAJPRDSR[3:0] | SVRAJDTP[2:0] | SVRAJDTN[2:0] |  |

| 4'b1111         | 3'b111        | 3'b111        |  |

## Option byte settings for U2A8, U2A6 [2/3]

Table 1: Option byte settings are fixed values for each configurations (SVRDRVCC, Fsw, Cout, Lout). Table 2:

Table1 Option byte for PID internal ADC and output pulse width setting

- Basically, set SVRAJPRDSR [3:0] with 4'b1111. However, adjustment for EMC noise reduction is possible. When adjusting, efficiency will worse, so please consider the trade-off between efficiency and noise reduction.

- Adjusting SVRAJDTP [2:0] and SVRAJDTN [2:0] to match the MOSFET can optimize efficiency. Please refer to the following page.

|              |           |           |           |                     |                    | byte for fild, inten |                    |                | <u>in soung</u>  |                   |                     |                 |  |  |

|--------------|-----------|-----------|-----------|---------------------|--------------------|----------------------|--------------------|----------------|------------------|-------------------|---------------------|-----------------|--|--|

| (            | Configur  | ation     | s         | Option byte setting |                    |                      |                    |                |                  |                   |                     |                 |  |  |

| SVRDRVCC [V] | Fsw [MHz] | Cout [uF] | Lout [uH] | SVRFSWMODE[1:0]     | SVRKPVSCL[13:0]    | SVRKIVSCL[13:0]      | SVRKDVSCL[13:0]    | SVRADNSMP[7:0] | SVRADTHRESH[7:0] | SVRADTHRESHE[7:0] | SVRMINSKIPDUTY[1:0] | SVRMAXDUTY[7:0] |  |  |

| 5            | 0.434     | 94        | 10        | 2'b00               | 14'b00011001000001 | 14'b00101001111010   | 14'b00010110010010 | 8'b00010000    | 8'b10101010      | 8'b11111001       | 2'b11               | 8'b11111100     |  |  |

| 5            | 0.868     | 47        | 4.7       | 2'b01               | 14'b00010100000010 | 14'b00011110111111   | 14'b00010011010101 | 8'b00010000    | 8'b00101010      | 8'b01111001       | 2'b11               | 8'b01111100     |  |  |

| 3.3          | 0.434     | 94        | 10        | 2'b00               | 14'b00100110001110 | 14'b0100000000010    | 14'b00100010000011 | 8'b00010000    | 8'b10101010      | 8'b11111001       | 2'b11               | 8'b11111100     |  |  |

| 3.3          | 0.868     | 47        | 4.7       | 2'b01               | 14'b00011110100111 | 14'b00101111010110   | 14'b00011101100011 | 8'b00010000    | 8'b00101010      | 8'b01111001       | 2'b11               | 8'b01111100     |  |  |

#### Table2 Option byte for gate driver

Updated on ver1.5

| Opti            | on byte se    | tting         |

|-----------------|---------------|---------------|

| SVRAJPRDSR[3:0] | SVRAJDTP[2:0] | SVRAJDTN[2:0] |

| 4'b1111         | 3'b111        | 3'b111        |

# **Option byte settings [3/3]**

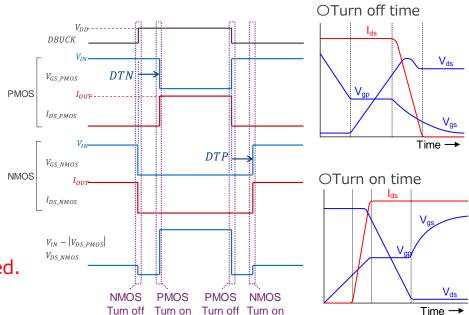

In order to avoid excessive current, the switching timing of MOSFETs should be controlled to have non-overlap time between the on-times of Hi-side(PMOS) and Lo-side(NMOS). So dead time should be set to satisfy the following relations. Dead time of Hi-side:OFF->Lo-side:ON min > PMOS Turn off time max Dead time of Lo-side:OFF->Hi-side:ON min > NMOS Turn off time max

Regarding the turn off time of MOSFETs, could you please get their information from the MOSFETs supplier you choose.

#### Note: The values in the following tables are simulation results and are not guaranteed.

|   | Pin conditions     | Output res     | istance [ohn | n]   |          |                  |      |                    |                |      |      |                  |      |              |

|---|--------------------|----------------|--------------|------|----------|------------------|------|--------------------|----------------|------|------|------------------|------|--------------|

|   | SVRAJPRDSR[3:0]    | VCC=3.0^       | ~3.3~3.6[V]  |      |          |                  |      | VCC=4.5~5.0~5.5[V] |                |      |      |                  |      | Descriptions |

| # | [3:2] for SVRNGATE | PMOS (pull-up) |              |      | NMOS (pu | NMOS (pull-down) |      |                    | PMOS (pull-up) |      |      | NMOS (pull-down) |      |              |

|   | 1:0] for SVRPGATE  | Min            | Тур          | Max  | Min      | Тур              | Max  | Min                | Тур            | Max  | Min  | Тур              | Max  |              |

| 1 | 4'b1111            | 10.4           | 15.1         | 26.3 | 9.9      | 15.0             | 26.5 | 8.4                | 11.5           | 19.2 | 8.5  | 12.5             | 21.2 |              |

| 2 | 4'b1010            | 13.5           | 19.8         | 34.9 | 12.8     | 19.5             | 35.3 | 10.8               | 15.0           | 25.3 | 10.7 | 15.8             | 27.5 | @Vds=0.2V    |

| 3 | 4'b0101            | 19.3           | 28.6         | 51.0 | 18.3     | 28.4             | 51.4 | 15.3               | 21.5           | 36.7 | 15.5 | 23.3             | 40.8 | @vds=0.2v    |

| 4 | 4'b0000            | 25.4           | 37.9         | 68.2 | 24.1     | 37.5             | 69.0 | 20.0               | 28.4           | 48.9 | 19.9 | 29.9             | 53.3 |              |

| 1 | 4'b1111            | 12.4           | 18.1         | 31.6 | 11.5     | 17.4             | 30.9 | -                  | -              | -    | -    | -                | -    |              |

| 2 | 4'b1010            | 16.3           | 23.9         | 42.0 | 15.4     | 23.5             | 42.4 | -                  | -              | -    | -    | -                | -    | @Vds=1.0V    |

| 3 | 4'b0101            | 23.5           | 34.8         | 61.6 | 21.7     | 33.4             | 60.3 | -                  | -              | -    | -    | -                | -    | @vus=1.0v    |

| 4 | 4'b0000            | 31.2           | 46.4         | 82.5 | 29.5     | 45.7             | 83.4 | -                  | -              | -    | -    | -                | -    |              |

| 1 | 4'b1111            | -              | -            | -    | -        | -                | -    | 11.8               | 16.4           | 27.3 | 11.1 | 16.3             | 28.1 |              |

| 2 | 4'b1010            | -              | -            | -    | -        | -                | -    | 15.5               | 21.6           | 36.3 | 15.1 | 22.1             | 38.8 | @Vds=2.5V    |

| 3 | 4'b0101            | -              | -            | -    | -        | -                | -    | 22.4               | 31.5           | 53.2 | 21.0 | 31.2             | 54.7 | @vus=2.5v    |

| 4 | 4'b0000            | -              | -            | -    | -        | -                | -    | 29.7               | 42.0           | 71.2 | 29.0 | 43.0             | 76.2 |              |

|   | Pin conditions<br>SVRAJDTP[2:0] | Dead time of Hi-side:OFF->Lo-side:ON_P [ns] |     |     |                    |     |     |   | Pin conditions | Dead time          | Dead time of Lo-side:OFF->Hi-side:ON [ns] |     |                    |     |     |

|---|---------------------------------|---------------------------------------------|-----|-----|--------------------|-----|-----|---|----------------|--------------------|-------------------------------------------|-----|--------------------|-----|-----|

| # |                                 | VCC=3.0~3.3~3.6[V]                          |     |     | VCC=4.5~5.0~5.5[V] |     |     | # | SVRAJDTN[2:0]  | VCC=3.0~3.3~3.6[V] |                                           |     | VCC=4.5~5.0~5.5[V] |     |     |

|   |                                 | Min                                         | Тур | Max | Min                | Тур | Max |   |                | Min                | Тур                                       | Max | Min                | Тур | Max |

| 1 | 3'b000                          | 18                                          | 26  | 39  | 17                 | 25  | 36  | 1 | 3'b000         | 18                 | 26                                        | 39  | 17                 | 25  | 36  |

| 2 | 3'b001                          | 41                                          | 53  | 71  | 41                 | 52  | 68  | 2 | 3'b001         | 41                 | 53                                        | 70  | 41                 | 52  | 68  |

| 3 | 3'b010                          | 65                                          | 80  | 103 | 64                 | 79  | 99  | 3 | 3'b010         | 65                 | 80                                        | 102 | 64                 | 79  | 99  |

| 4 | 3'b011                          | 88                                          | 107 | 135 | 88                 | 106 | 131 | 4 | 3'b011         | 88                 | 107                                       | 134 | 88                 | 106 | 131 |

| 5 | 3'b100                          | 112                                         | 134 | 166 | 111                | 133 | 163 | 5 | 3'b100         | 112                | 134                                       | 166 | 111                | 133 | 163 |

| 6 | 3'b101                          | 135                                         | 161 | 198 | 135                | 160 | 195 | 6 | 3'b101         | 135                | 161                                       | 197 | 134                | 160 | 195 |

| 7 | 3'b110                          | 159                                         | 188 | 230 | 158                | 187 | 227 | 7 | 3'b110         | 159                | 188                                       | 229 | 158                | 187 | 227 |

| 8 | 3'b111                          | 182                                         | 215 | 262 | 182                | 214 | 258 | 8 | 3'b111         | 182                | 215                                       | 261 | 181                | 214 | 258 |

Default code

RENESAS

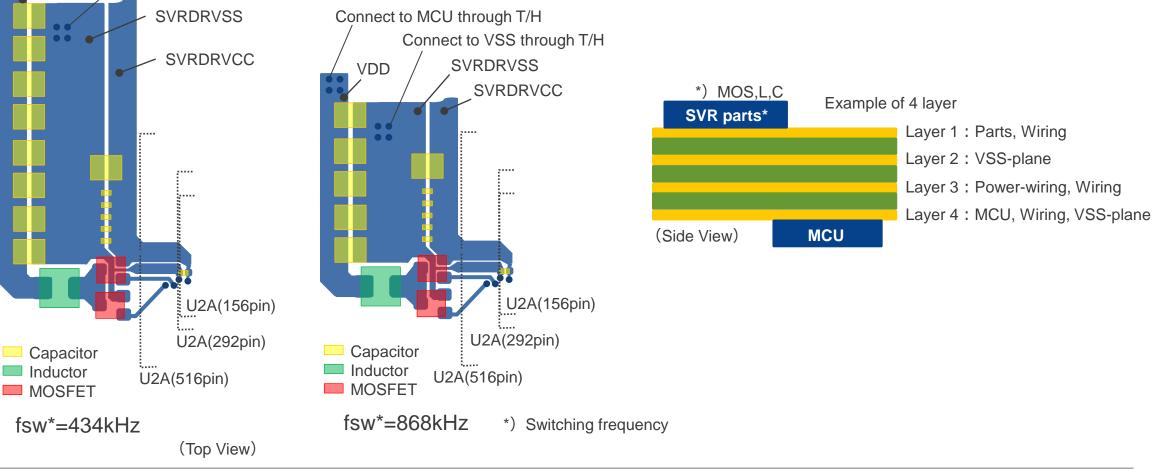

# U2A(156pin)

PCB layout guideline [1/3]

#### Updated on ver1.5

#### **Example of PCB layout**

'DD

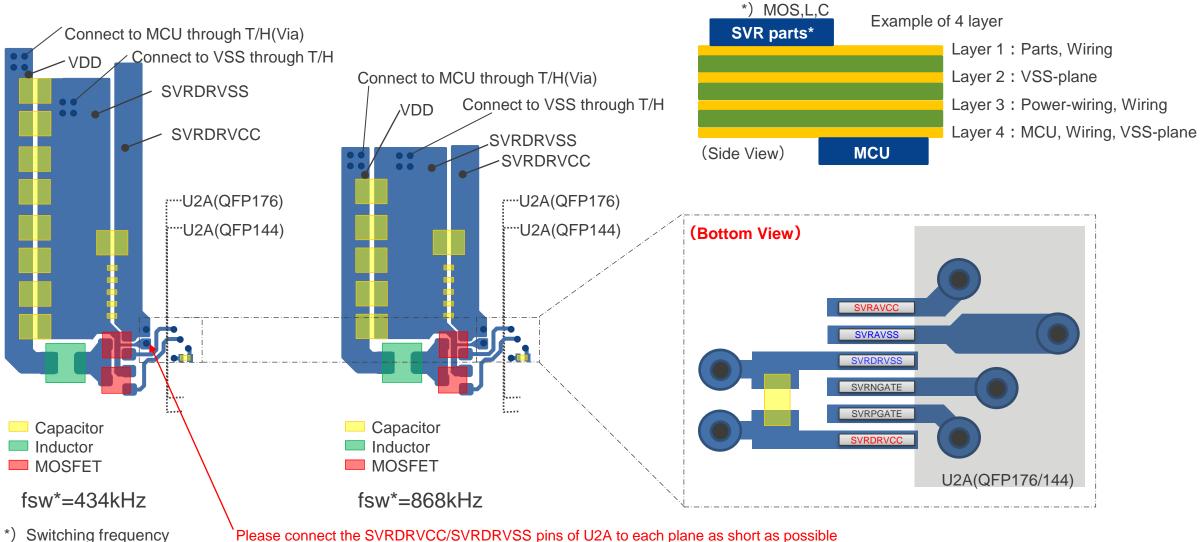

### PCB layout guideline [2/3] for QFP package

(Top View)

# PCB layout guideline [3/3]

### **Recommended PCB design rule:**

- 1) The part (C, MOS, L) of SVRDRVCC and the part (C) of VDD are arranged in the same layer (Layer 1). The distance between MOS and L, L and VDD-C should be within 3 mm each.

- 2) The VSS plane is arranged in the layer adjacent to the SVR part area (Layer 2) of Layer 1.

- 3) The MCU may be mounted on the same surface (Layer 1) as the component of the SVR.

- 4) Power supplies (including SVRAVCC) other than SVRDRVCC and VDD should be placed in the layer (Layer 3) between the VSS plane layer (Layer 2) and Layer 4.

- 5) In the case of a six-layer board, add two layers between Layer 3 (power supply wiring layer) and Layer 4. (eg Layer 3 = power supply, wiring, Layer 4 = VSS)

- 6) The pattern width of SVRDRVCC and VDD is 3 mm or more. The number of vias is 4 or more @ Φ0.6 mm (8 or more @ Φ0.3 mm).

- 7) Wiring the pattern width of SVRDRVSS at 1 mm or more. When the pattern width is less than 1 mm, it may be combined with the adjacent layer (eg Layer 1 = 0.5 mm, Layer 2 = 0.5 mm).

- 8) SVRDRVSS should be connected to VSS through via(4 or more @00.6mm) of SVRDRVSS in the vicinity of C located far from L.

- 9) C between SVRDRVCC and SVRDRVSS is located close to the MCU from the small capacity C.

- 10) C of SVRAVCC and SVRAVSS are placed closest to MCU. SVRAVCC is connected to SYSVCC and VCC. SVRAVSS is connected to VSS.

11) SVRPGATE / N wiring, MOS, L, SVRDRVCC, SVRDRVSS should not run in the same layer / adjacent layer as analogue high-sensitivity wiring.

- 1)2)4)5)11) To prevent SVR noise from diffusing to other power supplies, analog wiring, etc.

- 3) When SVR components can be arranged from the MCU without using vias, MCU and SVR components may be the same layer. On the other hand,

- if it can not be arranged, the MCU and the SVR part are separate layers only.

- 6)7)8) The pattern width and the number of vias consider the current amount.

Estimated pattern width is 1 mm / 1A. As a measure of the number of vias,  $\Phi$  0.25 mm: 0.8 A / piece,  $\Phi$  0.5 mm: 1.6 A / piece,  $\Phi$  1 mm: 3.2 A / piece. 6)8) Noise of SVR is superimposed on SVRDRVSS. In order not to diffuse noise to VSS, noise is reduced with via (1.5 nH or less) and then connected to VSS. 9)10) A ceramic capacitor having a small capacitance value has a high self-resonant frequency. That is, high frequency noise suppression effect is high.

In order to maximize this effect, a ceramic capacitor is placed close to the MCU (reduces parasitic inductance of the wiring).

### **Recommended settings of PWRGD\_CNT**

Following table shows the recommended wait time settings of PWRGD\_CNT for returning from DeepSTOP when using SVR.

|            | Configu         | urations     |              |              | Settings                  |                  |  |  |

|------------|-----------------|--------------|--------------|--------------|---------------------------|------------------|--|--|

| Product    | SVRDRVCC<br>[V] | Fsw<br>[MHz] | Cout<br>[µF] | Lout<br>[µH] | Minimum Wait Time<br>[µs] | PWRGD_CNT [11:0] |  |  |

| U2A-EVA    | 5               | 0.434        | 176          | 4.7          | 1140                      | 12D <sub>H</sub> |  |  |

|            |                 | 0.868        | 110          | 2.2          | 1430                      | 17A <sub>H</sub> |  |  |

|            | 3.3             | 0.434        | 176          | 4.7          | 1580                      | 1A2 <sub>H</sub> |  |  |

|            |                 | 0.868        | 110          | 2.2          | 1900                      | 1F6 <sub>H</sub> |  |  |

| U2A16      | 5               | 0.434        | 176          | 4.7          | 1130                      | 12B <sub>H</sub> |  |  |

|            |                 | 0.868        | 110          | 2.2          | 1130                      | 12B <sub>H</sub> |  |  |

|            | 3.3             | 0.434        | 176          | 4.7          | 1580                      | 1A2 <sub>H</sub> |  |  |

|            |                 | 0.868        | 110          | 2.2          | 1580                      | 1A2 <sub>H</sub> |  |  |

| U2A8, U2A6 | 5               | 0.434        | 94           | 10           | 1130                      | 12B <sub>H</sub> |  |  |

|            |                 | 0.868        | 47           | 4.7          | 1120                      | 128 <sub>H</sub> |  |  |

|            | 3.3             | 0.434        | 94           | 10           | 1590                      | 1A4 <sub>H</sub> |  |  |

|            |                 | 0.868        | 47           | 4.7          | 1580                      | 1A2 <sub>H</sub> |  |  |

# **Revision History [1/2]**

| Revision | Page    | Items                                                                                                                                                             | Date               |  |  |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|

| 1.0      | -       | New Release                                                                                                                                                       | February 15, 2019  |  |  |

| 1.1      | 5       | <ul> <li>Added the note.</li> <li>Added the Crss value of MOSFETs as a reference.</li> <li>Corrected the condition of Ciss from "Max" to<br/>"Typ".</li> </ul>    | June 28, 2019      |  |  |

|          | 9       | <ul><li>Updated values in tables.</li><li>Added the note.</li></ul>                                                                                               |                    |  |  |

| 1.2      | -       | <ul> <li>Corrected the pin name from "DCDC_P"<br/>to "SVRPGATE" and from "DCDC_N"<br/>to "SVRNGATE".</li> <li>Minor updated tables and block diagrams.</li> </ul> | September 17, 2019 |  |  |

|          | 9       | - Added the Option byte settings for U2A16.                                                                                                                       |                    |  |  |

| 1.3      | 3, 4, 6 | - Clarified applicable products                                                                                                                                   | December 1, 2020   |  |  |

|          | 7       | - Added the Lout and Cout settings for U2A8.                                                                                                                      |                    |  |  |

|          | 11      | - Added the Option byte settings for U2A8.                                                                                                                        |                    |  |  |

# **Revision History [2/2]**

| Revision | Page        | Items                                                               | Date          |

|----------|-------------|---------------------------------------------------------------------|---------------|

| 1.4      | 3, 4        | - Revised note for inductor                                         | June 16, 2021 |

| 1.5      | 3, 4, 7, 11 | - Clarified applicable products                                     | June 30, 2022 |

|          | 13, 14      | - Clarified applicable packages                                     |               |

| 1.6      | 16          | <ul> <li>Added the recommended settings of<br/>PWRGD_CNT</li> </ul> | May 30, 2023  |