RL78/G14

タイマRD タイマモード(PWM機能) CC-RL

R01AN2851JJ0100 Rev.1.00 2015.07.01

# 要旨

本アプリケーションノートでは、RL78/G14 のタイマ RD のタイマモード (PWM 機能 )(以下、PWM 機能) を使用して、PWM 波形を出力する方法を説明します。

# 対象デバイス

RL78/G14

本アプリケーションノートを他のマイコンへ適用する場合、そのマイコンの使用にあわせて変更し、十分評価してください。

# 目次

| 1.  | 仕様                | 3  |

|-----|-------------------|----|

|     | 動作確認条件            |    |

|     | ハードウェア説明          |    |

| 3.1 | ハードウェア構成例         |    |

| 3.2 | 使用端子一覧            |    |

| 5.2 | 区用圳」 克            |    |

| 4.  | ソフトウェア説明          | 6  |

| 4.1 | 動作概要              | 6  |

| 4.1 | 1.1 出力波形説明        | 6  |

| 4.2 | オプション・バイトの設定一覧    | 8  |

| 4.3 | 関数一覧              | 8  |

| 4.4 | 関数仕様              | 8  |

| 4.5 | フローチャート           | 10 |

| 4.5 | 5.1 全体フローチャート     | 10 |

| 4.5 | 5.2 初期設定          | 10 |

| 4.5 | 5.3   周辺機能初期設定    | 11 |

| 4.5 | 5.4   CPU初期設定     | 11 |

| 4.5 | 5.5 タイマRD初期設定     | 12 |

| 4.5 | 5.6 メイン処理         | 24 |

| 4.5 | 5.7 タイマRDカウント開始設定 | 24 |

| 4.5 | 5.8 タイマRD0割り込み    | 26 |

| 5.  | サンプルコード           | 27 |

| J.  |                   |    |

| 6   | 参老ドキュメント          | 27 |

# 1. 仕様

周期100μsのPWM波形を3本出力します。

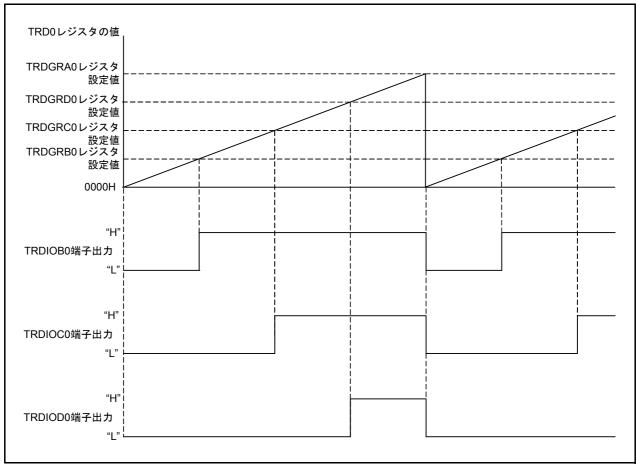

表 1.1に使用する周辺機能と用途を、図 1.1に出力タイミング図を示します。

表 1.1 使用する周辺機能と用途

| 周辺機能          | 用途      |

|---------------|---------|

| タイマRD(タイマRD0) | PWM波形出力 |

図 1.1 出力タイミング図

# 2. 動作確認条件

本アプリケーションノートのサンプルコードは、下記の条件で動作を確認しています。

# 表 2.1 動作確認条件

| 項目                             | 内容                                                      |

|--------------------------------|---------------------------------------------------------|

| 使用マイコン                         | RL78G14(R5F104LEA)                                      |

| 動作周波数                          | • 高速内蔵発振クロック (fн∞∞):16MHz(標準)                           |

|                                | • CPU/周辺ハードウエア・クロック (fclk):16MHz                        |

| 動作電圧                           | 5.0V(2.9V ~ 5.5V で動作可能)                                 |

|                                | LVD動作(V <sub>LVD</sub> ):リセット・モード 立ち上がり2.81V/立ち下がり2.75V |

| 統合開発環境 (CS+)                   | ルネサス エレクトロニクス製                                          |

|                                | CS+ V3.01.00                                            |

| Cコンパイラ (CS+)                   | ルネサス エレクトロニクス製                                          |

|                                | CC-RL V1.01.00                                          |

| 統合開発環境 (e <sup>2</sup> studio) | ルネサス エレクトロニクス製                                          |

|                                | e <sup>2</sup> studio V4.0.0.26                         |

| Cコンパイラ (e <sup>2</sup> studio) | ルネサス エレクトロニクス製                                          |

|                                | CC-RL V1.01.00                                          |

# 3. ハードウェア説明

# 3.1 ハードウェア構成例

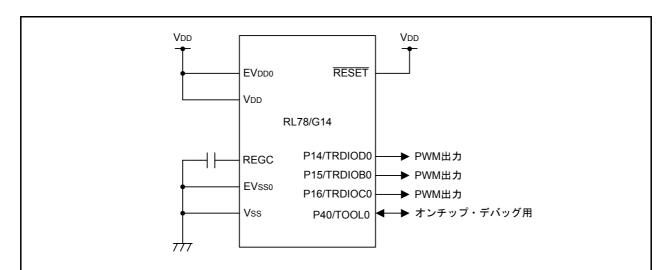

図3.1に本アプリケーションノートで使用するハードウェア構成例を示します。

- 注1. この回路イメージは接続の概要を示すために簡略化しています。実際に回路を作成される場合は、端子処理などを 適切に行い、電気的特性を満たすように設計してください。(入力専用ポートは個別に抵抗を介してVDDまたはVssに 接続してください)

- 注2. EVssで始まる名前の端子がある場合にはVssに、EVDDで始まる名前の端子がある場合にはVDDにそれぞれ接続してください。

- 注3. VDDはLVDにて設定したリセット解除電圧(VLVD)以上にしてください。

# 図 3.1 ハードウェア構成

# 3.2 使用端子一覧

表 3.1 に使用端子と機能を示します。

表 3.1 使用端子と機能

| 端子名         | 入出力 | 内容    |

|-------------|-----|-------|

| P14/TRDIOD0 | 出力  | PWM出力 |

| P15/TRDIOB0 | 出力  | PWM出力 |

| P16/TRDIOC0 | 出力  | PWM出力 |

# 4. ソフトウェア説明

## 4.1 動作概要

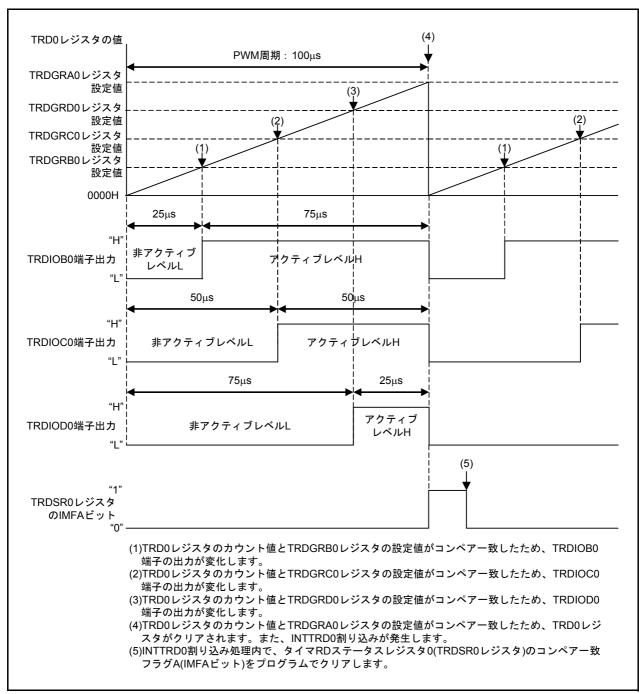

PWM機能を使用し、周期100µsのPWM波形を3本出力します。

出力する信号は、以下の通りです。

- TRDIOB0 端子出力: 非アクティブレベルL期間( $25\mu s$ )  $\rightarrow$  アクティブレベルH期間( $75\mu s$ )

- TRDIOC0 端子出力: 非アクティブレベルL期間(50 $\mu$ s)  $\rightarrow$  アクティブレベルH期間(50 $\mu$ s)

- TRDIOD0 端子出力: 非アクティブレベルL期間(75 $\mu$ s)  $\rightarrow$  アクティブレベルH期間(25 $\mu$ s)

タイマRDの設定を以下に示します。

#### <設定>

- •カウントソースに、fclk(16MHz)を使用します。

- タイマRD0を使用します。

- TRD0 レジスタは、TRDGRA0 レジスタとのコンペアー致後もカウントを継続します。

- •TRDGRC0レジスタは、ジェネラルレジスタで使用します。

- •TRDGRD0レジスタは、ジェネラルレジスタで使用します。

- TRDIOB0、TRDIOC0、TRDIOD0端子を出力許可にします。

- TRDIOB0、TRDIOC0、TRDIOD0 端子の出力レベルは アクティブレベル H、初期出力レベルは非アクティブレベルLとします。

- •TRD0レジスタとTRD1レジスタは、独立動作に設定します。

- パルス出力強制遮断入力機能は使用しません。

- •TRD0レジスタとTRDGRA0レジスタのコンペアー致割り込みを許可にします。

# 4.1.1 出力波形説明

PWM周期と、各端子から出力するPWM波形の計算式を以下に示します。

図4.1にPWMの出力波形を示します。

(1) PWM周期

PWM周期の計算式は、以下の通りです。 100μs = 1/16MHz × (TRDGRA0 + 1) = 62.5ns × 1600

(2) TRDIOB0端子のPWM出力

TRDIOB0端子の非アクティブレベルL期間の計算式は、以下の通りです。  $25\mu s = 1/16MHz \times (TRDGRB0 + 1)$  =  $62.5ns \times 400$

(3) TRDIOC0端子のPWM出力

TRDIOC0端子の非アクティブレベルL期間の計算式は、以下の通りです。 50μs = 1/16MHz × (TRDGRC0 + 1) = 62.5ns × 800

### (4) TRDIOD0端子のPWM出力

TRDIOD0端子の非アクティブレベルL期間の計算式は、以下の通りです。  $75\mu s = 1/16 MHz \times (TRDGRD0 + 1)$

= 62.5ns  $\times 1200$

図 4.1 PWMの出力波形

# 4.2 オプション・バイトの設定一覧

表 4.1 にオプション・バイト設定を示します。

# 表 4.1 オプション・バイト設定

| アドレス          | 設定値       | 内容                         |

|---------------|-----------|----------------------------|

| 000C0H/010C0H | 11101111B | ウォッチドッグ・タイマ動作停止            |

|               |           | (リセット解除後、カウント停止)           |

| 000C1H/010C1H | 01111111B | LVD リセット・モード               |

|               |           | 検出電圧:立ち上がり2.81V/立ち下がり2.75V |

| 000C2H/010C2H | 11101001B | 高速内蔵発振 HSモード 16MHz         |

| 000C3H/010C3H | 10000100B | オンチップ・デバッグ許可               |

# 4.3 関数一覧

表 4.2 に関数を示します。

#### 表 4.2 関数

| 関数名                 | 概要            |

|---------------------|---------------|

| hdwinit             | 初期設定          |

| R_Systeminit        | 周辺機能初期設定      |

| R_CGC_Create        | CPU初期設定       |

| R_TMR_RD0_Create    | タイマRD初期設定     |

| main                | メイン処理         |

| timer_rd0_start     | タイマRDカウント開始設定 |

| r_tmr_rd0_interrupt | タイマRD0割り込み    |

# 4.4 関数仕様

サンプルコードの関数仕様を示します。

### hdwinit

概 要初期設定ヘッダなし

宣言 void hdwinit(void)

説 明 周辺機能の初期設定を行います。

引数 なし リターン値 なし

# R\_Systeminit

概 要 周辺機能初期設定

ヘッダ なし

宣言 void R\_Systeminit(void)

説明本アプリケーションノートで使用する周辺機能の初期設定を行います。

引数 なし リターン値 なし

# R\_CGC\_Create

概 要 CPU初期設定

ヘッダ なし

宣言 void R\_CGC\_Create(void)

説 明 CPU初期設定を行います。

引数 なし

リターン値 なし

### R TMR RD0 Create

概 要 タイマRD初期設定

ヘッダ なし

宣言 void R\_TMR\_RD0\_Create(void)

説 明 タイマRDのPWM機能を使用するための初期設定を行います。

引数 なし

リターン値 なし

#### main

概 要 メイン処理

ヘッダ なし

宣言 void main(void)

説 明 メイン処理を行います。

引数 なし

リターン値 なし

### timer\_rd0\_start

概 要 タイマRDカウント開始設定

ヘッダ なし

宣言 void timer\_rd0\_start(void)

説 明 タイマRDカウント開始設定を行います。

引数 なし

リターン値 なし

# r\_tmr\_rd0\_interrupt

概要 タイマRD0割り込み

ヘッダ なし

宣言 static void \_\_near r\_tmr\_rd0\_interrupt(void)

説 明 ●タイマRD0割り込み処理を行います。

●コンペアー致フラグAをクリアします。

引数 なし

リターン値 なし

# 4.5 フローチャート

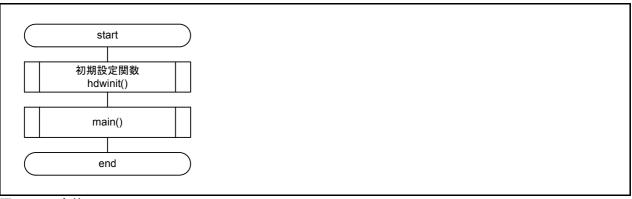

# 4.5.1 全体フローチャート

図 4.2に全体フローチャートを示します。

図 4.2 全体フローチャート

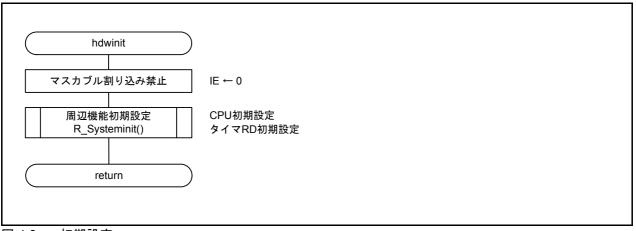

# 4.5.2 初期設定

図 4.3 に初期設定のフローチャートを示します。

図 4.3 初期設定

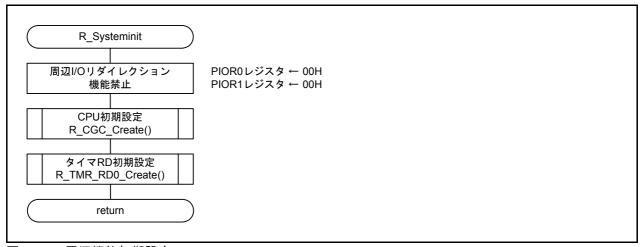

#### 4.5.3 周辺機能初期設定

図 4.4 に周辺機能初期設定のフローチャートを示します。

図 4.4 周辺機能初期設定

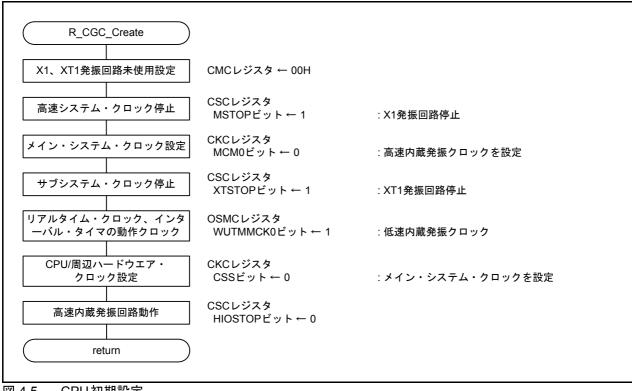

#### CPU初期設定 4.5.4

図 4.5にCPU 初期設定のフローチャートを示します。

CPU初期設定 図 4.5

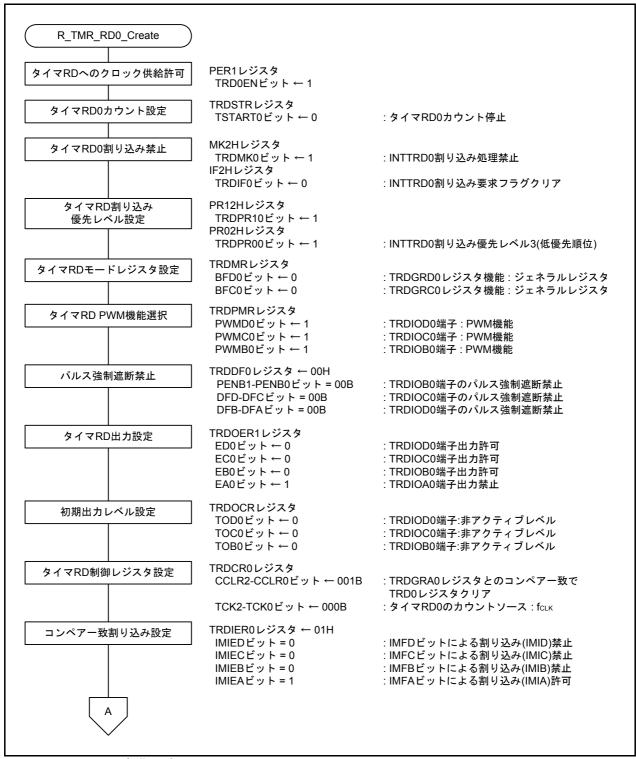

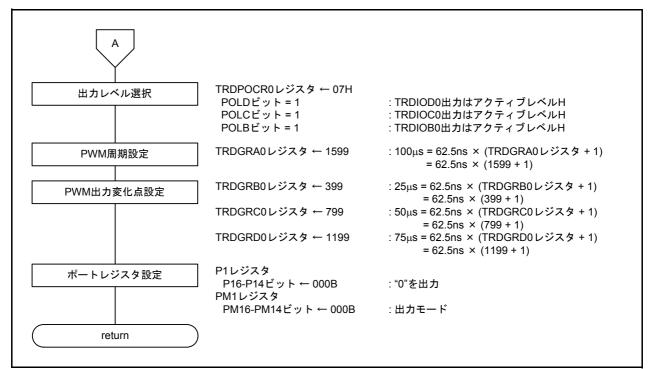

# 4.5.5 タイマRD初期設定

図4.6、図4.7にタイマRD初期設定のフローチャートを示します。

図 4.6 タイマRD初期設定(1/2)

図 4.7 タイマRD初期設定(2/2)

# タイマRDへのクロック供給許可

•周辺イネーブル・レジスタ1(PER1) タイマRDへのクロック供給を許可にします。

略号 PER1 設定値

| 7     | 6     | 5     | 4      | 3     | 2 | 1 | 0      |

|-------|-------|-------|--------|-------|---|---|--------|

| DACEN | TRGEN | CMPEN | TRD0EN | DTCEN | 0 | 0 | TRJ0EN |

| ×     | ×     | ×     | 1      | ×     | _ | _ | ×      |

#### ビット4

| TRD0EN | タイマ RD の入力クロック供給の制御          |  |  |  |

|--------|------------------------------|--|--|--|

| 0      | 入力クロック供給停止                   |  |  |  |

|        | タイマ RD で使用する SFR へのライト不可     |  |  |  |

|        | ・タイマ RD はリセット状態              |  |  |  |

| 1      | 入力クロック供給                     |  |  |  |

|        | ・タイマ RD で使用する SFR へのリード/ライト可 |  |  |  |

## タイマRD0カウント設定

• タイマRDモードレジスタ(TRDSTR) タイマRD0のカウントを停止します。

| 略号     | 7 |  |

|--------|---|--|

| TRDSTR | _ |  |

| 設定値    | _ |  |

| 7 | 6 | 5 | 4 | 3     | 2     | 1       | 0       |

|---|---|---|---|-------|-------|---------|---------|

| _ | _ | _ | _ | CSEL1 | CSEL0 | TSTART1 | TSTART0 |

| _ | _ | _ | _ | ×     |       | ×       | 0       |

# ビット2

| CSEL0 | TRD0 カウント動作選択                |

|-------|------------------------------|

| 0     | TRDGRA0 レジスタとのコンペア一致でカウント停止  |

| 1     | TRDGRA0 レジスタとのコンペアー致後もカウント継続 |

# ビット0

| Ī | TSTART0 | TRD0 カウント開始フラグ |

|---|---------|----------------|

|   | 0       | カウント停止         |

| Ī | 1       | カウント開始         |

レジスタ設定の詳細については、RL78/G14ユーザーズマニュアルハードウェア編を参照してください。 レジスタ図の設定値

# タイマRD0割り込み禁止

•割り込みマスク・フラグ・レジスタ(MK2H) INTTRD0割り込みを禁止に設定します。

| 略号   | 7    | 6       | 5 | 4       | 3     | 2      | 1      | 0      |

|------|------|---------|---|---------|-------|--------|--------|--------|

| MK2H | FLMK | IICAMK1 | 1 | SREMK3  | TRGMK | TRDMK1 | TRDMK0 | PMK11  |

|      |      |         |   | TMMK13H |       |        |        | CMPMK1 |

| 設定値  | ×    | ×       | _ | ×       | ×     | ×      | 1      | ×      |

#### ビット1

|   | TRDMK0 | 割り込み処理の制御 |

|---|--------|-----------|

| Ī | 0      | 割り込み処理許可  |

|   | 1      | 割り込み処理禁止  |

割り込み要求フラグ・レジスタ(IF2H) INTTRD0割り込み要求フラグをクリアします。

| 略 <del>号</del> | 7    | 6       | 5 | 4       | 3     | 2      | 1      | 0      |

|----------------|------|---------|---|---------|-------|--------|--------|--------|

| IF2H           | FLIF | IICAIF1 | 0 | SREIF3  | TRGIF | TRDIF1 | TRDIF0 | PIF11  |

|                |      |         |   | TMIF13H |       |        |        | CMPIF1 |

| 設定値            | ×    | ×       | _ | ×       | ×     | ×      | 0      | ×      |

### ビット1

|                                               | TRDIF0 | 割り込み要求フラグ             |

|-----------------------------------------------|--------|-----------------------|

| 0 割り込み要求信号が発生していない<br>1 割り込み要求信号が発生し、割り込み要求状態 |        | 割り込み要求信号が発生していない      |

|                                               |        | 割り込み要求信号が発生し、割り込み要求状態 |

レジスタ設定の詳細については、RL78/G14ユーザーズマニュアルハードウェア編を参照してください。 レジスタ図の設定値

設定値

# タイマRD割り込み優先レベル設定

優先順位指定フラグ・レジスタ(PR02H、PR12H) レベル3(低優先順位)に設定します。

| 略号    | 7     | 6        | 5 | 4        | 3      | 2       | 1       | 0       |

|-------|-------|----------|---|----------|--------|---------|---------|---------|

| PR02H | FLPR0 | IICAPR01 | 1 | SREPR03  | TRGPR0 | TRDPR01 | TRDPR00 | PPR011  |

|       |       |          |   | TMPR013H |        |         |         | CMPPR01 |

| 設定値   | ×     | ×        | ı | ×        | ×      | ×       | 1       | ×       |

|       |       |          |   |          |        |         |         |         |

| 略号    | 7     | 6        | 5 | 4        | 3      | 2       | 1       | 0       |

| PR12H | FLPR1 | IICAPR11 | 1 | SREPR13  | TRGPR1 | TRDPR11 | TRDPR10 | PPR111  |

|       |       |          |   | TMPR113H |        |         |         | CMPPR11 |

| TRDPR10 | TRDPR00 | 優先順位レベルの選択       |

|---------|---------|------------------|

| 0       | 0       | レベル 0 を指定(高優先順位) |

| 0       | 1       | レベル 1 を指定        |

| 1       | 0       | レベル 2 を指定        |

| 1       | 1       | レベル3を指定(低優先順位)   |

### タイマRDモードレジスタ設定

タイマRDモードレジスタ(TRDMR)TRDGRC0、TRDGRD0レジスタをジェネラルレジスタとして使用します。

| 略号    | 7    | 6    | 5    | 4    | 3 | 2 | 1 | 0    |

|-------|------|------|------|------|---|---|---|------|

| TRDMR | BFD1 | BFC1 | BFD0 | BFC0 | 1 | 1 | 1 | SYNC |

| 設定値   | ×    | ×    | 0    | 0    | ı | ı | ı |      |

## ビット5

|             | BFD0 | TRDGRD0 レジスタ機能選択      |

|-------------|------|-----------------------|

| 0 ジェネラルレジスタ |      | ジェネラルレジスタ             |

|             | 1    | TRDGRB0 レジスタのバッファレジスタ |

# ビット4

| BFC0 | TRDGRC0 レジスタ機能選択      |

|------|-----------------------|

| 0    | ジェネラルレジスタ             |

| 1    | TRDGRA0 レジスタのバッファレジスタ |

# ビット0

| Ī | SYNC | タイマ RD 同期         |

|---|------|-------------------|

|   | 0    | TRD0 と TRD1 は独立動作 |

|   | 1    | TRD0 と TRD1 は同期動作 |

レジスタ設定の詳細については、RL78/G14ユーザーズマニュアルハードウェア編を参照してください。 レジスタ図の設定値

### タイマRD PWM機能選択

タイマRD PWM機能選択レジスタ(TRDPMR)TRDIOB0、TRDIOC0、TRDIOD0端子にPWM機能を設定します。

6 2 0 略号 7 5 3 1 PWMD1 PWMC1 PWMB1 PWMD0 PWMC0 PWMB0 **TRDPMR** 設定値

#### ビット2

| PWMD0 | TRDIOD0 PWM 機能選択            |

|-------|-----------------------------|

| 0     | インプットキャプチャ機能またはアウトプットコンペア機能 |

| 1     | PWM 機能                      |

#### ビット1

| PWMC0 | TRDIOC0 PWM 機能選択            |

|-------|-----------------------------|

| 0     | インプットキャプチャ機能またはアウトプットコンペア機能 |

| 1     | PWM 機能                      |

### ビット0

| PWMB0 | TRDIOB0 PWM 機能選択            |

|-------|-----------------------------|

| 0     | インプットキャプチャ機能またはアウトプットコンペア機能 |

| 1     | PWM 機能                      |

### パルス強制遮断禁止

タイマRDデジタルフィルタ機能選択レジスタの(TRDDF0)TRDIOB0、TRDIOC0、TRDIOD0端子のパルス強制遮断を禁止します。

略号 TRDDF0 設定値

|   | 7     | 6     | 5     | 4     | 3   | 2   | 1   | 0   |

|---|-------|-------|-------|-------|-----|-----|-----|-----|

| ) | DFCK1 | DFCK0 | PENB1 | PENB0 | DFD | DFC | DFB | DFA |

|   | ×     | ×     | 0     | 0     | 0   | 0   | 0   | 0   |

#### ビット5-4

| PENB1 | PENB0 | TRDIOB0 端子パルス強制遮断制御 |

|-------|-------|---------------------|

| 0     | 0     | 強制遮断禁止              |

| 0     | 1     | ハイインピーダンス出力         |

| 1     | 0     | L出力                 |

| 1     | 1     | H出力                 |

これらのモードで対応する端子をタイマ RD の出力ポートとして使用しない場合、強制遮断禁止の 00B に設定してください。また、カウント停止中に設定してください。

レジスタ設定の詳細については、RL78/G14ユーザーズマニュアルハードウェア編を参照してください。 レジスタ図の設定値

#### ビット3-2

| 0     0     強制遮断禁止       0     1     ハイインピーダンス出力 | DFD        | DFC | TRDIOC0 端子パルス強制遮断制御 |  |  |  |

|--------------------------------------------------|------------|-----|---------------------|--|--|--|

| 0 1 ハイインピーダンス出力                                  | 0 0 強制遮断禁止 |     |                     |  |  |  |

|                                                  | 0          | 1   | ハイインピーダンス出力         |  |  |  |

| 1 0 L出力                                          | 1          | 0   | L出力                 |  |  |  |

| 1 1 日出力                                          | 1          | 1   | H出力                 |  |  |  |

これらのモードで対応する端子をタイマ RD の出力ポートとして使用しない場合,強制遮断禁止の 00B に設定してください。また、カウント停止中に設定してください。

### ビット1-0

| DFB | DFA | TRDIOD0 端子パルス強制遮断制御 |

|-----|-----|---------------------|

| 0   | 0   | 強制遮断禁止              |

| 0   | 1   | ハイインピーダンス出力         |

| 1   | 0   | L出力                 |

| 1   | 1   | H出力                 |

これらのモードで対応する端子をタイマ RD の出力ポートとして使用しない場合、強制遮断禁止の 00B に設定してください。また、カウント停止中に設定してください。

### タイマRD出力設定

・タイマRD出力マスタ許可レジスタ1(TRDOER1)

TRDIOA0端子の出力を禁止、TRDIOB0、TRDIOC0、TRDIOD0端子の出力を許可に設定します。

| 略号      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| TRDOER1 | ED1 | EC1 | EB1 | EA1 | ED0 | EC0 | EB0 | EA0 |

| 設定値     | ×   | ×   | ×   | ×   | 0   | 0   | 0   | 1   |

# ビット3

| ED0 | TRDIOD0 出力禁止              |

|-----|---------------------------|

| 0   | 出力許可                      |

| 1   | 出力禁止(TRDIOD0 端子は I/O ポート) |

# ビット2

| EC0 | TRDIOC0 出力禁止              |

|-----|---------------------------|

| 0   | 出力許可                      |

| 1   | 出力禁止(TRDIOC0 端子は I/O ポート) |

#### ビット1

| EB0 | TRDIOB0 出力禁止              |

|-----|---------------------------|

| 0   | 出力許可                      |

| 1   | 出力禁止(TRDIOB0 端子は I/O ポート) |

レジスタ設定の詳細については、RL78/G14ユーザーズマニュアルハードウェア編を参照してください。 レジスタ図の設定値

#### ビット0

| EA0 | TRDIOA0 出力禁止              |

|-----|---------------------------|

| 0   | 出力許可                      |

| 1   | 出力禁止(TRDIOA0 端子は I/O ポート) |

PWM機能では、1にしてください。

# 初期出力レベル設定

・タイマRD出力制御レジスタ(TRDOCR)

TRDIOB0、TRDIOC0、TRDIOD0端子の初期出力レベルを設定します。

| 略号     |  |

|--------|--|

| TRDOCR |  |

| 設定値    |  |

|   | /    | б    | 5    | 4    | 3    | 2    | 1    | Ü    |

|---|------|------|------|------|------|------|------|------|

| ₹ | TOD1 | TOC1 | TOB1 | TOA1 | TOD0 | TOC0 | TOB0 | TOA0 |

|   | ×    | ×    | ×    | ×    | 0    | 0    | 0    | ×    |

#### ビット3

| TOD0 | TRDIOD0 初期出力レベル選択 |

|------|-------------------|

| 0    | 初期出力は非アクティブレベル    |

| 1    | 初期出力はアクティブレベル     |

#### ビット2

| TOC0 | TRDIOC0 初期出力レベル選択 |

|------|-------------------|

| 0    | 初期出力は非アクティブレベル    |

| 1    | 初期出力はアクティブレベル     |

### ビット1

| Ī | TOB0 | TRDIOB0 初期出力レベル選択 |

|---|------|-------------------|

|   | 0    | 初期出力は非アクティブレベル    |

| I | 1    | 初期出力アクティブレベル      |

#### タイマRD制御レジスタ設定

• タイマRD制御レジスタ0(TRDCR0)

TRD0 レジスタクリアタイミングに TRDGRA0 レジスタとのコンペア一致を設定します。タイマ RD0のカウントソースに  $f_{CLK}$ を設定します。

| 略号     |

|--------|

| TRDCR0 |

| 設定値    |

|   | /     | 6     | 5     | 4     | 3     | 2    | 1    | 0    |

|---|-------|-------|-------|-------|-------|------|------|------|

| ) | CCLR2 | CCLR1 | CCLR0 | CKEG1 | CKEG0 | TCK2 | TCK1 | TCK0 |

|   | 0     | 0     | 1     | ×     | ×     | 0    | 0    | 0    |

### ビット7-5

| CCLR2                                             | CCLR1 | CCLR0 | TRD0 カウンタクリア選択 |

|---------------------------------------------------|-------|-------|----------------|

| 001B (TRDGRA0 レジスタとのコンペアー致で TRD0 レジスタクリア)にしてください。 |       |       |                |

レジスタ設定の詳細については、RL78/G14ユーザーズマニュアルハードウェア編を参照してください。 レジスタ図の設定値

#### ビット2-0

| TCK2 | TCK1 | TCK0 | カウントソース選択   |

|------|------|------|-------------|

| 0    | 0    | 0    | fclk, fhoco |

| 0    | 0    | 1    | fcLk/2      |

| 0    | 1    | 0    | fclk/4      |

| 0    | 1    | 1    | fcLk/8      |

| 1    | 0    | 0    | fclk/32     |

| 1    | 0    | 1    | TRDCLK 入力   |

| 1    | 1    | 0    | 設定しないでください  |

| 1    | 1    | 1    | 設定しないでください  |

# コンペアー致割り込み設定

タイマRD割り込み許可レジスタの(TRDIER0)IMFA ビットによる割り込み(IMIA)許可に設定します。

| 哈亏      |

|---------|

| TRDIER0 |

| 設定値     |

|    | 7 | 6 | 5 | 4    | 3     | 2     | 1     | 0     |

|----|---|---|---|------|-------|-------|-------|-------|

| R0 | 1 | 1 | 1 | OVIE | IMIED | IMIEC | IMIEB | IMIEA |

| į  | _ | _ | _ | ×    | 0     | 0     | 0     | 1     |

### ビット3

| IM | IED | インプットキャプチャ / コンペアー致割り込み許可 D |

|----|-----|-----------------------------|

|    | 0   | IMFD ビットによる割り込み(IMID)禁止     |

|    | 1   | IMFD ビットによる割り込み(IMID)許可     |

# ビット2

| IMIEC | インプットキャプチャ/コンペアー致割り込み許可 C |

|-------|---------------------------|

| 0     | IMFC ビットによる割り込み (IMIC) 禁止 |

| 1     | IMFC ビットによる割り込み (IMIC) 許可 |

#### ビット1

| IMIEB | インプットキャプチャ/コンペアー致割り込み許可 B |

|-------|---------------------------|

| 0     | IMFB ビットによる割り込み(IMIB)禁止   |

| 1     | IMFB ビットによる割り込み(IMIB)許可   |

### ビット0

|   | IMIEA | インプットキャプチャ / コンペアー致割り込み許可 A |

|---|-------|-----------------------------|

|   | 0     | IMFA ビットによる割り込み(IMIA)禁止     |

| I | 1     | IMFA ビットによる割り込み(IMIA)許可     |

レジスタ設定の詳細については、RL78/G14ユーザーズマニュアルハードウェア編を参照してください。 レジスタ図の設定値

### 出力レベル選択

タイマRD PWM機能出力レベル制御レジスタ 0(TRDPOCR0)TRDIOC0、TRDIOB0、TRDIOD0端子の出力レベルは、アクティブレベルHに設定します。

| 略号     | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|--------|---|---|---|---|---|------|------|------|

| TRDPOC | _ | - | _ | _ | - | POLD | POLC | POLB |

| R0     |   |   |   |   |   |      |      |      |

| 設定値    | _ | - | _ | _ | - | 1    | 1    | 1    |

### ビット2

| POLD | PWM 機能出力レベル制御 D           |

|------|---------------------------|

| 0    | TRDIOD0 の出力レベルはアクティブレベル L |

| 1    | TRDIOD0 の出力レベルはアクティブレベル H |

#### ビット1

|   | POLC | PWM 機能出力レベル制御 C           |

|---|------|---------------------------|

| ĺ | 0    | TRDIOC0 の出力レベルはアクティブレベル L |

| ĺ | 1    | TRDIOC0 の出力レベルはアクティブレベル H |

#### ビット0

|   | POLB | PWM 機能出力レベル制御 B           |

|---|------|---------------------------|

|   | 0    | TRDIOB0 の出力レベルはアクティブレベル L |

| Ī | 1    | TRDIOB0 の出力レベルはアクティブレベル H |

# PWM周期設定

タイマRDジェネラルレジスタA0(TRDGRA0) PWM周期を100µsに設定します。

| 略号      | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| TRDGRA0 | _  | -  | -  | -  | -  | -  | _ | - | - | _ | - | 1 | - | - | - | _ |

| 設定値     | 0  | 0  | 0  | 0  | 0  | 1  | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| _      | 機能                                 | 設定範囲          |

|--------|------------------------------------|---------------|

| ビット    | 表 4.3 の PWM 機能時の TRDGRA0 レジスタの機能参照 | 0000H ∼ FFFFH |

| 15 ~ 0 |                                    |               |

レジスタ設定の詳細については、RL78/G14ユーザーズマニュアルハードウェア編を参照してください。 レジスタ図の設定値

### PWM出力変化点設定

・タイマRDジェネラルレジスタB0(TRDGRB0) カウント開始から $25\mu$ s後にTRDIOB0端子の出力が変化するように設定します。

| 略号      | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| TRDGRB0 | -  | 1  | -  | -  | -  | -  | - | - | _ | - | - | ı | - | - | 1 | _ |

| 設定値     | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| _      | 機能                                | 設定範囲          |

|--------|-----------------------------------|---------------|

| ビット    | 表 4.3 の PWM 機能時の TRDGRB0 レジスタ機能参照 | 0000H ~ FFFFH |

| 15 ~ 0 |                                   |               |

• タイマRD ジェネラルレジスタ C0(TRDGRC0) カウント開始から 50μs後にTRDIOC0端子の出力が変化するように設定します。

| 略号      | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| TRDGRC0 | -  | -  | _  | _  | -  | -  | - | - | - | - | - | _ | - | - | - | _ |

| 設定値     | 0  | 0  | 0  | 0  | 0  | 0  | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| _      | 機能                                | 設定範囲          |

|--------|-----------------------------------|---------------|

| ビット    | 表 4.3 の PWM 機能時の TRDGRC0 レジスタ機能参照 | 0000H ~ FFFFH |

| 15 ~ 0 |                                   |               |

• タイマRD ジェネラルレジスタ D0(TRDGRD0) カウント開始から 75μs後にTRDIOD0 端子の出力が変化するように設定します。

| 略号      | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| TRDGRD0 | 1  | -  | -  | -  | -  | -  | - | ı | - | - | - | ı | - | - | - | _ |

| 設定値     | 0  | 0  | 0  | 0  | 0  | 1  | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 |

| _      | 機能                                | 設定範囲          |

|--------|-----------------------------------|---------------|

| ビット    | 表 4.3 の PWM 機能時の TRDGRD0 レジスタ機能参照 | 0000H ~ FFFFH |

| 15 ~ 0 |                                   |               |

## 表 4.3 PWM機能時のジェネラルレジスタの機能

| レジスタ    | 設定       | レジスタの機能                           | PWM 出力端子 |

|---------|----------|-----------------------------------|----------|

| TRDGRA0 | _        | ジェネラルレジスタ。PWM 周期を設定してください。        |          |

| TRDGRB0 | _        | ジェネラルレジスタ。PWM 出力の変化点を設定してください。    | TRDIOB0  |

| TRDGRC0 | BFC0 = 0 | ジェネラルレジスタ。PWM 出力の変化点を設定してください。    | TRDIOC0  |

| TRDGRD0 | BFD0 = 0 |                                   | TRDIOD0  |

| TRDGRC0 | BFC0 = 1 | バッファレジスタ。次回の PWM 周期を設定してください。     | _        |

| TRDGRD0 | BFD0 = 1 | バッファレジスタ。次回の PWM 出力の変化点を設定してください。 | TRDIOB0  |

レジスタ設定の詳細については、RL78/G14ユーザーズマニュアルハードウェア編を参照してください。 レジスタ図の設定値

# ポートレジスタ設定

・ポート・レジスタ1(P1) ポート・レジスタ1を設定します。

略号 P1 設定値

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P17 | P16 | P15 | P14 | P13 | P12 | P11 | P10 |

| ×   | 0   | 0   | 0   | ×   | ×   | ×   | ×   |

### ビット6

| P16 | 出力データの制御 |

|-----|----------|

| 0   | 0 を出力    |

| 1   | 1 を出力    |

#### ビット5

| P15 | 出力データの制御 |

|-----|----------|

| 0   | 0 を出力    |

| 1   | 1 を出力    |

#### ビット4

| P14 | 出力データの制御 |

|-----|----------|

| 0   | 0 を出力    |

| 1   | 1 を出力    |

ポート・モード・レジスタ1(PM1)P16~P14端子を出力モードに設定します。

略号 PM1 設定値

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| PM17 | PM16 | PM15 | PM14 | PM13 | PM12 | PM11 | PM10 |

| ×    | 0    | 0    | 0    | ×    | ×    | ×    | ×    |

### ビット6

| PM16 | P16 端子の入出力モードの選択  |

|------|-------------------|

| 0    | 出力モード(出力バッファ・オン)  |

| 1    | 入力モード (出力バッファ・オフ) |

## ビット5

|   | PM15 | P15 端子の入出カモードの選択 |

|---|------|------------------|

|   | 0    | 出力モード(出力バッファ・オン) |

| ĺ | 1    | 入力モード(出力バッファ・オフ) |

#### ビット4

|   | PM14 | P14 端子の入出力モードの選択 |

|---|------|------------------|

|   | 0    | 出力モード(出力バッファ・オン) |

| ĺ | 1    | 入力モード(出力バッファ・オフ) |

レジスタ設定の詳細については、RL78/G14ユーザーズマニュアルハードウェア編を参照してください。 レジスタ図の設定値

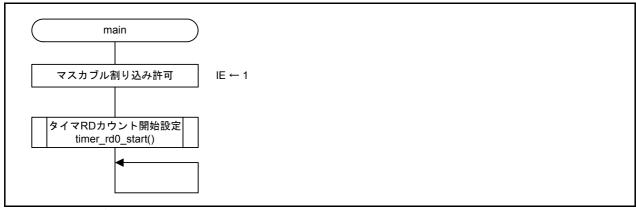

# 4.5.6 メイン処理

図 4.8にメイン処理のフローチャートを示します。

図 4.8 メイン処理

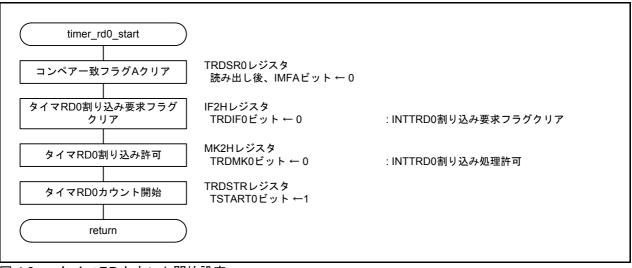

# 4.5.7 タイマRDカウント開始設定

図 4.9 にタイマRDカウント開始設定のフローチャートを示します。

図 4.9 タイマRDカウント開始設定

## コンペアー致フラグAクリア

• タイマRDステータスレジスタ 0(TRDSR0) タイマRDステータスレジスタ 0を読んだ後、コンペア一致フラグ A をクリアします。

略号 TRDSR0 設定値

| 7 | 6 | 5 | 4   | 3    | 2    | 1    | 0    |

|---|---|---|-----|------|------|------|------|

| 1 | 1 | 1 | OVF | IMFD | IMFC | IMFB | IMFA |

| _ | _ | _ | ×   | ×    | ×    | ×    | 0    |

#### ビット0

| IMFA     | インプットキャプチャ / コンペア一致フラグ A |

|----------|--------------------------|

| [0 になる   | 要因]                      |

| 読んだ後,    | 0 を書く                    |

| [1 になる   | 要因]                      |

| TRD0 と 1 | 「RDGRA0 の値が一致したとき        |

## タイマRD0割り込み要求フラグクリア

割り込み要求フラグ・レジスタ(IF2H) INTTRD0割り込み要求フラグをクリアします。

| 略号   | 7    | 6       | 5 | 4       | 3     | 2      | 1      | 0      |

|------|------|---------|---|---------|-------|--------|--------|--------|

| IF2H | FLIF | IICAIF1 | 0 | SREIF3  | TRGIF | TRDIF1 | TRDIF0 | PIF11  |

|      |      |         |   | TMIF13H |       |        |        | CMPIF1 |

| 設定値  | ×    | ×       | 1 | ×       | ×     | ×      | 0      | ×      |

#### ビット1

| TRDIF0 | 割り込み要求フラグ             |  |

|--------|-----------------------|--|

| 0      | 割り込み要求信号が発生していない      |  |

| 1      | 割り込み要求信号が発生し、割り込み要求状態 |  |

# タイマRD0割り込み許可

•割り込みマスク・フラグ・レジスタ(MK2H) INTTRD0割り込みを許可に設定します。

| 略号   | 7    | 6       | 5 | 4       | 3     | 2      | 1      | 0      |

|------|------|---------|---|---------|-------|--------|--------|--------|

| MK2H | FLMK | IICAMK1 | 1 | SREMK3  | TRGMK | TRDMK1 | TRDMK0 | PMK11  |

|      |      |         |   | TMMK13H |       |        |        | CMPMK1 |

| 設定値  | ×    | ×       | ı | ×       | ×     | ×      | 0      | ×      |

### ビット1

| TRDMK0 | 割り込み処理の制御 |

|--------|-----------|

| 0      | 割り込み処理許可  |

| 1      | 割り込み処理禁止  |

レジスタ設定の詳細については、RL78/G14ユーザーズマニュアルハードウェア編を参照してください。 レジスタ図の設定値

# タイマRD0カウント開始

・タイマRDモードレジスタ(TRDSTR) タイマRD0のカウントを開始します。

| 略号     | 7 | 6 | 5 | 4 | 3     | 2     | 1       | 0       |

|--------|---|---|---|---|-------|-------|---------|---------|

| TRDSTR | _ | 1 | 1 | _ | CSEL1 | CSEL0 | TSTART1 | TSTART0 |

| 設定値    | _ | 1 | ı | - | ×     |       | ×       | 1       |

| . *                   |     |    | _ |

|-----------------------|-----|----|---|

| $\boldsymbol{\vdash}$ | **1 |    | 0 |

| _                     | _   | Ι. | v |

| TST | ART0 | TRD0 カウント開始フラグ |

|-----|------|----------------|

|     | 0    | カウント停止         |

|     | 1    | カウント開始         |

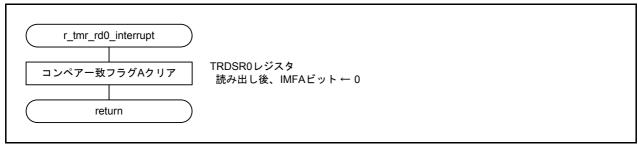

# 4.5.8 タイマRDO割り込み

図 4.10 にタイマ RD0 割り込みのフローチャートを示します。

図 4.10 タイマRD0割り込み

レジスタ設定の詳細については、RL78/G14ユーザーズマニュアルハードウェア編を参照してください。 レジスタ図の設定値

# 5. サンプルコード

サンプルコードは、ルネサスエレクトロニクスホームページから入手してください。

# 6. 参考ドキュメント

RL78/G14 ユーザーズマニュアル ハードウェア編 (R01UH0186J) RL78ファミリ ユーザーズマニュアル ソフトウェア編 (R01US0015J) (最新版をルネサス エレクトロニクスホームページから入手してください。)

テクニカルアップデート (最新の情報をルネサスエレクトロニクスホームページから入手してください。)

# ホームページとサポート窓口

ルネサス エレクトロニクスホームページ http://japan.renesas.com/

お問合せ先

http://japan.renesas.com/contact

| <b>フレニナニ</b> フ ヘヨ | RL78/G14                  |  |  |  |

|-------------------|---------------------------|--|--|--|

| 改訂記録              | タイマRD タイマモード(PWM機能) CC-RL |  |  |  |

| Rev.  | 発行日        |     | 改訂内容 |  |  |

|-------|------------|-----|------|--|--|

| IXEV. |            | ページ | ポイント |  |  |

| 1.00  | 2015.07.01 | -   | 初版発行 |  |  |

すべての商標および登録商標は、それぞれの所有者に帰属します。

# 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意 事項については、本ドキュメントおよびテクニカルアップデートを参照してください。

### 1. 未使用端子の処理

【注意】未使用端子は、本文の「未使用端子の処理」に従って処理してください。

CMOS 製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI 周辺のノイズが印加され、LSI 内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。未使用端子は、本文「未使用端子の処理」で説明する指示に従い処理してください。

2. 電源投入時の処置

【注意】電源投入時は、製品の状態は不定です。

電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。

外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の状態は保証できません。

同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットの かかる一定電圧に達するまでの期間、端子の状態は保証できません。

3. リザーブアドレス(予約領域)のアクセス禁止

【注意】リザーブアドレス(予約領域)のアクセスを禁止します。

アドレス領域には、将来の機能拡張用に割り付けられているリザーブアドレス(予約領域)があります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

4. クロックについて

【注意】リセット時は、クロックが安定した後、リセットを解除してください。

プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。

リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、 クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子 (または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定し てから切り替えてください。

5. 製品間の相違について

【注意】型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。

同じグループのマイコンでも型名が違うと、内部 ROM、レイアウトパターンの相違などにより、電気的特性の範囲で、特性値、動作マージン、ノイズ耐量、ノイズ輻射量などが異なる場合があります。型名が違う製品に変更する場合は、個々の製品ごとにシステム評価試験を実施してください。

## ご注意書き

- 1. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器・システムの設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因して、お客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 2. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報 の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 3. 本資料に記載された製品デ-タ、図、表、プログラム、アルゴリズム、応用回路例等の情報の使用に起因して発生した第三者の特許権、著作権その他の知的財産権 に対する侵害に関し、当社は、何らの責任を負うものではありません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許 諾するものではありません。

- 4. 当社製品を改造、改変、複製等しないでください。かかる改造、改変、複製等により生じた損害に関し、当社は、一切その責任を負いません。

- 5. 当社は、当社製品の品質水準を「標準水準」および「高品質水準」に分類しており、

各品質水準は、以下に示す用途に製品が使用されることを意図しております。

標準水準: コンピュータ、OA機器、通信機器、計測機器、AV機器、

家電、工作機械、パーソナル機器、産業用ロボット等

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、

防災・防犯装置、各種安全装置等

当社製品は、直接生命・身体に危害を及ぼす可能性のある機器・システム(生命維持装置、人体に埋め込み使用するもの等)、もしくは多大な物的損害を発生させるおそれのある機器・システム(原子力制御システム、軍事機器等)に使用されることを意図しておらず、使用することはできません。 たとえ、意図しない用途に当社製品を使用したことによりお客様または第三者に損害が生じても、当社は一切その責任を負いません。 なお、ご不明点がある場合は、当社営業にお問い合わせください。

- 6. 当社製品をご使用の際は、当社が指定する最大定格、動作電源電圧範囲、放熱特性、実装条件その他の保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質および信頼性の向上に努めていますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害等を生じさせないよう、お客様の責任において、冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、お客様の機器・システムとしての出荷保証を行ってください。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様の機器・システムとしての安全検証をお客様の責任で行ってください。

- 8. 当社製品の環境適合性等の詳細につきましては、製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に 関して、当社は、一切その責任を負いません。

- 9. 本資料に記載されている当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器・システムに使用することはできません。また、当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途に使用しないでください。当社製品または技術を輸出する場合は、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。

- 10. お客様の転売等により、本ご注意書き記載の諸条件に抵触して当社製品が使用され、その使用から損害が生じた場合、当社は何らの責任も負わず、お客様にてご負担して頂きますのでご了承ください。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを禁じます。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

ルネサスエレクトロニクス株式会社

営業お問合せ窓口

http://www.renesas.com

営業お問合せ窓口の住所は変更になることがあります。最新情報につきましては、弊社ホームページをご覧ください。

ルネサス エレクトロニクス株式会社 〒100-0004 千代田区大手町2-6-2 (日本ビル)

技術的なお問合せおよび資料のご請求は下記へどうぞ。 総合お問合せ窓口:http://japan.renesas.com/contact/