# Low-Power Operations Application Note

# Introduction

To reduce the average current consumption and conserve energy, the RH850/U2B series provides a variety of different low-power options.

This document describes the hardware features implemented in the RH850/U2B devices as well as their usage in typical application scenario:

• Cyclic digital and analog signal polling (with port expansion)

The information in this document should be used in conjunction with the corresponding User's Manuals of the RH850/U2B series.

### Target Device

This application note is intended to describe the Low-Power Operations on RH850/U2B series.

The RH850/U2B series has following variants:

| RH850/U2B24-FCC | BGA468 | R7F702Z23EDBG   |  |

|-----------------|--------|-----------------|--|

|                 |        | R7F702Z28EDBG   |  |

| RH850/U2B10-FCC | BGA468 | R7F702Z21EDBG   |  |

|                 |        | R7F702Z26EDBG   |  |

|                 | BGA373 | R7F702Z21EDBA   |  |

|                 |        | R7F702Z26EDBA   |  |

|                 | BGA292 | R7F702Z21EDBB   |  |

|                 |        | R7F702Z26EDBB   |  |

| RH850/U2B6-FCC  | BGA292 | R7F702Z22EDBB   |  |

| RH850/U2B10     | BGA468 | R7F70254EFABG-C |  |

|                 |        | R7F70254FFABG-C |  |

|                 | BGA373 | R7F70254AFABA-C |  |

|                 |        | R7F70254BFABA-C |  |

|                 | BGA292 | R7F70254AFABB-C |  |

|                 |        | R7F70254BFABB-C |  |

| RH850/U2B6      | BGA292 | R7F702552FABB-C |  |

|                 |        | R7F702556FABB-C |  |

### **Disclaimer:**

Renesas Electronics does not warrant the information included in this document. You are fully responsible for incorporation of these circuits, software, and information in the design of your equipment and system. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

# Contents

| Introduction                                                                                                                                                                                                                                                                                        | 1                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Target Device                                                                                                                                                                                                                                                                                       | 1                                |

| Contents                                                                                                                                                                                                                                                                                            | 2                                |

| Contents of Figures                                                                                                                                                                                                                                                                                 | 4                                |

| Contents of Tables                                                                                                                                                                                                                                                                                  | 5                                |

| 1. Background                                                                                                                                                                                                                                                                                       | 6                                |

| <ol> <li>Reference Documents</li> <li>User's Manual</li> </ol>                                                                                                                                                                                                                                      |                                  |

| <ol> <li>Overview of power domains and power supply</li> <li>Power Supply Pins</li> <li>Power Domains Arrangement</li> </ol>                                                                                                                                                                        | 8                                |

| <ul> <li>4. Operation and Chip Standby Modes</li></ul>                                                                                                                                                                                                                                              | 13<br>15                         |

| <ul> <li>4.2.2 System and Peripheral Clock</li> <li>4.3 Chip Standby Modes</li> <li>4.3.1 STOP Mode</li> </ul>                                                                                                                                                                                      | 16<br>17<br>17                   |

| <ul> <li>4.3.2 DeepSTOP Mode</li> <li>4.3.3 Cyclic RUN Mode</li> <li>4.3.4 Cyclic STOP Mode</li> <li>4.4 Wake-Up Control</li> <li>4.5 I/O Buffer Control</li> <li>4.6 BIST Execution</li> </ul>                                                                                                     | 25<br>29<br>31<br>35             |

| <ul> <li>5. Module Standby Mode</li> <li>5.1 Procedure of Module Standby Mode</li> <li>5.1.1 Transition to Module Standby Mode</li> <li>5.1.2 Cancelling Module Standby Mode</li> <li>5.2 Module Standby Registers</li> <li>5.3 Behavior of Module Standby Mode during Chip Standby Mode</li> </ul> | 38<br>38<br>38<br>38<br>38<br>39 |

| <ol> <li>Low-Power Sampler (LPS)</li> <li>Overview</li> <li>Digital Input Mode</li> <li>General Feature of Digital Input Mode</li> </ol>                                                                                                                                                            | 41<br>41<br>43<br>43             |

| 6.2.2 Configuration of Digital Input Mode                                                                                                                                                                                                                                                           | 44                               |

| . 46<br>. 47<br>. 51 |

|----------------------|

|                      |

| . 51                 |

|                      |

| . 51                 |

|                      |

| .53                  |

| . 53                 |

|                      |

| .54                  |

| •                    |

# Contents of Figures

| Figure 4-1 Transition to Chip Standby Modes                        | . 13 |

|--------------------------------------------------------------------|------|

| Figure 4-2 Example of STOP mode transition                         | . 19 |

| Figure 4-3 Example of DeepSTOP mode transition                     | . 23 |

| Figure 4-4 Example of Cyclic RUN mode transition                   | . 27 |

| Figure 4-5 Example of Cyclic STOP mode transition                  | . 30 |

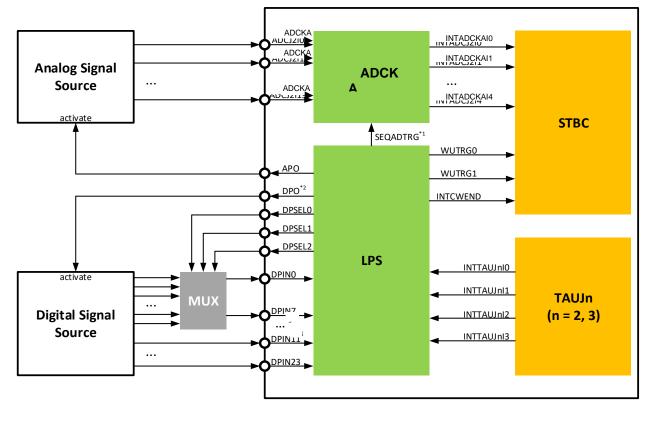

| Figure 6-1 Block Diagram of the LPS                                | . 42 |

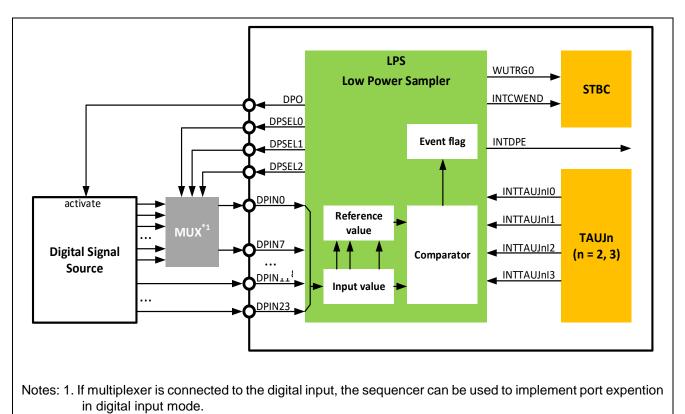

| Figure 6-2 Block Diagram for the Digital Input Mode of LPS         | . 43 |

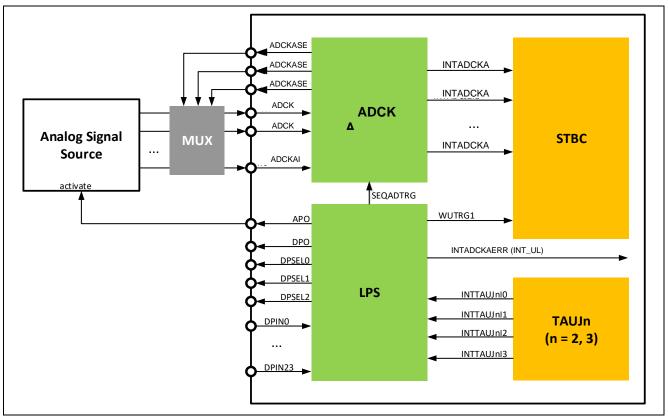

| Figure 6-3 Block Diagram for the Analog Input Mode of LPS          | . 47 |

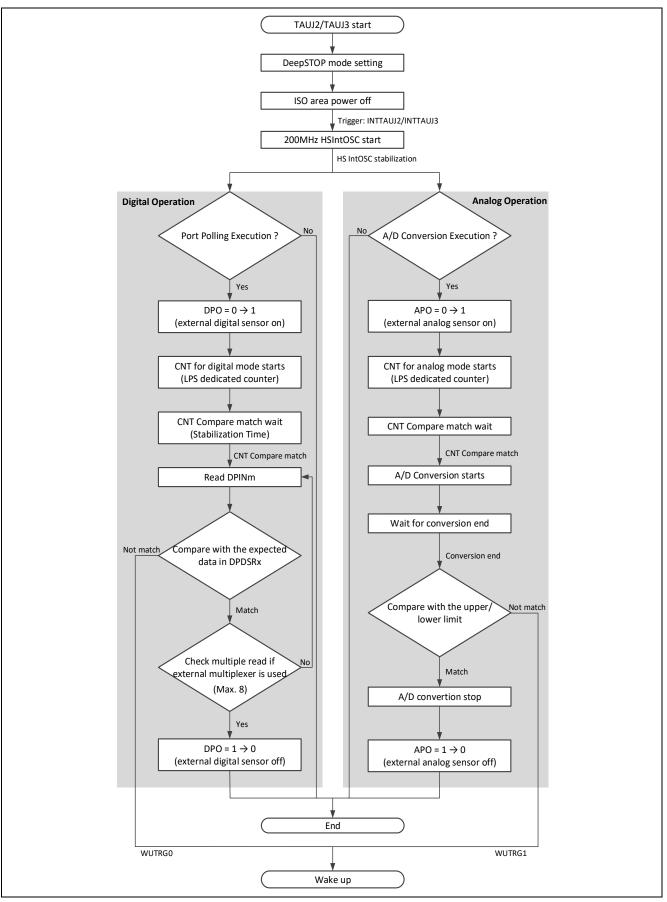

| Figure 6-4 Basic flow chart of the mixed mode                      | . 52 |

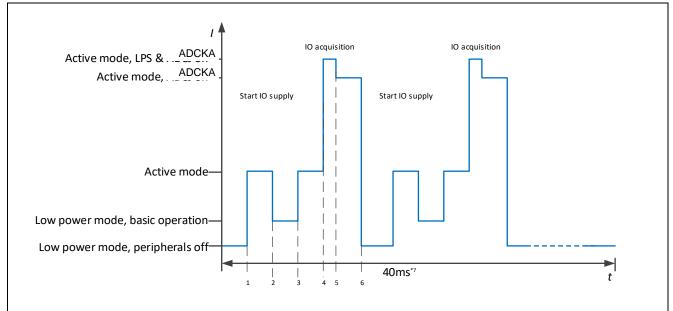

| Figure 7-1 Cyclic Wake-up Calculation of Digital and Analog Inputs | . 53 |

# Contents of Tables

| Table 3-1 Power Supply Pins                                                              | 8  |

|------------------------------------------------------------------------------------------|----|

| Table 3-2 Functional Modules and Power Domain 1                                          | 1  |

| Table 4-1 List of Operation Modes 1                                                      | 4  |

| Table 4-2 Operation of Clock Oscillators in Standby Modes 1                              | 5  |

| Table 4-3 Operation statuses of STOP and DeepSTOP modes 2                                | 23 |

| Table 4-4 Operation Statuses of Cyclic RUN and Cyclic STOP modes                         | 27 |

| Table 4-5 Overview of Wake-Up Factors                                                    | 31 |

| Table 4-6 Wake-Up Factors                                                                | 31 |

| Table 4-7 Buffer Operation before, during and after Chip Standby Modes                   | 35 |

| Table 4-8 Execution Conditions of Standby-Resume BIST                                    | 36 |

| Table 5-1 MSR Registers*2                                                                | 39 |

| Table 5-2 Module Standby Settings and Clock Supply of Peripherals in Chip Standby Mode 4 | 10 |

| Table 6-1 TAUJ Configuration for LPS Application 4                                       | 14 |

| Table 6-2 Configuration of LPS for Digital Input Mode 4                                  | 15 |

| Table 6-3 Status and Result Registers of LPS 4                                           | 16 |

| Table 6-4 ADCJ2 Configuration <sup>*2</sup>                                              | 18 |

| Table 6-5 Configuration of LPS for Analog Input Mode 4                                   | 19 |

### 1. Background

The target of low-power operations is to reduce the (average) current consumption of the device in the related application scenarios.

Typical low-power application is

• Digital and analog port polling (with optional port expansion)

For this use case, the following functionalities are available:

- Support to stop or power-off certain peripherals when no active operation is required.

- CPU operation without Code Flash (Cyclic RUN mode and Cyclic STOP mode), including operation of all peripherals of the AWO area, as well as RLIN3 and MSPI located on the ISO area.

- Support the HW polling of digital and analog input signals and the comparison of the inputs with preconfigured thresholds.

This document introduces the related functions:

- Power supply, described in Section 3.

- Operation and chip standby modes, described in Section 4.

- Module standby mode, described in *Section 5*.

- Low-power sampler, described in Section 6.

- Typical use case of low-power application is presented in Section 7.

# 2. Reference Documents

This chapter contains information about the device reference documentation.

# 2.1 User's Manual

The Hardware User's Manual provides information about the functional and electrical behavior of the device.

At the release time of this document the following manual versions are available:

RH850/U2B Group User's Manual (Rev.1.00): R01UH0923EJ0100

# 3. Overview of power domains and power supply

The internal circuits of RH850/U2B series products are separated into two independent power domains:

- Always-On Area (AWO)

- Isolated Area (ISO)

These power domains are controlled by the power control located on the AWO Area. The AWO area itself remains powered in all operating modes.

The power supply of the Isolated area can be turned off to reduce the overall power consumption depending on the type of stand-by mode.

Dedicated on-chip voltage regulators generate the internal supply voltage for each power domain. The device RH850/U2B series includes the following voltage supplies:

- Power supply voltage SYSVCC for system logic and on-chip voltage regulators. The output voltage of the voltage regulators is supplied to the digital circuits in Always-On area power domain.

- Power supply voltage SVRDRVCC and SVRAVCC and SYSVCC for Switching Voltage Regulator (SVR).

- Power supply voltage ISOVDD for the digital circuits in Isolated area power domain. The ISO area power domain is supplied by an external power supply or SVR.

- Power supply voltage EnVCC for the I/O ports.

- Power supply voltage AnVCC and ADSVCC for the A/D converters and the separated I/O ports.

- Power supply voltage AFCVCC for the FCMP, RDC3AL and the separated I/O ports.

- Power supply voltage LVDVCC for the LVDS ports.

- Power supply voltages EMUVCC and EMUVDD for the Aurora ports.

- Power supply voltage GETH0PVCC, GETH0BVCC for the Ethernet.

# 3.1 Power Supply Pins

Table 3-1 lists all power supply pins and the related peripherals:

| Power supply                       | Power Supply Pins     | Power Supply for                                                                                                                                | Voltage Range              |

|------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Power supply for internal circuits | SYSVCC                | <ul> <li>Power supply for System Logic<br/>and Internal voltage regulator<br/>power and SVR power</li> <li>Power supply terminal for</li> </ul> | 3.0 – 3.6 V<br>4.5 – 5.5 V |

|                                    |                       | PORTS                                                                                                                                           | _                          |

|                                    | VCC                   | Power supply for FLASH<br>JP0x                                                                                                                  |                            |

|                                    | JOVCC                 | RHSIF debug interface (RHSIFD)                                                                                                                  | 3.0 – 3.6 V<br>4.5 – 5.5 V |

|                                    | J1VCC                 | Reference clock for RHSIFD<br>(HSIFD_REFCLK pin)                                                                                                | 3.0 – 3.6 V<br>4.5 – 5.5 V |

|                                    | OSCVCC                | Power supply for OSC                                                                                                                            | 3.0 – 3.6 V<br>4.5 – 5.5 V |

|                                    | RAMSVCL               | Stabilizing capacitance for<br>Retention RAM                                                                                                    | 1.025 – 1.155 V            |

|                                    | SVRDRVCC<br>(DRV_VCC) | Power supply for SVR                                                                                                                            | 3.0 – 3.6 V                |

|                                    | SVRAVCC<br>(AD_VCC)   |                                                                                                                                                 | 4.5 – 5.5 V                |

|                                    | VDD                   | Power supply terminal for ISOVDD                                                                                                                | 1.025 – 1.155 V            |

|                                    | VSS                   | Common ground                                                                                                                                   | -                          |

| Table 3-1 | Power Supply | Pins |

|-----------|--------------|------|

|-----------|--------------|------|

|                  |           | One word for OV/D                   |                                      |

|------------------|-----------|-------------------------------------|--------------------------------------|

|                  | SVRAVSS   | Ground for SVR                      | -                                    |

|                  | (AD_VSS)  |                                     |                                      |

|                  | SVRDRVSS  |                                     |                                      |

|                  | (DRV_VSS) |                                     |                                      |

|                  | AWOVCL    | External buffer capacitance of      | 1.025 – 1.155 V                      |

|                  |           | regulator                           |                                      |

|                  |           | Power supply terminal for ISOVDD    |                                      |

| Power supply for | E0VCC     | RESETOUT                            | 3.0 – 3.6 V                          |

| I/O port         |           | Port group                          | 4.5 – 5.5 V                          |

|                  |           | Pxx_xx                              |                                      |

|                  | E1VCC     | Port group                          |                                      |

|                  |           | Pxx_xx                              |                                      |

|                  | E2VCC     | Port groups                         |                                      |

|                  |           | Pxx_xx                              |                                      |

|                  | VSS       | Common ground                       | _                                    |

| Power supply for | A0VCC     | Analog circuits of ADCK, Port group | 3.0 – 3.6 V                          |

| A/D converters   | A0VREFH   | AN0xx                               | 4.5 – 5.5 V                          |

|                  | A0VSS     | -                                   | _                                    |

|                  | A1VCC     | Analog circuits of ADCK, Port group | 3.0 – 3.6 V                          |

|                  | A1VREFH   | AN1xx                               | 4.5 – 5.5 V                          |

|                  | AIVISEITI |                                     | 4.0 0.0 V                            |

|                  |           | Angles size its of ADOK Dart server | -                                    |

|                  | A2VCC     | Analog circuits of ADCK, Port group | 3.0 – 3.6 V                          |

|                  | A2VREFH   | AN2xx                               | 4.5 – 5.5 V                          |

|                  | A2VSS     |                                     | -                                    |

|                  | A3VCC     | Analog circuits of ADCK, Port group | 3.0 – 3.6 V                          |

|                  | A3VREFH   | AN3xx                               | 4.5 – 5.5 V                          |

|                  | A3VSS     |                                     | -                                    |

| Power supply for | ADSVCC    | Analog circuits of DSADC and        | 3.0 – 3.6 V                          |

| Delta-Sigma and  |           | CADC, Port group                    | 4.5 – 5.5 V                          |

| cyclic A/D       | ADSVSS    | ADSVSS ANxx                         | -                                    |

| converters       |           |                                     |                                      |

| Power supply for | LVDVCC    | LVDS port                           | 3.0 – 5.5 V                          |

| LVDS             | VSS       | Common ground                       | _                                    |

| Power Supply for | AFCVCC    | FCMP                                | 3.0 – 3.6 V                          |

| Fast comparator  |           | RDC3AL                              | 4.5 – 5.5 V                          |

| and RDC3AL       | AFCVSS    |                                     | -                                    |

| Power supply for | GETH0PVCC | Power supply for Ethernet domain    | • 3.14 – 3.46 V (w/                  |

| Ethernet         |           |                                     | SGMII)                               |

|                  |           |                                     | • 3.0 – 3.6 V (w/o                   |

|                  |           |                                     | SGMII)                               |

|                  |           |                                     | ● 4.5 – 5.5 V (w/o                   |

|                  |           |                                     | SGMII)                               |

|                  | GETH0BVCC |                                     | • 3.14 – 3.46 V (w/                  |

|                  |           |                                     | SGMII)                               |

|                  |           |                                     | <ul> <li>- *1 (w/o SGMII)</li> </ul> |

|                  | GETH0VCL  |                                     | 1.025 – 1.155 V                      |

|                  | (SGVCL)   |                                     |                                      |

|                  | GETH1VCL  |                                     | 1.025 – 1.155 V                      |

|                  | VSS       | Common ground                       | -                                    |

| Power supply for | EMUVCC    | Debug circuits                      | 3.0 – 3.6 V                          |

| EMU              | EMUVDD    | Debug circuits of EMU(Aurora)       | • 1.04 – 1.14 V                      |

|                  |           |                                     | (Aurora ON)                          |

| L                | 1         |                                     | · · /                                |

# Low-Power Operations Application Note

|     | ERAM circuits of FLASH | • 1.025 – 1.155 V<br>(Aurora OFF) |

|-----|------------------------|-----------------------------------|

| VSS |                        | -                                 |

Notes: 1. Typically input 3.0 - 3.6 V voltage or connect to VSS with  $\ge 1k\Omega$  pull-down resistance.

# 3.2 Power Domains Arrangement

Table 3-2 shows the functional distribution of the Power Domains:

| Power Domain | Functions                                                          |  |  |

|--------------|--------------------------------------------------------------------|--|--|

| AWO Area     | STBC, Reset controller                                             |  |  |

|              | Retention RAM                                                      |  |  |

|              | CLMA0, CLMA1, CLMA2                                                |  |  |

|              | Main OSC, LS IntOSC, HS IntOSC                                     |  |  |

|              | <ul> <li>WDTBA, RTCA, TAUJ2, TAUJ3, ADCKA</li> </ul>               |  |  |

|              | • LPS                                                              |  |  |

|              | AWO Port groups                                                    |  |  |

| ISO Area     | CPU subsystem, DFP                                                 |  |  |

|              | Code flash, Data flash, Local RAM, Cluster RAM                     |  |  |

|              | PLL, SGMII_PLL, HSIFPLL, SSCG, SSCG1                               |  |  |

|              | • CLMA3, CLMA4, CLMA5, CLMA6, CLMA7, CLMA8, CLMA9, CLMA10, CLMA12, |  |  |

|              | CLMA13, CLMA14, CLMA15                                             |  |  |

|              | <ul> <li>WDTB0, WDTB1, WDTB2, WDTB3, WDTB4, WDTB5</li> </ul>       |  |  |

|              | RHSIF, TPBA, GTM                                                   |  |  |

|              | <ul> <li>TAUD, OSTM, RS-CANFD, RLIN3, RIIC, LTSC</li> </ul>        |  |  |

|              | • ADCK0, ADCK1, ADCK2, ADCK3, TAPA, TSG3, ATU6, ENCA, SFMA, FLXA,  |  |  |

|              | ETN, RSENT, MMCA                                                   |  |  |

|              | DSADC, CADC, DSMIF                                                 |  |  |

|              | RHSB, DFE, HRPWM, EMU3S                                            |  |  |

|              | FCMP, RDC3AL/AS                                                    |  |  |

|              | SWDT, ICUM, ACEU                                                   |  |  |

|              | PSI5, PSI5-S                                                       |  |  |

|              | MSPI, PIC, KCRC, OTS, ECM                                          |  |  |

|              | ISO Port groups                                                    |  |  |

|              | DMON                                                               |  |  |

### Table 3-2 Functional Modules and Power Domain

# **4.** Operation and Chip Standby Modes

The standby controller of RH850/U2B series products support 2 standby modes:

- Chip Standby mode

- Module Standby mode

In this section, a general description about the chip-level low power operations is provided. For module standby modes, please refer to *Section 5 'Module Standby Mode'* in this document.

The RH850/U2B series support the following operation modes:

- RUN mode

- STOP mode

- DeepSTOP mode

- Cyclic RUN mode

- Cyclic STOP mode

- Power Off Standby mode

# 4.1 Overview

The chip-level low-power modes includes STOP mode, DeepSTOP mode and Cyclic operation (Cyclic RUN mode and Cyclic STOP mode).

Transition to chip standby mode should be performed by CPU0(PE0), when CPU0(PE0) shifts to chip standby mode, CPUn(PEn) will also shift to chip standby mode.

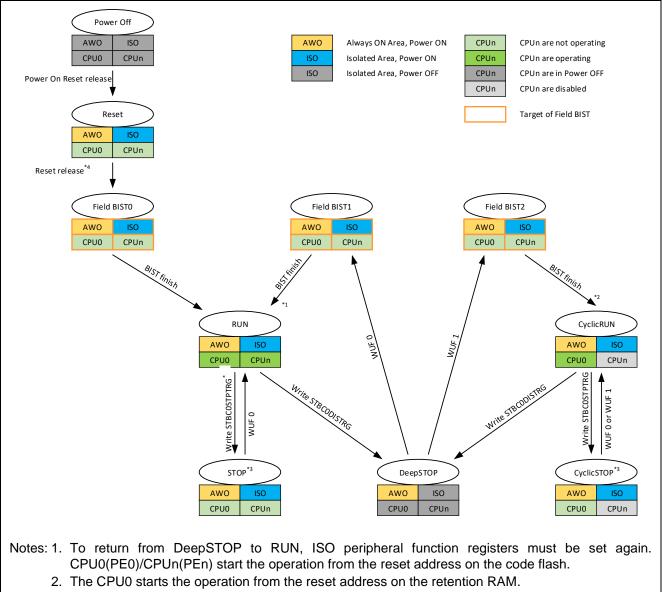

Figure 4-1 shows the state transition of operation modes.

- 3. CPU and bus clocks are stopped at STOP mode/Cyclic STOP mode.

- 4. The Field BIST0 is executed before transition to RUN mode after Power On Reset and System Reset 1/2.

Figure 4-1 Transition to Chip Standby Modes

Table 4-1 lists the definition and mode transition trigger of the operation modes:

| Operation Mode       | Definition                                                                                                                                                                           | Mode Transition Trigger                                                                                               |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| RUN <sup>*1</sup>    | Normal operation mode, all functions are operational                                                                                                                                 | -                                                                                                                     |

| STOP                 | Chip-level standby mode, the clock supplies to certain clock domain can be stopped                                                                                                   | STBC0STPT.STBC0STPTRG                                                                                                 |

| DeepSTOP             | Chip-level standby mode to reduce power<br>consumption further than STOP mode, clock<br>supplies are stopped and the power supply to ISO<br>area is switched off                     | STBC0PSC.STBC0DISTRG                                                                                                  |

| Cyclic RUN           | Low-power operation mode, limited peripherals can<br>operate at low speed.<br>The CPUn(PEn) <sup>*2</sup> is not available.CPU0 executes<br>the instructions from the retention RAM. | <ul> <li>Wake-up factor 1 (from<br/>DeepSTOP mode)</li> <li>Wake-up factor 0/1 (from<br/>Cyclic STOP mode)</li> </ul> |

| Cyclic STOP          | STOP mode in cyclic operation, CPU0 halts its operation                                                                                                                              | STBC0STPT.STBC0STPTRG                                                                                                 |

| Power Off<br>Standby | Only RAM retention is possible in this mode. Low leakage is realized by turning off the power outside of the MCU and by stopping oscillators.                                        | Asserting the external reset<br>pin and turning off the power<br>except SYSVCC                                        |

Notes: 1. RUN mode is not discussed in this application note. 2. n!=0

In transition of operation modes, the Build-In-Self-Test (BIST) can be executed during DeepSTOP Reset. For detailed information please refer to *Section 4.6 BIST Execution*.

# 4.2 Clock Supply in Chip Standby Mode

### 4.2.1 Clock Oscillators

In chip standby mode (STOP mode, DeepSTOP mode, and Cyclic STOP mode), the LS IntOSC continues operation. Main OSC, HS IntOSC and PLL can be set to stop or continue via <name>STPM registers.

HV IntOSC continues in STOP and Cyclic modes and can be set stopped or continue via the VMONDSCR register in DeepSTOP mode.

Table 4-2 lists the operation of clock oscillators in standby modes.

| Oscillators                | STOP mode                                                                                      | DeepSTOP mode                                                                                                                                                   | Cyclic<br>STOP          | Cyclic RUN            |  |  |  |

|----------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------|--|--|--|

| Main OSC                   |                                                                                                | CSTPMSK = 0, oscillation is stop<br>CSTPMSK = 1, oscillation contin                                                                                             | •                       | Oscillation continues |  |  |  |

| LS IntOSC<br>HS IntOSC     |                                                                                                | OSCSTPMSK = 0, oscillation is stoppedOscillationOSCSTPMSK = 1, oscillation continuescontinues                                                                   |                         |                       |  |  |  |

| PLL                        | Oscillation continues when<br>bit<br>MOSCSTPM.MOSCSTPMSK<br>= 1 and<br>PLLSTPM.PLLSTPMSK = 1*2 | Disabled <sup>*3</sup>                                                                                                                                          | Not available operation | in cyclic             |  |  |  |

| HV<br>IntOSC <sup>*4</sup> | Oscillation continues                                                                          | <ul> <li>For bit<br/>VMONDSCR.DSDETEN</li> <li>= 0, oscillation is stopped</li> <li>For bit<br/>VMONDSCR.DSDETEN</li> <li>= 1, oscillation continues</li> </ul> | Oscillation co          | ntinues               |  |  |  |

#### Table 4-2 Operation of Clock Oscillators in Standby Modes

Notes: 1. After power supply the LS IntOSC starts operation. It cannot be stopped.

2. For detailed information, please refer to the device User's Manual R01UH0923EJ0100 Section 15.4.5 'Phase Locked Loop (PLL)'.

3. PLL is disabled in DeepSTOP mode, a software restart is necessary to start the PLL after transition from DeepSTOP mode to RUN mode.

4. Only used for VMON, the general operation of this oscillator in chip standby mode is described in *Section 4.3.2 'DeepSTOP Mode'*. Further information is not provided in this application note.

## 4.2.2 System and Peripheral Clock

The following CPU subsystem clocks are stopped in chip standby modes (STOP mode, DeepSTOP mode and Cyclic STOP mode):

- CPU clock CLK\_CPU

- SBUS clock CLK\_SBUS

- HBUS clock CLK\_HBUS

Regarding to peripherals, the clock stop mask bits MSR\_<name>.STPMSK\_<name> are used to determine the operation status of the clock in chip standby mode:

• If the stop mask bit is set to 0, the stop request is not masked, the related peripheral clock stops during chip standby mode.

If the clock is in operation before entering standby mode, the clock restarts automatically after wake-up of chip standby mode.

• If the stop mask bit is set to 1, the stop request is masked, the corresponding peripheral clock continues operate during chip standby mode.

The clock supply of ISO area is stopped in DeepSTOP mode.

Table 5-1 in Section 5.2 'Module Standby Registers' includes the information about the peripheral clock supplies which can be set continue using MSR\_<name> registers in standby modes.

Section 5.3 provides the information of the clock supply to peripherals in each operation mode and chip standby mode.

# **4.3**Chip Standby Modes

# 4.3.1 STOP Mode

In STOP mode, the clock supply to the CPU core and the CPU subsystem is stopped.

The low speed internal oscillator CLK\_LSIOSC and high voltage internal oscillator CLK\_HSIOSC can operate.

Main oscillator CLK\_MOSC, high speed internal oscillator CLK\_HSIOSC and PLL are stopped in default settings, these clock sources can be configured to continue operating by masking stop request.

In addition, basically all peripheral functions are stopped before the transition to STOP mode is made. Only a limited number of peripherals may remain operable on the available clock sources.

The contents of Local RAM and Retention RAM before the transition to STOP mode are remained.

The I/O buffers remain their state before entering STOP mode.

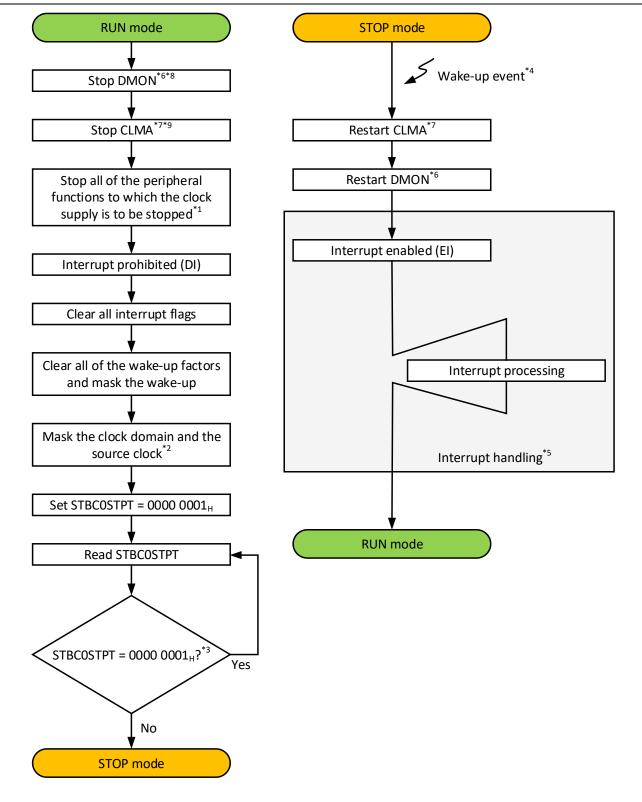

#### (1) Preparation for STOP Mode

Before starting STOP mode, the following setup is needed as the preparation for standby:

- Stop Delay Monitor (DMON).

- Stop Clock Monitor (CLMA). (if the monitor clock would be stopped.)

- Stop all the peripheral functions whose clock supply will be stopped.

- Disable the interrupt handling by the CPU instruction "DI".

- Set the interrupt control registers.

- Clear the interrupt flag (EICn.EIRFn = 0).

- Mask the interrupts for non-wake-up factors (EICn.EIMKn= 1).

- Release the masks of the interrupts for wake-up factors (EICn.EIMKn = 0).

- Set the wake-up related registers.

- Clear the wake-up factor flags (the WUFC0\_Ax / WUFC0\_ly registers, x = 0 to 2, y = 0 to 3).

- Mask the non-wake-up factor (the WUFMSK0\_Ax / WUFMSK0\_ly registers, x = 0 to 2, y = 0 to 3).

- Release the masks of the wake-up factors (the WUFMSK0\_Ax / WUFMSK0\_ly registers, x = 0 to 2, y = 0 to 3).

- Set the clock stop mask register to select the clock domains to be stopped and the ones to continue operating (using the MSR\_<name>.STPMSK\_<name> bit).

- Specify whether to oscillate or stop each clock source. In addition, set the clock stop mask register to

select the clock sources to be stopped and the ones to continue operating (using the MOSCSTPMSK bit

in the MOSCSTPM register and the HSOSCSTPMSK bit in the HSOSCSTPM register and the

PLLSTPMSK bit in the PLLSTPM register).

### (2) Start of STOP Mode

According to Figure 4-1 and Table 4-1, setting the STBC0STPTRG bit of register STBC0STPT to 1, the device is shifted into STOP mode.

For the detailed information for the operation status of different modules in STOP mode, please refer to Table 4-3.

## (3) End of STOP Mode

The device can return to RUN mode from STOP mode when a wake-up event is generated as configured in the corresponding WUF0\_Ax or WUF0\_Iy (x = 0 to 2, y = 0 to 3) registers.

#### (4) Wake-up Handling

The generation of wake-up events can be determined by the wake-up factor flags WUF0\_Ax or WUF0\_ly (x = 0 to 2, y = 0 to 3).

When an interrupt is enabled by the CPU instruction "EI", the corresponding wake-up interrupt will be executed.

### (5) Transition Procedure to STOP Mode

The transition procedure (example) to STOP mode is shown below in Figure 4-2.

- Notes: 1. Before the transition to STOP mode, all the peripheral functions whose clock supply will be stopped, must be turned off. Otherwise the operation of the peripheral function may be incorrect.

- 2. The clock mask must be set before 0000 0001H is written to STBC0STPT.

- STBC0STPT.STBC0STPTRG bit is cleared automaticlly after transition to STOP mode. The clock supply to the CPU is stopped and the operation shifts to the STOP mode while checking that STBC0STPT = 0000 0001<sub>H</sub>.

- 4. STBC0STPT is set to 0000 0000<sub>H</sub> at the generation of a wake-up event. The generated wake-up factor can be checked by the WUF0\_Ax and WUF0\_Iy (x = 0 to 2, y = 0 to 3) registers.

- 5. This processing is optional. It is required to execute the interrupt handling after the wake-up.

- 6. For details please refer to HW user's Manual R01UH0923EJ0100 Section 13.4.7.4 'Procedures to Reset DMON.

- 7. For details please refer to HW user's Manual R01UH0923EJ0100 Section 16.6.2 'Procedures to Reset by CLMATEST.RESCLM.

- 8. Stop DMON when Main OSC stops at chip standby mode.

Figure 4-2 Example of STOP mode transition

#### (6) Operation Status of STOP Mode

For the detailed information for the operation status of CPUs and peripherals during STOP mode, please refer to *Section 4.3.2* Table 4-3.

### **4.3.2** DeepSTOP Mode

In DEEPSTOP mode, the power supply to the Isolated Area is turned off.

The low speed internal oscillator LS IntOSC continues.

PLL is automatically disabled during transition to DeepSTOP mode.

Main oscillator Main OSC and high speed internal oscillator HS IntOSC are stopped in default settings, these clock sources can be configured to continue operating by masking stop request.

The high voltage internal oscillator HV IntOSC can be automatically disabled, depends on the configuration in the VMON DeepSTOP control register VMONDSCR.

For peripherals in Always-On Area that continue operation in DeepSTOP, the clock supply can be continued by setting the clock stop mask register.

The I/O buffers in DeepSTOP mode are changing into I/O buffer hold state by default, meaning the state of the buffers is frozen. The input or output remains in the state before entering DeepSTOP mode, no external or internal signal can change its state until the I/O buffer hold state is terminated after wake-up from DeepSTOP.

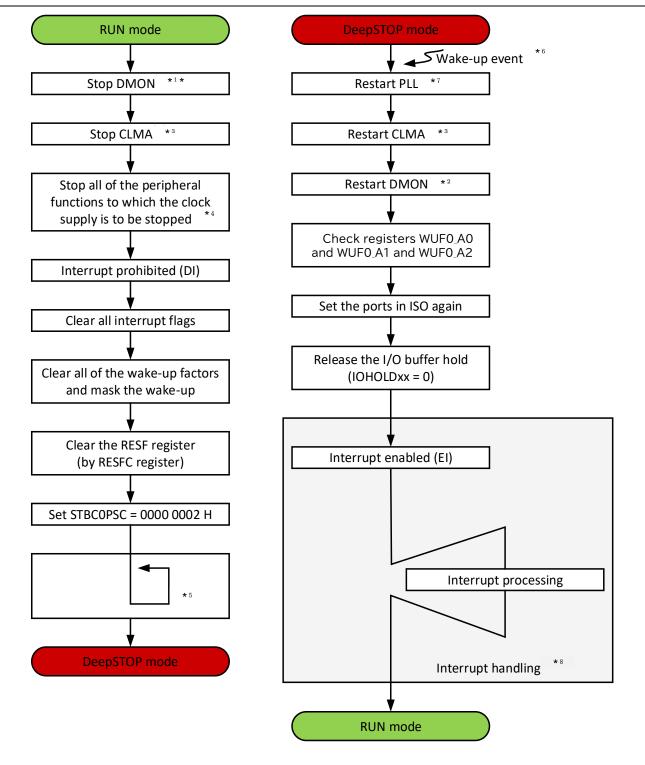

#### (1) Preparation for DeepSTOP Mode

Before starting DeepSTOP mode, the following setup is needed as the preparation for standby:

- Stop DMON.

- Stop CLMA (if the monitor clock would be stopped).

- Stop all the peripheral functions to which the clock supply is to be stopped.

- Disable the interrupt handling by the CPU instruction "DI".

- Set the interrupt control registers.

- Clear the interrupt flag (EIC.EIRFn = 0).

- Mask the interrupts for non-wake-up factors (EIC.EIMKn = 1).

- Release the masks of the interrupts for wake-up factors (EIC.EIMKn = 0).

- Set the wake-up related registers.

- Clear the wake-up factor flags (the WUFCn\_Ax / WUFCn\_ly registers, n = 0 or 1, x = 0 to 2, y = 0 to 3).

- Mask the non-wake-up factor (the WUFMSKn\_Ax / WUFMSKn\_Iy registers, n = 0 or 1, x = 0 to 2, y = 0 to 3).

- Release the masks of the wake-up factors (the WUFMSKn\_Ax / WUFMSKn\_ly registers, n = 0 or 1, x = 0 to 2, y = 0 to 3).

- Set the clock stop mask register to select the clock domains to be stopped and the ones to continue operating (using the MSR\_<name>.STPMSK\_<name> bit).

- Specify whether to oscillate or stop each clock source. In addition, set the clock stop mask register to

select the clock sources to be stopped and the ones to continue operating (using the MOSCSTPMSK bit

in the MOSCSTPM register and the HSOSCSTPMSK bit in the HSOSCSTPM register).

#### (2) Start of DeepSTOP Mode

According to Figure 4-1, if the STBC0PSC.STBC0DISTRG bit is set to 1, the device starts DeepSTOP mode.

#### (3) End of DeepSTOP Mode

When a wake-up factor is generated, the microcontroller returns from DeepSTOP mode.

By releasing DeepSTOP mode, the Build-In-Self-Test (BIST) might be executed, for detailed BIST execution condition, please refer to *Section 4.5 BIST Execution*.

#### (4) Wake-up Handling

- If the device returns from DeepSTOP mode due to wake-up factor 0:

- The device switches to RUN mode, the operation starts from the reset vector address.

If one of the FENMI or FEINT interrupts has been generated before recovery from DeepSTOP mode to RUN mode, the microcontroller restarts operation from operation from exception handler address:

- FENMI: FENMI handler address (E0<sub>H</sub>)

- FEINT: FEINT handler address (F0<sub>H</sub>)

The general-purpose registers and local RAM are undefined after return from DeepSTOP mode.

- If the device returns from DeepSTOP mode due to wake-up factor 1:

- The device switches to Cyclic RUN mode, the CPU0 starts the operation from the reset address on the retention RAM.

If one of the FENMI or FEINT interrupts has been generated before recovery from DeepSTOP mode to Cyclic RUN mode, the microcontroller restart operation from the exception handler address:

- FENMI: FENMI handler address (FE80 0000<sub>H</sub> + E0<sub>H</sub>)

- FEINT: FEINT handler address (FE80 0000<sub>H</sub> + F0<sub>H</sub>)

- The generation of the wake-up factors can be determined by the wake-up factor flags WUFn\_Ax (n = 0 or 1, x = 0 to 2).

- The ports in the Isolated area maintain the I/O buffer hold state.

Release the I/O buffer hold state by executing the following steps:

- 1. Re-configure the peripheral functions and port functions.

- 2. Set IOHOLDn.IOHOLD\_xxx = 0. (n=0, 1)

- To execute an interrupt of the wake-up factor after the wake-up, evaluate the information of wakeup factor flag by software and set the interrupt request flag in the interrupt control register. Then, when an interrupt is enabled by the CPU instruction "EI", the generated wake-up interrupt will be executed.

(5) Transition Procedure to DeepSTOP Mode

Figure 4-3 shows a general example of the transition procedure to enter and leave the DeepSTOP mode.

Notes: 1. Stop DMON when Main OSC stops at chip standby mode.

- 2. For details please refer to HW user's Manual R01UH0923EJ0100 Section 13.4.7.4 'Procedures to Reset DMON.

- 3. For details please refer to HW user's Manual R01UH0923EJ0100 Section 16.6.2 'Procedures to Reset by CLMATEST.RESCLM'.

- 4. When the operation of the peripheral function is stopped during operating due to the transition to the DeepSTOP mode, the operation of the peripheral function may be incorrect. Therefore, before the transition to the DeepSTOP mode, stop all of the peripheral functions whose clock supply is to be cut off.

- 5. After setting STBC0PSC = 0000  $0002_{H}$ , wait for the transition to the DeepSTOP mode by the unconditional loop.

- 6. The CPU starts the program from the reset vector after the generation of a wake-up event. The return from the DeepSTOP mode by a reset can be checked by the RESF register. In addition, the generated wake-up event can be checked by the WUF0\_A0, WUF0\_A1 and WUF\_A2 registers.

- 7. A software PLL restart is necessary, if PLL is requied after transition to RUN mode.

- 8. This processing is optional. It is required to execute the interrupt handling after the wake-up.

# Figure 4-3 Example of DeepSTOP mode transition

#### (6) Operation Status of DeepSTOP Mode

For the detailed information for the operation status of CPUs and peripherals during DeepSTOP mode, please refer to Table 4-3.

|                   | Function                         |                      | STOP Mode | DeepSTOP Mode |

|-------------------|----------------------------------|----------------------|-----------|---------------|

| Port              | AWO                              |                      | Stop      | Operable      |

|                   | ISO                              |                      | Stop      | Stop          |

| CPU               |                                  |                      | Stop      | Stop          |

| LPS               |                                  |                      | Operable  | Operable      |

| EXTCLK            |                                  |                      | Operable  | Operable      |

| Peripheral Interc | connect (PI                      | C)                   | Stop      | Stop          |

| DFP               |                                  |                      | Stop      | Stop          |

| Mortor Control    | EMU                              |                      | Stop      | Stop          |

| IP                | RDC                              |                      | Stop      | Stop          |

| DSMIF             |                                  |                      | Stop      | Stop          |

| Flash             | Code Fla                         | sh                   | Stop      | Stop          |

|                   | Data Flas                        | sh                   | Stop      | Stop          |

| RAM               | Local RA                         | Μ                    | Stop      | Stop          |

|                   | Cluster R                        | AM                   | Stop      | Stop          |

|                   | Retention RAM                    |                      | Stop      | Operable      |

| Timer             | Operating System Timer<br>(OSTM) |                      | Stop      | Stop          |

|                   | Window                           | WDTBA                | Operable  | Operable      |

|                   | Watchd<br>og<br>Timer            | WDTB0 to 5,<br>SWDTA | Stop      | Stop          |

|                   | Timer Arr<br>(TAUD)              | ay Unit D            | Stop      | Stop          |

|                   | Timer<br>Array<br>Unit J         | TAUJ2,<br>TAUJ3      | Operable  | Operable      |

|                   | Long-Ter<br>Counter (            | m System<br>LTSC)    | Stop      | Stop          |

|                   | Generic T<br>(GTM)               | Timer Module         | Stop      | Stop          |

|                   | ATU                              |                      | Stop      | Stop          |

|                   | Real-time<br>(RTCA)              | e Counter            | Operable  | Operable      |

|                   | Motor Co<br>(TSG3)               | ntrol Timer          | Stop      | Stop          |

|                   | Timer Op                         | tion (TAPA)          | Stop      | Stop          |

|                   |                                  | ttern Buffer         | Stop      | Stop          |

#### Table 4-3 Operation statuses of STOP and DeepSTOP modes

|                | Encoder Timer (ENCA)                                  | Stop      | Stop     |

|----------------|-------------------------------------------------------|-----------|----------|

|                | High-Resolution PWM<br>(HRPWM)                        | Stop      | Stop     |

| Communication  | RLIN3                                                 | Operable  | Stop     |

|                | Multichannel Serial<br>Peripheral Interface<br>(MSPI) | Stop      | Stop     |

|                | Renesas High-Speed<br>Serial I/F (RHSIF)              | Stop      | Stop     |

|                | I2C Interface (RIIC)                                  | Stop      | Stop     |

|                | CAN Interface<br>(RS-CANFD)                           | Operable  | Stop     |

|                | FlexRay (FLXA)                                        | Stop      | Stop     |

|                | Renesas High Speed<br>Bus (RHSB)                      | Stop      | Stop     |

|                | Ethernet (ETN)                                        | Stop      | Stop     |

|                | Single Edge Nibble<br>Transmission (RSENT)            | Stop      | Stop     |

|                | PSI5                                                  | Stop      | Stop     |

|                | PSI5S                                                 | Stop      | Stop     |

|                | Multimedia Card<br>Interface (MMCA)                   | Stop      | Stop     |

|                | Serial Flash Memory<br>Interface A (SFMA)             | Stop      | Stop     |

| Safety         | Clock CLMA0 to 2                                      | Stop      | Operable |

|                | Monitor CLMA3 to 15                                   | Stop      | Stop     |

|                | Voltage Monitor (VMON)                                |           | Stop     |

|                | OTS                                                   | Stop      | Stop     |

|                | Data CRC Function K<br>(KCRC)                         | Stop      | Stop     |

|                | Error Control Module<br>(ECM)                         | Operable* | Stop     |

| A/D Converter  | SAR-ADCA                                              | Operable  | Operable |

|                | SAR-ADC0~3                                            | Stop      | Stop     |

|                | DS-ADC/CADC                                           | Stop      | Stop     |

|                | FCOMP                                                 | Stop      | Stop     |

| Digital Filter | DFE                                                   | Stop      | Stop     |

| Security       | ICUMHA                                                | Stop      | Stop     |

Note: ECM delay timer clock (CLK\_ECMCNT) stops.

# 4.3.3 Cyclic RUN Mode

Cyclic RUN mode is very similar to the 'normal' RUN mode, except the fact that:

- PLL and Flash memory are not available.

- The CPU0 fetches the instruction from the Retention RAM (Standby RAM), the CPUn (n!=0) are not available.

- Only a limited number of peripherals (RLIN3, MSPI and AWO peripherals) can be active.

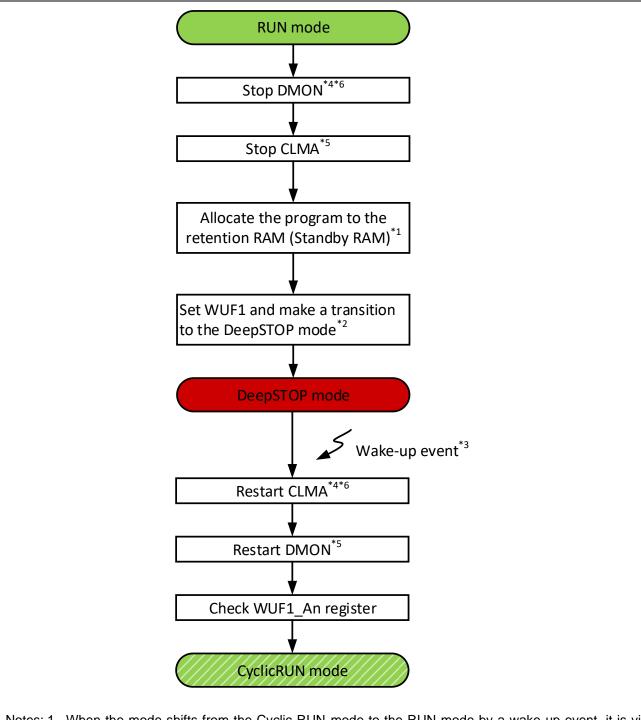

#### (1) Preparation for Cyclic RUN Mode

Before the transition to Cyclic RUN mode, the following preparation is necessary:

- Stop DMON and CLMA if Main OSC is stopped in STOP mode.

- Arrange the program for Cyclic RUN in the Retention RAM.

- Set the wake-up related registers:

- Clear the wake-up factor flags (the WUFC1\_Ax/WUFC1\_ly register, x = 0 to 2, y = 0 to 3).

- Mask the non-wake-up factor (the WUFMSK1\_Ax/WUFMSK1\_ly register, x = 0 to 2, y = 0 to 3).

- Release the masks of the wake-up factor (the WUFMSK1\_Ax/WUFMSK1\_ly register, x = 0 to 2, y = 0 to 3).

- Make the transition to DeepSTOP mode. For details on how to transit to DeepSTOP mode, please refer to Section 4.3.2 DeepSTOP mode.

#### (2) Start of Cyclic RUN Mode

The operation transitions to Cyclic RUN mode from DeepSTOP mode at the generation of wake-up factor 1.

The operation transitions to Cyclic RUN mode from Cyclic STOP mode at the generation of wake-up factors 0 or 1.

The operation starts from the reset vector address of Cyclic RUN mode (the first address of the Standby RAM).

If one of the FENMI or FEINT interrupts has been generated before recovery from DeepSTOP mode to Cyclic RUN mode, the microcontroller restart operation from the exception handler address:

- FENMI: FENMI handler address (beginning address + E0<sub>H</sub>)

- FEINT: FEINT handler address (beginning address + F0<sub>H</sub>)

### (3) End of Cyclic RUN Mode

The Cyclic RUN mode ends:

- at the transition to the Cyclic STOP mode by setting the STBC0STPT.STBC0STPTRG bit to 1

- at the transition to the DeepSTOP mode by setting the STBC0PSC.STBC0DISTRG bit to 1.

### (4) Transition Procedure to Cyclic RUN Mode

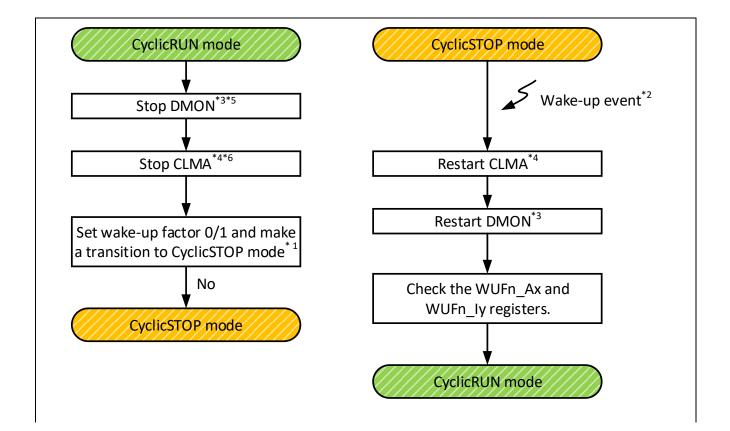

The transition procedure (example) to Cyclic RUN mode is shown below in Figure 4-4.

- Notes: 1. When the mode shifts from the Cyclic RUN mode to the RUN mode by a wake-up event, it is via DeepSTOP mode. The transition to the DeepSTOP mode should be made in the processing of the interrupt vector for the wake-up event. In that case, the interrupt processing program on the Retention RAM must be allocated.

- 2. Before the transition to the DeepSTOP mode, clear the flag for wake-up factor 1 in the WUFC1 An register and set wake-up factor that is be used 1 to by the WUFMSK1\_A0/WUFMSK1\_A1/WUFMSK1\_A2 register. Other processing for the transition to the DeepSTOP mode is as usual, please refer to Section 4.2.2 (5) Transition Procedure to DeepSTOP Mode.

- 3. The CPU starts the program from the top address on the Retention RAM after the generation of a wake-up event. The generated wake-up event can be checked by the WUF1\_Ax (x = 0 to 2) register.

- 4. For details please refer to HW user's Manual R01UH0923EJ0100 Section 13.4.7.4 'Procedures to Reset DMON' and Section 13.4.6.4 'DMONDIAGME DMON DIAG Monitor Enable Register'.

- 5. For details please refer to HW user's Manual R01UH0923EJ0100 Section 16.6.2 'Procedures to Reset by CLMATEST.RESCLM' and Section 16.5.7 'CLMAnCTL CLMAn Control Register'.

- 6. Stop DMON when Main OSC stops at chip standby mode.

Figure 4-4 Example of Cyclic RUN mode transition

#### (5) Operation Status of Cyclic RUN Mode

Table 4-4 lists the detailed operation status of Cyclic RUN mode.

#### Table 4-4 Operation Statuses of Cyclic RUN and Cyclic STOP modes

|                  | Function                           |                 | Cyclic RUN Mode | Cyclic STOP Mode |

|------------------|------------------------------------|-----------------|-----------------|------------------|

| Port             | AWO                                |                 | Operable        | Operable         |

|                  | ISO                                |                 | Stop            | Stop             |

| CPU              | CPU0                               |                 | Operable        | Stop             |

|                  | CPUn (n ;                          | ≠ 0)            | Stop            | Stop             |

| LPS              |                                    |                 | Operable        | Operable         |

| EXTCLK           |                                    |                 | Operable        | Operable         |

| Peripheral Inter | connect (Pl                        | C)              | Stop            | Stop             |

| DFP              |                                    |                 | Stop            | Stop             |

| Motor Control    | EMU                                |                 | Stop            | Stop             |

| IP               | RDC                                |                 | Stop            | Stop             |

| DSMIF            |                                    |                 | Stop            | Stop             |

| Flash            | Code Flas                          | sh              | Stop            | Stop             |

|                  | Data Flas                          | h               | Stop            | Stop             |

| RAM              | Local RA                           | N               | Stop            | Stop             |

|                  | Cluster R                          | AM              | Stop            | Stop             |

|                  | Retention                          | RAM             | Operable        | Operable         |

| Timer            | Operating System Timer<br>(OSTM)   |                 | Stop            | Stop             |

|                  | Window                             | WDTBA           | Operable        | Operable         |

|                  | Watchdo<br>g Timer                 | WDTB0           | Operable        | Stop             |

|                  |                                    | WDTB1 to 5      | Stop            | Stop             |

|                  |                                    | SWDTA           | Operable        | Stop             |

|                  | Timer Array Unit D<br>(TAUD)       |                 | Stop            | Stop             |

|                  | Timer<br>Array<br>Unit J           | TAUJ2,<br>TAUJ3 | Operable        | Operable         |

|                  | Long-Term System<br>Counter (LTSC) |                 | Stop            | Stop             |

|                  | Generic T<br>(GTM)                 | ïmer Module     | Stop            | Stop             |

|                  | ATU                                |                 | Stop            | Stop             |

|                  | Real-time<br>(RTCA)                | Counter         | Operable        | Operable         |

|                  | Motor Cor<br>(TSG3)                | ntrol Timer     | Stop            | Stop             |

|                  | Timer Opt                          | tion (TAPA)     | Stop            | Stop             |

|                  | Timer Pat<br>(TABA)                | tern Buffer     | Stop            | Stop             |

|                  | Encoder 7                          | Timer (ENCA)    | Stop            | Stop             |

|                  | High-Res<br>(HRPWM)                | olution PWM     | Stop            | Stop             |

|                  | RLIN3                              |                 | Operable        | Operable         |

| Communicatio Multichannel Ser<br>n Peripheral Interfa<br>(MSPI) |                                              |                           | Operable  | Stop      |

|-----------------------------------------------------------------|----------------------------------------------|---------------------------|-----------|-----------|

|                                                                 | Renesas<br>Serial I/F                        | High-Speed<br>(RHSIF)     | Stop      | Stop      |

|                                                                 | I2C Interf                                   | ace (RIIC)                | Stop      | Stop      |

|                                                                 | CAN Inter<br>(RS-CAN                         |                           | Stop      | Stop      |

|                                                                 | FlexRay (                                    | FLXA)                     | Stop      | Stop      |

|                                                                 | Renesas<br>Bus (RHS                          | High Speed<br>SB)         | Stop      | Stop      |

|                                                                 | Ethernet                                     | (ETN)                     | Stop      | Stop      |

|                                                                 |                                              | ge Nibble<br>sion (RSENT) | Stop      | Stop      |

|                                                                 | PSI5                                         |                           | Stop      | Stop      |

|                                                                 | PSI5S<br>Multimedia Card<br>Interface (MMCA) |                           | Stop      | Stop      |

|                                                                 |                                              |                           | Stop      | Stop      |

|                                                                 |                                              | sh Memory<br>A (SFMA)     | Stop      | Stop      |

| Safety                                                          | Clock                                        | CLMA0 to 2                | Operable  | Operable  |

|                                                                 | Monitor                                      | CLMA3 to 15               | Stop      | Stop      |

|                                                                 | Voltage Monitor (VMON)                       |                           | Stop      | Stop      |

|                                                                 | OTS                                          |                           | Stop      | Stop      |

|                                                                 | Data CRC Function K<br>(KCRC)                |                           | Stop      | Stop      |

|                                                                 | Error Control Module<br>(ECM)                |                           | Operable* | Operable* |

| A/D Converter                                                   | SAR-ADC                                      | CA                        | Operable  | Operable  |

|                                                                 | SAR-ADC                                      | 20~3                      | Stop      | Stop      |

|                                                                 | DS-ADC/                                      | CADC                      | Stop      | Stop      |

|                                                                 | FCOMP                                        |                           | Stop      | Stop      |

| Digital Filter                                                  | DFE                                          |                           | Stop      | Stop      |

| Security                                                        | ICUMHA                                       |                           | Stop      | Stop      |

Note: ECM delay timer clock (CLK\_ECMCNT) stops.

# **4.3.4** Cyclic STOP Mode

In Cyclic STOP mode, the functions except RLIN3 and the AWO area peripheral function are stopped.

# (1) Preparation for Cyclic STOP Mode

For Cyclic STOP mode, the following setups must be done before the transition:

- Stop DMON.

- Stop CLMA (if the monitor clock would be stopped).

- Ensure the transition to Cyclic RUN mode is finished.

- Set the wake-up related registers.

- Clear the wake-up factor flags (the WUFCn\_Ax/WUFCn\_ly register, n = 0 or 1, x = 0 to 2, y = 0 to 3).

- Mask the non-wake-up factor (the WUFMSKn\_Ax/WUFMSKn\_Iy register, n = 0 or 1, x = 0 to 2, y = 0 to 3).

- Release the masks of the wake-up factor (the WUFMSKn\_Ax/WUFMSKn\_ly register, n = 0 or 1, x = 0 to 2, y = 0 to 3).

- (2) Start of Cyclic STOP Mode

According to Figure 4-1, the operation switches from Cyclic RUN to Cyclic STOP mode when the STBC0STPTRG bit in register STBC0STPT is set to 1.

#### (3) End of Cyclic STOP Mode

The operation transitions to Cyclic RUN mode at the generation of wake-up factor 0 or 1.

#### (4) Wake-up Handling

The generation of the wake-up factors can be determined by the wake-up factor flags (WUFn\_Ax/WUFn\_ly, n = 0 or 1, x = 0 to 2, y = 0 to 3).

### (5) Transition Procedure to Cyclic STOP Mode

The transition procedure (example) to Cyclic STOP mode is shown below in Figure 4-5.

- Notes: 1. The wake-up factors 0 and 1 are normally set to make a transition respectively to RUN mode and Cyclic RUN mode. In the case of Cyclic STOP mode, the operation can only directly switch to Cyclic RUN mode by either wake-up factor 0 or 1.

- When a wake-up factor is generated in Cyclic STOP mode, the mode shifts to Cyclic RUN mode and the operation starts immediately after the processing shifted to Cyclic RUN mode. The generated wake-up factors can be checked by the WUFn\_Ax, WUFn\_Iy (n = 0 or 1, x = 0 to 2, y = 1) registers.

- 3. For details please refer to HW user's Manual R01UH0923EJ0100 Section 13.4.7.4 'Procedures to Reset DMON' and Section 13.4.6.4 'DMONDIAGME DMON DIAG Monitor Enable Register'.

- 4. For details please refer to HW user's Manual R01UH0923EJ0100 Section 16.6.2 'Procedures to Reset by CLMATEST.RESCLM' and Section 16.5.7 'CLMAnCTL CLMAn Control Register'.

- 5. Stop DMON when Main OSC stops at chip standby mode.

Figure 4-5 Example of Cyclic STOP mode transition

#### (6) Operation Status of Cyclic STOP Mode

For detailed operation status of Cyclic STOP mode, please refer to Table 4-4 in Section 4.2.3.

# 4.4 Wake-Up Control

The chip operation returns from standby modes when a wake-up event occurs.

For different mode transition, the RH850/U2B group provide different category of wake-up events. Table 4-5 shows an overview of these wake-up factors and the operation after wake-up events.

| Category | Mode Transition           | Wake-Up Factor        | Operation after Wake-Up |                             |  |

|----------|---------------------------|-----------------------|-------------------------|-----------------------------|--|

|          |                           |                       | System Clock            | Fetch Address               |  |

| Wake-Up  | $STOP \to RUN$            | WUF0_Ax, $x = 0$ to 2 | Clock setting           | Next address before         |  |

| Factor 0 |                           | WUF0_ly, $y = 0$ to 3 | before STOP             | STOP mode was entered       |  |

|          |                           |                       | mode                    | or interrupt vector         |  |

|          | $DeepSTOP \to RUN$        | WUF0_Ax, $x = 0$ to 2 | Internal OSC            | RESET vector of code        |  |

|          |                           |                       | Clock (200 MHz          | flash                       |  |

|          |                           |                       | or 240 kHz)             |                             |  |

|          | Cyclic STOP $\rightarrow$ | WUF0_Ax, $x = 0$ to 2 | Internal OSC            | RESET vector of code        |  |

|          | Cyclic RUN                | WUF0_ly, y = 1        | Clock (200 MHz          | flash                       |  |

|          |                           |                       | or 240 kHz)             |                             |  |

| Wake-Up  | $DeepSTOP \rightarrow$    | WUF1_Ax, $x = 0$ to 2 | Internal OSC            | RESET vector of retention   |  |

| Factor 1 | Cyclic RUN                |                       | Clock (200 MHz          | RAM                         |  |

|          |                           |                       | or 240 kHz)             |                             |  |

|          | Cyclic STOP $\rightarrow$ | WUF1_Ax, $x = 0$ to 2 | Internal OSC            | Next address before         |  |

|          | Cyclic RUN                | WUF1_ly, y = 1        | Clock (200 MHz          | Cyclic STOP mode was        |  |

|          |                           |                       | or 240 kHz)             | entered or interrupt vector |  |

The wake-up events are controlled by the following standby controller registers:

• Wake-up factor registers: WUF0\_A0, WUF0\_A1, WUF0\_A2, WUF0\_I0, WUF0\_I1, WUF0\_I2, WUF0\_I3 WUF1\_A0, WUF1\_A1, WUF1\_A2, WUF1\_I0, WUF1\_I1, WUF1\_I2, WUF1\_I3

Upon occurrence of an effective wake-up factor, the associated wake-up factor flag is set to 1. By checking these registers and their flags, it is possible to identify the wake-up factor.

Wake-up factor mask registers: WUFMSK0\_A0, WUFMSK0\_A1, WUFMSK0\_A2, WUFMSK0\_I0, WUFMSK0\_I1, WUFMSK0\_I2, WUFMSK0\_I3, WUFMSK1\_A0, WUFMSK1\_A1, WUFMSK1\_A2, WUFMSK1\_I0, WUFMSK1\_I1, WUFMSK1\_I2, WUFMSK1\_I3

Each bit of these registers is assigned to a certain wake-up factor. Wake-up by this factor is enabled if its mask bit is set to 0. Wake-up factors assigned to both wake-up factor 0 and 1 should not be enabled at the same time.

Wake-up factor clear registers: WUFC0\_A0, WUFC0\_A1, WUFC0\_A2, WUFC0\_I0, WUFC0\_I1, WUFC0\_I2, WUFC0\_I3, WUFC1\_A0, WUFC1\_A1, WUFC1\_A2, WUFC1\_I0, WUFC1\_I1, WUFC1\_I2, WUFC1\_I3

By setting the applicable bits in these registers to 1, the wake-up factor bit (WUFny) in the wake-up factor registers (WUF0\_A0, WUF0\_A1, WUF0\_A2, WUF0\_I0, WUF0\_I1, WUF0\_I2, WUF0\_I3, WUF1\_A0, WUF1\_A1, WUF1\_A2, WUF1\_I0, WUF1\_I1, WUF1\_I2, WUF0\_I3) can be cleared.

Note: The wake-up factor flag in the wake-up factor registers only indicate the occurrence of wake-up factor. These flags do not indicate a transition from chip standby mode to normal operation mode.

Table 4-6 lists the assignment of the wake-up factors to the control register bits and status register bits.

| Wake-Up Factor | Module | Bit Assignment of       | STOP $\rightarrow$ | DeepSTOP                 | Cyclic STOP          | DeepSTOP             |

|----------------|--------|-------------------------|--------------------|--------------------------|----------------------|----------------------|

|                |        | Wake-Up Factor          | RUN                | $\rightarrow \text{RUN}$ | $\rightarrow$ Cyclic | $\rightarrow$ Cyclic |

|                |        | Registers <sup>*1</sup> |                    |                          | RUN <sup>*2</sup>    | RUN                  |

#### Table 4-6 Wake-Up Factors

# Low-Power Operations Application Note

| TNMI       | Port   | WUF0_A0    | [0]  | $\checkmark$ |              |              |              |

|------------|--------|------------|------|--------------|--------------|--------------|--------------|

| INTCLMATIO | CLMA0  | WUFMSK0_A0 | [1]  |              |              |              |              |

| INTCLMATI1 | CLMA1  | WUFC0_A0   | [2]  |              |              |              |              |

| INTCLMATI2 | CLMA3  | or         | [3]  |              | _            | _            | _            |

|            | CLMA15 | WUF1_A0    | [•]  |              |              |              |              |

| INTWDTBA   | WDTBA  | WUFMSK1_A0 | [5]  |              |              | $\checkmark$ |              |

| IRQ0       | Port   | WUFC1_A0   | [6]  |              |              | $\checkmark$ | $\checkmark$ |

| IRQ1       | Port   |            | [7]  |              |              | $\checkmark$ | $\checkmark$ |

| IRQ2       | Port   |            | [8]  |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ3       | Port   |            | [9]  |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ4       | Port   |            | [10] |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ5       | Port   |            | [11] |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ6       | Port   |            | [12] |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ7       | Port   |            | [13] |              |              | $\checkmark$ | $\checkmark$ |

| IRQ8       | Port   |            | [14] |              | $\checkmark$ | $\checkmark$ |              |

| IRQ9       | Port   | 1          | [15] | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ10      | Port   | 1          | [16] | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ11      | Port   | 1          | [17] | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ12      | Port   | 1          | [18] | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ13      | Port   |            | [19] |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ14      | Port   |            | [20] |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ15      | Port   |            | [21] |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ16      | Port   | WUF0_A1    | [0]  |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ17      | Port   | WUFMSK0_A1 | [1]  |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ18      | Port   | WUFC0_A1   | [2]  |              | $\checkmark$ | $\checkmark$ |              |

| IRQ19      | Port   | or         | [3]  |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ20      | Port   | WUF1_A1    | [4]  |              | $\checkmark$ | $\checkmark$ |              |

| IRQ21      | Port   | WUFMSK1_A1 | [5]  |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ22      | Port   | WUFC1_A1   | [6]  |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ23      | Port   |            | [7]  |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ24      | Port   |            | [8]  |              |              | $\checkmark$ |              |

| IRQ25      | Port   |            | [9]  |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ26      | Port   |            | [10] |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ27      | Port   |            | [11] |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ28      | Port   |            | [12] |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ29      | Port   |            | [13] |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ30      | Port   |            | [14] | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ31      | Port   |            | [15] | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ32      | Port   |            | [16] | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IRQ33      | Port   |            | [17] |              |              |              |              |

| IRQ34      | Port   |            | [18] |              |              |              |              |

| IRQ35      | Port   |            | [19] |              |              |              |              |

| IRQ36      | Port   |            | [20] |              |              |              |              |

| IRQ37      | Port   |            | [21] |              |              |              |              |

| IRQ38      | Port   |            | [22] |              |              | $\checkmark$ |              |

| IRQ39      | Port   |            | [23] |              |              | $\checkmark$ |              |

| IRQ40      | Port   |            | [24] |              |              | $\checkmark$ |              |

| IRQ41      | Port   |            | [25] |              |              | $\checkmark$ |              |

| IRQ42      | Port   |            | [26] |              |              | $\checkmark$ |              |

| IRQ43      | Port   |            | [27] |              |              | $\checkmark$ |              |

| WUTRG0     | LPS    | WUF0_A2    | [0]  |              |              | $\checkmark$ | $\checkmark$ |

# Low-Power Operations Application Note

| WUTRG1            | LPS     | WUFMSK0_A2 | [1]  |              |              |              |              |

|-------------------|---------|------------|------|--------------|--------------|--------------|--------------|

| INTDCUTDI         | JTAG    | WUFC0_A2   | [2]  | $\checkmark$ |              | $\checkmark$ |              |

| INTTAUJ2I0        | TAUJ2   | or         | [3]  | $\checkmark$ |              | $\checkmark$ |              |

| INTTAUJ2I1        | TAUJ2   | WUF1_A2    | [4]  | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |

| INTTAUJ2I2        | TAUJ2   | WUFMSK1_A2 | [5]  | $\checkmark$ |              | $\checkmark$ |              |

| INTTAUJ2I3        | TAUJ2   | WUFC1_A2   | [6]  | $\checkmark$ |              | $\checkmark$ |              |

| INTTAUJ3I0        | TAUJ3   |            | [7]  | $\checkmark$ |              | $\checkmark$ |              |

| INTTAUJ3I1        | TAUJ3   |            | [8]  | $\checkmark$ |              | $\checkmark$ |              |

| INTTAUJ3I2        | TAUJ3   |            | [9]  | $\checkmark$ |              | $\checkmark$ |              |

| INTTAUJ3I3        | TAUJ3   |            | [10] | $\checkmark$ |              | $\checkmark$ |              |

| INTRTCA01S        | RTCA    |            | [11] | $\checkmark$ |              | $\checkmark$ |              |