# **MOSFET**

パワーMOS FET アプリケーションノート R07AN0006JJ0110 (Previous: RJJ05G0003-1000) Rev.1.10 2022.12.5

# 要旨

本アプリケーションノートでは、データシートに記載された内容を中心に、MOSFET の特性や基本的な使用方法について説明します。

## 目次

| 1. | MOS                  | FET とは                              | . 2    |

|----|----------------------|-------------------------------------|--------|

| 2. | 用語                   | <b>吾説明</b>                          | . 3    |

|    | 2. 1<br>2. 2         | 絶対最大定格                              |        |

| 3. | 電気                   | 贰的特性                                | . 5    |

|    | 3. 1<br>3. 2<br>3. 3 | 定格電流、許容損失                           | 5<br>6 |

|    | 3. 4                 | 容量特性                                |        |

|    | 3. 4.<br>3. 4.       | 2 ゲートチャージ特性                         | 8      |

|    | 3. 4.                |                                     |        |

|    | 3. 5<br>3. 6         | スイッチング特性          内蔵ダイオード特性         | 11     |

|    | 3. 6.<br>3. 6.       | 2 内蔵ダイオードの逆回復特性                     | 12     |

|    | 3. 6.<br>3. 7        | アバランシェ動作                            | 14     |

|    | 3. 7.<br>3. 7.       | .2 アバランシェ破壊のモードⅡ《エネルギー破壊》           | 15     |

|    | 3.8                  | 非絶縁型同期整流コンバータ Low Side 側のセルフターンオン現象 | 17     |

| 4  | MOS                  | FFT の損失                             | 18     |

### 1. MOSFET とは

MOSFET (Metal Oxide Semiconductor Field Effect Transistor)は、日本語では電界効果トランジスタと言われ、バイポーラトランジスタと比べて高速スイッチング、低損失が特徴のデバイスです。

MOSFET は、その高速性、低損失特性を活かし、電子機器、FA機器、自動車の各種電源回路(DC-DC コンバータなど)やモーター駆動用インバータなど民生/産業用分野から車載機器に至るまで幅広い応用分野で使用されています。

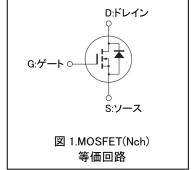

図1に MOSFET (Nch) 等価回路を、図2に MOSFET (Nch) とバイポーラトランジスタ (NPN型) の構造、特長の比較を示します。

NPN 型バイポーラトランジスタは電流制御型のデバイスで不純物濃度が高いN型半導体のエミッタとP型半導体のベースをN型半導体のコレクタで挟んだ構造となっています。ベース-エミッタのPN接合部に順方向電圧を印加すると、エミッタから注入される電子とベース層から注入される正孔が再結合する事でベース-エミッタ間で電流が流れます。しかし、ベース層から注入される正孔よりも不純物濃度の高いエミッタから注入される電子の数が多い

ため、正孔と再結合しなかった多数の電子はベース層を通り抜け、正の電圧が印加されているコレクタまで拡散し、その結果、コレクターエミッタ間に電流が流れます。

一方、MOSFET は金属(Metal)-酸化膜(Oxide)-半導体(Semiconductor)の MOS 構造からなる電圧制御型のデバイスです。具体的にはN型半導体のドレインとN型半導体のソースとの間にP型半導体があり、このP型半導体の上に絶縁膜(シリコン酸化膜)で絶縁されたゲート電極が配置される構造となっています。ゲート電極にプラス電荷を印加するとP型半導体内にある電子が引き寄せられる事でN型半導体の特性を持つ反転層が現れドレイン-ソース間がN型半導体で繋がる形となり、ドレイン-ソース間にプラスの電圧を印加する事でドレインからソースに電流が流れます。

また、バイポーラトランジスタは電子と正孔をキャリアとして電流を流しますが MOSFET は電子のみをキャリアとして電流を流す事から、より高速なスイッチング動作が可能となります。

## 2. 用語説明

### 2.1 絶対最大定格

絶対最大定格とは MOSFET を安全にご使用頂くために規定された定格値です。

この絶対最大定格を瞬時でも超えると劣化や破壊に至る可能性がありますので必ず最大定格以内でご使用下さい。

尚、絶対最大定格は、特に指定のない限り Ta=25℃の値です。

表 1. 絶対最大定格

| 項目          | 記 号                   | 定義                                     |

|-------------|-----------------------|----------------------------------------|

| ドレイン・ソース電圧  | $V_{ m DSS}$          | ゲート・ソース間を短絡し、ドレイン・ソース間に印加できる電圧の<br>最大値 |

| ゲート・ソース電圧   | $V_{GSS}$             | ドレイン・ソース間を短絡し、ゲート・ソース間に印加できる電圧の<br>最大値 |

| ドレイン電流      | $I_D$                 | 許容されるドレイン電流の最大値                        |

| せん頭ドレイン電流   | $I_{\text{D(pulse)}}$ | パルス動作時に許容されるドレイン電流の最大値                 |

| 逆ドレイン電流     | ${ m I}_{ m DR}$      | 寄生ダイオードに許容される電流の最大値                    |

| アバランシェ電流    | ${ m I}_{ m AP}$      | 単発のアバランシェ動作時に許容されるドレイン電流の最大値           |

| アバランシェエネルギー | E <sub>AS</sub>       | 単発のアバランシェ動作時に許容されるエネルギーの最大値            |

| 許容チャネル損失    | P <sub>ch</sub>       | ドレイン・ソース間で発生する電力損失で許容される最大値            |

| チャネル温度      | $T_{ m ch}$           | 許容されるチャネル温度の最大値                        |

| 保存温度        | $T_{ m stg}$          | 電力を印加しない状態で保存できる温度範囲                   |

### 注記事項

本製品の使用条件(使用温度/電流/電圧等)が絶対最大定格以内であっても、高負荷(高温および大電流/高電圧印加、多大な温度変化等)で連続して使用される場合は、信頼性が著しく低下するおそれがあります。弊社半導体信頼性ハンドブック(取り扱い上のご注意とお願いおよびディレーティングの考え方と方法)および個別信頼性情報(信頼性試験レポート、推定故障率等)をご確認の上、適切な信頼性設計をお願いします。

## 2.2 電気的特性

表 2 に MOSFET の電気的特性の意味を示します。 尚、電気的特性は、特に指定のない限り Ta=25℃の値です。

### 表 2. 電気的特性

| 項目              | 記号                   | 定 義                                                                          |

|-----------------|----------------------|------------------------------------------------------------------------------|

| ドレイン・ソース破壊電圧    | $V_{(BR)\; DSS}$     | ゲート・ソース間を短絡し、指定のドレイン電流におけるドレイン・<br>ソース間電圧                                    |

| ドレイン遮断電流        | $I_{ m DSS}$         | ゲート・ソース間を短絡し、ドレイン・ソース間に指定の電圧を印<br>加した時のドレイン電流                                |

| ゲート遮断電流         | $I_{GSS}$            | ドレイン・ソース間を短絡し、ゲート・ソース間に指定の電圧を印<br>加した時のゲート電流                                 |

| ゲート・ソース間 しきい値電圧 | $V_{\text{GS(off)}}$ | 指定のドレイン・ソース間電圧を印加し、指定のドレイン電流となるゲート・ソース間電圧                                    |

| ドレイン・ソース間オン抵抗   | R <sub>DS(on)</sub>  | 指定のゲート・ソース間電圧を印加し、指定のドレイン電流におけるドレイン・ソース間抵抗                                   |

| 入力容量            | C <sub>iss</sub>     | 指定のゲート・ソース間電圧、指定のドレイン・ソース間電圧及び<br>指定の周波数における入力容量                             |

| 出力容量            | $C_{oss}$            | 指定のゲート・ソース間電圧、指定のドレイン・ソース間電圧及び<br>指定の周波数における出力容量                             |

| 帰還容量            | $C_{rss}$            | 指定のゲート・ソース間電圧、指定のドレイン・ソース間電圧及び<br>指定の周波数における帰還容量                             |

| ゲート電荷量          | $Q_{\rm g}$          | ゲート・ソース間を指定の電圧とするために必要な電荷量                                                   |

| ゲート・ソース間電荷量     | $Q_{gs}$             | ゲート・ソース間電圧がしきい値電圧となるまでに必要な電荷量                                                |

| ゲート・ドレイン間電荷量    | $Q_{\mathrm{gd}}$    | ゲート・ドレイン間のミラー効果によって増加する電荷量                                                   |

| ターンオン遅延時間       | $t_{d(on)}$          | ゲート・ソース間電圧が所定の電圧まで上昇した時点からドレイン・ソース間電圧が所定の電圧に下降するまでの時間<br>(3.5 項 スイッチング特性 参照) |

| 上昇時間            | t <sub>r</sub>       | ドレイン・ソース間電圧が所定の電圧から所定の電圧まで下降する<br>時間 (3.5 項 スイッチング特性 参照)                     |

| ターンオフ遅延時間       | $t_{d(off)}$         | ゲート・ソース間電圧が所定の電圧まで下降した時点からドレイン・ソース間電圧が所定の電圧に上昇するまでの時間<br>(3.5 項 スイッチング特性 参照) |

| 下降時間            | $t_{f}$              | ドレイン・ソース間電圧が所定の電圧から所定の電圧まで上昇する<br>時間(3.5 項 スイッチング特性 参照)                      |

| 内蔵ダイオード順電圧      | $V_{ m DF}$          | 寄生ダイオードの順方向に指定の電流が流れるときのソース・ドレ<br>イン間電圧                                      |

| 内蔵ダイオード逆回復時間    | t <sub>rr</sub>      | 寄生ダイオードに逆回復電流が流れている期間における所定の時間(3.6項内蔵ダイオード特性参照)                              |

| 内蔵ダイオード逆回復電荷量   | Qrr                  | 寄生ダイオードに逆回復電流が流れている期間における所定の時間の電荷量(3.6項内蔵ダイオード特性参照)                          |

#### 電気的特性 3.

#### 3.1 定格電流、許容損失

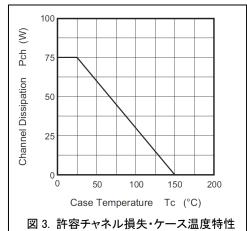

図3は許容チャネル損失とケース温度の関係を示した例に なり

ます。

一般的に許容チャネル損失 Pch はケース温度 Tc=25℃のと きの値を定格としており、ケース温度の上昇に伴い許容チャ ネル損失は制限されます。T<sub>c</sub>=25℃以上のときの許容チャネル 損失は次の式から求められます。

$$Pch = \frac{(Tchmax - Tc)}{\theta ch - c}$$

Tch max: 絶対最大定格 Tch

*Tc*: ケース温度

$\Theta$ ch-c: チャネル・ケース間熱抵抗

(例: 200V/20A/0.1 Ω typ)

#### 3.2 安全動作領域

安全動作領域は、個別のデータシートにてご確認下さい。

尚、安全動作領域は当社指定の条件下における設計値である事に注意して下さい。

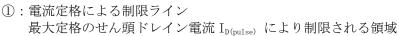

図4に安全動作領域(SOA)を示します。

SOA 制限領域は、下記の5つの領域に区分されます。

- ②:オン抵抗による制限ライン 理論的にオン抵抗 RDS (on) max により制限される領域

- ③:許容損失による制限ライン 許容チャネル損失 Pch により制限される領域で、3.1項 許容チャネル損失の計算式により算出されます。

- 二次降伏ラインは製品により有るものと無いものがあります。

- 二次降伏ラインのある製品は安全動作領域が狭くなるため注意が必要です。

尚、二次降伏ラインは3.1項 許容チャネル損失の計算式を適用できません。

⑤:電圧定格による制限ライン 最大定格のドレイン・ソース電圧 V<sub>DSS</sub> で制限される領域

### 3.3 静特性

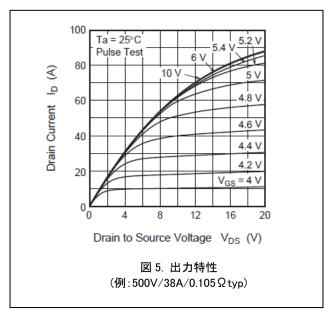

図5に出力特性の例を示します。

出力特性は、任意のゲート電圧条件において、ドレイン電流を流している時のドレイン・ソース間電圧を示しています。

また、このドレイン・ソース間電圧はゲート電圧やケース温度により変化しますので設計の際には配慮が必要です。

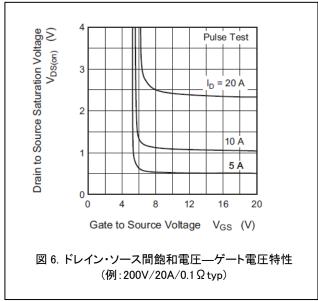

図6にドレイン・ソース間飽和電圧-ゲート電圧特性の例を示します。

ドレイン・ソース間飽和電圧 VDS (on) は、ゲート・ソース電圧 VGS が増加すると小さくなり、

且つ VDS (on) の変化が小さくなります。この様な VDS (on) が低く飽和する領域の VGS で使用する事が必要です。一方、VGS が小さい領域では VDS (on) が高く損失増加に繋がる事から、この領域で使用される事は推奨できません。

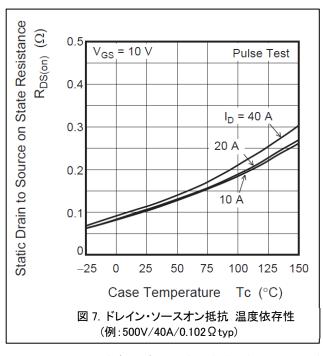

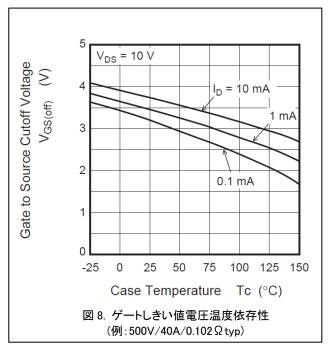

図 7,8 にドレイン・ソースオン抵抗とゲートしきい値電圧の温度依存性の例を示します。

ドレイン・ソースオン抵抗は正の温度依存性があるため、MOSFET 動作によって発熱すると電流を流しにくくなり、並列動作時に電流集中を起こしにくい特性があります。これに対しゲートしきい値電圧は負の温度依存性があるため、高温時にしきい値電圧が下がってしまいノイズによる誤動作を起こしやすくなる可能性や、低温時にしきい値電圧が上がってしまい MOSFET が十分にオンできなくなる可能性があります。このため設計の際にはこれら特性も配慮した検証が必要です。

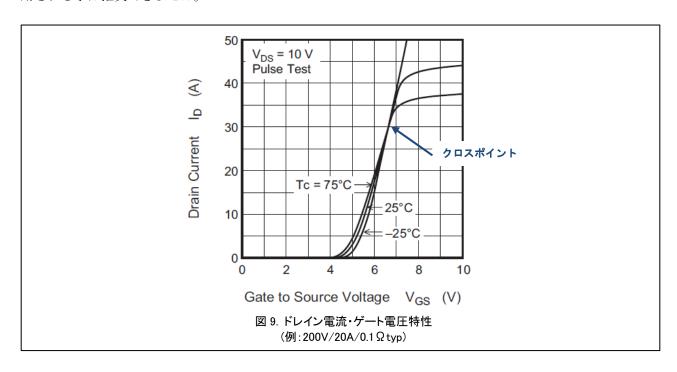

図9にドレイン電流・ゲート電圧特性の例を示します。

ドレイン電流・ゲート電圧特性には温度依存性があり、ドレイン電流はクロスポイントを中心にゲート電圧 が低い領域では正の温度係数、ゲート電圧が高い領域では負の温度係数となります。

パワーデバイスは動作中に発熱するため、並列使用の際にはドレイン電流のバランスが取れる負の温度係数領域でご使用ください。また、VGS が低い領域では VDS (on) が高く損失増加に繋がる事から、この領域で使用される事は推奨できません。

### 3.4 容量特性

#### 3.4.1 Ciss, Coss, Crss

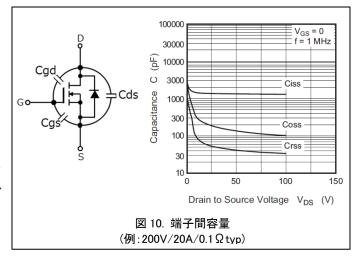

図 10 に端子間容量並びに、容量対ドレイン・ソース電圧特性の例を示します。

入力容量 Ciss、出力容量 Coss、帰還容量 Crss は、

次のような関係になります。

Ciss = Cgs + Cgd Coss = Cds + Cgd Crss = Cgd ただし、

Cgs: ゲート・ソース間容量Cds: ドレイン・ソース間容量Cgd: ゲート・ドレイン間容量

測定条件は、ドレイン・ソース間電圧 VDS、 ゲート・ソース間電圧 VGS、周波数 f を規定し ています。尚、各容量値への温度による影響は、 ほとんどありません。

## 3.4.2 ゲートチャージ特性

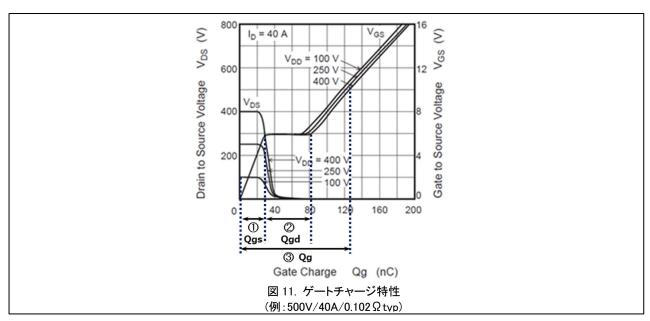

図 11 にゲートチャージ特性の例を示します。

MOSFET のゲートチャージ特性は、ドライブ電流、ドライブ損失を決めるパラメータです。図 11 の特性カーブを①~③の部分に分け、それらの期間について、動作を説明します。

#### <期間(1)>

ドレイン電流を流し始めるしきい値電圧までゲート電圧を上昇させます。VGS=0V から上昇している部分が、ゲート・ソース間の容量 Cgs を充電している部分です。

#### <期間②>

期間①から飽和領域に移行する期間で、ドレイン・ソース間電圧が変化しゲートードレイン容量 Cgd が充電されます。この期間はミラー効果により見かけ上の容量が大きくなるため VGS が一定となりますが、MOSFET が完全に ON 状態になり、VDS の変化がなくなるとともにミラー効果もなくなります。

#### <期間③>

完全に飽和状態になっており、VDS は変化しません。 時間と共に、VGS 電圧は上昇します。

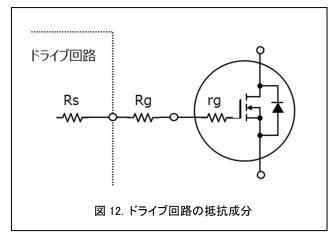

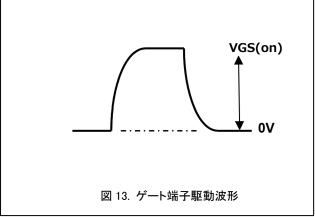

### 3.4.3 ゲートドライブ電流の決め方

このゲートドライブ電流は、ゲートシリーズ抵抗 Rg、ドライブ回路の信号源抵抗 Rs、素子内部抵抗 rg と、ドライブ電圧 VGS (m) で決定され以下の式で表されます。

$$I_{G(peak)} = \frac{V_{GS(on)}}{Rg + Rs + rg}$$

従って、ドライブ回路の出力段には  $I_{G(peak)}$  以上の電流駆動能力を持たせるよう設計する必要があります。なお、実際のピーク電流は、ドライブ回路の遅れや、ドライブ回路から MOSFET チップのゲートパットまでの配線インダクタンス等によるゲート電流の  $d_{IG}/d_{t}$  の立ち上がり遅れ等により、計算値より小さくなる傾向があります。

また、スイッチング動作におけるスイッチング損失、サージ電圧は Rg に依存します。 スイッチング動作時のサージ電圧は、Rg の値を大きくすることにより抑制されますが、 あまり大きくするとスイッチング損失の増大をまねく事から、これを考慮して最適な Rg を選定する 必要があります。

### 3.4.4 ドライブ損失の算出

ドライブ回路の発生損失が全てこれらの抵抗成分で消費される場合、ドライブ損失は次式で表されます。 (f: スイッチング周波数)

$$P_{(Drive\ Loss)} = V_{GS(on)} \times Qg \times f$$

### 3.5 スイッチング特性

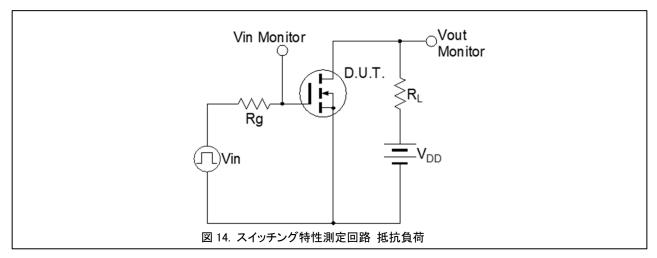

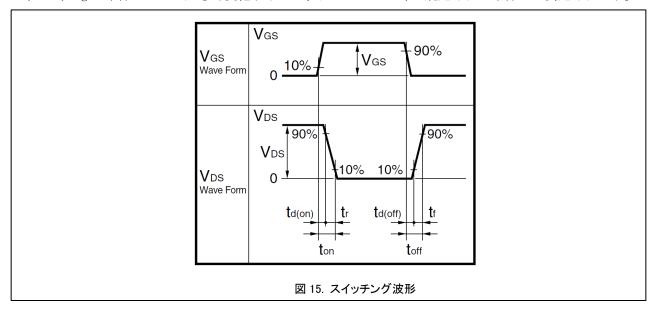

MOSFET はスイッチング素子のため、スイッチング速度(ターンオン時間、ターンオフ時間)は効率 (損失)を左右する重要なパラメータの一つです。図14に抵抗負荷スイッチング測定回路を示します。

スイッチング時間は図15に示される4つの期間に分割して測定します。またそれらの時間はTch, ID, VDS, VGS, Rgの条件によって大きく変化するため、データシート等に規定された条件にて測定されます。

#### t<sub>d(on)</sub> (ターンオン遅延時間)

ゲート・ソース間電圧が10%まで上昇し、ドレイン・ソース間電圧が90%に下降するまでの時間

#### tr (立ち上り時間)

ドレイン・ソース間電圧が90%から10%に下降するまでの時間

### t<sub>d(off)</sub> (ターンオフ遅延時間)

ゲート・ソース間電圧が90%まで下降し、ドレイン・ソース間電圧が10%に上昇するまでの時間

#### t<sub>f</sub> (立ち下り時間)

ドレイン・ソース間電圧が 10%から 90%に上昇するまでの時間

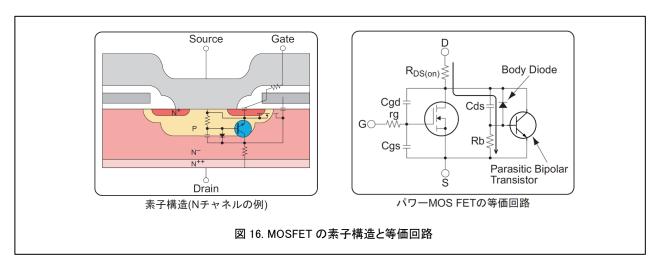

## 3.6 内蔵ダイオード特性

図 16 に MOSFET の構造と等価回路を示します。この図に示すように内蔵ダイオードは、構造上ソース・ドレイン間に形成されており、寄生ダイオードまたはボディーダイオードとも言われています。寄生ダイオードはモータコントロール用インバータ回路においてフリーホイールダイオードとして回生電流を流すために使用される事があります。

こうした用途においては回生電流を流し込んだ直後に逆電圧が印加されるような場合、回路、動作条件により MOSFET が破壊することがありますので注意が必要です。

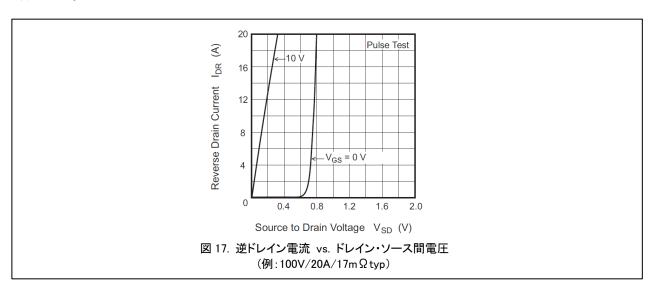

#### 3.6.1 内蔵ダイオードの順方向特性

図 17 に逆ドレイン電流対ソース・ドレイン電圧特性の例を示します。このダイオードは一般的な整流ダイオードに劣らない特性を有しており、モータ駆動用途などのブリッジ回路、PWM アンプの出力段などに使用する場合、外付の転流ダイオードが省略できる場合があります。

また、VGS を正にバイアスすることによりチャネルを形成すると電流は両方向同じように流れ、小電流領域では  $IDR \times Ron$  の直線となるので通常のダイオードより VF が小さくなり、用途によってはその優位性を発揮します。

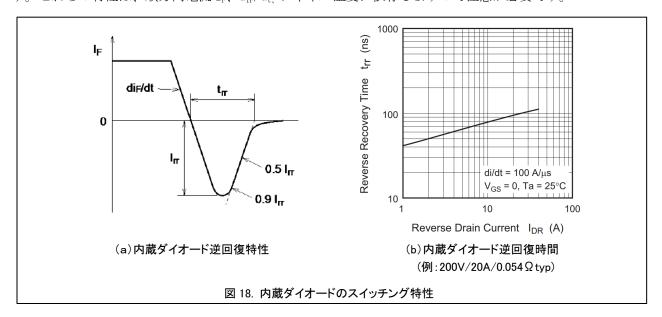

### 3.6.2 内蔵ダイオードの逆回復特性

ダイオードに順方向電流を流している状態から逆素子状態へ切り替わるとき、蓄積された少数キャリアが 放出されます。この少数キャリアを放出し終えるまでの時間が逆回復時間 trr と呼ばれ、その時の電流を逆 回復電流 Irr、それらの積分値を逆回復電荷量 Qrr と呼びます。

$$Qrr = \frac{1}{2}Irr \times trr$$

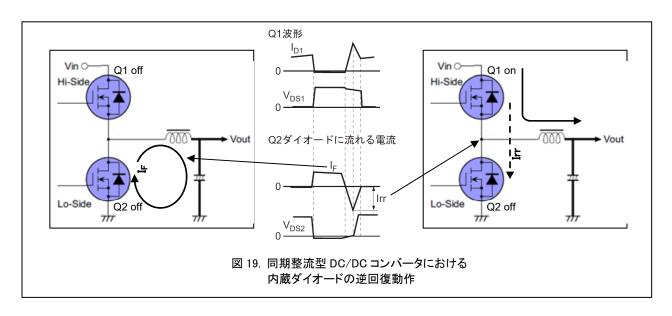

例えば同期整流回路では、ハイサイド MOSFET がターンオフし、ローサイド MOSFET がターンオフからターンオンするまでの間にデットタイムを設けますが、その間に trr、Irr、Qrr は生じています。(図 19)

$t_{rr}$ 期間は等価的に短絡状態となりますので、大きな損失を伴います。またスイッチング動作時には動作周波数の制約になるため、一般的には  $t_{rr}$ が早く、 $I_{rr}$ が小さい( $Q_{rr}$ が小さい)ことが望ましいとされています。これらの特性は、順方向電流  $I_{F}$ 、 $d_{iF}/d_{t}$ 、チャネル温度に依存しますので注意が必要です。

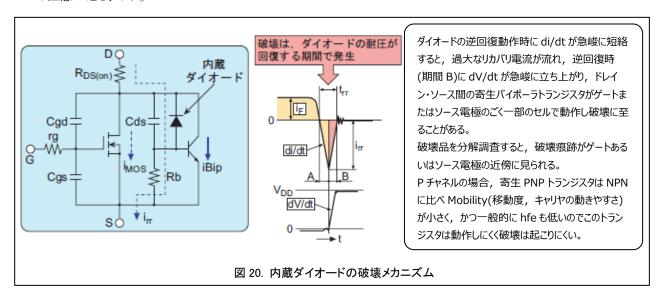

### 3.6.3 内蔵ダイオードの破壊のメカニズム

図20に内蔵ダイオードの破壊メカニズムを示します。

現在、内蔵ダイオード破壊耐量はかなり改善され、寄生バイポーラ TRS が動作 しにくいように構造的に対策が施されているため、通常の使用状態では破壊の問題はほとんど 起こりません。

但し、フリーホイールダイオードとして使用するなど内蔵ダイオードへ順方向電流 IF を流し込んだ直後に逆電圧が印加されるような場合、回路、動作条件により MOSFET が破壊することがありますので注意が必要です。

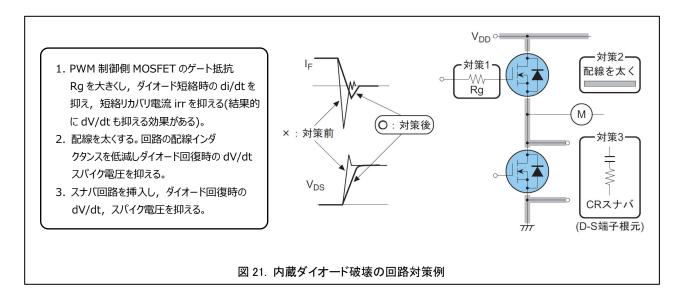

図 21 に内蔵ダイオード破壊の回路対策例(使用上の注意)を示します。

### 3.7 アバランシェ動作

アバランシェ動作とは、誘電負荷でのスイッチング動作オフ時に発生するフライバック電圧や、リーケージインダクタンスによるスパイク電圧が MOSFET のドレイン定格電圧を超えブレークダウン領域に入る事でドレイン-ソース間に電流(アバランシェ電流)が流れる間の動作を指します。

MOSFET には単発もしくは繰り返しのアバランシェ動作規格を持つ製品がありますが、 "繰り返し"の 意味は例えば電源起動時など過渡的に連続して入るサージ電圧などを指しており、定常的に定格電圧を 超える動作は対象外となりますので注意が必要です。

アバランシェ動作による MOSFET の破壊モードは以下の3つです。

- 1. 電流破壊モード

- 2. エネルギ破壊モード

- 3. dV/dt 破壊

以下にそれぞれの破壊モードについて説明します。

#### 3.7.1 アバランシェ破壊のモード I 《電流破壊》

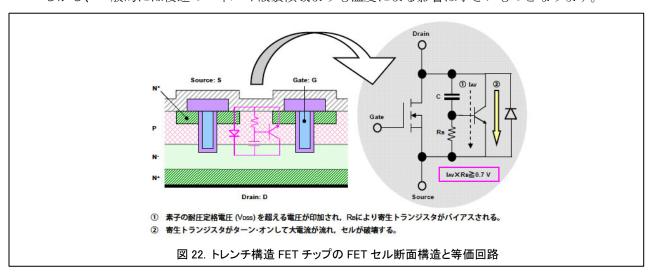

MOSFET は、多数の小さな FET セルの集合体で形成(多数の FET セルが並列に接続)されています。 特に 250 V以下の低電圧系品種では、素子のオン抵抗を低減させるため、個々の FET セルを微細化し、 表面に溝(トレンチ)を形成してその中にゲートを埋め込む(FET セル面積を縮小する)構造を用いて 性能向上を図っています。

図 22 にトレンチ構造 FET チップの FET セルの断面構造と等価回路を示します。図 22 の断面構造において、ソース電極に接続されている N+層、チャネルを形成する P 層、そしてドレイン側の N-層との間で NPN 型寄生トランジスタが構成されます。

このような構造の FET において、どのようにして電流破壊が生じるかについて下記に説明します。

- (1) ドレイン・ソース間に定格値を超える電圧が印加されると、ブレークダウン電流(アバランシェ電流: IAV)が流れます。

- (2) この電流 (IAV①) は、パルス的に寄生容量 (C) を経由して P層の抵抗成分 (RB) を通して ドレインからソースに流れます。

- (3) ここで IAV が大電流化し、RB 両端の電圧が寄生 NPN トランジスタの VBE オン電圧値以上になると、NPN トランジスタがターンオンします。

- (4) その結果、寄生トランジスタで増幅された過大電流(IAV②)がコレクタ側に流れ、大電流による発熱で寄生トランジスタ(= FET)が破壊されます。

電流破壊を回避するためには、セル構造の設計段階で寄生容量(C)、抵抗成分(RB)を極力小さくする工夫が必要です。また、破壊電流は温度による影響も受け、高温になればなるほど小さな電流で破壊に至ります。

しかし、一般的には後述のエネルギ破壊領域よりも温度による影響は小さいものとなります。

### 3.7.2 アバランシェ破壊のモードⅡ《エネルギー破壊》

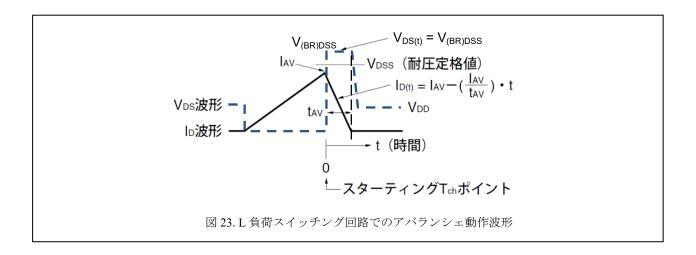

L負荷スイッチング回路でのアバランシェ動作波形(図23)では、アバランシェ動作時(tAV)に MOSFET のチャネル温度(Tch)が上昇します。これはアバランシェ電圧(V(BR)DSS)、アバランシェ電流 (IAV)のエネルギーが、MOSFETで消費されるためです。

エネルギー破壊モードとは、MOSFET にエネルギーが印加され、チャネル温度定格を超える事で破壊することを指します。このときの破壊エネルギー量(EAV)は、下記要件にて算出されます。

$$\mathsf{E}_{\mathsf{AV}} = \frac{1}{2} \, \mathsf{L} \cdot \mathsf{I}_{\mathsf{AV}}^2 \, \frac{\mathsf{V}_{(\mathsf{BR})\mathsf{DSS}}}{\mathsf{V}_{(\mathsf{BR})\mathsf{DSS}} - \mathsf{V}_{\mathsf{DD}}}$$

- ・L値(tAVに比例)

- ・L 負荷に流したピーク電流 IAV (L 負荷のオン時間に比例)

- ・FET のアバランシェ電圧 V(BR)DSS

また、エネルギー破壊は温度上昇に起因する破壊のため、アバランシェ動作に入る直前のチャネル温度(スターティング Tch)に直接的に影響されます。

備考 当社個別製品のデータシートで保証しているアバランシェ・エネルギー耐量 (EAS) は、全般的に スターティング Tch=25  $\mathbb C$  時の保証値です。

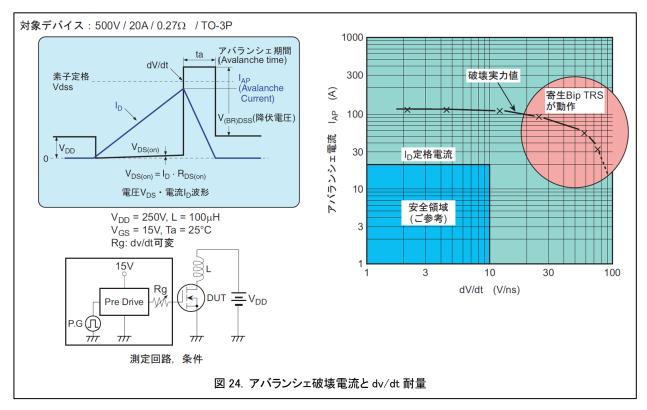

### 3.7.3 アバランシェ破壊のモードⅢ《dV/dt 破壊》

次に3つ目の要因であるアバランシェ破壊耐量と dV/dt の関係について述べます。図 24 にアバランシェ破壊電流 IAP の dV/dt 耐量依存性実測値を示します。MOSFET は図 16 の構造で前述したようにドレイン・ソース間に寄生バイポーラトランジスタが形成されています。 dV/dt を急峻にしていくと容量 Cds を通して過渡的な電流が流れ、このトランジスタがオンするため破壊耐量の低下をまねきます。図 24 の例では  $dV/dt \le 10V/ns$  が安全領域といえるでしょう。この値は個別素子により異なります。

### 3.8 非絶縁型同期整流コンバータ Low Side 側のセルフターンオン現象

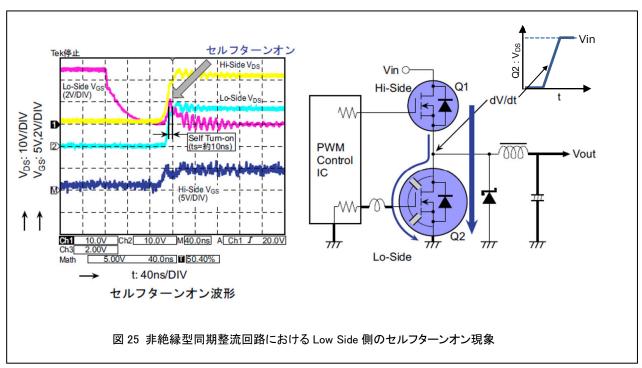

図 25 に非絶縁型同期整流回路における Low Side 側のセルフターンオン現象を示します。

この現象では、Low Side 側素子 Q2 がオフ状態から、High Side 側素子 Q1 がオンする切替えのタイミング のときに起こります。Q2 のドレイン・ソース電圧が  $V_{DS}$  = 0  $\to$  0 0  $\to$  0  $\to$

尚、このときの Low side 素子のゲート・ソース間電圧は以下の式で示されます。

$V_{GS}(Q2) = \{Cgd/(Cgs + Cgd)\} \times dV(t)$

この VGS(Q2)が VGS(off)を超えるとセルフターンオンを起こします。

これにより、Q1, Q2 が同時オンとなり過大な損失が発生し、素子の発熱・温度上昇を引き起こし、効率悪化の要因となります。

セルフターンオンの回路対策方法としては、一般的に下記の2点があげられます。

- 1. High Side 素子のターンオン時間のみを遅くする(dV/dt を抑える)。

- 2. Low Side 素子のゲート・ソース間に外付けに容量を挿入し Cgs と Cgd の容量比 Cgd/(Cgs + Cgd)を小さくすることによりセルフターンオンのマージンを向上させる。

### 4. MOSFET の損失

MOSFET が定格内動作であるかの判断を行う際、電圧や電流は測定頂く事で確認できますが、チャネル温度の確認は困難です。

ここでは動作波形とデバイスのケース温度 Tc からチャネル温度 Tch を算出する手順を説明します。 尚、ここで算出されるチャネル温度 Tch は推定値になります。

#### (1)チャネル温度算出の手順

同じ動作波形が繰り返し入力される場合のチャネル温度の算出手順を示します。

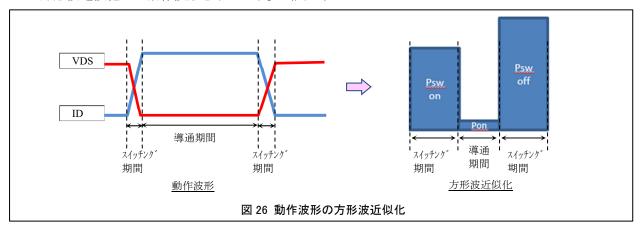

#### ①動作波形の方形波近似化

ドレイン電流 ID 及びドレイン-ソース間電圧 VDS の動作波形を MOSFET のスイッチング 動作期間と導通期間に区分し、各期間の損失を ID 及び VDS の波形の状態に合わせて計算し、 方形波近似化した動作波形を求めます。(図 26)

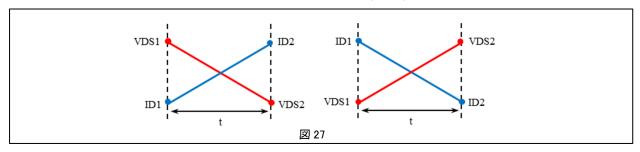

(a)VDS と ID の波形がクロス(上昇×下降)する場合(図 27)は下記式を用います。

$P=1/6 \times \{(2 \times ID1 \times VDS1)+(2 \times ID2 \times VDS2)+(ID1 \times VDS2)+(ID2 \times VDS1)\}$

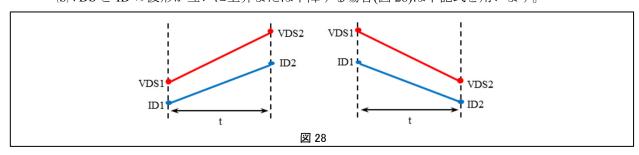

(b)VDS と ID の波形が互いに上昇または下降する場合(図 28)は下記式を用います。

$P=[1/3 \times \{(VDS2-VDS1) \times (ID2-ID1)\} ]+[1/2 \times \{(ID1 \times VDS2)+(ID2 \times VDS1)\} ]$

(c)導通期間の損失はドレイン電流 ID とオン抵抗 RDS(on)から算出します。

$P=(ID)^2 \cdot RDS(on)$

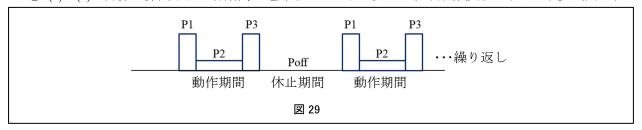

② (a)~(c)の計算で算出された各期間の電力をまとめると次のような動作波形になります。 (図 29)

③同じ動作波形が繰り返し入力される電力損失波形に対しては、動作波形の全期間平均値分から1~2 周期分の波形を合わせて計算する方法が算出も容易で精度が高く有効です。

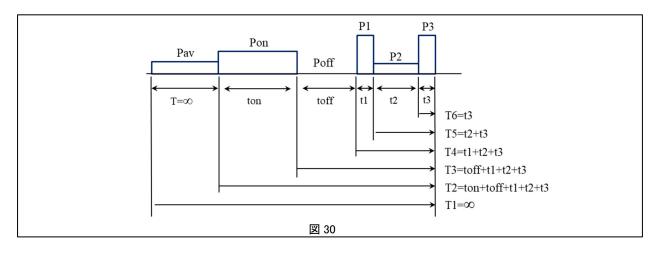

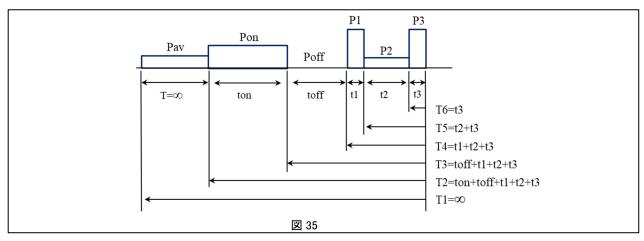

そのためには②で求めた動作波形から全期間の平均損失 Pav と 1 周期の中で休止期間を除いた動作期間の平均損失 Pon を算出し、図 30 の様な方形波近似波形を作成します。下記はその具体例になります。

動作期間の平均損失 Pon:損失波形1周期(P1~P3)の平均損失とし次の様に算出します。

Pon =(P1・t1+P2・t2+P3・t3)/T4 尚、T4 =t1+t2+t3 とします。

全期間平均損失 Pav: 損失波形 1 周期(P1~P3)及び休止期間(Poff)の平均値とし次の様に算出します。

チャネル温度上昇 Δ Tch: 全期間平均損失 Pav、動作期間の平均損失 Pon、動作期間 1 周期分の損失と 熱抵抗を用いて次の計算式で算出します。

$\Delta$  Tch=Pav·Rth(T1)+(Pon-Pav)·rth(T2)+(Poff-Pon)·rth(T3)+(P1-Poff)·rth(T4) +(P2-P1)·rth(T5)+(P3-P2)·rth(T6)··· $\pm$ -1

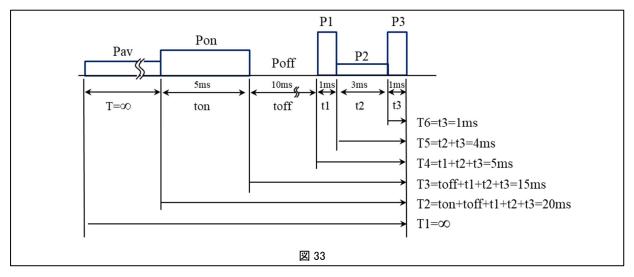

尚、図30の通りT1~T6は次の通りとします。

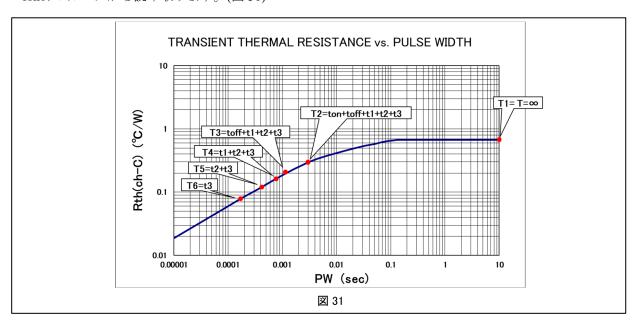

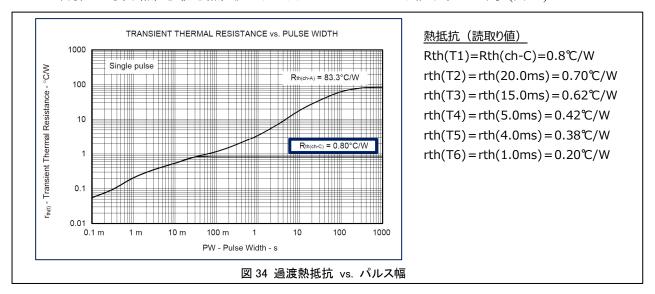

T1= T=∞ (飽和熱抵抗) T2=ton+toff+t1+t2+t3 T3=toff+t1+t2+t3 T4=t1+t2+t3 T5=t2+t3 T6=t3 ④チャネル温度上昇  $\Delta$  Tch の計算に必要なチャネルケース熱抵抗 Rth(ch-C)は熱抵抗グラフ内 1shot のカーブから読み取ります。(図 31)

⑤ご使用条件におけるデバイスのケース温度 Tc とチャネル温度上昇  $\Delta Tch$  によりチャネル温度 Tch が算出されます。

$Tch=Tc+\Delta Tch$

### [計算事例]

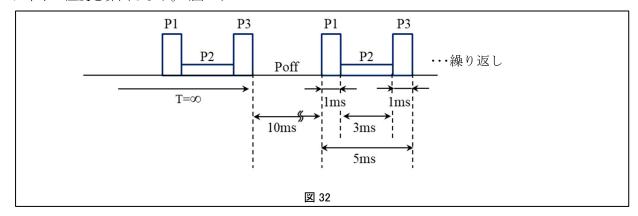

MOSFET のケース温度 Tc=60℃、方形波近似波形の P1=P3=25W、P2=10W、パルス幅が下記のときのチャネル温度を算出します。(図 32)

上記は同じ動作波形が繰り返し入力される電力損失波形ですので全期間平均値分に1周期分の 波形を合わせて計算します。(図 33)

動作期間の平均損失 Pon(P1~P3)を算出します。

Pon =

$$(P1 \cdot t1 + P2 \cdot t2 + P3 \cdot t3)/T4 = (25W \cdot 1ms + 10W \cdot 3ms + 25W \cdot 1ms)/5ms$$

= $16W$

全期間平均損失 Pav (P1~P3 及び Poff)を算出します。

Pav=

$$(Pon \cdot T4)/T3 = (16W \cdot 5ms)/15ms$$

=5.3W

チャネル温度上昇 $\Delta$  Tch の計算は下記の通りです。

$$\Delta$$

Tch=Pav·Rth(T1)+(Pon-Pav)·rth(T2)+(Poff-Pon)·rth(T3)+(P1-Poff)·rth(T4) +(P2-P1)·rth(T5)+(P3-P2)·rth(T6) …式-1

ここで計算に必要な熱抵抗値を熱抵抗グラフ内 1shot のカーブから読み取ります。(図 34)

上記で求めた損失及び熱抵抗から次式にて∠Tch を算出します。

Δ Tch=Pav·Rth(T1)+(Pon-Pav)·rth(T2)+(Poff-Pon)·rth(T3)+(P1-Poff)·rth(T4) +(P2-P1)·rth(T5)+(P3-P2)·rth(T6) =5.3W·0.8°C/W+(16W-5.3W)·0.70°C/W+(0-16W)·0.62°C/W+(25W-0)·0.42°C/W +(10W-25W)·0.38°C/W+(25W-10W)·0.2°C/W =4.2°C+7.5°C-9.9°C+10.5°C-5.7°C+3.0°C =9.6°C

ケース温度 Tc=60  $\mathbb{C}$  とチャネル温度上昇  $\Delta$  Tch によりチャネル温度 Tch が算出されます。

Tch=Tc +  $\Delta$  Tch =60°C+9.6°C  $\rightleftharpoons$ 70°C

尚、計算式(式-1)は熱抵抗でまとめた表記となっていますが他の資料では下記の様に電力でまとめた表記(式-2)で書かれることもあります。 これら2つの式はどちらを用いても同様の計算結果を得られます。

(参考に式-1 から式-2 への変換結果を記載します)

$\Delta$  Tch=Pav·{Rth(T1)-rth(T2)}+Pon·{rth(T2)-rth(T3)}+Poff·{rth(T3)-rth(T4)}+P1·{rth(T4)-rth(T5)}+P2·{rth(T5)-rth(T6)}+P3·rth(T6) ··· 式-2

```

[式-1 から式-2 への変換結果]

```

- - $= Pav \cdot Rth(T1) + Pon \cdot rth(T2) Pav \cdot rth(T2) + Poff \cdot rth(T3) Pon \cdot rth(T3) + P1 \cdot rth(T4) Poff \cdot rth(T4) + P2 \cdot rth(T5) P1 \cdot rth(T5) + P3 \cdot rth(T6) P2 \cdot rth(T6)$

- $= Pav \cdot Rth(T1) Pav \cdot rth(T2) + Pon \cdot rth(T2) Pon \cdot rth(T3) + Poff \cdot rth(T3) Poff \cdot rth(T4) \\ + P1 \cdot rth(T4) P1 \cdot rth(T5) + P2 \cdot rth(T5) P2 \cdot rth(T6) + P3 \cdot rth(T6)$

- $= Pav \cdot \{Rth(T1)-rth(T2)\} + Pon \cdot \{rth(T2)-rth(T3)\} + Poff \cdot \{rth(T3)-rth(T4)\} + P1 \cdot \{rth(T4)-rth(T5)\} + P2 \cdot \{rth(T5)-rth(T6)\} + P3 \cdot rth(T6) \cdots \overrightarrow{x} 2$

### ご注意書き

- 1. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。回路、ソフトウェアおよびこれらに関連する情報を使用する場合、お客様の責任において、お客様の機器・システムを設計ください。これらの使用に起因して生じた損害 (お客様または第三者いずれに生じた損害も含みます。以下同じです。) に関し、当社は、一切その責任を負いません。

- 2. 当社製品または本資料に記載された製品データ、図、表、プログラム、アルゴリズム、応用回路例等の情報の使用に起因して発生した第三者の特許権、著作権その他の知的財産権に対する侵害またはこれらに関する紛争について、当社は、何らの保証を行うものではなく、また責任を負うものではありません。

- 3. 当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 4. 当社製品を組み込んだ製品の輸出入、製造、販売、利用、配布その他の行為を行うにあたり、第三者保有の技術の利用に関するライセンスが必要となる場合、当該ライセンス取得の判断および取得はお客様の責任において行ってください。

- 5. 当社製品を、全部または一部を問わず、改造、改変、複製、リバースエンジニアリング、その他、不適切に使用しないでください。かかる改造、改変、複製、リバースエンジニアリング等により生じた損害に関し、当社は、一切その責任を負いません。

- 6. 当社は、当社製品の品質水準を「標準水準」および「高品質水準」に分類しており、各品質水準は、以下に示す用途に製品が使用されることを意図しております。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット等

高品質水準:輸送機器(自動車、電車、船舶等)、交通制御(信号)、大規模通信機器、金融端末基幹システム、各種安全制御装置等 当社製品は、データシート等により高信頼性、Harsh environment 向け製品と定義しているものを除き、直接生命・身体に危害を及ぼす可能性のある 機器・システム(生命維持装置、人体に埋め込み使用するもの等)、もしくは多大な物的損害を発生させるおそれのある機器・システム(宇宙機器 と、海底中継器、原子力制御システム、航空機制御システム、プラント基幹システム、軍事機器等)に使用されることを意図しておらず、これらの 用途に使用することは想定していません。たとえ、当社が想定していない用途に当社製品を使用したことにより損害が生じても、当社は一切その責 任を負いません。

- 7. あらゆる半導体製品は、外部攻撃からの安全性を 100%保証されているわけではありません。当社ハードウェア/ソフトウェア製品にはセキュリティ対策が組み込まれているものもありますが、これによって、当社は、セキュリティ脆弱性または侵害(当社製品または当社製品が使用されているシステムに対する不正アクセス・不正使用を含みますが、これに限りません。) から生じる責任を負うものではありません。当社は、当社製品または当社製品が使用されたあらゆるシステムが、不正な改変、攻撃、ウイルス、干渉、ハッキング、データの破壊または窃盗その他の不正な侵入行為(「脆弱性問題」といいます。) によって影響を受けないことを保証しません。当社は、脆弱性問題に起因しまたはこれに関連して生じた損害について、一切責任を負いません。また、法令において認められる限りにおいて、本資料および当社ハードウェア/ソフトウェア製品について、商品性および特定目的との合致に関する保証ならびに第三者の権利を侵害しないことの保証を含め、明示または黙示のいかなる保証も行いません。

- 8. 当社製品をご使用の際は、最新の製品情報(データシート、ユーザーズマニュアル、アプリケーションノート、信頼性ハンドブックに記載の「半導体デバイスの使用上の一般的な注意事項」等)をご確認の上、当社が指定する最大定格、動作電源電圧範囲、放熱特性、実装条件その他指定条件の範囲内でご使用ください。指定条件の範囲を超えて当社製品をご使用された場合の故障、誤動作の不具合および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めていますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は、データシート等において高信頼性、Harsh environment 向け製品と定義しているものを除き、耐放射線設計を行っておりません。仮に当社製品の故障または誤動作が生じた場合であっても、人身事故、火災事故その他社会的損害等を生じさせないよう、お客様の責任において、冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、お客様の機器・システムとしての出荷保証を行ってください。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様の機器・システムとしての安全検証をお客様の責任で行ってください。

- 10. 当社製品の環境適合性等の詳細につきましては、製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。かかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器・システムに使用することはできません。当社製品および技術を輸出、販売または移転等する場合は、「外国為替及び外国貿易法」その他日本国および適用される外国の輸出管理関連法規を遵守し、それらの定めるところに従い必要な手続きを行ってください。

- 12. お客様が当社製品を第三者に転売等される場合には、事前に当該第三者に対して、本ご注意書き記載の諸条件を通知する責任を負うものといたします

- 13. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを禁じます。

- 14. 本資料に記載されている内容または当社製品についてご不明な点がございましたら、当社の営業担当者までお問合せください。

- 注 1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社が直接的、間接的 に支配する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

(Rev.5.0-1 2020.10)

### 本社所在地

〒135-0061 東京都江東区豊洲 3-2-24 (豊洲フォレシア)

www.renesas.com

#### 商標について

ルネサスおよびルネサスロゴはルネサス エレクトロニクス株式会社の 商標です。すべての商標および登録商標は、それぞれの所有者に帰属 します。

#### お問合せ窓口

弊社の製品や技術、ドキュメントの最新情報、最寄の営業お問合せ窓口に関する情報などは、弊社ウェブサイトをご覧ください。

www.renesas.com/contact/