# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等) 交通用信号機器、防災・防犯装置、各種安全装置、生命維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# M66291 アプリーションノート

RJJ06F0003-0111Z Rev.1.11 2004.03.01

# 1. 資料概要

### 1.1. 概要

本資料(以降アプリケーションノートと記載)は、ルネサス製USB汎用ASSPデバイス M66291を制御するための応用技術資料です。

## 1.2. アプリケーションノートの特徴

アプリケーションノートは以下のような特徴を持っています。

- ・M66291 制御に関する手法を、記述例をあげて具体的に記載しています。

- ・M66291 を使用する場合の注意事項を記載しています。

- ・「ルネサス汎用 ASSP M66291/M66290A USB Sample Firmware 」とリンクしています。

- ・豊富な機能用途を具体的に記載しています。

なお、「ルネサス汎用ASSP M66290A/M66291 USB Firmware」は一部のUSB特殊信号の制御には対応していません。また、本資料はM66291の制御方法の一例です。お客様の応用に合わせて変更する必要があります。

## 1.3. 関連ドキュメント

[1] M66291GP/HP データシート

[http://www.renesas.com/jp/usb]

[2] ルネサス汎用 ASSP M66291/M66290A USB Sample Firmware

【Renesas よりユーザに配布】

[3] USB Specification Revsion 2.0

[http://www.usb.org/developers/docs/]

### 1.4. 凡例等

- (1) '\*'を付加した端子名は"L"アクティブを示します。"L"アクティブ/"H"アクティブ設定可能な端子についても、デフォルトが"L"アクティブの場合は'\*'を付加しています。

- (2) M66291 のレジスタ名称は、xxビット、xxレジスタ、のようにゴシックフォントを用いています。

- (3) 数値の記述方法は以下のとおりです。

- 十六進表記;00h、FFh など

- 十進表記:1、2、64、256 など

- 二進表記;'0000'、'0101'、'0'、'1'など

# 2. M66291 概要

#### 2.1. M66291 の特徴

M66291 は、制御 CPU を特定しない USB ASSP です。

制御 CPU のメモリマップ上に M66291 のレジスタマップをアサインし、セパレートバスで直接 M66921 のレジスタへのアクセスを行う方法で制御します。接続方法については、2.2 制御用 CPU との 接続例、及び、7 応用例を参照ください。

M66291の主な特徴は以下のとおりです。詳細はデータシートを参照ください。

#### <<USB機能に関する特徴>>

- ◆ USB Specification Rev. 2.0準拠

- ◆ USBトランシーバ回路内蔵

- ◆ Full Speed(12Mbps)転送に対応

- ◆ Vbus直結可能(5V耐圧入力)、D+信号プル アップ出力

- ◆オリジナルデザインの SIE(Serial Interface Engine)/DPLL (Digital Phase Lock Loop)による高品質USB信号

- ◆ ハードウエアによるデバイスステート/コ ントロール転送の状態(遷移タイミング) 管理により、エニュメレーションプログ ラム作成及びタイミング設計が容易

- ◆ 連続送受信モード(複数のトランザクシ ョンデータをFIFOにバッファリング)に より、CPU負荷軽減(ハイパフォーマン ス、スループット向上)

- ◆ USB全転送タイプに対応 (コントロール、バルク、アイソクロナス、 インタラプト)

- ◆エンドポイント用 FIFO バッファを 3KByte内蔵

new ♦ 最大7本のエンドポイント(EP0~6)を選

- ◆ エンドポイント毎(EP1~6)に以下の転送 条件を設定可能

- •データ転送タイプ (バルク転送、アイソクロナス転送、イン タラプト転送)

- •転送方向(IN/OUT)

- •FIFOバッファサイズ(最大1024Byte×2)

- ダブルバッファ構成

- •連続送受信(最大1024Byte×2のバッファ リング)

- •最大パケットサイズ

new ◆ SOF同期信号出力機能内蔵

#### <<制御CPUとの接続性等の特徴>>

アン切替え

new ◆ 4本のコンフィギュアブルFIFOポート

•エンドポイント番号の割り当て機能 new ●ビット幅(8ビット/16ビット)、エンディ

new •DMAインターフェースつきFIFOポー ト2本

- ◆ CPUへのUSB割り込み要因通知機能 •煩雑な要因解析を不要にする"割込みキ

- ューイング機能" new •最大2本のINT端子

- ◆ CPUとの柔軟な接続性 new •バス幅(8ビット/16ビット)選択可能

- •I/O電圧(2.7V-5.5V)

- •割り込み信号(INTO、INT1)、DMA制御 信号(Dreq0、Dreq1、Dack0、Dack1) の極性設定可能

- new •マルチワードDMA(バースト)可能

- ◆ 4種のクロック入力周波数に対応

- •6/12/24/48MHzクロック入力に対応 (IOVcc=2.7~3.6V時)

- •24/48MHzクロック入力に対応 (IOVcc=4.5~5.5V時)

- •発振バッファ、48MHz出力のPLL内蔵

- new ◆ コア電源 3.3V単一、I/O電源 3-5V

- ◆ 低消費電力;

- new 15mA(標準)(USB転送時) 10μA(標準)(クロック停止、USB切断時)

# <<用途>>>

- ◆プリンター、スキャナー

- ◆ディスプレイモニタ、マルチメディアス

- ★ デジタルカメラ、ターミナルアダプタ

- ◆ その他、Full Speed USB搭載のPC周辺 機器全般

#### <<パッケージ>>

M66291GP:48P6Q (LQFP) M66291HP:52PJV(VQFN)

new :M66290A からの追加/変更機能

図 2-1 M66291 の特徴

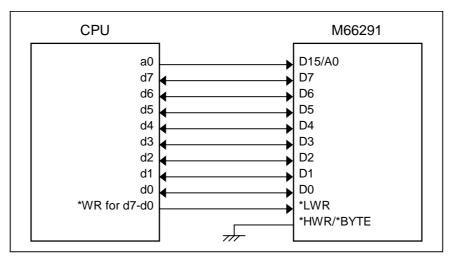

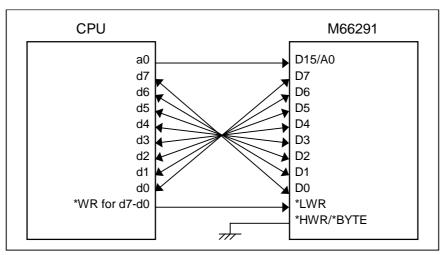

## 2.2. 制御用 CPU との接続例

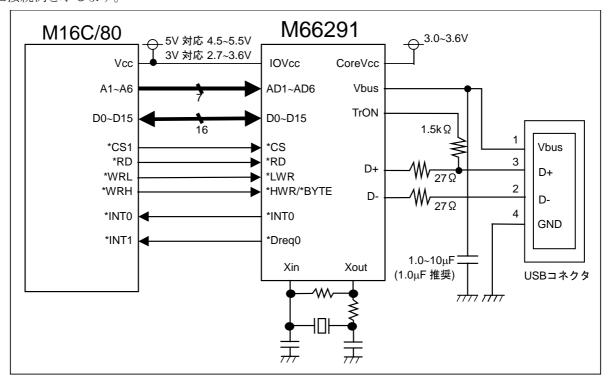

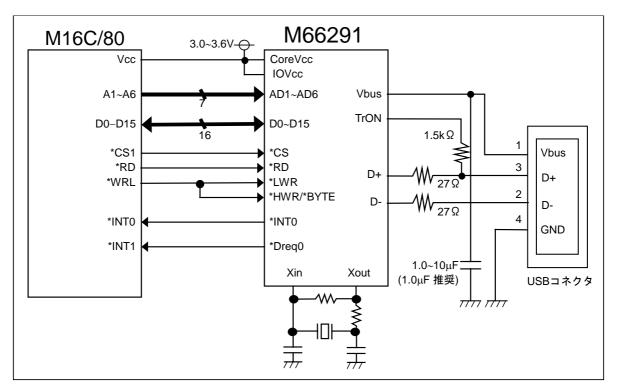

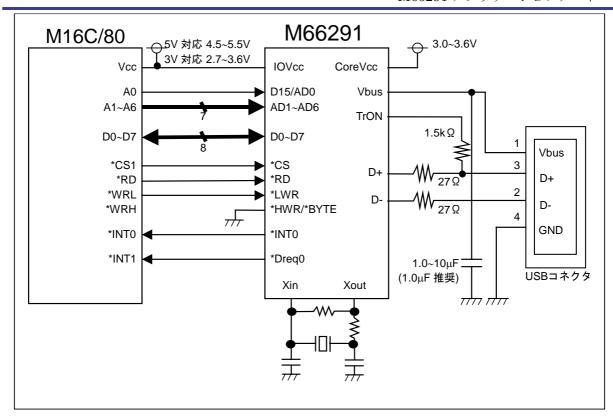

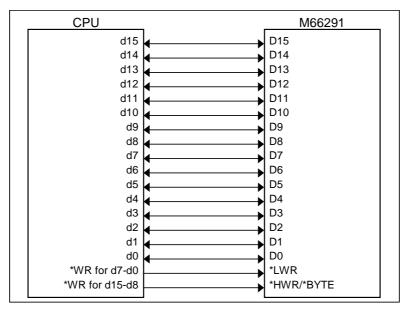

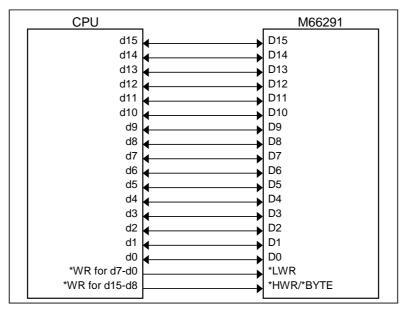

図 2-2 - 図 2-4に M66291 を制御するための CPU としてルネサス 16 ビットマイコン M16C/80 を用いた接続例を示します。

図 2-2 M66291 接続例 1 (16bit バス幅)

図 2-3 M66291 接続例 2 (16bit バス幅;M66290A 互換)

図 2-4 M66291 接続例 3 (8bit バス幅)

#### 2.3. 制御用プログラム概略フロー

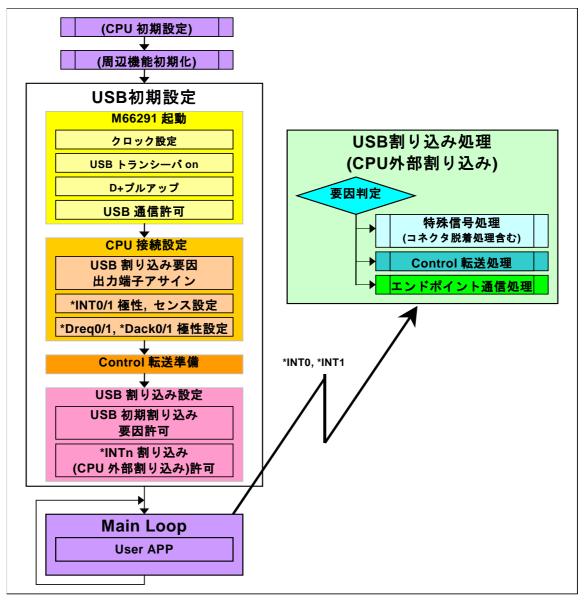

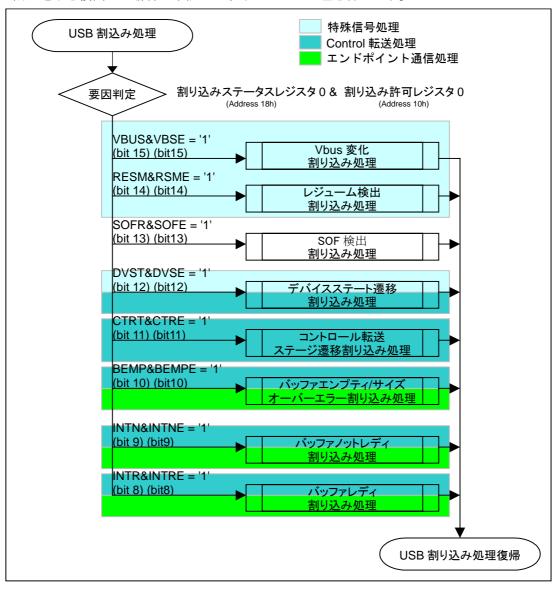

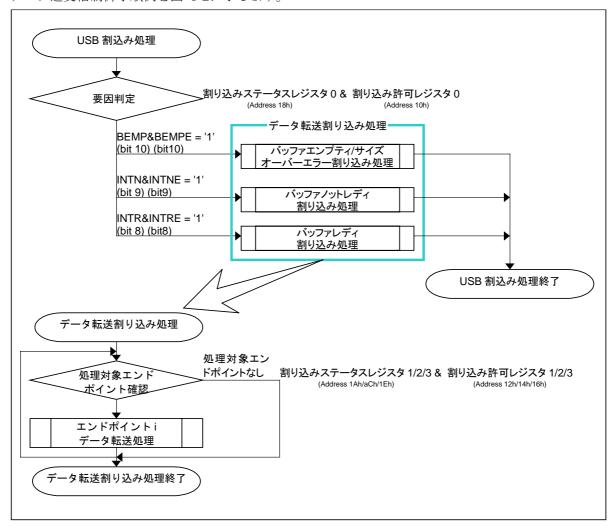

M66291 は USB のデータ送受信、特殊信号処理等を割り込み信号で CPU に通知します。したがって、 制御プログラムは初期設定プログラムと USB 割り込み処理プログラムによって構成されます。

制御 CPU の外部割り込みプログラムにて、割り込み要因を判別し、該当する処理を実行してください。

- (1) 特殊信号処理

- Vbus 割り込み、レジューム割り込み、SOF 検出割り込み、デバイスステート遷移割り込み

- (2) コントロール転送処理 コントロール転送ステージ遷移割り込み、デバイスステート遷移割り込み

- (3) エンドポイントデータ転送処理 バッファエンプティ/サイズオーバエラー割り込み、バッファノットレディ割り込み、バッファレデ ィ割り込み

M66291 が判定可能な各種 USB 処理を CPU の割り込みルーチンで処理する場合、M66291 制御プロ グラム構成例は以下のようになります。

図 2-5 M66291 制御プログラム構成例

#### 2.4. 割り込み処理

メイン CPU は M66291 からの\*INTn 信号により USB 割り込みを認識します。USB 割り込みの要因は次の4種類の割り込みステータスレジスタの内容により識別可能です。

- (1) **割り込みステータス 0 レジスタ**(Address 18h)割り込み種別識別

- (2) 割り込みステータス 1 レジスタ(Address 1Ah)バッファレディ発生エンドポイント識別

- (3) 割り込みステータス 2 レジスタ(Address 1Ch)バッファノットレディ発生エンドポイント識別

- (4) **割り込みステータス 3 レジスタ**(Address 1Eh)バッファエンプティ/サイズオーバエラー発生エンドポイント識別

M66291 の割り込み識別には、割り込みステータス 0 レジスタ及び割り込み許可 0 レジスタを用います。 各割り込みに対応したビット状態(二つのレジスタの論理積)により割り込み要因を認識し、該当する割り 込み処理を行います。

割り込みステータス 1 レジスタ、割り込みステータス 2 レジスタ及び割り込みステータス 3 レジスタはエンドポイントバッファ状態割り込みに対応するエンドポイント番号を識別します。

必要に応じて、割り込み処理の中で各割り込み要因をクリアしてください。

USB 割り込みを検出した場合は下記のようなフローで処理を行います。

図 2-6 M66291 割り込み処理例

#### 2.5. データ転送割り込み

M66291 は3タイプのデータ転送割り込み要因を備えており、ユーザの用途に合わせてデータ転送割り 込み要因を選択することが可能です。各割り込み要因は割り込みステータスレジスタ 1~3 により、当該割 り込み要因が発生したエンドポイントを認識することが可能です。各データ転送割り込み要因は転送タイ プ、転送方向及びアクセス方法により割り込み発生条件が異なりますのでご注意ください。

各割り込みの要因クリア方法及び詳細機能については、「M66291 データシート」を参照ください。

| 割             |                | バッファレディ<br>割り込み    | バッファノット<br>レディ割り込み     | バッファエンプティ/サイズ<br>オーバエラー割り込み    |

|---------------|----------------|--------------------|------------------------|--------------------------------|

|               | (割り込み<br>発生条件) | 削り込み<br>(FIFO バッファ | (USB送受信                | (IN トークンに対し送信データ               |

| 転送タイプ         |                | 読み書き可能)            | 不可)                    | なし/最大パケットサイズを超<br>えるデータパケット受信) |

| コントロール Read   | l 転送時          | (発生しない)            | IN トークンに対              | 送信完了                           |

|               |                |                    | し NAK 応答 <sup>1</sup>  |                                |

| コントロール Writ   | e 転送時          | 受信データ読み            | OUT トークンに              | パケットサイズオーバー                    |

|               |                | 出し可能               | 対し NAK 応答              |                                |

|               |                | 送信データ書き            | IN トークンに対              | 送信完了                           |

| CPU_FIFO_DATA | IN 時           | 込み可能               | し NAK 応答 <sup>1</sup>  | (バッファエンプティ)                    |

| へのアクセス        | データ転送          | 受信データ読み            | OUT トークンに              | パケットサイズオーバー                    |

|               | OUT 時          | 出し可能               | 対し NAK 応答 <sup>1</sup> |                                |

|               | データ転送          | 送信データ書き            | IN トークンに対              | 送信完了                           |

| Dn_FIFO_DATA  | IN 時           | 込み可能 2             | し NAK 応答               | (バッファエンプティ)                    |

| へのアクセス        | データ転送          | 受信データ読み            | OUT トークンに              | パケットサイズオーバー                    |

|               | OUT 時          | 出し可能 2             | 対し NAK 応答              |                                |

表 2-1 データ転送タイプごとのデータ転送割り込み発生条件

USBの各データ転送タイプごとの推奨設定は次のとおりです。

転送タイプ 許可する割り込み要因 ダブルバッファ機能 連続転送機能 コントロール転送ステージ遷移 コントロール Read NA バッファエンプティ/サイズオーバ エラー(非連続転送) コントロール Write コントロール転送ステージ遷移 NA 0 バッファレディ(非連続転送) バルク IN バッファレディ O O バルク OUT バッファレディ O O インタラプト IN バッファエンプティ/サイズオーバ X エラー インタラプトOUT バッファレディ \_ × アイソクロナス IN バッファレディ O アイソクロナス OUT バッファレディ O

表 2-2 転送タイプ別推奨設定

O:「使用する」設定を推奨 一:「使用しない」設定を推奨 ×:必ず「使用しない」に設定 NA:「使用する」設定不可

<sup>1</sup> エンドポイントが IN 方向の場合に FIFO バッファをクリアを行うと、INTR 割り込みが連続して発生しますので ご注意ください。

<sup>&</sup>lt;sup>2</sup> INTM[DMA 割り込みモードビット](Address 48h、50h)でバッファレディ割り込みの発生有無を設定できます。 あわせて、*2.6 FIFO 制御*も参照ください。

### 2.6. FIFO 制御

M66291 は 3K バイトの大容量 FIFO バッファを内蔵しており、エンドポイント 1~エンドポイント 6 の各エンドポイントに対して別々のバッファ領域を割り当てて使用します。FIFO バッファは 64 バイト ×48 ブロックで構成されており、各エンドポイントにおける領域確保は、EPi\_Buf\_Nmb[バッファ先頭番号ビット]¹、EPi\_Buf\_siz [バッファサイズビット]¹及び EPi\_DBLB[ダブルバッファモードビット]¹で指定します。領域確保の方法は、後述の設定例を参照ください。領域は重複設定してもエラー扱いされません。重複領域に後から書き込まれたデータが有効となりますのでご注意ください。

各エンドポイントバッファへのアクセスは、4本の FIFO データレジスタによって行います。FIFO データレジスタは、エンドポイント 0 専用の EPO\_FIFO データレジスタ(CPU アクセス)、及び、エンドポイント 1~エンドポイント 14 共用の 15 共用の 17 を共同の 18 本の FIFO データレジスタ構成され、共用の FIFO データレジスタは、CPU アクセス専用の CPU\_FIFO データレジスタが 14 本、DMA 転送インターフェース可能な Dn\_FIFO データレジスタが 18 本あります。 EP1 - EP6 のどのエンドポイントへアクセスするかは、それぞれの FIFO 選択レジスタ18 の設定に従います。

なお、CPU\_EP[CPU アクセスエンドポイント指定ビット]<sup>2</sup>、D0\_DMA\_EP、D1\_DMA\_EP[DMA アクセスエンドポイント指定ビット]<sup>2</sup>で指定しているエンドポイント番号を重複させないでください。各FIFO\_DATA レジスタを使用しない場合は、CPU\_EP または Dn\_DMA\_EP に"0h"を設定してください。

4本の FIFO データレジスタはそれぞれ下記機能を内蔵しており、FIFO 選択レジスタ/制御レジスタの設定に従い動作を行います。

- (1) ショートパケット送信機能 (IVAL[IN バッファセット/OUT バッファステータスビット]<sup>3</sup>使用) ショートパケット送出時等 FIFO バッファがフルになる前に送信データ書き込み完了としたい場合 は、FIFO バッファにデータを書き込んだ後 IVAL='1'を書き込んでください。

- (2) 送信/受信バッファクリア機能 (BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、(BCLR[/v)-v)では、

- (3) zero-length パケット(Null パケット)送信機能 (IVAL & BCLR 使用) IVAL='1'、BCLR='1'を同時に書き込むことで、zero-length パケット(Null パケット)送出の準備完了 となります。ホスト PC からの IN トークンに対応して、M66291 は長さ zero-length パケット(Null パケット)を送信します。

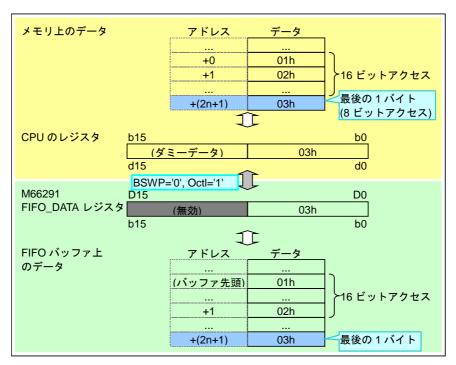

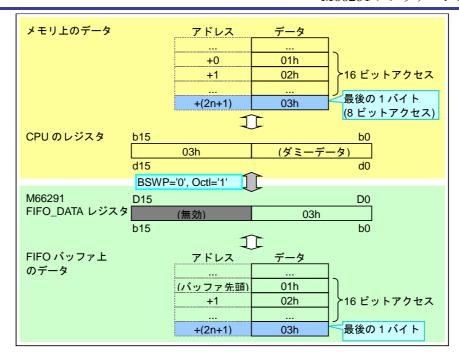

- (4) データ長(8/16 ビット)設定機能 (Octl[レジスタ 8 ビットモードビット]<sup>2</sup> or EPi\_Octl<sup>4</sup>使用) 16bit バス幅接続の場合に、FIFO バッファの書き込み途中で FIFO バッファレジスタの有効ビット 数の切替え(16 ビット→8 ビット)が可能です。奇数バイト数((2n+1)バイト)データの書き込みを行いたい場合、16 ビットモード(Octl='0'、かつ、EPi\_Octl='0')で 2n バイトのデータを書き込み、その後、Octl='1'(または、EPi\_Octl='1')を設定することにより 8 ビットモードに切り替え、最後の 1 バイトのデータ書き込みを行います。<sup>5</sup>

- (5) 受信データ長カウントダウン機能 RCNT[リードカウントモードビット]<sup>2</sup>使用) RCNT='1'を設定して FIFO バッファの読み出しを行うと、1 回の読み出し毎に CPU\_DTLN<sup>3</sup>がディクリメントされます。16 ビットアクセス時は-2 ずつ、8 ビットアクセス時は-1 ずつディクリメントされます。受信データ長カウントダウン機能は CPU\_FIFO データレジスタへのアクセスの場合のみ有効です。

- (6) バッファリワインド機能 FIFO バッファリワインドビット] <sup>2</sup>使用) FIFO バッファにデータ書き込み途中、もしくは FIFO バッファからデータ読み出し途中に、RWND='1'を書きこむと、FIFO バッファ内部カウンタが初期化されます。

書き込み時:それまでに書き込みを行ったデータが無効となります。

読み出し時:バッファの先頭データから再読み出し可能となります。

RWND='0'であれば、書き込み/読み出し途中で CPU\_EP/DMA\_EP の切り替えを行い、再び CPU\_EP を元のエンドポイントに割り付けた場合でも、続きのデータの書き込み/読み出しを行うことができ

<sup>&</sup>lt;sup>5</sup> CPU\_FIFO 選択レジスタ上の Octl と、CPU\_EP で指定しているエンドポイントの EPi\_Octl との"or"が動作に反映されます。

<sup>&</sup>lt;sup>1</sup> EPi コンフィギュレーションレジスタ 0(Address 60h、64h、68h、6Ch、70h、74h)

<sup>&</sup>lt;sup>2</sup> CPU FIFO 選択レジスタ 0(Address 40h)、Dn FIFO 選択レジスタ 0(Address 48h、50h)

<sup>&</sup>lt;sup>3</sup> CPU\_FIFO 制御レジスタ 0(Address 42h)、Dn\_FIFO 制御レジスタ 0(Address 4Ah、52h)

<sup>&</sup>lt;sup>4</sup> EPi コンフィギュレーションレジスタ 1(Address 62h、66h、6Ah、6Eh、72h、76h)

ます。<sup>1</sup>

また、IN 方向のエンドポイントに EPi\_NULMD $^4$ ='1'を設定している場合、FIFO データ書き込み中は"バッファノットレディ状態(ホストからの IN トークンに応答できないため)"と認識され、zero-length パケット(Null パケット)送信自動付加機能が動作します。

FIFO バッファ書き込みが遅い場合は上記のような現象が発生しますのでご注意ください。なお、M66291 は、以下の(1)または(2)のときに FIFO バッファ書き込み完了と認識します。

- (1) IVAL='1'を書き込んだ。((書き込みデータ数)<(FIFO バッファサイズ)の場合)

- (2) FIFO バッファ Full まで書き込みを行った。

連続転送設定時、(送信したいデータ数)<(FIFO バッファサイズ)の場合にも、上記(1)の方法で書きこみ終了させてください。

FIFO バッファのアクセスフローの例は5 データ転送を参照ください。

# 2.6.1. 連続転送モード時に、FIFO バッファ容量未満かつ最大パケットサイズの整数倍のデータを読み出す方法

連続転送モード時に、CPU\_FIFO データレジスタ経由で、FIFO バッファ容量未満かつ最大パケットサイズの整数倍のデータをリードする場合の手順例を示します。

USB specification revision1.1 の 5.8.3 章で、bulk 転送のデータ転送完了は次のように定義されており、ここでは、前者の場合(デバイス側が受信データ数を予測可能な場合)について例を示します。

- Has transferred exactly the amount of data expected

- Transfers a packet with a payload size less than wMaxPacketSize or transfers a zero-length packet.

この場合には、バッファレディ割り込みでデータを読み出すたびに受信すべき総受信バイト数と、受信済みの総バイト数を比較し、最後の1面受信時には SIE\_DTLN[SIE\_FIFO 受信データ長ビット] をポーリングすることにより、受信完了を知ることができます。 SIE\_DTLN は1パケット分のデータを受信完了したタイミングでハードウエアにより更新されます。 SIE\_DTLN が受信すべきバイト数に達した時点で、以下の手順でデータを読み出してください。

- (1) CPU\_EP で指定したエンドポイントの PID $^3$  = '00'(NAK)にする

- (2) Sreq<sup>2</sup>='0'を確認する(Sreq='0'になるまで待つ)

- (3) TGL<sup>2</sup>='1'を書き込む(受信データが CPU から読み出し可能になる)

- (4) Creq<sup>4</sup>='0'を確認する(Creq='0'になるまで待つ)

- (5) データ読み出し

- (6) 読み出し完了後、CPU\_EP で指定したエンドポイントの PID = '01'(Buf)にする

<sup>&</sup>lt;sup>4</sup> CPU\_FIFO 制御レジスタ 0(Address 42h)

<sup>&</sup>lt;sup>1</sup> RWND='1'書き込み時は、RWND と CPU\_FIFO 選択レジスタ/Dn\_FIFO 選択レジスタ上の他のビットを同時に書き 込まないでください。

<sup>&</sup>lt;sup>2</sup> SIE\_FIFO ステータスレジスタ 0(Address 46h)

<sup>&</sup>lt;sup>3</sup> EPi コンフィギュレーションレジスタ 1(Address 62h、66h、6Ah、6Eh、72h、76h)

## 表 2-3 各エンドポイントコンフィギュレーションレジスタ設定例 1

|    |        |                      |                    | 転送タイプ           |                |                 |  |

|----|--------|----------------------|--------------------|-----------------|----------------|-----------------|--|

|    |        |                      |                    | バルク IN          | インタラプト IN      | アイソクロナス IN      |  |

| I∃ | Ŀ      | 最大パケットサイズ            |                    | 64 バイト          | 32 バイト         | 100 バイト         |  |

| 月月 | e<br>F | FIFO バッファサイズ         |                    | 512 バイト         | 64 バイト         | 256 バイト         |  |

| 伢  | 削      | ダブルバッファ構成            |                    | 256×2           | ı              | 128× 2          |  |

|    |        | FIFO バッファ番号割り        | 付け                 | 08h-0Fh         | 20h-20h        | 22h-25h         |  |

|    |        | 転送タイプ                | [EPi_TYP]          | '01'            | '10'           | '11'            |  |

| コン |        | 転送方向                 | [EPi_DIR]          | '1'             | '1'            | '1'             |  |

| フ  |        | トグルモード               | [EPi_ITMD]         | '0'             | '0'            | '0'             |  |

| イギ | 0      | バッファサイズ <sup>1</sup> | [EPi_Buf_siz]      | '0011'(256 バイト) | '0000'(64 バイト) | '0001'(128 バイト) |  |

| ナユ |        | ダブルバッファモード           | [EPi_DBLB]         | 1b(256×2 バイト)   | 0b             | 1b(128×2 バイト)   |  |

| V  |        | 連続送受信モード             | [EPi_RWMD]         | '1'             | '0'            | '0'             |  |

| シ  |        | バッファ先頭番号 [           | EPi_Buf_Nmb]       | 08h             | 20h            | 22h             |  |

| 目  |        | 応答 PID               | [EPi_PID]          | _               | _              | _               |  |

| レ  |        | 長さ0のデータ送信自動          | 付加モード <sup>2</sup> | '1'             | '0'            | '0'             |  |

| ジ  | ジ      |                      | [EPi_NULMD]        |                 |                | U               |  |

| スタ | 1      | 自動クリアモード             | [EPi_ACLR]         | '0'             | '0'            | '0'             |  |

| 設  |        | FIFO アクセスモード         | [EPi_Octl]         | '0'             | '0'            | '0'             |  |

| 設定 |        | 最大パケットサイズ            | [EPi_MXPS]         | 040h            | 020h           | 064h            |  |

表 2-4 各エンドポイントコンフィギュレーションレジスタ設定例 2

|     |             |                      |                                    | 転送タイプ            |                |                 |  |

|-----|-------------|----------------------|------------------------------------|------------------|----------------|-----------------|--|

|     |             |                      |                                    | バルク OUT          | インタラプト OUT     | アイソクロナス<br>OUT  |  |

| ,   | +           | 最大パケットサイズ            |                                    | 64 バイト           | 32 バイト         | 100 バイト         |  |

| 1   | 吏<br>甲<br>列 | FIFO バッファサイズ         |                                    | 1024 バイト         | 64 バイト         | 256 バイト         |  |

| 1   | 列           | ダブルバッファ構成            |                                    | 512×2            | _              | 128×2           |  |

|     |             | FIFO バッファ番号割り        | 付け                                 | 10h-1Fh          | 21h-21h        | 26h-29h         |  |

|     |             | 転送タイプ                | [EPi_TYP]                          | '01'             | '10'           | '11'            |  |

| コ   |             | 転送方向                 | [EPi_DIR]                          | '0'              | '0'            | '0'             |  |

| フ   |             | トグルモード               | [EPi_ITMD]                         | '0'              | '0'            | '0'             |  |

| イギ  | 0           | バッファサイズ <sup>1</sup> | [EPi_Buf_siz]                      | '0111'(1024 バイト) | '0000'(64 バイト) | '0001'(128 バイト) |  |

| ナユ  |             | ダブルバッファモード           | [EPi_DBLB]                         | '1'(1024×2 バイト)  | '0'            | '1' (128×2 バイト) |  |

| V   |             | 連続送受信モード             | [EPi_RWMD]                         | '1'              | '0'            | '0'             |  |

| シ   |             | バッファ先頭番号             | [EPi_Buf_Nmb]                      | 10h              | 21h            | 26h             |  |

| 3   |             | 応答 PID               | [EPi_PID]                          | _                | _              | -               |  |

| ンレジ | 1           | 長さ0のデータ送信自動          | が付加モード <sup>2</sup><br>[EPi_NULMD] | '0'              | '0'            | '0'             |  |

| スタ  |             | 自動クリアモード             | [EPi_ACLR]                         | '0'              | '0'            | '0'             |  |

| ジ設  |             | FIFO アクセスモード         | [EPi_Octl]                         | '0'              | '0'            | '0'             |  |

| 設定  |             | 最大パケットサイズ            | [EPi_MXPS]                         | 040h             | 020h           | 064h            |  |

<sup>&</sup>lt;sup>1</sup> 確保される FIFO バッファの領域=([EPi\_Buf\_siz]+1)×64 バイトとなります。

<sup>&</sup>lt;sup>2</sup> zero-length パケット(Null データ)送信自動付加モードを使用する場合の注意点

ダブル FIFO バッファの設定の場合に、バッファの片方のデータを PC に送信し終わった時点でもう片方にまだ制 御 CPU からデータ書き込み中であったら、M66291 は zero-length パケット(Null パケット)を自動的に送信して しまいます。よって、zero-length パケット(Null データ)送信自動付加モードは全部の送信データを FIFO バッフ アに書き込み終わったあとセットする必要があります。

<sup>9.6</sup> zero-length パケット(Null パケット)送信自動付加機能に関する Q&Aも参照ください

#### 2.7. Dn\_FIFO データレジスタへのアクセス(DMA コントローラインターフェース)

#### 2.7.1. DMA コントローラインターフェース概要

外部 DMA コントローラから FIFO バッファアクセスを行うために、M66291 は DO FIFO データレジ スタ/D1\_FIFO データレジスタ(以下 Dn\_FIFO データレジスタ)を持ちます。 DMA コントローラによるア クセスを行う場合は、CPU アクセス同様に EPi **コンフィギュレーションレジスタ 0/1** にてバッファ領域 を確保し、Dn\_FIFO 選択レジスタにて DMA 転送方法の指定を行い、Dn\_FIFO データレジスタを使用し てデータ転送を行います。

DMA 転送方法は、以下 4 つのパラメータによって設定します。ご使用になる DMA コントローラの仕 様にあわせてパラメータを設定してください。パラメータ一覧を表 2-5に、パラメータの組み合わせ一覧 を表 2-6に示します。各パラメータの詳細については、M66291GP/HP データシート【2.31 Dn\_FIFO 選 択レジスタ】を参照ください。

M66291 では、DMA コントローラを使用せずに(通常の CPU アクセスによって)、Dn FIFO データレ **ジスタ**に対してアクセスを行うことも可能です。

#### 表 2-5 DMA インターフェース用パラメーター覧

| パラメータ       | 説明                                                 |

|-------------|----------------------------------------------------|

| バーストモード     | サイクルスチール転送/バースト転送の選択                               |

| [BUST]      | '0': サイクルスチール転送(1 ワード/1 バイト転送毎に*Dreq 信号がアサート/ネゲ    |

|             | ートを繰り返す転送)                                         |

|             | '1': バースト転送(FIFO バッファレディで*Dreq 信号をアサートし、割り当てた      |

|             | FIFO バッファへのアクセス終了時に*Dreq 信号をネゲートする転送)¹             |

| 転送方法        | Dn_FIFO データレジスタアクセスに使用される信号の選択                     |

| [DFORM]     | '00': *Dack 信号、及び、リード/ライト信号で制御                     |

|             | (チップセレクト信号、アドレス信号は don't care)                     |

|             | '01': *Dack 信号のみで制御                                |

|             | (チップセレクト信号、アドレス信号、リード/ライト信号は don't care)           |

|             | '10':チップセレクト信号、アドレス信号、及びリード/ライト信号で制御               |

|             | (*Dack 信号はインアクティブ固定にして下さい)                         |

|             | '11': (設定禁止)                                       |

| DMA 割り込みモード | バッファレディ割り込み発生条件の選択 <sup>2</sup>                    |

| [INTM]      | '0': OUT バッファ設定時:DMA 転送終了 EPB_RDY³='1'がセットされる(バッファ |

|             | レディ割り込み発生)                                         |

|             | IN バッファ設定時:EPB_RDY ビットは'1'にセットされない(バッファレディ         |

|             | 割り込みは発生しない)                                        |

|             | '1': CPU_FIFO と同様の条件(FIFO バッファ読み出し可能/FIFO バッファ書き込  |

|             | み可能)でバッファレディ割り込みが発生する                              |

| DMA イネーブル   | *Dreq 信号出力許可/不許可の選択 <sup>2</sup>                   |

| [DMAEN]     | '0': *Dreq 信号を出力しない                                |

|             | '1': Dreq <sup>4</sup> の状態を*Dreq 信号に出力する           |

<sup>1</sup> バースト転送時の\*Dreq 信号のネゲート条件は以下のとおりです。

<sup>(1)</sup>非連続転送モード時:以下(A)~(C)のいずれかの場合

<sup>(</sup>A)すべての受信データ読み出し終了時

<sup>(</sup>B)最大パケットサイズ分のデータ書き込み終了時

<sup>(</sup>C)ショートパケット分のデータ書き込み(zero-length パケットの場合も含む)終了後に IVAL='1'をセット時

<sup>(2)</sup>連続転送モード時:以下(A)~(C)のいずれかの場合

<sup>(</sup>A)受信の場合(ショートパケット受信時も含む)

<sup>⇒</sup>FIFO バッファの片側のデータ読み出し終了時(ダブルバッファの場合は片面の読み出し終了時)

<sup>(</sup>B)[(送信データバイト数)≧FIFO バッファバイト数(ダブルバッファの場合は片側のバイト数)]の場合 ⇒割り当てた FIFO バッファ分のデータ書き込み終了時(ダブルバッファの場合は片面の読み出し終了時)

<sup>(</sup>C)[(送信データバイト数)<FIFO バッファバイト数(ダブルバッファの場合は片側のバイト数)]の場合 ⇒すべての送信データ書き込み終了後、IVAL='1'をセット時

<sup>&</sup>lt;sup>2</sup> INTM='0'、かつ、DMAEN='0'の組み合わせでは使用しないでください。

<sup>&</sup>lt;sup>3</sup> 割り込みステータスレジスタ 1(Address 1Ah)

<sup>&</sup>lt;sup>4</sup> Dn\_FIFO 制御レジスタ(Address 4Ah、52h)

#### 表 2-6 DMA インターフェース用パラメータ有効組み合わせ一覧

| No | BUSF | DFOR | N<br>T | Α | 備考                                                                                           |

|----|------|------|--------|---|----------------------------------------------------------------------------------------------|

|    |      | М    |        | Ν |                                                                                              |

| 1  | 0    | 00   | 0      | 1 | M66290A(1word 転送モード)互換モードです                                                                  |

| 2  | 0    | 00   | 1      | 1 | 組み合わせ No.1 で、バッファレディ毎にバッファレディ割り込みを発生させるモードです。                                                |

| 3  | 0    | 01   | 0      |   | 1 サイクル転送(*Dack 信号の立下りでソースからデータを読み出し、*Dack 信号の立ち上がりでディスティネーションにデータを書き込む)用のモードです。結線方法にご注意ください。 |

| 4  | 0    | 01   | 1      | 1 | 組み合わせ No.3 で、バッファレディ毎にバッファレディ割り込みを発生させるモードです。                                                |

| 5  | 0    | 10   | 0      |   | *Dack ハンドシェイクを持たない DMA コントローラ用のモードです。<br>*Dack 信号はインアクティブ固定にして下さい。                           |

| 6  | 0    | 10   | 1      | 0 | CPU アクセス用(DMA コントローラ不使用) のモードです。*Dreq 信号/*Dack 信号<br>を使用しません。*Dack 信号はインアクティブ固定にして下さい。       |

| 7  | 0    | 10   | 1      | 1 | 組み合わせ No.5 で、バッファレディ毎にバッファレディ割り込みを発生させるモードです。                                                |

| 8  | 1    | 00   | 0      | 1 | 組み合わせ No.1 のバースト転送モードです。                                                                     |

| 9  | 1    | 00   | 1      | 1 | 組み合わせ No.2 のバースト転送モードです。                                                                     |

| 10 | 1    | 01   | 0      | 1 | 組み合わせ No.3 のバースト転送モードです。                                                                     |

| 11 | 1    | 01   | 1      | 1 | 組み合わせ No.4 のバースト転送モードです。                                                                     |

| 12 | 1    | 10   | _      |   | 組み合わせ No.5 のバースト転送モードです。                                                                     |

| 13 | 1    | 10   | 1      | 1 | 組み合わせ No.7 のバースト転送モードです。                                                                     |

\*Dreq 信号は、DMA\_EP[DMA 転送エンドポイント指定ビット]に指定されたエンドポイントのバッファが レディ状態になった時にアサートされます。ここで、バッファレディ状態とは、そのエンドポイントの転 送方向が OUT(ホストからのデータを受信)に設定されていれば読み出し可能状態を指し、そのエンドポイ ントの転送方向が IN(ホストヘデータを送信)に設定されていれば書き込み可能状態を指します。

DMA 転送では CPU アクセスと同様にエンドポイントに割り当てた FIFO バッファの状態によりバッ ファノットレディ割り込み、バッファエンプティ/サイズオーバエラー割り込みが発生します。しかし、 バッファレディ割り込みの発生条件に関しては、表 2-5に示すとおり、INTM の設定によって差異があり

INTM='0'の場合、バッファレディ割り込みの発生によりショートパケットを受信したことを認識するこ とができます。DMA\_DTLN¹を参照することにより、ショートパケットのバイト数、または、連続受信モ ードではショートパケット受信時の受信データのバイト数を示します。INTM='0'の設定で使用する場合、 バッファレディ割り込み処理の中で必ず BCLR='1'を行い FIFO バッファをクリアしてください。

<sup>&</sup>lt;sup>1</sup> Dn\_FIFO 制御レジスタ(Address 4Ah、52h)

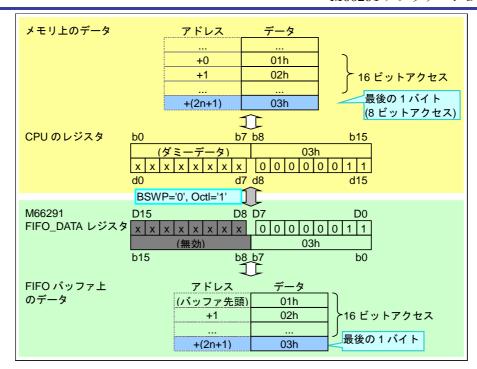

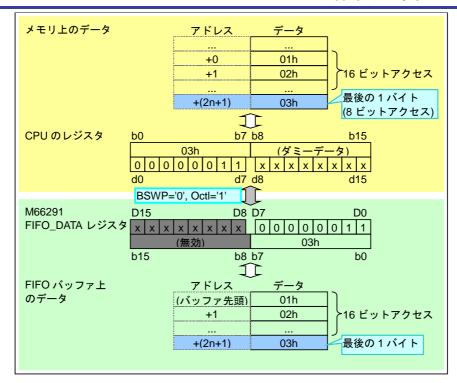

### 2.7.2. 16bit バス幅接続時に Dn\_FIFO データレジスタで奇数バイト数データの読み出し/書き込みを行う 方法

## 2.7.2.1. OUT 方向(読み出し)の場合

(2n+1)バイト受信する場合、DMA コントローラの転送カウンタを(2(n+1))バイト((n+1)回)に設定し、 全データ読み出し後、(n+1)回目の転送データの上位を無視してください(n+1回目のリードデータは上位 /下位同じデータになります)。

この場合はショートパケット受信時ですので、バッファレディ割り込み処理の中で上記判定を行います。 読み出した FIFO バッファの受信データ数を DMA DTLN で確認してください。

#### 2.7.2.2. IN 方向(書き込み)の場合

(2n+1)バイト送信する場合、DMA コントローラの転送カウンタを(2n)バイト(n回)に設定し、DMA コ ントローラの終了割り込みの中で、Octl¹='1'、または、EPi Octl='1'²を設定後、最後の 1 バイトを書き込 み書きこみ、IVAL='1'をセットしてください。

#### 2.7.3. Dn FIFO レジスタ経由で FIFO バッファにショートパケットデータを書き込む方法

DMA コントローラの転送カウンターに書き込むバイト数を設定し、DMA コントローラの終了割り込 み処理にて、IVAL='1'をセットしてください。

### 2.7.4. 連続転送モード時に、FIFO バッファ容量未満かつ最大パケットサイズの整数倍のデータを読み出 す方法

連続転送モード時に、Dn\_FIFO データレジスタ経由で、FIFO バッファ容量未満かつ最大パケットサイ ズの整数倍のデータを読み出す場合の手順例を示します。

USB specification revision 1.1 の 5.8.3 章で、bulk 転送のデータ転送完了は次のように定義されており、 ここでは、前者の場合(デバイス側が受信データ数を予測可能な場合)について例を示します。

- Has transferred exactly the amount of data expected

- Transfers a packet with a payload size less than *wMaxPacketSize* or transfers a zero-length packet. この場合には、トランザクション回数機能が使用できます。データ受信前に TRNCNT³にトランザクシ ョン回数を設定してください。

M66291 は設定した回数分のパケット受信後、\*Dreq 信号をアサートします。手順としては、次のとおり です。

- (1) 受信データ数がわかるまで、PID<sup>2</sup>='00'(NAK)にしておく

- (2) TRCLR<sup>4</sup>='1' (トランザクションカウンタクリア)

- (3) TRNCNT=(受信パケット数) (同時に DMA コントローラの転送カウンタセット)

- (4) TREN<sup>4</sup>='1'(トランザクションカウント有効)

- (5) PID='01'(Buf)(受信開始)

- (6) (受信、DMAC によるデータ読み出し)

- (7) 受信完了時(DMA コントローラ割り込み処理の中)、PID='00'(NAK)

<sup>&</sup>lt;sup>4</sup> Dn\_FIFO 制御レジスタ(Address 4Ah、52h)

<sup>&</sup>lt;sup>1</sup> Dn\_FIFO 選択レジスタ(Address 48h、50h)

<sup>&</sup>lt;sup>2</sup> EPi コンフィギュレーションレジスタ 1(Address 62h、66h、6Ah、6Eh、72h、76h)

<sup>&</sup>lt;sup>3</sup> DMAn\_トランザクション回数レジスタ(Address 4Eh、56h)

# 3. 初期設定

USB 通信用の初期設定は、図 2-5中「USB 初期設定」に示したフローとなります。

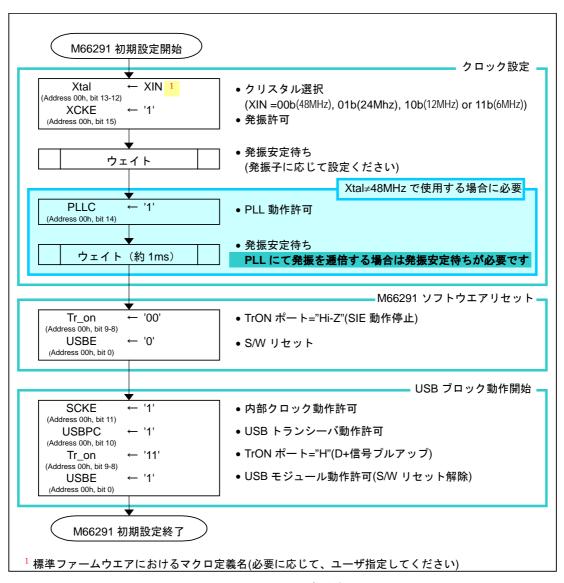

#### 3.1. M66291 起動

M66291 の発振が安定してから初期化処理を行います。PLL 動作許可設定後はクロックによる不安定な 動作を避けるために待ち時間(1ms 以上)が必要です。TrON ポートを"H"出力することにより D+信号がプ ルアップされ、ホスト(アップストリーム側)がデバイス接続を検知します。

S/W リセット(USBE $^1$ ='0')実行時の各レジスタ状態は M66291 データシート【レジスタ一覧】を参照く ださい。

M66291 起動を図 3-1に示します。図 3-1に関する補足事項は以下のとおりです。

- (1) 水晶発振子により発振供給する場合の起動例を示しています。

- (2) ウエイト後の SW リセットはホストに対する非接続通知も兼ねており、USB バスリセット信号を 受信するために行っています。

- (3) ホストより Vbus が供給されている場合に行う M66291 起動(初期設定)時の設定例です。

図 3-1 M66291 起動例

<sup>&</sup>lt;sup>1</sup> USB 動作許可レジスタ(Address 00h)

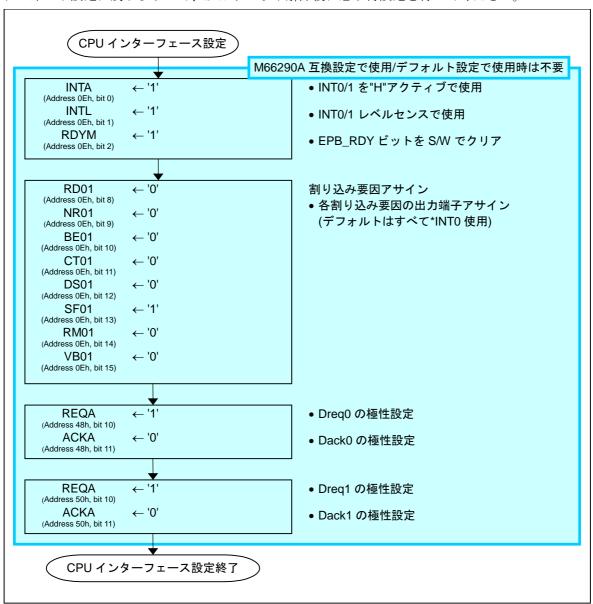

### 3.2. CPU 接続設定

M66291 には、制御 CPU との接続性向上のためにいくつかの機能があります。M66291 初期設定後に、必要に応じて以下の設定を行ってください。M66290A 互換設定の場合、デフォルト設定で使用される場合はこれらの処理は必要ありません。

- (1) 割り込み端子\*INT0、\*INT1 の極性("L"アクティブ(デフォルト)/"H"アクティブ)、及び、割り込みセンス(エッジセンス(デフォルト)/レベルセンス)設定

- (2) \*Dreq0、\*Dack0、\*Dreq1、\*Dack1 の極性設定(DMA インターフェース使用時)("L"アクティブ(デフォルト)/"H"アクティブ)

- (3) 各割り込み要因の出力端子アサイン(デフォルトではすべて\*INT0 にアサイン)

上記(1)~(3)の処理は S/W リセット解除後(USBE='0' $\rightarrow$ '1')に行ってください。S/W リセット実行直後はデフォルト設定に戻りますので、S/W リセット解除後に必ず再設定を行ってください。

図 3-2 CPU 接続設定例

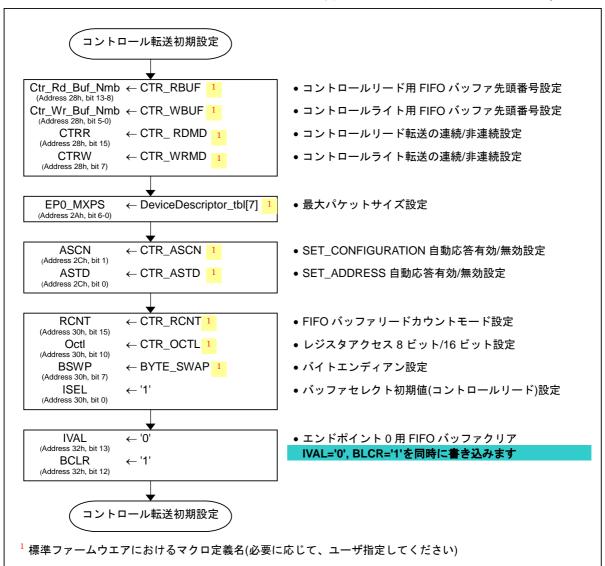

## 3.3. コントロール転送準備(エンドポイント 0 初期設定)

M66291 の初期設定後に、コントロール転送を行える状態にするため、エンドポイント 0 初期設定を行ってください。エンドポイント 0 初期設定手順例を図 3-3に示します。図 3-3に関する補足事項は以下のとおりです。

- (1) エンドポイント 0 初期設定は、M66291 起動、CPU 接続設定後に行ってください。

- (2) FIFO バッファ先頭番号の指定は、送受信の FIFO バッファ領域が重ならないように行ってください。また、同時使用の可能性のあるエンドポイント 1-エンドポイント 6の FIFO バッファ領域とも重ならないように指定してください。

- コントロール転送が FIFO バッファを使用するのは Data ステージにおけるデータパケット送受信時です。Setup ステージのデータパケットの受信は専用レジスタに格納されます。

- (3) 旧タイプのホストコントローラ、及び、旧タイプのホスト OS に対応するため、最大パケットサイズは"8 バイト"を推奨しています。

- (4) 自動応答が有効な状態遷移は4 コントロール転送を参照ください。

- (5) FIFO バッファクリアは IVAL<sup>1</sup> = '0'、 BLCR<sup>1</sup> = '1'を同時に書き込んでください。

- (6) 図 3-3のエンドポイント0の各設定はマクロ定義されている場合の例を示しています。

図 3-3 エンドポイント 0 初期設定手順例

<sup>&</sup>lt;sup>1</sup> EP0\_FIFO 制御レジスタ(Address 32h)

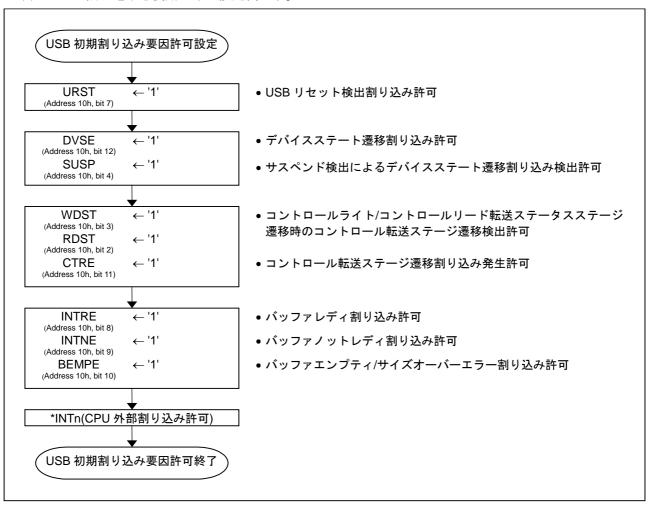

#### USB 初期割り込み要因許可 3.4.

M66291 により USB 通信を開始するために、M66291 の割り込み許可設定を行ってください。割り込 み許可に関する主な注意点を以下に示します。

- (1) M66291 の割り込み許可設定は M66291 起動、エンドポイント 0 初期設定処理後に行ってください。

- (2) 制御用 CPU 及び他チップと、M66291 割り込み許可に関するタイミングは、システム構成及びご 用途に合わせて設計してください。

- (3) エンドポイント 1-エンドポイント 6 に対するデータ転送割り込み許可(バッファレディ割り込み、 バッファノットレディ割り込み、バッファエンプティ/サイズオーバエラー割り込み)は、Set Configuration リクエスト受信後に行ってください。

Vbus 供給されている(USB デバイスがすでに PC に接続されている)場合のUSB 初期割り込み要因許可 設定例を図 3-4に示します。図 3-4の補足説明は以下のとおりです。

(1) VBUS割り込みを使用しない設定例です。

図 3-4 USB 初期割り込み要因許可設定例

# 4. コントロール転送

## 4.1. コントロール転送概要

コントロール転送は主にセットアップ時に使用される双方向転送で、少なくとも2つのトランザクションステージ(セットアップステージ、ステータスステージ)により構成されます。また、セットアップステージとステータスステージ間に、データステージが存在する場合があります。

USB 通信では、エンドポイント 0 によるコントロール転送及びエンドポイント 0 のコントロール転送 によりホストからデバイスに送信されるいくつかのリクエストに対する応答は必須機能です。

M66291 は、エンドポイント 0 によるコントロール転送及び、セットアップ処理(バスエニュメレーション)制御用プログラムが簡単に記述できるように以下の4機能を備えています。

(1) デバイスステート遷移管理機能

【本資料*4.2、4.3*参照】

(2) データステージ遷移管理機能

【本資料*4.4、4.5*参照】

(3) 連続送受信機能

【本資料4.7、4.9参照】

(4) 自動応答機能

【本資料4.9参照】

#### 4.1.1. コントロール転送を構成するトランザクション

コントロール転送は、以下3種類のトランザクションで構成されます。

(1) セットアップステージ:

セットアップ、データ(DATA0)、及び、ハンドシェークパケットにより構成されます。

SETUP トークン  $\rightarrow$  DATA0(リクエスト)  $\rightarrow$  ACK

本資料では、この一連のトランザクションを SETUP(DATAO) と表記します。

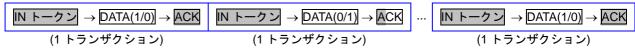

(2) データステージ:

バルク転送と同様にデータトランザクションが必要なだけ繰り返されます。

①コントロールリードの場合

②コントロールライトの場合

本資料では、この一連のトランザクションを IN/OUT(DATA) と表記します。

(3) ステータスステージ:

データステージと逆方向のトークン、及び、zero-lengthパケット(DATA1)で構成されます。

(A) コントロールリードの場合

OUT トークン  $\rightarrow$  DATA1(zero-length パケット)  $\rightarrow$  ACK

(B) コントロールライトの場合

$|N \leftarrow DATA1(zero-length パケット) \rightarrow ACK$

本資料では、この一連のトランザクションを IN/OUT(DATA1:HSK) と表記します。

#### 4.1.2. コントロール転送の種類

コントロール転送には、以下の3種類があります。

(1) コントロールリード転送:

SETUP(DATA0) IN(DATA1) IN(DATA0) ... IN(DATA0/1) OUT(DATA1:HSK) セットアップステージ データステージ ステータスステージ

(2) コントロールライト転送:

OUT(DATA1) OUT(DATA0) ... OUT(DATA0/1) SETUP(DATA0) IN(DATA1:HSK) セットアップステージ データステージ ステータスステージ

(3) ノーデータコントロール転送:

SETUP(DATA0) IN(DATA1:HSK) ステータスステージ セットアップステージ

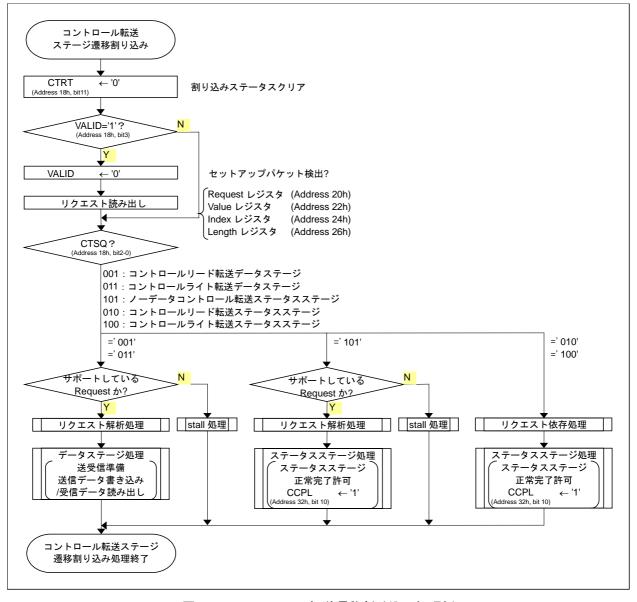

M66291 はステージ管理機能を備えており、コントロール転送遷移割り込み(CTRT='1')によりステージ 遷移を通知します。CPU は割り込み要因によってコントロール転送の該当するステージ処理を行います。 セットアップステージで取得されたデータの内容によって、デバイスはホストの要求するリクエスト種類 が明らかになり、該当するコントロール転送の処理を行うことができます。

また、M66291 は連続送受信機能を備えています。コントロール転送における連続送受信機能は、デー タステージのデータを最大 256 バイトまで割り込みを発生せずに、連続してデータを送受信する機能です。 連続送受信機能を用いることで、データステージでは1トランザクションごとに FIFO アクセスを行う必 要がなくなり、CPU稼働率を高めることができます。

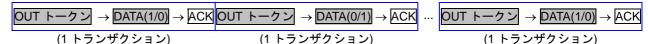

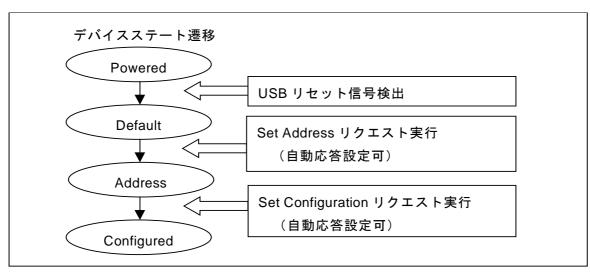

#### USB デバイスステート遷移 4.2.

M66291 は USB デバイスステートの Powered、Default、Address、Configured、Suspended ステー トのデバイスステート遷移管理を H/W で行います。レジューム検出以外のデバイスステート遷移は、デ バイスステート遷移割り込み(DVST'='1')によって CPU へ通知します。レジューム検出によるデバイスス テート遷移は、レジューム割り込み(RESM¹='1')によって CPU へ通知します。

自動応答設定時は Set Address、Set Configuration リクエストに対して、CPU への割り込みを発生さ せずに転送を完了させることができます。

図 4-1 デバイスステート遷移

<sup>&</sup>lt;sup>1</sup> 割り込みステータスレジスタ 0(Address 18h)

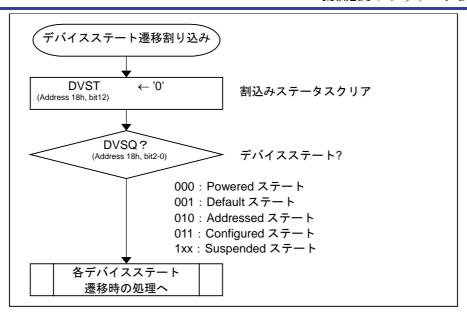

#### 4.3. デバイスステート遷移処理

デバイスステート遷移が正常に実行されると、M66291 は DVSQ[デバイスステート]1に遷移後のデバイ スステート値をストアし、デバイスステート遷移移割り込みを発生(DVST='1')させます。デバイスステー ト遷移割り込みの要因には以下の4種類があり、各割り込み要因毎にデバイスステート遷移割り込み発生 のマスク(各要因検出時の DVST ビットセットの禁止/許可)を設定することができます。

デバイスステート遷移割り込みの発生要因

- (1) USB リセット検出(許可ビット:URST¹)

- (2) Set Address 実行(許可ビット:SADR¹)

- (3) Set Configuration 実行(許可ビット:SCFG¹)

- (4) サスペンド検出(許可ビット:SUSP¹)

制御プログラムは、割り込みによって検出したデバイスステート遷移に必要な処理を実行し、ステート 遷移に伴うユーザプログラムを実行します。

各デバイスステートへの遷移条件と、遷移時に必要な処理を以下に示します。

| デバイスステート           | 遷移条件                          | 遷移時の処理                 |

|--------------------|-------------------------------|------------------------|

| パワーステート            | S/W リセット                      | 図 3-2 CPU接続設定例を参考に必要な  |

| (Powered state)    |                               | 処理を行ってください             |

| デフォルトステート          | USB バスリセット検出                  | (1)エンドポイント 1–エンドポイント 6 |

| (Default state)    |                               | に対するデータ転送割り込み禁止/割      |

|                    |                               | り込みステータスクリア            |

|                    |                               | (2)エンドポイント 1–エンドポイント 6 |

|                    |                               | に割り付けた FIFO バッファクリア    |

| アドレスステート           | (1)デフォルトステートにおいて、             | アドレス保持等                |

| (Address state)    | Set Address リクエスト検出           |                        |

|                    | (2)構成ステートにおいて、                |                        |

|                    | configuration value =0 ∅ Set  |                        |

|                    | Configuration リクエスト検出         |                        |

| 構成ステート             | configuration value ≠ 0 Ø Set | 構成番号保持等                |

| (Configured state) | Configuration リクエスト検出         |                        |

| サスペンドステート          | Suspend 信号検出                  | サスペンド処理                |

| (Suspended state)  |                               |                        |

表 4-1 デバイスステート状態遷移条件と処理

図 4-2 デバイスステート状態遷移

<sup>&</sup>lt;sup>1</sup> 割り込み許可レジスタ 0(Address 10h)

図 4-3 セットアップステージ制御手順例

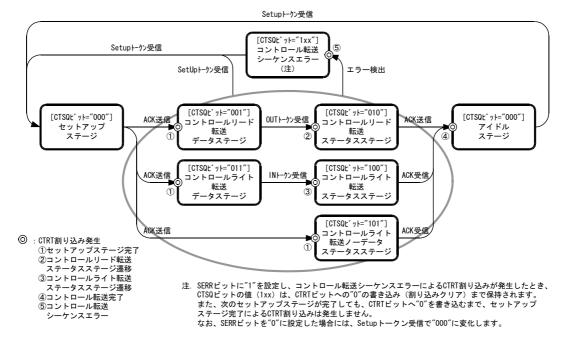

# 4.4. コントロール転送ステージ遷移

M66291 はコントロール転送ステージのセットアップステージ、データステージ、ステータスステージのステージ遷移管理を H/W で行います。M66291 はコントロール転送ステージ遷移を検出すると、 CTSQ[コントロール転送ステージ]¹に遷移後のコントロール転送ステージ値をストアし、コントロール転送ステージ遷移割り込み(CTRT¹='1')を発生させます。

自動応答設定時はSet Address、Set Configuration リクエストに対しては、CPU に割り込みを発生させずに転送を完了させることができます。

コントロール転送ステージ遷移割り込みの要因としては以下の5種類があり、セットアップステージ完了以外の要因については各割り込み要因毎にコントロール転送ステージ遷移割り込み発生のマスク(各要因検出時のCTRTビットセットの禁止/許可)を設定することができます。

コントロール転送ステージ遷移割り込みの発生要因

- (1) セットアップステージ完了(マスク不可)

- (2) コントロールライト転送ステータスステージ遷移(許可ビット:WDST¹)

- (3) コントロールリード転送ステータスステージ遷移(許可ビット:RDST¹)

- (4) コントロール転送完了(許可ビット:CMPL¹)

- (5) コントロール転送シーケンスエラー(許可ビット:SERR¹)

H/W で検出可能なコントロール転送シーケンスエラーは次に示す7つのエラーです。

- (1) コントロールライトデータステージでの IN トークンパケット受信 (データステージの OUT トークンパケットに対して1度も ACK 応答をしていない状態での IN トークンパケット受信)

- (2) コントロールライトステータスステージでの OUT トークンパケット受信

- (3) コントロールリードデータステージでの OUT トークンパケット受信 (データステージの IN トークンパケットに対して 1 度もデータ転送をしていない状態での OUT トークンパケット受信)

- (4) コントロールリードステータスステージでの IN トークンパケット受信

- (5) コントロールリードステータスステージでの zero-length パケット以外のデータパケット受信

- (6) ノーデータコントロールステータスステージでの OUT トークンパケット受信

- (7) 最大パケットサイズを超えたデータの受信

コントロールライトデータステージにおいて、リクエストの wLength 値を超えたデータパケットを受信した場合は、シーケンスエラーと認識することはできません。

なお、H/W でコントロール転送シーケンスエラーを検出した場合には、自動的に応答 PID は STALL('1x')になり、次のセットアップパケットを受信するまで PID='1x'の状態を保持します。

図 4-4にコントロール転送ステージ遷移を示します。

<sup>&</sup>lt;sup>1</sup> 割り込み許可レジスタ 0(Address 10h)

図 4-4 コントロール転送ステージ遷移

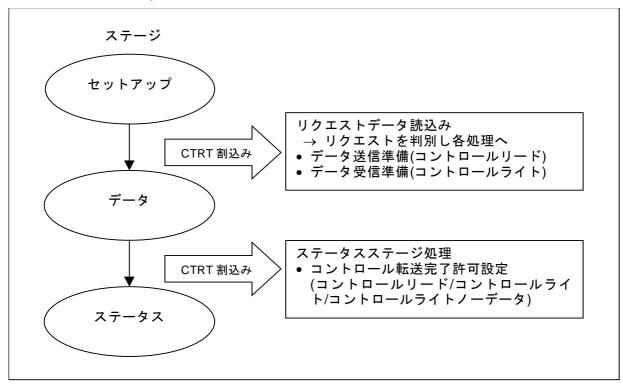

# 4.5. コントロール転送ステージ遷移処理

コントロール転送ステージ遷移割り込み(CTRT='1')により、M66291 のコントロール転送ステージ遷移 を検出した CPU は、CTSQ[コントロール転送ステージ]を確認し該当する処理を行います。

M66291 は、セットアップステージのデータパケット(ホスト PC からのリクエスト)を専用レジスタに格納しています。また、データステージのデータパケットは、エンドポイント 0 用 FIFO バッファを使用します。

コントロール転送の転送ステージと遷移時の処理を表 4-2に示します。

表 4-2 コントロール転送の転送ステージと遷移時の処理

| 転送ステージ               | 遷移時の処理                                  |

|----------------------|-----------------------------------------|

| アイドルまたはセットアップステージ    | 特に処理は不要(ユーザの必要に応じて処理を行って                |

|                      | ください)                                   |

| コントロールリード転送データステージ   | リクエストデータ解析                              |

|                      | データ送信準備(含む送信データ書き込み)                    |

| コントロールライト転送データステージ   | リクエストデータ解析                              |

|                      | データ受信準備                                 |

|                      | 受信データ読み出し                               |

| ノーデータコントロール転送        | リクエストデータ解析                              |

| ステータスステージ            | 2 2 · · · / / / / / / / / / / / / / / / |

| コントロールリード転送ステータスステージ | 特に処理は不要(ユーザの必要に応じて処理を行って                |

|                      | ください)                                   |

| コントロールライト転送ステータスステージ | 特に処理は不要(ユーザの必要に応じて処理を行って                |

|                      | ください)                                   |

| コントロール転送シーケンスエラー     | セットアップ再受信準備                             |

コントロールライト転送において、最終パケットを受信したことによるバッファレディ割り込みとステータスステージ遷移割り込みがほぼ同時に発生する場合がありますので、割り込み処理プログラムは、コントロール転送ステージ遷移割り込み処理の前にエンドポイント 0 バッファレディ割り込み処理を行うように設計してください。

図 4-5 ステータスステージ遷移処理

## 4.6. セットアップステージ

セットアップトランザクションにて、ホストから8バイトのリクエスト(セットアップステージのデー タパケット)が転送され、以下の4レジスタに格納されます。

| レジスタ名   | アドレス | ビット  | 格納値       |

|---------|------|------|-----------|

| Dogwood | 20h  | 15-8 | bRequest  |

| Request | 20H  | 7-0  | bmRequest |

| Value   | 22h  | 15-0 | wValue    |

| Index   | 24h  | 15-0 | wIndex    |

| Length  | 26h  | 15-0 | wLength   |

表 4-3 リクエスト格納レジスタ

リクエストをレジスタに格納した後、M66291 は VALID[セットアップパケット検出ビット]<sup>!</sup>='1'をセッ トし、CTSQ[コントロール転送ステージ] にコントロール転送ステージ管理機能により該当する値を設定 し、コントロール転送ステージ遷移割り込み(CTRT'='1')を発生させます。

制御プログラムは、VALID='0'を設定したのちに、リクエストをレジスタから読み出し、エラー判定、 リクエスト解析処理を施し、データステージの準備を行います。あるリクエストのデータステージ処理中、 あるいはステータスステージ処理中に新たなセットアップトランザクションが発生した場合には、それま でのリクエスト処理を中断し、新たなリクエスト処理を行なう必要があります。このため、コントロール 転送ステージ遷移割り込み処理の中では毎回必ず VALID の値を確認してください。

M66291 はセットアップトランザクションを正常受信すると自動的に"ACK"応答します。また、セット アップパケット受信後にエンドポイント 0の PID を自動的に"NAK"設定します。

コントロール転送遷移割り込み処理例を図 4-6に示します。

<sup>&</sup>lt;sup>1</sup> 割り込みステータスレジスタ 0 (Address 18h)

図 4-6 コントロール転送遷移割り込み処理例

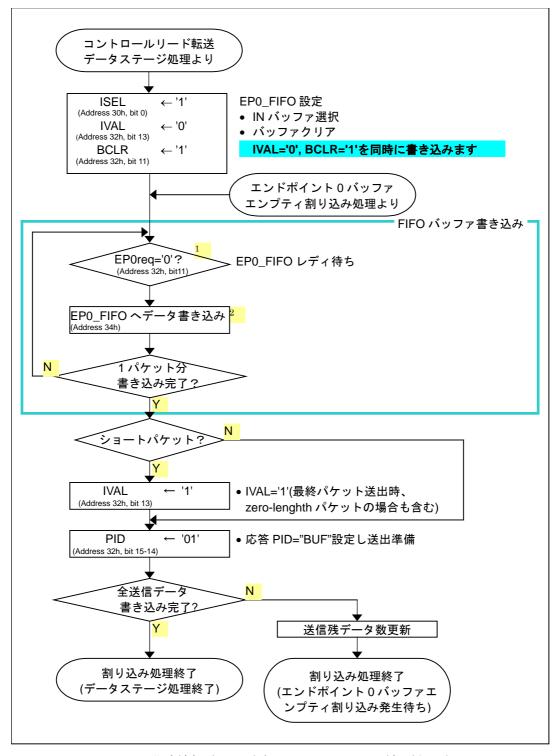

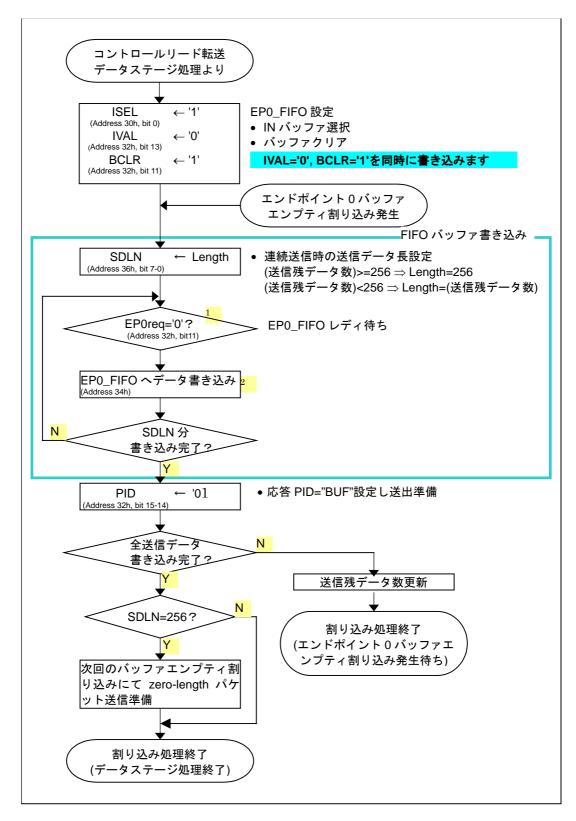

#### 4.7. コントロールリード転送データステージ処理例

セットアップステージにて受信したリクエストがコントロールリードリクエストの場合は、データステ ージにおいてホストPCに対してリクエストされたデータ送信を行ってください。

M66291 はコントロールリード時のデータ送信(データステージ)において連続転送機能を備えており、 設定を行えば、複数パケットの連続送信が可能になります。 設定可能な SDLN[コントロールリード連続送 信データ長] $^{1}$ の最大値は 256 バイトです。

連続送信設定の場合で、FIFO バッファに書き込んだデータ長が最大パケットサイズで割り切れ(最大パ ケットサイズの n 倍)、かつ、256 バイト未満の場合は、全データ送出後に自動的に zero-length パケット (Null パケット)送出の準備を行います。但し、FIFO バッファに書き込んだデータ長が 256 バイトの場合 は、自動的な zero-length パケット送出準備は行いませんので、制御プログラムで送出準備を行う必要が あります。非連続送信設定の場合に、最後のデータパケットが最大パケットサイズの場合にも、制御プロ グラムで zero-length パケット送出準備を行う必要があります。 $^2$

ショートパケット送信の場合など、FIFO 容量未満のデータ送信時は、最終データ書き込み後に IVAL='1' 設定を行いパケット送出準備を完了してください。M66291 はデータステージで OUT トークンを受信す ると、自動的にステータスステージにステージ遷移します。

非連続転送モード時コントロールリード転送処理例を図 4-7に、連続転送モード時コントロールリード 転送処理例を図 4-8に示します。

<sup>&</sup>lt;sup>1</sup> EP0 連続送信データ長レジスタ(Address 36h)

<sup>&</sup>lt;sup>2</sup> USB specification 1.1 5.2.2 章に次のような規定があるためです。

When all of the data structure is returned to the host, the function should indicate that the Data stage is ended by returning a packet that is shorter than the MaxPacketSize for the pipe. If the data structure is an exact multiple of wMaxPacketSize for the pipe, the funtion will return a zero-length packet to indicate the end of the Data stage.

図 4-7 非連続転送モード時コントロールリード転送処理例

- 1 FIFO データレジスタへのアクセスサイクルがデータシートを満たす場合は、この確認は省略可能です。

- <sup>2</sup> 16bit バス幅接続のシステムで、奇数バイト数のデータ書き込みを行う場合は、16 ビットモードで最後の1バイト 直前まで書き込みし、Octl='1'設定により 16bit→8bit に切り替えて最後の 1 バイトの書き込みを行います。16 ビ ットモード時にバイトスワップ機能(BSWP='1)を使用する場合は、BSWP='0'に戻してから Octl='1'設定を行ってく ださい。

図 4-8 連続転送モード時コントロールリード転送処理例

- 1 FIFO データレジスタへのアクセスサイクルがデータシートを満たす場合は、この確認は省略可能です。

- <sup>2</sup> 16bit バス幅接続のシステムで、奇数バイト数のデータ書き込みを行う場合は、16 ビットモードで最後の1 バイト 直前まで書き込みし、Octl='1'設定により 16bit→8bit に切り替えて最後の1 バイトの書き込みを行います。16 ビットモードにバイトスワップ機能(BSWP='1)を使用する場合は、BSWP='0'に戻してから Octl='1'設定を行ってください。

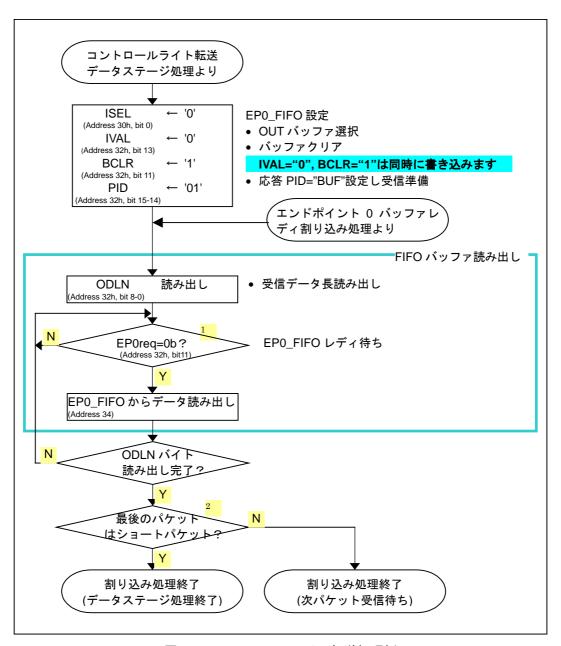

## 4.8. コントロールライト転送データステージ処理例

セットアップステージにて受信したリクエストがコントロールライトリクエストの場合は、データステージにおいてホスト PC よりリクエストされたデータ受信を行ってください。

M66291 はコントロールライト時のデータ受信(データステージ)において連続転送機能を備えており、設定を行えば、複数パケットの連続受信が可能になります。コントロール転送の連続受信時に設定できるバッファ領域は最大 256 バイトです。256 バイトを超えるデータを受信する場合は複数回にわけて受信・読み出しを行ってください。

M66291 はデータステージで IN トークンを受信すると、自動的にステータスステージにステージ遷移 します。

コントロールライト転送処理例を、図 4-9に示します。

図 4-9 コントロールライト転送処理例

- 1 FIFO データレジスタへのアクセスサイクルがデータシートを満たす場合は、この確認は省略可能です。

- <sup>2</sup> 16bit バス接続のシステムで ODLN が奇数の場合は、最後の 1 ワード(2 バイト)を読み出し後、上位 8 ビットを破棄してください。

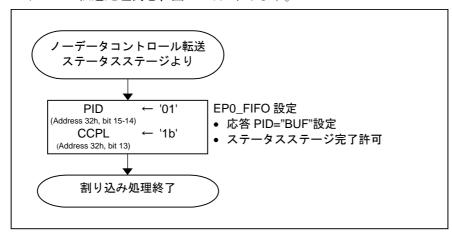

# 4.9. ノーデータコントロール転送処理(ステータスステージ)例

セットアップステージにて受信したリクエストがノーデータコントロール転送のリクエストの場合は、 セットアップステージ以降はホストPCとのデータ送受信は行いません。

M66291 はセットアップステージでノーデータコントロール転送のリクエストを受信すると、自動的にステータスステージにステージ遷移します。なお、ノーデータコントロール転送リクエストの判定には、bmRequestType 及び wLength フィールドを使用します。

M66291 はノーデータコントロール転送である標準リクエスト Set Address、Set Configuration に対して、CPU に割り込みを発生させずに転送を完了させることができます(自動応答機能)。

M66291 が SetAddress 自動応答を行うのは以下の条件を満たす場合のみです。その他のステートの Set Address リクエストに対しては自動応答を行いません。自動応答を行わない場合でも、M66291 は USB アドレスレジスタ(Address 08h)の更新は行います。

(1) デバイスステートがデフォルトステートで、Set Address リクエストを受信した。

M66291 が Set Configuration 自動応答を行うのは以下のいずれかの条件を満たす場合のみです。その他のステート、及び ConfigurationValue が下記と異なる Set Configuration リクエストに対しては自動 応答を行いません。

- (1) デバイスステートがアドレスステートで、Set Configuration リクエストを受信した。

- (2) デバイスステートが構成ステートで、Set Configuration リクエストを受信した。

ノーデータコントロール転送処理例を、図 4-10に示します。

図 4-10 ノーデータコントロール転送処理例

# 5. データ転送

## 5.1. データ転送概要

データ転送は片方向転送で、少なくとも2つのパケット(トークンパケット、データパケット)により構成されます。ホストとデバイス間のデータ転送をデータパケット再送機能により保証する転送では、データパケットの後ろにハンドシェークパケットが加わり、3パケット構成となります。転送種別は、ホストとデバイス間の通信エラーを検出せず、転送レートを保証する2パケット構成のアイソクロナス転送と、通信エラー検出行うが転送レートが保証されない3パケット構成のバルク転送、そして、通信エラー検出行い、転送レートを保証する3パケット構成のインタラプト転送の3種類があります。

データ転送タイプによる特徴は以下のとおりです。

転送タイプ バルク転送 インタラプト転送 アイソクロナス転送 実時間性 低い リアルタイム 高い 保証 保証 転送間隔 非保証 データ転送量 大量 少量 少量-大量 パケット数 3 Data0/Data1 Data0/Data1 Data パケット Data0 Handshake 有り 有り 無し 最大パケットサイズ 8, 16, 32, 64 0-640 - 1023M66291 の機能特性 使用禁止 使用禁止 連続送信機能1 有効 ダブルバッファ機能 有効 有効 有効 zero-length パケット自 有効(連続転送時) 使用禁止 使用禁止 動送信機能<sup>2</sup> DMA アクセス 有効 有効 有効

表 6-1 データ転送タイプ一覧

データ転送のトランザクションは次のように規定されています。

(1) バルク IN、インタラプト IN:

INトークン、データ(DATA0/1)及びハンドシェークパケットにより構成されます。

$$IN \vdash -2 \rightarrow DATA(0/1) \rightarrow ACK$$

(2) アイソクロナス IN:

INトークン及びデータ(DATA0)により構成されます。

$$|N|$$

トークン $\rightarrow DATA(0)$

(3) バルク OUT、インタラプト OUT:

OUTトークン、データ(DATA0/1)及びハンドシェークパケットにより構成されます。

OUT トークン

$$\rightarrow$$

DATA(0/1)  $\rightarrow$  ACK

(4) アイソクロナス OUT:

OUTトークン及びデータ(DATAO)により構成されます。

OUT トークン ightarrow DATA(0)

これら一連のトランザクションを IN(DATAO/1)、OUT(DATAO/1)と表記します。

¹ インタラプト転送、アイソクロナス転送設定時は、EPi\_RWMD[連続送受信モード]='0'に設定してください。

<sup>&</sup>lt;sup>2</sup> (バルク OUT 転送かつ EPi\_RWMD='1')の時以外は、EPi\_NULMD[zero-length パケット自動送信モード]='0'に設定してください。

各データ転送は次のようなトランザクション構成で通信が行われます。

(1) バルク IN 転送、インタラプト IN 転送:

IN(DATA0) IN(DATA1) IN(DATA0) IN(DATA1) ... IN(DATA0/1)

(2) アイソクロナス IN 転送:

IN(DATA0) IN(DATA0) IN(DATA0) IN(DATA0) ... IN(DATA0)

(3) バルク **OUT** 転送、インタラプト **OUT** 転送:

OUT(DATA0) OUT(DATA1) OUT(DATA0) OUT(DATA1) ... OUT(DATA0/1

(4) アイソクロナス OUT 転送:

OUT(DATA0) OUT(DATA0) OUT(DATA0) OUT(DATA0) ... OUT(DATA0)

#### 5.2. M66291 によるデータ転送の特徴

M66291 は、USB 通信で規定されている全タイプのデータ転送が可能です。また、各エンドポイント にて行うデータ転送プログラムが簡単に記述できるように以下の機能を備えています。

(1) 豊富なエンドポイント割り込み

【本資料*2.5、5.3*参照】

(2) 合計 3K バイトの FIFO バッファ

【本資料*2.6、5.4、5.5*参照】

(3) 連続送受信機能(バルク転送)

【本資料2.6参照】

(4) エンドポイント毎に転送条件が設定可能

【本資料2.6参照】

M66291 はダブルバッファ機能を備えています。ダブルバッファを使用する設定を行えば、デバイスが ホストとデータ通信中でも、FIFO バッファ空きを待つことなくバッファアクセスを行うことが可能です。 ダブルバッファ機能を使用することにより USB バスのトラフィックを向上させることができます。

また、M66291 はバルク転送に対し連続送受信機能を使用することができます。データ転送における連 続送受信機能は、最大 1K バイトまで割り込みを発生せずに連続してデータを送受信する機能です。連続 送受信機能を用いることで、バルク転送では1トランザクションごとに FIFO バッファアクセスを行う必 要がなくなり、CPU稼働率を高めることができます。

M66291 は、FIFO バッファがフルでホストからのデータを受信できない状態、または FIFO バッファ が空でホストからの IN トークンに対してデータ送信を行えない状態のときに、ホストからのトークンパ ケットを受信すると自動的に"NAK"応答を行います。

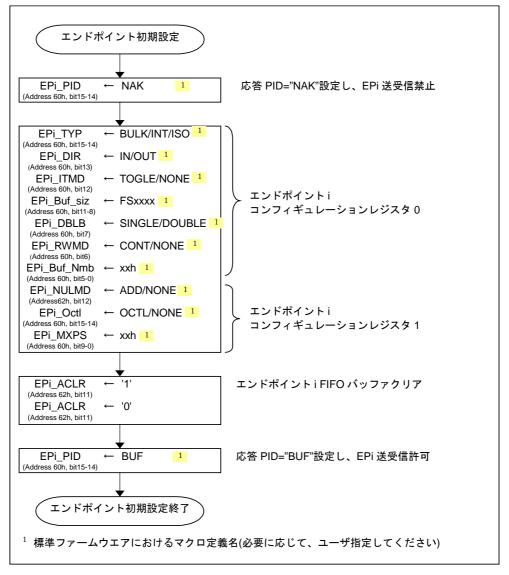

エンドポイント初期設定制御手順例を図 5-1に示します。

図 5-1 エンドポイント初期設定制御手順例

#### データ送受信割り込み 5.3.

M66291 はバッファレディ、バッファノットレディ、バッファエンプティの3種類のデータ転送割り込 み機能を備えています。また、各割り込みはステータスレジスタ 1-3 により、割り込み要因の発生したエ ンドポイントを認識することが可能です。データ転送割り込みは転送タイプ、転送方向及びアクセス方法 により発生要因が異なりますのでご注意ください。要因の差異に関しては2.5 データ転送割り込みを参照 ください。

データ送受信制御手順例を図 5-2に示します。

図 5-2 データ送受信制御手順例

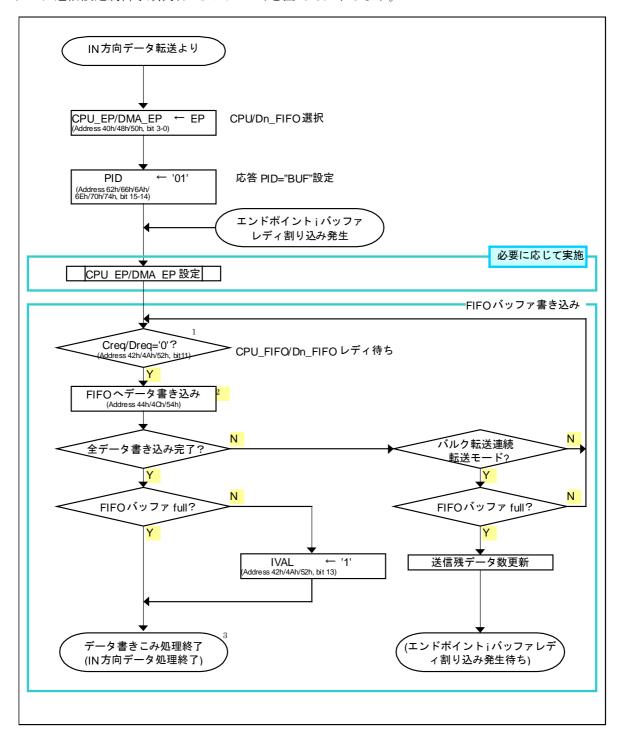

#### FIFO アクセス(データ送信:IN 方向) 5.4.

デバイス側に、ホストへの送信データが存在する場合は、IN トランザクションによりデータを送信し ます。USB 通信はホスト PC のサンプリングによりデータ転送が行われるため、デバイス側アプリケー ションは送信データが発生したら M66291 の FIFO バッファに送信するデータを書き込み、ホストからの INトークンを待ちます。データ送信が終了し、FIFO バッファに CPU 側からの書き込みが可能となった 時点で、M66291 は CPU に対してバッファレディ割り込みを通知します。要因の詳細に関しては2.5 デ *ータ転送割り込み*を参照ください。

データ送信設定制御手順例(CPU アクセス)を図 5-3に示します。

図 5-3 データ送信設定制御手順例(CPU アクセス)

- <sup>1</sup> FIFO データレジスタへのアクセスサイクルがデータシートを満たす場合は、この確認は省略可能です。

- <sup>2</sup> 16bit バス幅接続のシステムで、奇数バイト数のデータ書き込みを行う場合は、16 ビットモードで最後の 1 バイト

直前まで書き込みし、Octl='1'設定により  $16bit \rightarrow 8bit$  に切り替えて最後の 1 バイトの書き込みを行います。16 ビットモード時にバイトスワップ機能(BSWP='1)を使用する場合は、BSWP='0'に戻してから Octl='1'設定を行ってください。

3 バルク転送連続送信モードの場合、最後の1パケットがショートパケットではない場合に、アプリケーションによってはこの後の**エンドポイント** i **バッファレディ**割り込みで zero-length パケット送信準備が必要です。

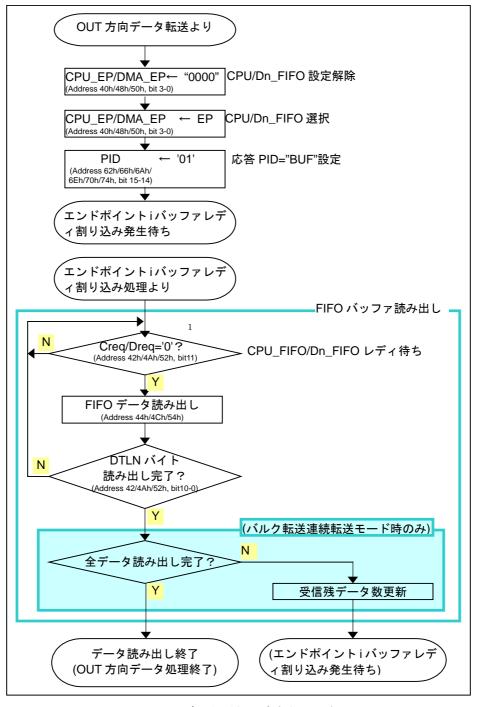

#### 5.5. FIFO アクセス(データ受信:OUT 方向)

デバイスがホスト PC からデータを受信する場合は、OUT トランザクションによりデータ転送を行い ます。USB 通信はホスト PC のサンプリングによりデータ転送が行われるため、デバイス側アプリケー ションでは、あらかじめ M66291 の FIFO バッファを空き状態(受信可能状態)にしておき、ホストからの OUT トークンを待つ処理を行ってください。M66291 は、受信完了により FIFO バッファの読み出しが 可能となったことを、CPU に対してバッファレディ割り込み発生させることによって通知します。(要因 の詳細に関しては*2.5 データ転送割り込み*を参照)

データ受信設定制御手順例を図 5-4に示します。

図 5-4 データ受信設定制御手順例

1 FIFO データレジスタへのアクセスサイクルがデータシートを満たす場合は、この確認は省略可能です。

# 6. USB 特殊処理

### 6.1. バスリセット信号処理

### 6.1.1. USB Specification 概要

デバイスは、USB バス上の USB バスリセット信号( $2.5 \mu s$  以上の SE0)を検出後、すでに割り振られた アドレスを Default アドレスに変更するとともに、Default ステートにステート遷移する必要があります。

### 6.1.2. M66291 の機能

USB バスリセット検出に伴う M66291 レジスタ初期化については、M66291 データシート【レジスター覧】を参照ください。

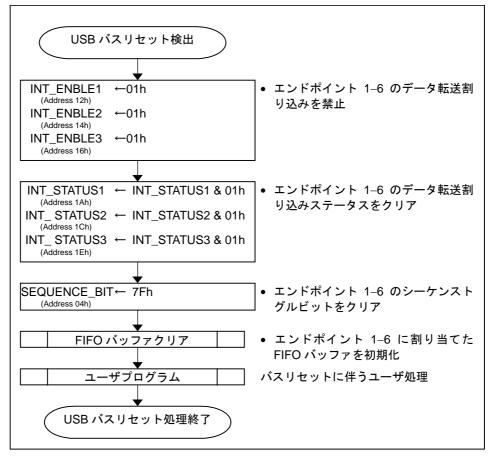

#### 6.1.3. デバイス側アプリケーションの動作

デバイス側アプリケーションは、USB バスリセット検出(デバイスステート遷移割り込み(DVSQ='001') 検出)後、ホストからのリクエスト(バスエニュメレーション)に応答する準備を行う必要があります。

USB バスリセット信号検出処理例を図 6-1に示します。

図 6-1 USB バスリセット信号検出処理例

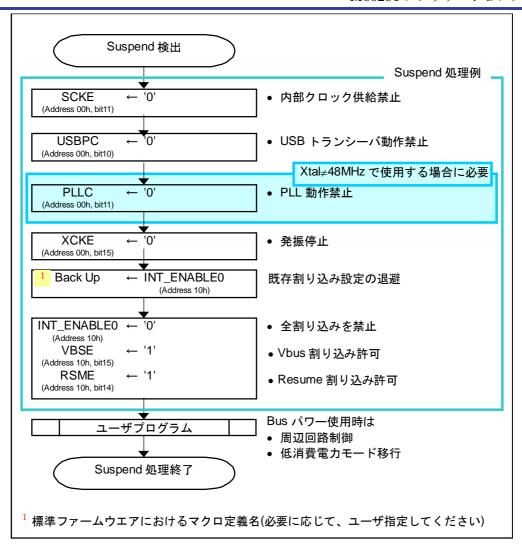

### 6.2. サスペンド信号処理

### 6.2.1. USB Specification 概要

USB バス上でサスペンド信号(3.0ms 以上のアイドル状態)を検出すると、デバイスは USB specification で規定されている任意のステートから Suspend ステートへ遷移を行う必要があります。また、Suspend ステートにあるデバイスは、通常 USB バスから  $500 \, \mu$  A 未満の電流しか引き出すことができません。

デバイスが Suspend ステートから復帰するためには、何らかのバス アクティビティが発生するか、リモートウェイクアップ機能を使用してホストに要求を行う必要があります。

#### 6.2.2. M66291 の機能

M66291 は、サスペンド信号を検出すると、Suspend ステートに遷移し、デバイスステート遷移割り込み(DVSQ='1xx')を発生させます。

M66291 自身の消費電力を小さくするために、以下の設定が有効です。具体的な消費電力値については、M66291 データシート【電気的特性】を参照ください。

- (1) 内部クロック供給禁止(SCKE='0')<sup>1</sup>

- (2) 発振バッファ停止(XCKE='0')<sup>1</sup>

- (3) USB トランシーバ動作禁止(USBPC='0')<sup>1</sup>

M66291 は内部クロック供給停止中、発振バッファ停止中、又は、USB トランシーバ動作禁止中にも、RESM 割り込みによるバス アクティビティを検出することが可能です。( $6.3~\nu$ ジューム (バス アクティビティ検出)、6.4~Suspend~ステート中の USB バスリセット検出を参照)

### 6.2.3. デバイス側アプリケーションの動作

デバイスが Bus powered を使用している場合、デバイス側アプリケーションは、サスペンド信号検出 (Suspend ステートへのデバイスステート遷移割り込み(DVSQ='1xx')検出)後、低消費電力モードに移行する必要があります。低消費電力モードに移行する場合、レジューム検出時にデバイス動作を通常に戻す必要があるため、レジューム検出が可能な設定(RESM割り込みの許可)を行ってください。

また、デバイスがリモートウェイクアップ機能をサポートしている場合は、システム仕様に従い、リモートウェイクアップ信号送出機能を実装する必要があります。*6.5 リモートウェイクアップ処理*も参照ください。

サスペンド検出処理例を図 6-2に示します。

<sup>&</sup>lt;sup>1</sup> USB 動作許可レジスタ(Address 00h)

図 6-2 サスペンド検出処理例

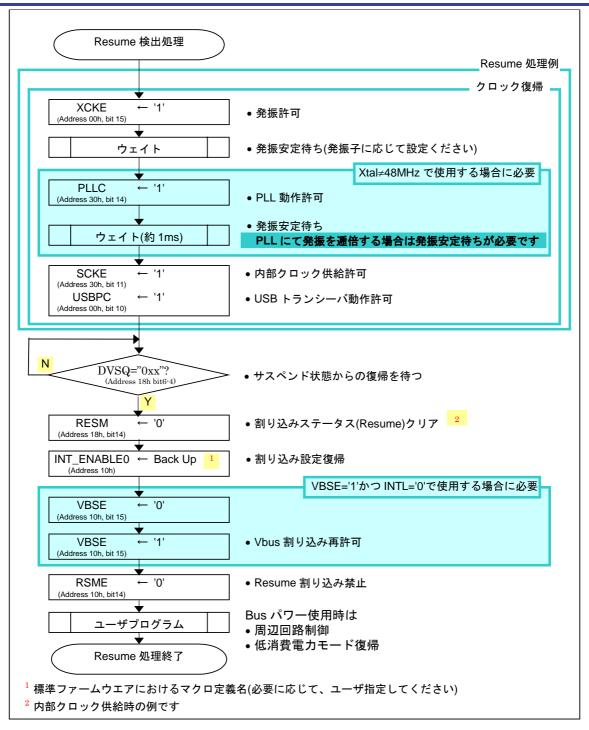

# 6.3. レジューム (バス アクティビティ検出)処理

### 6.3.1. USB Specification 概要

USB バスが Suspend 状態の時に USB バスの状態変化があった場合に、デバイスはレジュームを検出する必要があります。

### 6.3.2. M66291 の機能

デバイスステートが Suspend ステートである時に USB バスの状態変化("J" $\rightarrow$ "K"もしくは"SE0")を検出した場合に、M66291 はレジューム検出割り込み(RESM)を発生させ、サスペンド検出直前のデバイスステートに自動的に遷移します。

レジューム検出割り込みは USB バス状態の変化を検出しますので、M66291 の内部クロック供給停止中、発振バッファ停止中、又は、USB トランシーバ動作禁止中にも、RESM 割り込みによるバス アクティビティ検出が可能です。

### 6.3.3. デバイス側アプリケーションの動作

サスペンド時に低消費電力モードに移行する等の処理を行うシステムの場合、レジューム検出時にデバイス動作を通常に戻す必要があります。

また、レジューム検出割り込みのステータスフラグのクリア方法は、内部クロック供給時と停止時で異なりますのでご注意ください。

- (1) 内部クロック供給時: RESM='0'1を書き込んでください

- (2) 内部クロック停止時: RESM='0'、RESM='1'を連続して書き込んでください レジューム検出処理例を図 6-3に示します。

<sup>&</sup>lt;sup>1</sup> 割り込みステータスレジスタ 0(Address 18h)、bit14

図 6-3 レジューム検出処理例

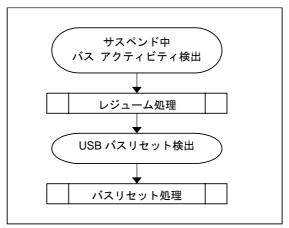

### 6.4. Suspend ステート中の USB バスリセット検出

### 6.4.1. USB Specification 概要

USB バスリセット信号もバス アクティビティの一種ですので、この場合、デバイスは、サスペンド状態からのレジューム、及び、USB バスリセット信号の検出を行う必要があります。

### 6.4.2. M66291 の機能

M66291 の内部クロック供給を停止している場合は、レジューム検出は行いますが、USB バスリセット信号の検出を行うことができません。したがって、Suspend ステート中に USB バスリセットが発生した場合は、以下のようなシーケンスとなります。

- (1) レジューム検出

- (2) FW によるレジューム処理(M66291 の内部クロック供給、USB トランシーバ動作等)

- (3) USB バスリセット検出(デバイスステート(DVSQ='001': Default)遷移割り込みを発生)

### 6.4.3. デバイス側アプリケーションの動作

デバイス側アプリケーションは、ホストからの USB リセット信号発行中に、レジューム処理を終わらせる必要があります。USB Specification によれば、ホスト PC が発行する USB バスリセット信号 10ms 以上に対し、デバイス側(M66291)が USB バスリセットを検出するために  $2.5\mu s$  必要ですので、レジューム検出後遅くても 9.975ms 以内に内部クロック復帰処理が終了するように処理タイミングを設計してください。

Suspend ステート中の USB バスリセット検出処理例を図 6-4に示します。

図 6-4 Suspend ステート中の USB バスリセット検出処理例

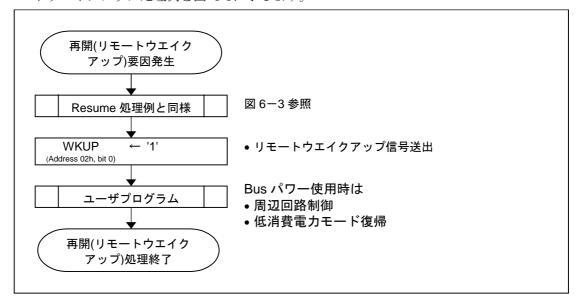

### 6.5. リモートウェイクアップ処理

### 6.5.1. USB Specification 概要

デバイスステートが Suspend ステートであるときに、デバイス側の要因により USB 通信を再開したい場合は、デバイスからリモートウェイクアップ信号を送出させホストに対してレジューム要求を促すことができます。

リモートウェイクアップ信号は、USBバスがアイドル状態に遷移した後、アイドル状態を 5ms のあいだ保持した後に出力する必要があります。また、リモートウェイクアップレジューム信号の出力期間は 1ms 以上 15ms 以内と定められています。

リモートウェイクアップ機能には使用条件があります。以下(1)、(2)を満たす場合のみ、デバイスはリモートウェイクアップを行うことができます。

- (1) 構成ステートから遷移した Suspend ステートでの使用であること

- (2) 当該デバイスに対し、SetFeature リクエストによって、リモートウェイクアップが許可されていること

### 6.5.2. M66291 の機能

M66291 のリモートウェイクアップ機能は、リモートウエイクアップ出力設定後、2ms 間のアイドルステートを保った後、10ms 間の K ステート出力を行います。Suspend 信号検出時点で USB バスがアイドル状態に遷移した後 3ms 経過しているため、上記 2ms 間のアイドル状態保持機能により、デバイス側アプリケーションが Suspend 検出直後にリモートウェイクアップ信号の出力設定を行ったとしても、バスアイドル 5ms 保持の規格を遵守することが可能です。

### 6.5.3. デバイス側アプリケーションの動作

デバイス要因により Suspend ステートからのレジュームを行いたい場合は、レジューム要因発生後レジューム検出割り込み発生時と同様の処理を行い、その後、リモートウエイクアップ出力処理を行います。 リモートウェイクアップ処理例を図 6-5に示します。

図 6-5 リモートウェイクアップ処理例

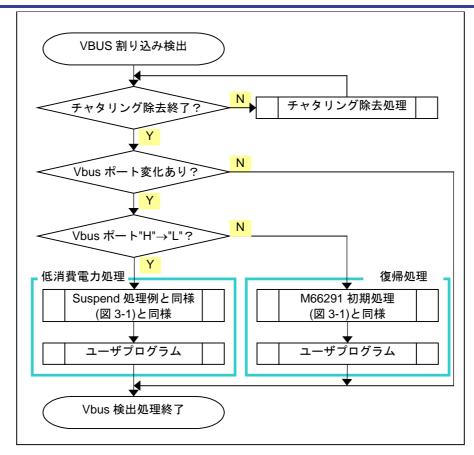

### 6.6. Vbus 変化の検出処理

### 6.6.1. USB Specification 概要

full speed デバイスは、VBUS 信号が 4.01V 以上になった後 100ms 以内に D+信号を pull up しなければなりません。ホストは、full speed デバイスの D+信号が pull up された後、少なくとも 100ms 待ってから(D+信号の状態が安定するのを待つため)、USB 通信を開始します。

デバイスは、VBUS が供給されていない時には、D+、D-信号を pull up してはいけません。

#### 6.6.2. M66291 の機能

M66291 は、Vbus 入力端子の状態変化を検出("H"→"L"、"L"→"H"両エッジを検出可能)した場合に Vbus 割り込みを発生(VBUS='1')させます。立ち上がり/立下りのどちらのエッジを検出したかは、Vbus 入力ビット(Vbus)で確認することが可能です。M66291 の内部クロック供給が停止されていても、M66291 は VBUS 割り込みを発生させることができ、Vbus 端子の状態を Vbus 入力ビットに反映させることができます。

M66291 の TrON 端子の出力は Vbus 端子の状態が反映されます。 Vbus 端子に USB コネクタの VBUS 信号を接続し、かつ、TrON 端子を使用して D+信号の pull up を行うデバイスの場合、self pawered デバイスであっても、USB ケーブルが抜かれた時に D+信号の pull up をやめるための特別な回路、FW 処理は不要です。

### 6.6.3. デバイス側アプリケーションの動作

USB ケーブルが抜かれた場合に何らかの処理が必要なシステム(self powered で Vbus 供給がない場合に消費電力を落とす必要がある、又は、bus powered で電源 off の前に処理を行う必要がある等のシステム)では、USB ケーブルの挿抜を Vbus 入力端子の状態変化で検出し、処理を行う必要があります。

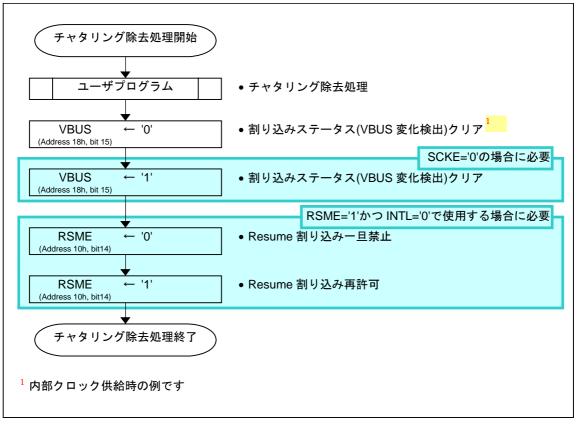

Vbus 検出処理例を図 6-6に示します。省電力処理/復帰処理は消費電力を小さくする場合の例です。

Vbus 割り込みを使用する場合は、M66291 の初期処理の中で、Vbus 割り込みを許可(VBSE='1')する必要があります。なお、Vbus 入力ビット(Vbus)はチャタリング除去のうえ状態確認を行う必要があります。チャタリング除去処理の中で、VBUS(Vbus 割り込みステータスビット)のクリアを行ってください。

また、VBUS割り込みのステータスフラグのクリア方法は、内部クロック供給時と停止時で異なりますのでご注意ください。

- (1) 内部クロック供給時: VBUS='0'<sup>1</sup>を書き込んでください

- (2) 内部クロック停止時: VBUS='0'、VBUS='1'を連続して書き込んでください

VBUS クリア処理例を図 6-7に示します。

<sup>&</sup>lt;sup>1</sup> 割り込みステータスレジスタ 0(Address 18h)、bit15

図 6-6 Vbus 検出処理例

図 6-7 VBUS クリア処理例

# 7. 応用例

#### CPU との接続方法(16bit バス幅) 7.1.

M66291 が接続される CPU からのアクセスについて考える場合、CPU のエンディアンが問題になりま す。M66291に接続が想定される CPU のエンディアンを表 7-1に列挙します。

| No. | ビット<br>エンディアン | バイト<br>エンディアン | CPU 例                         |

|-----|---------------|---------------|-------------------------------|

| 1   | リトル           | リトル           | 7700 シリーズ、7900 シリーズ、M16C ファミリ |

|     |               |               | SH ファミリなど                     |

| 2   | リトル           | ビッグ           | H8 シリーズ、他社マイコン                |

| 3   | ビック           | リトル           | (一般的ではないので掲載省略)               |

| 4   | ビック           | ビック           | M32R ファミリ                     |

表 7-1 M66291 に接続が想定される CPU とそのエンディアン

この章では、16bit バス幅での各 CPU と M66291 との結線方法、及びアクセス方法について説明しま す。M66291 へのアクセスは、レジスタへのアクセス、FIFO バッファへのアクセスに大別され、FIFO バッファへのアクセスには、CPU によるアクセスと DMA 転送によるアクセスがあります。また、奇数 バイト数のデータを FIFO バッファに書きこむ場合の 1 バイトアクセスについての考察も述べます(奇数 バイト数データの読み出しについては、2.6 FIFO 制御、2.7.2 16bit バス幅接続時に Dn\_FIFO データレ ジスタで奇数バイト数データの読み出し/書き込みを行う方法を参照ください)。

各種エンディアンの CPU と M66291 の接続性を表 7-2にまとめます。

| エンディアン |     | 接続方法        | BSWP             | アク セス <sup>1</sup> |      |

|--------|-----|-------------|------------------|--------------------|------|

| ビット    | バイト |             | 設定值 <sup>2</sup> | レジスタ               | FIFO |

| リトル    | リトル | 7.1.1章の方法   | '0'              | ok                 | ok   |

| リトル    | ビッグ | 7.1.2.1章の方法 | '1'              | ok                 | ok   |

|        |     | 7.1.2.2章の方法 | '0'              | invert             | ok   |

| ビッグ    | ビッグ | 7.1.3.1章の方法 | '1'              | ok ok              |      |

|        |     | 7.1.3.2章の方法 | '0'              | invert             | ok   |

表 7-2 PU のエンディアンによる M66291 の接続性(16bit 接続時)

M66291 と CPU を結線するときに、データのバイト単位での逆転がなく、ありのままで転送できるか どうかは大きな問題です。M66291では、プログラムを工夫することによりこの問題を解決することが可 能です。

実際に設計されるときは、お客様の使い方にあわせて結線方法を選択する必要があります。

ok:データのありまま読み出せる、或いは書き込めることを示します。 invert:バイトが逆転して読み出せる、或いは書き込めることを示します。

<sup>16</sup>bit アクセス時の設定値を示します(8bit アクセス時は必ず BSWP='0'に設定してください)。

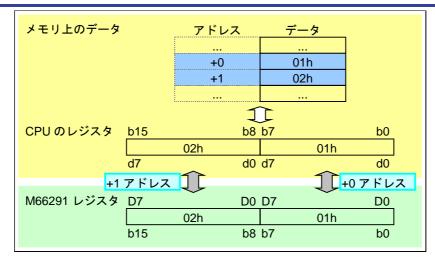

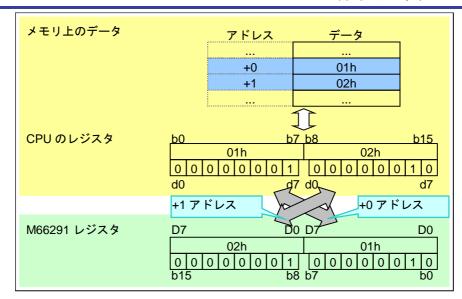

### 7.1.1. ビットエンディアンがリトル、バイトエンディアンがリトルの CPU の場合(16bit バス幅)

ルネサスの 7700 シリーズ、7900 シリーズ、M16C ファミリ、SH ファミリなどはこの種類の CPU で す。

### <接続>

図 7-1 ビットエンディアン:リトル、バイトエンディアン:リトルの接続例(16bit バス幅)

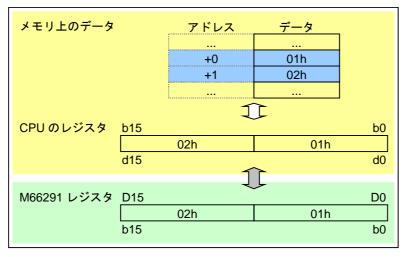

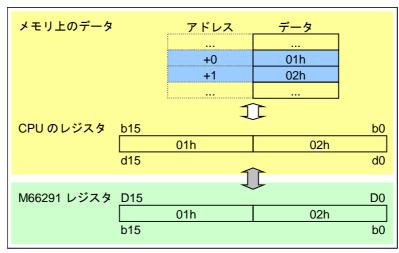

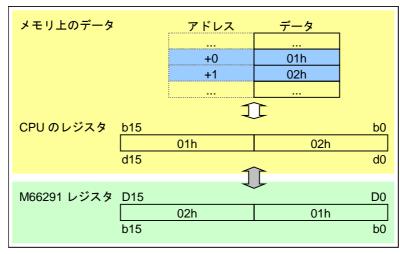

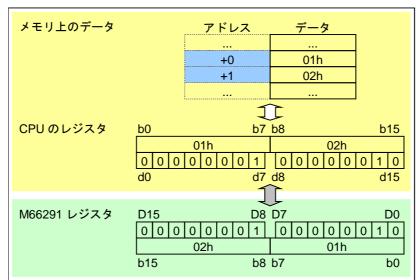

### <レジスタアクセス(FIFO\_DATA レジスタ以外)>

読み出し:M66291のレジスタのデータがそのまま、CPUのレジスタ或いはメモリに読み出されます。 書き込み:CPUのレジスタ或いはメモリ上のデータがそのまま、M66291のレジスタに書き込まれます。

図 7-2 ビットエンディアン:リトル、バイトエンディアン:リトル のレジスタアクセスイメージ(16bit バス幅)

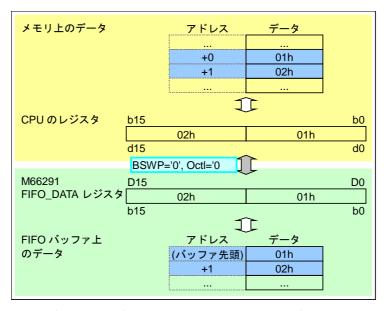

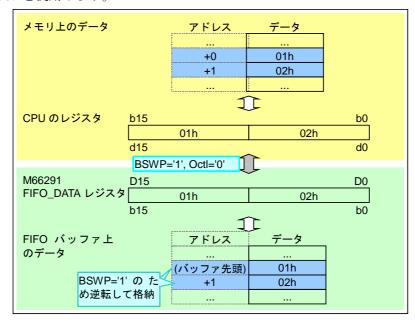

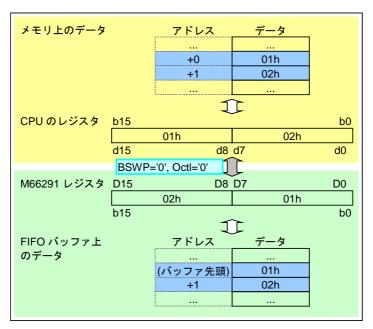

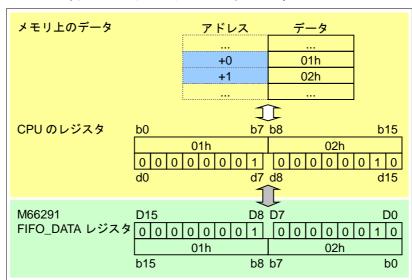

### <FIFO バッファ(FIFO\_DATA レジスタ)アクセス>

(1) M66291 の FIFO に対する CPU アクセス

基本的に、BSWP(バイトスワップモード;Address 40h, bit 12)='0'、Octl(レジスタ8bitモード;Address 40h, bit 6)¹='0'を設定してアクセスします。

奇数バイト数データの最後の1バイトのみ、BSWP='0'、Octl='1'を設定し、CPUのd7-d0に有効デー タを、CPUのd15-d8にダミーデータを出力し、16ビット単位で書き込みます。

読み出し:M66291のFIFOレジスタから読み出したデータがそのまま、順番にメモリに格納されます。 書き込み:メモリに格納されたデータがそのまま、順番にM66291のFIFOバッファに書き込まれます。

(2) M66291 の FIFO に対する DMA アクセス

CPUアクセスと同様です。但し、BSWP、Octlは、Dn\_FIFO選択レジスタ(Address 48h or 50h, bit 12) 上のBSWP、Octl<sup>2</sup>を使用します。

図 7-3 ビットエンディアン:リトル、バイトエンディアン:リトル の FIFO バッファアクセスイメージ 1(16bit バス幅、16 ビットアクセス)

Octl(Address 40h, bit 6)と、EPi\_Octl(Address (62+(i-1)\*2)h, bit 10)(i は CPU\_EP(Address 40h, bit 3-0)で設定して いるエンドポイント)は"or"で反映されます。どちらか一方が'1'に設定されますと、当該エンドポイントの FIFO バ ッファアクセスは8ビットモードになります。

Octl(Address 48h or 50h, bit 6) & EPi\_Octl(Address (62+(i-1)\*2)h, bit 10)(i l DMA\_EP(Address 48h or 50h, bit 3-0) で設定しているエンドポイント)は"or"で反映されます。

図 7-4 ビットエンディアン:リトル、バイトエンディアン:リトル の FIFO バッファアクセス 2(16bit バス幅、バイト書き込み)

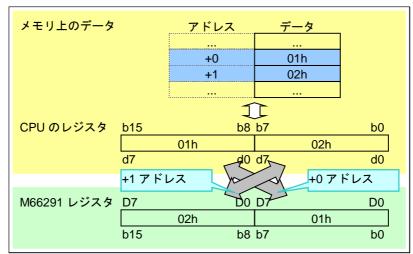

### 7.1.2. ビットエンディアンがリトル、バイトエンディアンがビッグの場合(16bit バス幅)

ルネサスの H8 シリーズなどはこの種類の CPU があります。M66291 との接続を考える場合には、基 本的には方法(1)(7.1.2.1章)を推奨します。参考資料として方法(2)(7.1.2.2章)を併記します。

# 7.1.2.1. ビットエンディアンがリトル、バイトエンディアンがビッグの場合(16bit バス幅) (1) <接続>

図 7-5 ビットエンディアン:リトル、バイトエンディアン:ビッグの接続図(16bit バス幅) (1)

### <レジスタアクセス(FIFO DATA レジスタ以外)>

読み出し: M66291のレジスタのデータがそのまま、CPUのレジスタ或いはメモリに読み出されます。 書き込み: CPUのレジスタ或いはメモリ上のデータがそのまま、M66291のレジスタに書き込まれます。

図 7-6 ビットエンディアン:リトル、バイトエンディアン:ビッグ のレジスタアクセスイメージ(16bit バス幅)(1)

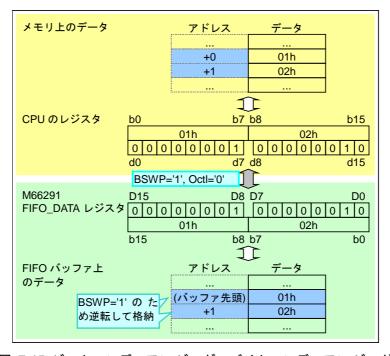

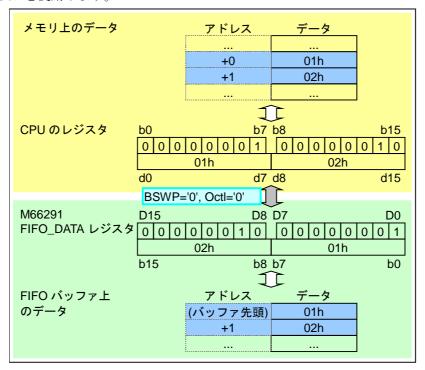

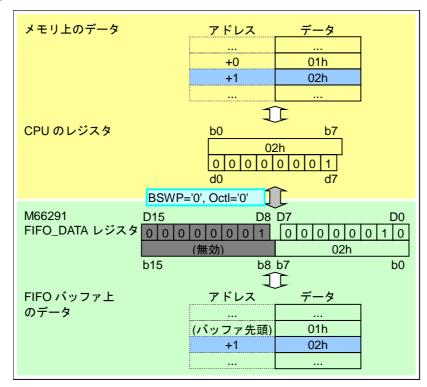

### <FIFO バッファ(FIFO\_DATA レジスタ)アクセス>

(1) M66291 の FIFO に対する CPU アクセス

基本的にBSWP(バイトスワップモード;Address 40h, bit 12)='1'、Octl(レジスタ8bitモード;Address 40h, bit 6)¹='0'を設定してアクセスします。BSWP='1'の場合、CPU FIFO-FIFOバッファ間のデータ転 送時にM66291内部でバイト単位で上位・下位を入れ替えます。即ち、読み出し時はFIFOバッファの 下位バイトがD15-D8に、上位バイトがD7-0に読み出されます。書き込み時は、D15-D8のデータが FIFOバッファの下位バイトに、D7-D0のデータが上位バイトに書き込まれます。

奇数バイト数データの最後の1バイトのみ、BSWP='0'、かつOctl='1'を設定し、CPUのD7-D0に有効 なデータを、CPUのD15-D8にダミーデータを出力し、16ビット単位で書き込みます。

読み出し: M66291のFIFOバッファに格納された順番で、メモリに格納されます。

書き込み: メモリに格納された順番で、M66291のFIFOバッファに格納されます。

(2) M66291 の FIFO に対する DMA アクセス

CPUアクセスと同様です。但し、BSWP、Octlは、Dn\_FIFO選択レジスタ(Address 48h or 50h, bit 12) 上のBSWP、Octl<sup>2</sup>を使用します。

図 7-7 ビットエンディアン:リトル、バイトエンディアン:ビッグ の FIFO バッファアクセスイメージ(16bit バス幅)(1) (16 ビットアクセス)

Octl(Address 40h, bit 6)と、EPi\_Octl(Address (62+(i-1)\*2)h, bit 10)(i は CPU\_EP(Address 40h, bit 3-0)で設定して いるエンドポイント)は"or"で反映されます。どちらか一方が'1'に設定されますと、当該エンドポイントの FIFO バ ッファアクセスは8ビットモードになります。

Octl(Address 48h or 50h, bit 6) & EPi\_Octl(Address (62+(i-1)\*2)h, bit 10)(i l DMA\_EP(Address 48h or 50h, bit 3-0) で設定しているエンドポイント)は"or"で反映されます。

図 7-8 ビットエンディアン:リトル、バイトエンディアン:ビッグ の FIFO バッファアクセスイメージ(16bit バス幅)(1) (バイト書き込み)

# 7.1.2.2. ビットエンディアンがリトル、バイトエンディアンがビッグの場合(16bit バス幅) (2) <接続>

図 7-9 ビットエンディアン:リトル、バイトエンディアン:ビッグの接続図(16bit バス幅) (2)

### <レジスタアクセス(FIFO\_DATA レジスタ以外)>

読み出し: M66291のレジスタのデータがバイト単位で逆転して、CPUのレジスタ或いはメモリに読み 出されます。

書き込み: CPUのレジスタ或いはメモリ上のデータがバイト単位で逆転して、M66291のレジスタに書 き込まれます。

図 7-10 ビットエンディアン:リトル、バイトエンディアン:ビッグ のレジスタアクセスイメージ(16bit バス幅)(2)

### <FIFO バッファ(FIFO\_DATA レジスタ)アクセス>

### (1) M66291 の FIFO に対する CPU アクセス

基本的にBSWP(バイトスワップモード;Address 40h, bit 12)='0'、Octl(レジスタ8bitモード;Address 40h, bit 6)¹='0'の設定でアクセスします。奇数バイト数書き込み時の最後の1バイトのみ、BSWP='0'、 かつOct|='1'を設定し、CPUのD15-D8に有効なデータを、CPUのD7-D0にダミーデータを出力し、16 ビット単位で書き込みます。

読み出し: M66291のFIFOバッファに格納された順番で、メモリに格納されます。 書き込み: メモリに格納された順番で、M66291のFIFOバッファに格納されます。

### (2) M66291 の FIFO に対する DMA アクセス

CPUアクセスと同様です。但し、BSWP、Octlは、Dn FIFO選択レジスタ(Address 48h or 50h, bit 12) 上のBSWP、Octl<sup>2</sup>を使用します。

図 7-11 ビットエンディアン:リトル、バイトエンディアン:ビッグ の FIFO バッファアクセスイメージ(16bit バス幅)(2) (16 ビットアクセス)

Octl(Address 40h, bit 6)と、EPi\_Octl(Address (62+(i-1)\*2)h, bit 10)(i は CPU\_EP(Address 40h, bit 3-0)で設定して いるエンドポイント)は"or"で反映されます。どちらか一方が'1'に設定されますと、当該エンドポイントの FIFO バ ッファアクセスは8ビットモードになります。

Octl(Address 48h or 50h, bit 6) & EPi\_Octl(Address (62+(i-1)\*2)h, bit 10)(i l DMA\_EP(Address 48h or 50h, bit 3-0) で設定しているエンドポイント)は"or"で反映されます。

図 7-12 ビットエンディアン:リトル、バイトエンディアン:ビッグの FIFO バッファアクセスイメージ(16bit バス幅)(2) (バイト書き込み)

### 7.1.3. ビットエンディアンがビッグ、バイトエンディアンがビッグの場合(16bit バス幅)

ルネサスの M32R ファミリなどはこの種類の CPU です。M66291 との接続を考える場合には、基本的 には方法(1)(7.1.3.1章)の方法を推奨します。参考資料として方法(2)(7.1.3.2章)を併記します。

# 7.1.3.1. ビットエンディアンがビッグ、バイトエンディアンがビッグの場合(16bit バス幅) (1) <接続>

図 7-13 ビットエンディアン:ビッグ、バイトエンディアン:ビッグの接続例(16bit バス幅) (1)

### <レジスタアクセス(FIFO DATA レジスタ以外)>

読み出し:M66291のレジスタのデータがそのまま、CPUのレジスタ或いはメモリに読み出されます。 書き込み:CPUのレジスタ或いはメモリ上のデータがそのまま、M66291のレジスタに書き込まれます。

図 7-14 ビットエンディアン:ビッグ、バイトエンディアン:ビッグ のレジスタアクセスイメージ(16bit バス幅)(1)

### <FIFO バッファ(FIFO DATA レジスタ)アクセス>

### (1) M66291 の FIFO に対する CPU アクセス

基本的にBSWP(バイトスワップモード;Address 40h, bit 12)='1'、Octl(レジスタ8bitモード;Address 40h, bit 6)'='0'の設定でアクセスします。BSWP='1'の場合、CPU\_FIFO-FIFOバッファ間のデータ転送時にM66291内部でバイト単位で上位/下位を入れ替えます。即ち、読み出し時はFIFOバッファの下位バイトがM66291のD15-D8に、上位バイトがM66291のD7-D0に読み出されます。書き込み時は、M66291のD15-D8のデータがFIFOバッファの下位バイトに、M66291のD7-D0のデータが上位バイトに書き込まれます。

奇数バイト数データの最後の1バイトのみ、BSWP='0'、かつOctl='1'を設定し、CPUのD15-D8に有効なデータを、CPUのD7-D0にダミーデータを出力し、16ビット単位で書き込みます。

読み出し: M66291のFIFOバッファに格納された順番で、メモリに格納されます。

書き込み: メモリに格納された順番で、M66291のFIFOバッファに格納されます。

### (2) M66291 の FIFO に対する DMA アクセス

CPUアクセスと同様です。但し、BSWP、Octlは、Dn\_FIFO選択レジスタ(Address 48h or 50h, bit 12) 上のBSWP、Octl<sup>2</sup>を使用します。

図 7-15 ビットエンディアン:ビッグ、バイトエンディアン:ビッグ の FIFO バッファアクセスイメージ(16bit バス幅)(1) (16 ビットアクセス)

Octl(Address 40h, bit 6)と、EPi\_Octl(Address (62+(i-1)\*2)h, bit 10)(i は CPU\_EP(Address 40h, bit 3-0)で設定しているエンドポイント)は"or"で反映されます。どちらか一方が'1'に設定されますと、当該エンドポイントの FIFO バッファアクセスは 8 ビットモードになります。

<sup>&</sup>lt;sup>2</sup> Octl(Address 48h or 50h, bit 6)と、EPi\_Octl(Address (62+(i-1)\*2)h, bit 10)(iは DMA\_EP(Address 48h or 50h, bit 3-0) で設定しているエンドポイント)は"or"で反映されます。

図 7-16 ビットエンディアン:リトル、バイトエンディアン:ビッグの FIFO バッファアクセスイメージ(16bit バス幅)(1) (バイト書き込み)

### 7.1.3.2. ビットエンディアンがビッグ、バイトエンディアンがビッグの場合(16bit バス幅)(2) <接続>

図 7-17 ビットエンディアン:ビッグ、バイトエンディアン:ビッグの接続例(16bit バス幅) (2)

### <レジスタアクセス(FIFO\_DATA レジスタ以外)>

読み出し: M66291のレジスタのデータがバイト単位で逆転して、CPUのレジスタ或いはメモリに読み 出されます。

書き込み: CPUのレジスタ或いはメモリ上のデータがバイト単位で逆転して、M66291のレジスタに書 き込まれます。

図 7-18 ビットエンディアン:ビッグ、バイトエンディアン:ビッグ のレジスタアクセスイメージ(16bit バス幅)(2)

### <FIFO バッファ(FIFO\_DATA レジスタ)アクセス>

(1) M66291 の FIFO に対する CPU アクセス

基本的にBSWP(バイトスワップモード;Address 40h, bit 12)='0'、Octl(レジスタ8bitモード;Address 40h, bit 6)¹='0'の設定でアクセスします。奇数バイト数書き込み時の最後の1バイトのみ、BSWP='0'、 かつOctl='1'を設定し、CPUのd0-d7に有効なデータを、CPUのd8-D15にダミーデータを出力し、16 ビット単位で書き込みます。

読み出し: M66291のFIFOバッファに格納された順番で、メモリに格納されます。

書き込み: メモリに格納された順番で、M66291のFIFOバッファに格納されます。

(2) M66291 の FIFO に対する DMA アクセス

CPUアクセスと同様です。但し、BSWP、OctIは、Dn\_FIFO選択レジスタ(Address 48h or 50h, bit 12) 上のBSWP、Octl<sup>2</sup>を使用します。

図 7-19 ビットエンディアン:ビッグ、バイトエンディアン:ビッグ の FIFO バッファアクセスイメージ(16bit バス幅)(2) (16 ビットアクセス)

Octl(Address 40h, bit 6)と、EPi\_Octl(Address (62+(i-1)\*2)h, bit 10)(i は CPU\_EP(Address 40h, bit 3-0)で設定して いるエンドポイント)は"or"で反映されます。どちらか一方が'1'に設定されますと、当該エンドポイントの FIFO バ ッファアクセスは8ビットモードになります。

Octl(Address 48h or 50h, bit 6) & EPi\_Octl(Address (62+(i-1)\*2)h, bit 10)(i は DMA\_EP(Address 48h or 50h, bit 3-0) で設定しているエンドポイント)は"or"で反映されます。

図 7-20 ビットエンディアン:ビッグ、バイトエンディアン:ビッグの FIFO バッファアクセスイメージ(16bit バス幅)(2) (バイト書き込み)

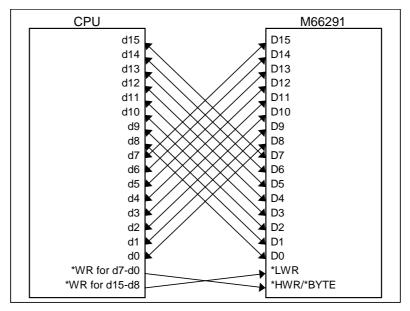

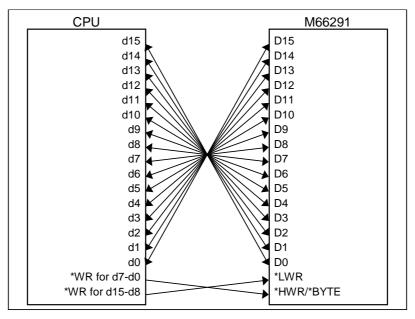

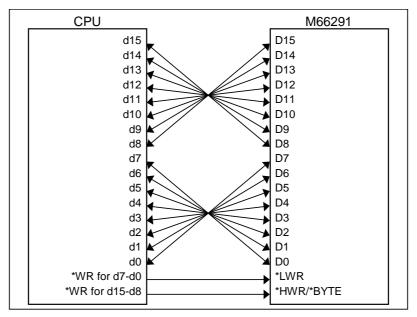

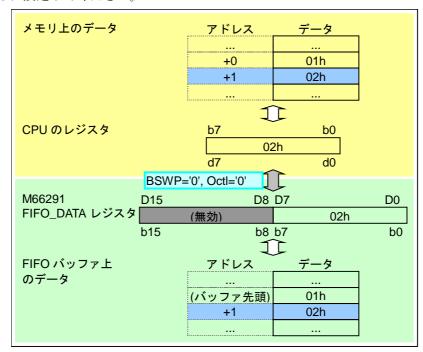

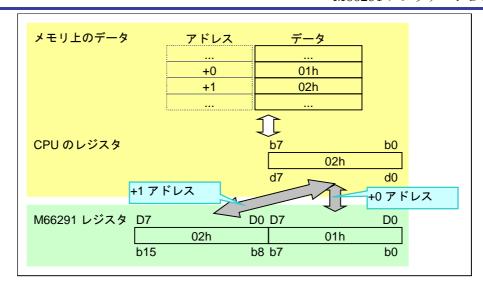

#### 7.2. CPU との接続方法(8bit バス幅)

この章では、8bit バス幅での各 CPU と M66291 との結線方法、及びアクセス方法について説明します。 CPU とエンディアンの種類については、表 7-1を参照ください。M66291 へのアクセスは、レジスタへ のアクセス、FIFO バッファへのアクセスに大別され、FIFO バッファへのアクセスには、CPU によるア クセスと DMA 転送によるアクセスがあります。

8bit バス幅接続の場合、FIFO バッファへのアクセス方法は接続方法によらず共通となります。FIFO バッファへのアクセスイメージを7.2.1 外部 8bit バス幅の場合の FIFO バッファアクセスに示します。 FIFOバッファへのアクセスは常にバイト単位で行ってください。

16 ビットアクセス可能な CPU と M66291 が 8bit バス幅で接続される場合のレジスタアクセスについ ては、CPU のエンディアンを考慮する必要があります。レジスタへのアクセスイメージについて7.2.2章 -7.2.5章に示します。各種エンディアンの CPU と M66291 の接続性を表 7·2にまとめます。

| CPU のエンディアン |     | CPU からの 接続方法 |           | BSWP             | アクセス <sup>1</sup> |      |

|-------------|-----|--------------|-----------|------------------|-------------------|------|

| ビット         | バイト | 16bit アクセス可否 |           | 設定値 <sup>2</sup> | レジスタ              | FIFO |

| リトル         | リトル | 可の CPU       | 7.2.2章の方法 | '0'              | ok                | ok   |

| リトル         | ビッグ | 可の CPU       | 7.2.3章の方法 | '0'              | invert            | ok   |

| リトル         | _   | 不可の CPU      | 7.2.4章の方法 | '0'              | ok                | ok   |

| ビッグ         | ビッグ | 可の CPU       | 7.2.5章の方法 | '0'              | invert            | ok   |

| _           | ビッグ | 不可の CPU      | 検討省略      | _                | _                 | _    |

表 7-3 CPU のエンディアンによる M66291 の接続性(8bit バス幅接続時)

実際に設計されるときは、お客様の使い方にあわせて結線方法を選択する必要があります。

ok:データのありまま読み出せる、或いは書き込めることを示します。 invert:バイトが逆転して読み出せる、或いは書き込めることを示します。

<sup>8</sup>bit バス幅接続の場合は、BSWP='0'に固定して使用してください。

### 7.2.1. 外部 8bit バス幅の場合の FIFO バッファアクセス

(1) M66291 の FIFO に対する CPU アクセス

BSWP(バイトスワップモード;Address 40h, bit 12)='0'の設定でアクセスします。常に8ビットの変数 /レジスタを使用し、M66291のFIFOレジスタのb7-b0に対してアクセスしてください(即ち、偶数アドレスのみにアクセスしてください)。

読み出し: M66291のFIFOバッファに格納された順番で、メモリに格納されます。

書き込み: メモリに格納された順番で、M66291のFIFOバッファに格納されます。

(2) M66291 の FIFO に対する DMA アクセス

CPUアクセスと同様です。DMACの転送単位をバイトに指定してください。BSWP(Address 48h or 50h, bit 12) ='0'に設定してください。

図 7-21 FIFO バッファアクセスイメージ(8bit バス幅)

# 7.2.2. ビットエンディアンがリトル、バイトエンディアンがリトルの CPU の場合(8bit バス幅) <接続>

図 7-22 ビットエンディアン:リトルの接続例(8bit バス幅)

<レジスタアクセスイメージ>

FIFO\_DATA レジスタ以外のレジスタを CPU 内部で 16 ビットで扱う場合、CPU の下位バイト(D7–D0) が M66291 の偶数アドレスに、CPU の上位バイト(b15–b8)が M66291 の奇数アドレスにアクセスします。

図 7-23 ビットエンディアン:リトル、バイトエンディアン:リトル のレジスタアクセスイメージ(8bit バス幅) (CPU 内部 16 ビット)

# 7.2.3. ビットエンディアンがリトル、バイトエンディアンがビッグの CPU の場合

<接続>

図 7-22と同様です。

### <レジスタアクセスイメージ>

FIFO レジスタ以外のレジスタについて CPU内部で 16 ビットで扱う場合、CPU の下位バイト(b15-b8) が M66291 の偶数アドレスに、CPU の上位バイト(b7-b0)が M66291 の奇数アドレスに対してアクセスします。

図 7-24 外部 8bit バス幅、ビットエンディアン:リトル、バイトエンディアン:ビッグ のレジスタアクセスイメージ(8bit バス幅) (CPU 内部 16 ビット)

### 7.2.4. 内部 8 ビット、ビットエンディアンがリトルの CPU の場合

<接続>

図 7-22と同様です。

<レジスタアクセスイメージ>

図 7-25 外部 8bit バス幅、ビットエンディアン:リトル、バイトエンディアン:リトル のレジスタアクセスイメージ 1(CPU 内部 16 ビットの場合)

# 7.2.5. ビットエンディアンがビッグ、バイトエンディアンがリトルの CPU の場合 <接続>

図 7-26 外部 8bit バス幅、ビットエンディアン:ビッグの接続例

### <レジスタアクセス>

FIFO レジスタ以外のレジスタについては、CPU の上位バイト(b7-b0)が M66291 の偶数アドレスに、 CPU の下位バイト(b15-b8)が M66291 の奇数アドレスにアクセスします。

M66291のレジスタのデータがバイト単位で逆転して、CPUのレジスタ或いはメモリ 読み出し: に読み出されます。

書き込み: CPUのレジスタ或いはメモリ上のデータががバイト単位で逆転して、M66291のレジスタに 書き込まれます。

図 7-27 外部 8bit バス幅、ビットエンディアン:ビッグ、バイトエンディアン:ビッグ のレジスタアクセスイメージ(CPU 内部 16 ビットの場合)

### 7.2.6. 内部 8 ビット、ビットエンディアンがビッグの CPU の場合

### <接続>

図 7-26と同様です。

<データ転送例>

図 7-28 ビットエンディアン:ビッグ、バイトエンディアン:ビッグ のレジスタアクセスイメージ(CPU 内部 16 ビット)

### <アクセス方法>

(1) M66291 のレジスタに対する CPU アクセス

M66291のレジスタのb7-b0に対しては偶数アドレスで、b15-b8に対しては奇数アドレスでアクセスしてください。

### (2) M66291 の FIFO に対する CPU アクセス

BSWP(バイトスワップモード;Address 40h, bit 12)='0'の設定でアクセスします。常にM66291の FIFOレジスタのb7-b0に対してアクセスしてください(即ち、偶数アドレスのみにアクセスしてください)。

読み出し: M66291のFIFOバッファに格納された順番で、メモリに格納されます。 書き込み: メモリに格納された順番で、M66291のFIFOバッファに格納されます。

### (3) M66291 の FIFO に対する DMA アクセス

CPUアクセスと同様です。但し、BSWP(Address 48h or 50h, bit 12)を設定します。また、DMACの転送単位はバイトに指定してください。

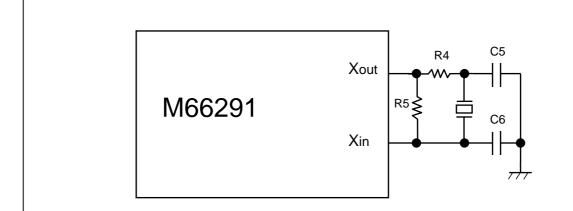

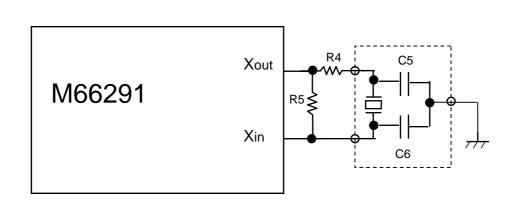

# 7.3. 発振回路

本回路例は、弊社で作製した基板の発振回路例です。

発振回路定数は、発振子メーカが、一定条件のもと(指定のない限り、常温で電源電圧は3.3V) で測定したものであり、実際のシステムにおける高周波、ノイズ、電源特性、配線パターン等の 周辺環境については、一切考慮しておりません。したがって、実際のシステムにおいては、値が 異なる場合があります。

尚、ルネサス テクノロジ及びルネサス ソリューションズは、この回路定数を保証しておりません。 必ず参考値としてご利用下さい。

お客様のシステムにおける最適発振回路定数が必要な場合は、発振子メーカにご依頼下さい。

また、回路を構成する際に安定化している電源の使用及び、M66291の電源端子(CoreVcc,IOVcc) と Ground 端子(GND)間にパスコンを入れることを推奨します。

図 7-29 は株式会社大真空製水晶発振子を使用した例です。

図 7-30 は株式会社村田製作所製セラミック発振子を使用した例です。

水晶発振子の仕様及び回路定数

| メーカー | NO | 品名      | 発振<br>周波数 | 負荷<br>容量 | R4                     | R5                   | C5   | C6   |

|------|----|---------|-----------|----------|------------------------|----------------------|------|------|

| ㈱大真空 | 1  | DSX421G | 12MHz     | 12pF     | $1.5 \mathrm{K}\Omega$ | $1 \mathrm{M}\Omega$ | 18pF | 18pF |

|      | 2  | DSX630G | 12MHz     | 16pF     | $680\Omega$            | $1 \mathrm{M}\Omega$ | 27pF | 27pF |

|      | 3  | DSX630G | 24MHz     | 16pF     | $560\Omega$            | $1 \mathrm{M}\Omega$ | 18pF | 18pF |

|      | 4  | DSX630G | 48MHz     | 16pF     | $560\Omega$            | $1 \mathrm{M}\Omega$ | 3pF  | 3pF  |

図 7-29 発振回路例 1 (株式会社大真空製水晶発振子)

セラミック発振子の仕様及び回路定数(C5.C6 は発振子に内蔵)

| メーカー       | NO | 品名                                      | 発振    | R4          | R5           | C5     | C6     |

|------------|----|-----------------------------------------|-------|-------------|--------------|--------|--------|

|            |    |                                         | 周波数   |             |              |        |        |

| 機村田<br>製作所 | 1  | CSTCE12M0G150-R0                        | 12MHz | $220\Omega$ | 1ΜΩ          | (33pF) | (33pF) |

|            | 2  | CSTCW24M0X11()-R0<br>(*)CSTCW2400MX41() | 24MHz | 0Ω          | 1ΜΩ          | (6pF)  | (6pF)  |

|            | 3  | CSTCW48M0X11()-R0<br>(*)CSTCW4800MX41() | 48MHz | 0Ω          | $1 M \Omega$ | (6pF)  | (6pF)  |

(\*)2001年6月以前の旧型番です。

図 7-30 発振回路例 2 (株式会社村田製作所セラミック発振子)

### ※注意点

上記 NO.2,NO.3 は狭偏差対応タイプです。

USB用途でご使用される場合、発振周波数精度が厳しいものとなりますので、ご使用される基板 (基板が変更する)毎に評価を行う必要がありますのでご注意下さい。

発振子の周波数合わせ込み選別により、各基板ごとに品名()内にカスタム品番をメーカーより つけられることを推奨されております。詳細は発振子メーカーにお問い合わせ下さい。

# 8. M66291 と M66290A の主な相違点

M66291 と M66290A の主な相違点を以下に述べます。また、本アプリケーションノートの付録として、 レジスタの相違点一覧を添付します。

### 8.1. 追加機能について

### 8.1.1. USB 転送機能に関する機能追加

### 8.1.1.1. エンドポイント数増加

エンドポイント6が追加され、最大7本のエンドポイントが使用可能となりました。

### 8.1.1.2. コントロール転送の連続転送機能強化

コントロール転送における連続転送使用時の設定可能最大データ数を 255 バイトから 256 バイトに増加しました。

このことにより、255 バイトを超えるデータの送受信時にも、ショートパケットがはさまれませんので、 1回の連続転送設定で転送できるデータ数に実質的に制限がなくなりました。

#### 8.1.1.3. データ転送の連続転送機能強化

OUT 方向の連続転送使用時におけるデータ読み出し機能を追加しました。

受信データ数がマックスパケットサイズの整数倍、かつ、FIFO バッファ容量より小さい場合にも CPU がデータを読み出せるように、SIE\_FIFO ステータスレジスタ(Address 46h)、および、トランザクション 回数レジスタ(Address 4Eh)を追加しました。

#### 8.1.1.4. isochronous 転送機能強化

ishochronous 転送での SOF への同期性をよりとりやすくするため、IDLY[アイソクロナス送信ディレイセットビット](CPU\_FIFO 制御レジスタ(Address 42h)、bit 14)を追加しました。また、USB バスの SOF パケット受信時にパルスを出力する機能を追加しました。SOF パルスは、"L"アクティブ/"H"アクティブを選択できます。

#### 8.1.2. バスインターフェース機能に関する機能追加

### 8.1.2.1. バスインターフェース電源トレラント強化

3.3V 動作、5V 動作の CPU と M66291 を直接接続可能にしました。M66291 へのコア Vcc=3.3V は必要ですが、制御用 CPU、外付け DMA コントローラ等の動作電圧が 5V の場合でも外付けバッファ等は必要ありません。

5V インターフェイスでご使用になる場合は、M66291 の初期化処理で LDRV[駆動電流調整ビット](駆動電流調整レジスタ(Address 5Eh)、bit 0)='1'を設定してください。

### 8.1.2.2. 8bit バス幅インターフェース追加

8bit バス幅で M66291 を制御することが可能になりました。この場合は、M66291 起動時に \*HWR/\*BYTE 端子に"L"レベルを入力してください。8bit バス幅で使用される場合、空き端子となる D8-D14 はプログラマブル入出力ポートとして使用できます。

#### 8.1.2.3. バッファレディ割り込みステータスクリア機能追加

M66290Aではバッファレディ割り込みのステータス(割り込みステータスレジスタ 1(Address H'18)) クリアはソフトウエアでは行えませんが、M66291では、RDYM[レディモードビット](極性設定レジスタ (Address 0Eh)、bit 2)='1'に設定すればバッファレディ割り込みのステータスをソフトウエアでクリアすることができます。RDYM='0'設定時(M66290A 互換時)は IN 方向のエンドポイントに関して、送信すべきデータがないタイミングでレディ割り込みが発生したままになるになるため、回避するために当該エンドポイントのバッファレディ割り込みを禁止する処理が必要ですが、RDYM='1'設定時は他の割り込みと同様にソフトウエアで制御できます。このため、バッファのステータスを示す FIFO ステータスレジスタ (Address 58h)を追加しました。RDYM='0'設定時は、割り込みステータスレジスタ 1 と FIFO ステータスレジスタレジスタは同じ内容となります。

RDYM='1'設定時は、OUT 方向に設定したエンドポイントの FIFO バッファの読み出し完了時にバッファクリア(BCLR='1')が必要ですのでご注意ください(RDYM='0'設定は読み出し終了時にハードウエアでクリアされます)。

## 8.1.2.4. FIFO\_DATA レジスタ機能強化

D1\_FIFO レジスタ(Address 54h)を追加し、データ転送用として合計 3 つの FIFO\_DATA レジスタが使用可能となりました。

また、Dn\_FIFO レジスタに対して、Dack ハンドシェイクを使用しないモード、CPU による読み出し/書き込みモード等を追加し、アクセスの利便性を強化しました。

#### 8.1.2.5. 割り込み機能強化

CPU への割り込み出力制御用に**極性設定レジスタ(Address 0Eh)**を追加しました。以下の制御が可能です。

- (1) 割り込み出力端子を最大 2 本使用でき、割り込み要因毎に出力端子を設定できます(SOF パルス出力を使用する場合は\*INT0 のみ使用可)。

- (2) 割り込み出力端子の"L"アクティブ/"H"アクティブを選択できます。

- (3) 割り込み出力端子のエッジセンス/レベルセンスを選択できます。

尚、リセット直後は M66291 の割り込み出力端子は"L"アクティブで起動します。"H"アクティブでご使用になる場合、切り替え直後に空割り込み発生の可能性があります。CPU の仕様をご確認の上、処理設計をお願いします。

# 8.2. M66290A との互換性について

M66290A と M66291 の互換性について以下に説明します。実際の移植時にはお客様にて十分なご検討と評価をお願いいたします。

#### 8.2.1. CPU との接続方法

CPU との接続方法は、図 2-3を参照ください。

M66290A との互換機能で使用する場合に機能が異なる端子を表 8-1に示します。

また、FIFO アクセスサイクル高速化に伴い、バスタイミング規定が M66290A と異なっていますので、制御 CPU とのタイミング検証を十分に実施ください。

| 端子  | M66291         |            | M66290A   |                    |  |

|-----|----------------|------------|-----------|--------------------|--|

| No. | 端子名            | 端子処理       | 端子名       | 端子処理               |  |

| 8   | *Dack1(入力)     | 未使用時"H"固定  | *TRST(入力) | *RST とショート         |  |

| 9   | *Dreq1(出力)     | 未使用時オープン   | TCK(入力)   | 未使用時"L"固定、または、オープン |  |

| 10  | *TC1(入力)       | 未使用時"H"固定  | TMS(入力)   | 未使用時"H"固定、または、オープン |  |

| 11  | *INT1/*SOF(出力) | 未使用時オープン   | TDI(入力)   | 未使用時"H"固定、または、オープン |  |

| 12  | IOVcc          | Vcc とショート  | TDO(出力)   | 未使用時オープン           |  |

| 35  | IOVcc          | Vcc とショート  | Vcc       | Vcc                |  |

| 41  | *HWR/*BYTE     | *LWR とショート | TEST2     | "L"固定、または、オープン     |  |

表 8-1 M66291/M66290A 端子相違点

### 8.2.2. ソフトウエア移植時の注意点

M66291 で機能が追加されたレジスタについても、デフォルト値は M66290A と互換動作となるように 設計されていますが、例外を以下に示します。

#### 8.2.2.1. バッファリワインド機能

(1) エンドポイント 0 のバッファリワインド機能

M66290 では、ISEL[バッファセレクトビット](EP0\_FIFO 選択レジスタ(Address 30h)の bit 0)を変更するとエンドポイント 0 に割り当てた FIFO バッファのポインタを初期化します。

M66291 では、ISEL を変更してもバッファポインタは初期化されません。

(2) エンドポイント 1~5 のバッファリワインド機能

RWND[バッファリワインドビット](CPU\_FIFO 選択レジスタ(Address 40h)、Dn\_FIFO 選択レジスタ (Address 48h、50h) の bit 12)が追加され、CPU\_EP/DMA\_EP(同レジスタ b3-b0)の切替時に当該エンド

ポイントにアサインした FIFO バッファのポインタを初期化する/しないをソフトウエアで指定できるようになりました。

M6690Aでは、CPU\_EP/DMA\_EPを切り替えると必ずポインタが初期化されます。

M66291 のデフォルト(RWND='0')は、切り替え時のバッファポインタ初期化が発生しません。 RWND='1'を設定すると、バッファポインタの初期化が発生します。

#### (2) DMA インターフェイスの設定

M66290AとM66291ではDMAインターフェイスの設定ビットがビットの位置/機能ともに異なっています。詳細は、データシート及び、 $2.7~Dn_FIFO$  データレジスタへのアクセス(DMA コントローラインターフェース)を参照ください。

M66290A の"1 ワード転送モード"が M66291 のサイクルスチールモードに相当します。 また、M66290A での"高速転送モード"は M66291 にはありません。

### (3) バッファエンプティ割り込みの発生タイミング

ダブルバッファで OUT 転送を行う時のバッファエンプティ割り込みの発生タイミングが異なります。

M66290A では、SIE 側 FIFO バッファのデータ送出完了時に、CPU 側 FIFO バッファの書き込みが完了していなければ、バッファエンプティ割り込みが発生します。

M66291 では、SIE 側 FIFO バッファのデータ送出完了時に、CPU 側 FIFO バッファが空であればバッファエンプティ割り込みが発生します。CPU 側 FIFO バッファに対して書き込み中、または書き込み完了の場合は、バッファエンプティ割り込みが発生しません。

#### 8.2.2.2. リモートウエイクアップ機能について

M66290A はリモートウエイクアップ信号出力後、デバイスステートがアドレスステート(Address state)に遷移します。

M66291 はリモートウエイクアップ信号出力後、サスペンドステートに遷移する直前のステートに遷移します。実質的には、構成ステート(Configured state)に遷移します。

# 9. Q & A

# 9.1. 基板設計に関する Q & A

| 9.1.10. | [質問] | H/Wリセット直後、S/Wリセット直後の端子の状態を教えてください。                                   |

|---------|------|----------------------------------------------------------------------|

|         | [回答] | 以下のとおりです。詳細はデータシートをご参照ください。                                          |

|         |      | (1)H/Wリセット直後は以下のとおりです。                                               |

|         |      | ① 入力;D7~D0、D14/P6~D8/P0、D15/A0、A6~A1、*CS、*LWR、*HWR/*BYTE、*RD、        |

|         |      | *Dack0、*Dack1、*TC1、Vbus、*RST、Xin、TEST、D+、D-                          |

|         |      | (但し、*CS、*RD、*Dack0、*Dack1、*TC1は非アクティブ)                               |

|         |      | ② 出力;*INT0("H")、*INT1/*SOF("H")、*Dreq0("H")、*Dreq1("H")、TrON(Hi-Z) 、 |

|         |      | Xout("H")                                                            |

|         |      | (端子名直後の()内は、リセット直後の状態を示します)                                          |

|         |      | (2)S/Wリセット直後は以下のとおりです。                                               |

|         |      | 以下の端子以外は、リセットする前の状態を保持します。                                           |

|         |      | ① *INT0、*INT1/*SOFは"H"出力に戻ります。                                       |

|         |      | (M66291は、SWリセットにより割り込みステータスをクリアし、割り込み出力をキャ                           |

|         |      | ンセルします。また、極性設定レジスタもクリアしますので、割り込み出力がデフォル                              |

|         |      | ト("L"アクティブ)に戻ります)                                                    |

|         |      | ② XoutはS/Wリセットの影響を受けません。S/Wリセット直前のUSB動作許可レジスタの                       |

|         |      | 設定に従います。                                                             |

|         |      | ▶ 入力端子に中間電位を与える、又は、Vbus、TEST、D+、D-以外の入力端子をオープ                        |

|         |      | ンのままにすると、リーク電流が発生する可能性があります。システム設計の際にはご                              |

|         |      | 注意くださいますようお願いいたします。                                                  |

| 9.1.11. |      | *                                                                    |

|         | [回答] | 以下のとおりです。詳細はデータシートをご参照ください。                                          |

|         |      | (1)Vbus端子;500kΩでPull downされています。                                     |

|         |      | (2)TEST端子;50kΩでPull downされています。                                      |

| 9.1.12. | [質問] | 電源が入ったままResetを長時間Assertした場合問題はありませんか?                                |

|         | [回答] | -                                                                    |

| 9.1.13. | [質問] | CPUインタフェース仕様に関して5Vトレラント対応がされていますか?                                   |

|         | [回答] | IOVcc=5Vの場合、CPUインターフェース関連端子は5Vトレラントとなります。                            |

# 9.2. コントロール転送に関する Q & A