## M16C/6C グループ

シリアルインタフェースUARTi (i=0~5)補足資料

R01AN0421JJ0100 Rev.1.00 2011.03.09

## 1. 要約

この資料はM16C/6C グループのシリアルインタフェース UARTi (i=0~5) の仕様について補足するものです。

## 2. はじめに

この資料は、テクニカルアップデート TN-16C-A201A/J「M16C/65、M16C/64A、M16C/63、M16C/6C グループの仕様変更」に示したシリアルインタフェース UARTi の仕様変更またはマニュアルの記述を補足するものです。

仕様変更を確認する場合に使用してください。また、最後に旧来マニュアルをつけていますので、記述 を比較する場合に参照してください。

なお、I<sup>2</sup>C モードを使用したプログラムを作成する場合は、下のアプリケーションノートを参照してください。

- •UARTi特殊モード1を使用したI<sup>2</sup>Cバスインタフェース (RJJ05B1545)

- UARTi 特殊モード1を使用したI<sup>2</sup>C-busインタフェース (マスタ送信/受信) (RJJ05B1596)

- UARTi 特殊モード1を使用したI<sup>2</sup>C-busインタフェース (スレーブ送信/受信) (RJJ05B1604)

## 3. 仕様変更または補足内容

### 3.1 クロック同期形シリアルI/Oモード、UARTモード

「送受信回路の初期化」が分かり難かったので、下のように同じ手順にします。従来記載していた方法でも誤りではありません。

#### 通信の途中終了時、または通信エラー発生時の処理

クロック同期形シリアルI/OモードまたはUARTモードで、通信を途中終了させた場合、または通信エラーが発生した場合、次の手順で再設定を行ってください。

- (1) UiC1 レジスタのTEビットを"0"(送信禁止)、REビットを"0"(受信禁止)にする。

- (2) UiMR レジスタの SMD2~SMD0 ビットを"000b" (シリアルインタフェースは無効)にする。

- (3) UiMR レジスタの SMD2~SMD0 ビットを "001b"(クロック同期形シリアル I/O モード)、"100b" (UARTモードキャラクタ長 7 ビット)、"101b" (UARTモードキャラクタ長 8 ビット)、"110b" (UART モードキャラクタ長 9 ビット)のいずれかにする。

- (4) UiC1 レジスタのTEビットを"1"(送信許可)、REビットを"1"(受信許可)にする。

#### 3.2 I<sup>2</sup>Cモード

仕様変更内容を下に示します。また、 $I^2C$  モードは機能説明を見直しています。大幅に変更した箇所を、「4. 特殊モード1 ( $I^2C$  モード)」に示します。

### 3.2.1 UiSMR4 レジスタ

UiSMR4レジスタのビットは $I^2$ C モードで使用します。UiSMR レジスタのIICM ビットが"I" ( $I^2$ C モード) のとき"I"にできます。IICM ビットが"I"のときは"I"を書かないでください。

STAREQ、RSTAREQ、STPREQ、STSPSEL、SCLHI ビットはI<sup>2</sup>C モードでマスタの場合に使用します。 STSPSEL ビットは先にSTAREQ、RSTAREQ、STPREQ ビットのいずれかを"1" (スタート)にした後、"1"(スタートコンディション/ストップコンディション生成回路選択)にしてください。

ACKD、ACKC、SWC9 ビットはI<sup>2</sup>Cモードでスレーブの場合に使用します。

#### 3.2.2 UiBRG レジスタ

I<sup>2</sup>Cモードでは、UiBRGレジスタに設定する値を"03h"以上にしてください。

#### 3.2.3 UiSMR3 レジスタ

I<sup>2</sup>Cモードでは、UiSMR3レジスタのCKPHビットを"1" (クロック遅れあり) にしてください。

#### 3.2.4 注意事項

次の注意事項を追加しました。

### 3.2.4.1 "L" レベル/"H" レベル入力電圧、"L" レベル出力電圧

"L"入力電圧、"H"入力電圧、および"L"出力電圧は、I<sup>2</sup>Cバス規格と異なります。 SCL、SDAと端子を共用する入出力ポートの推奨動作条件を参照してください。

<I<sup>2</sup>Cバス規格>

"H"入力電圧(V<sub>IH</sub>) = min 0.7 V<sub>CC</sub>

"L"入力電圧(V<sub>II</sub>) = max 0.3 V<sub>CC</sub>

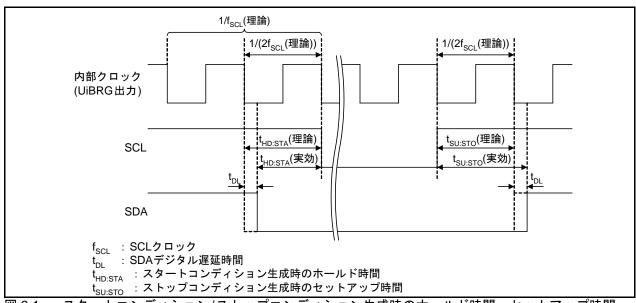

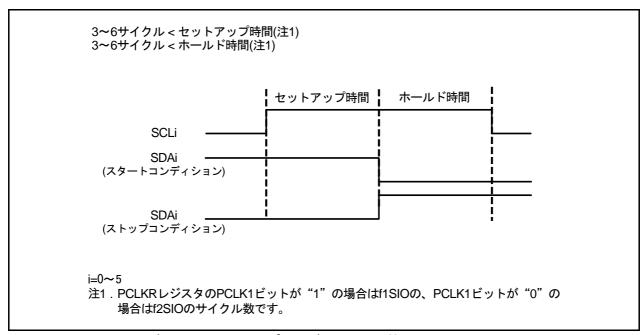

#### 3.2.4.2 コンディション生成時のセットアップ時間およびホールド時間

スタートコンディション生成時、SCLクロックの1/2サイクル分の時間がホールド時間( $t_{HD}$ :STA)となります。ストップコンディション生成時、SCLクロックの1/2サイクル分の時間がセットアップ時間( $t_{SU}$ :STO)となります。

また、SDAデジタル遅延機能を使用する場合、遅延時間を考慮してください(ユーザーズマニュアルハードウェア編のUART章「SDAデジタル遅延機能」参照)。

以下にコンディション生成時のホールド時間およびセットアップ時間の算出例を示します。

#### <100kbps設定時の算出例>

- UiBRGカウントソース: f1 = 20MHz

- UiBRG レジスタの設定値: n = 100 − 1

- SDA デジタル遅延設定値: DL2~DL0 = 101b (UiBRG カウントソースの 5~6サイクル) の場合、

```

= f1/(2(n+1))

f<sub>SCI</sub>(理論)

= 20MHz/(2\times(99+1)) = 100kbps

= 遅延サイクル数 /f1 = 6/20MHz

t_{DL}

= 0.3 \mu s

t<sub>HD:STA</sub>(理論)

= 1/(2f<sub>SCL</sub>(理論))

= 1/(2 \times 100 \text{kbps})

=5\mu s

t<sub>SU:STO</sub>(理論)

= 1/(2f<sub>SCL</sub>(理論))

= 1/(2 \times 100 \text{kbps})

=5\mu s

= t_{HD:STA}(理論) - t_{DL} = 5 \mu s - 0.3 \mu s

t<sub>HD:STA</sub>(実効)

= 4.7 \mu s

t<sub>SU:STO</sub>(実効)

= t_{SU:STO}(理論) + t_{DL} = 5 \mu s + 0.3 \mu s

= 5.3 \mu s

```

図 3.1 スタートコンディション/ストップコンディション生成時のホールド時間、セットアップ時間

#### 3.2.4.3 UiBRGカウントソースによる最大送受信速度の制限

I<sup>2</sup>Cモードでは、UiBRGレジスタに設定する値を"03h"以上にしてください。

内部回路が SCL クロックのレベルを認識するまで、最大で UiBRG カウントソースの 3 サイクルを要します。したがって、接続可能な  $I^2$ C バスのビットレートは、UiBRG カウントソースの速度の 1/3 以下です。 UiBRG レジスタに "00h" ~"02h" を設定した場合は、ビットずれを起こす可能性があります。

#### 3.2.4.4 スレーブ時のリスタートコンディション

スレーブ時、リスタートコンディションを検出すると、その後の処理を正しく実行しない場合があります。スレーブ時はリスタートコンディションを使用しないでください。

## 3.2.4.5 スレーブ時の送受信開始条件

スレーブとして、UiCOレジスタのTXEPTビットが"1"(送信レジスタにデータなし)の状態から送受信を始める場合は、外部クロックが"H"のときに、最後の条件を満たすようにしてください。

送受信開始条件(順序は関係ありません)

- •UiC1レジスタのTEビットが"1"(送信許可)

- •UiC1レジスタのTIビットが"0" (UiTBレジスタにデータあり) 受信

- •UiC1レジスタのREビットが"1"(受信許可)

- •UiC1レジスタのTEビットが"1"(送信許可)

- •UiC1 レジスタのTIビットが"0" (UiTB レジスタにデータあり)

#### 3.3 特殊モード2

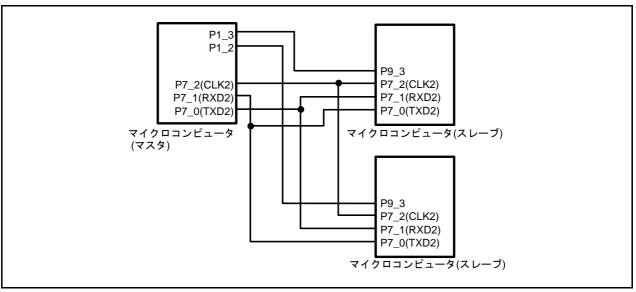

特殊モード2は、マスタモードで使用してください。スレーブモード(外部クロック)で使用しないでください。したがって、特殊モード2では、UiMRレジスタのCKDIRビットを"0"(内部クロック)にしてください。

ただし、条件によってはスレーブモードを使用できるのでアプリケーションノートを準備します。 シリアルインタフェース 特殊モード2(スレーブ通信)(RJJ05B1671-0100)

## 4. 特殊モード1 (I<sup>2</sup>C モード)

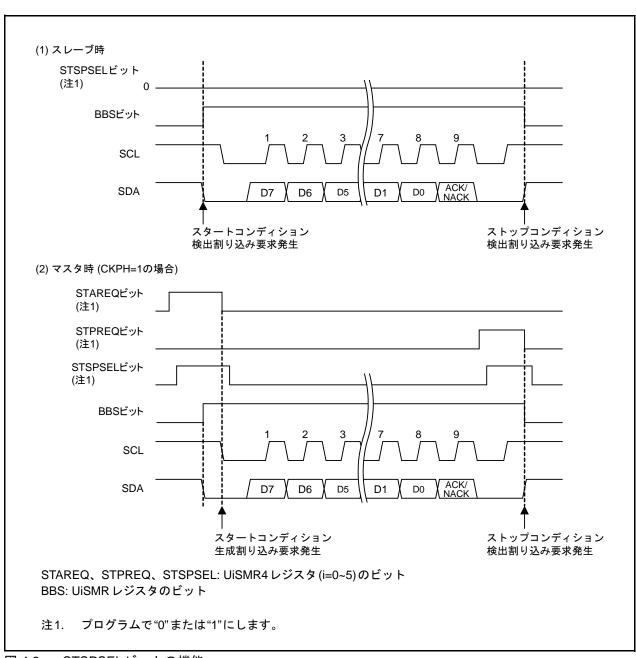

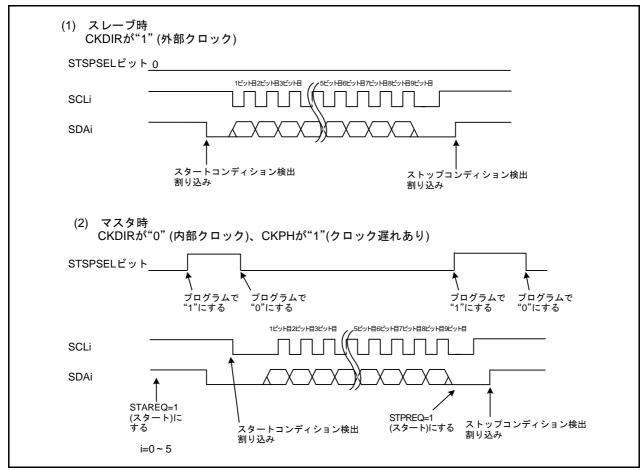

#### 4.1 スタートコンディション、ストップコンディションの検出

スタートコンディション検出回路によりスタートコンディションを、ストップコンディション検出回路によりストップコンディションを検出します。

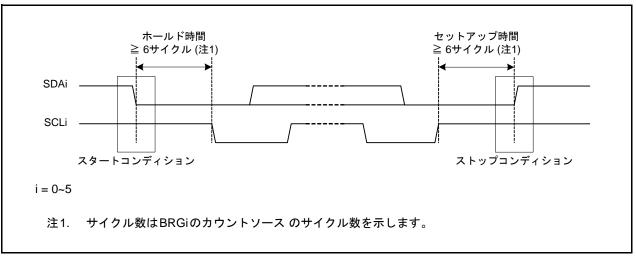

スタートコンディション検出割り込み要求は、SCLi端子が"H"の状態でSDAi端子が"H"から"L"に変化すると発生します。ストップコンディション検出割り込み要求は、SCLi端子が"H"の状態でSDAi端子が"L"から"H"に変化すると発生します。

スタートコンディション検出割り込みと、ストップコンディション検出割り込みは、割り込み制御レジスタ、ベクタを共用していますので、どちらの要求による割り込みかは、UiSMR レジスタのBBS ビットで判定してください。

スタートコンディション、ストップコンディションを検出するには、図 4.1 に示すとおりセットアップ 時間、ホールド時間ともにBRGiのカウントソースの6サイクル以上必要です。Fast-Modeの仕様を満たす ためには、BRGiのカウントソースは10MHz以上である必要があります。

図 4.1 スタートコンディション、ストップコンディションの検出

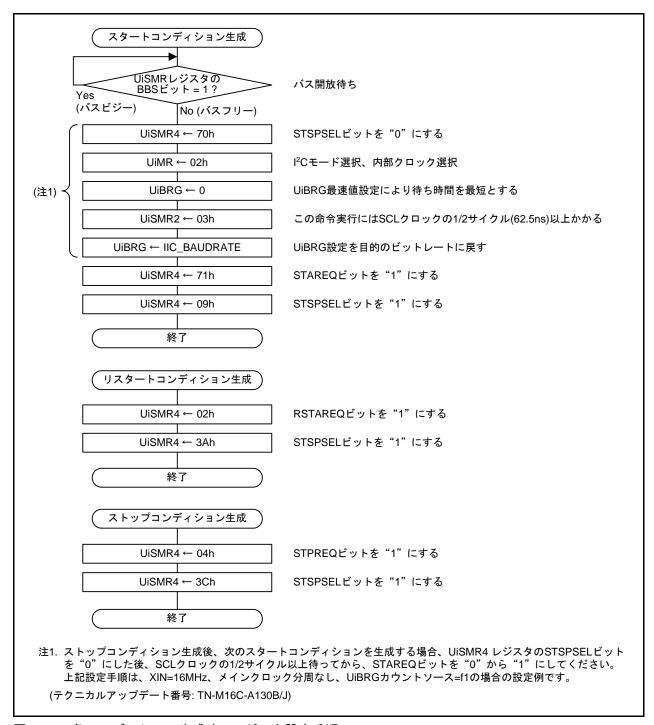

### 4.2 スタートコンディション、ストップコンディションの生成

UiSMR4レジスタ(i=0~5)のSTAREQビットを"1"(スタート)にするとスタートコンディションを生成します。

UiSMR4 レジスタの RSTAREQ ビットを"1" (スタート)にするとリスタートコンディションを生成します。

UiSMR4レジスタのSTPREQビットを"1"(スタート)にするとストップコンディションを生成します。 出力の手順は次のとおりです。

- (1) STAREQビット、RSTAREQビット、またはSTPREQビットを"1"(スタート)にする

- (2) UiSMR4 レジスタのSTSPSEL ビットを"1" (出力)にする

表 4.1と図 4.2にSTSPSELビットの機能を示します。

表 4.1 STSPSEL ビットの機能

| 機能                                           | STSPSEL=0          | STSPSEL=1                                                                 |

|----------------------------------------------|--------------------|---------------------------------------------------------------------------|

|                                              | スタートコンディション、ストップコン | STAREQビット、RSTAREQビット、<br>STPREQビットに従って、スタートコン<br>ディション、ストップコンディションを<br>出力 |

| スタートコンディション、ス<br>トップコンディション割り込<br>み要求発生タイミング |                    | スタートコンディション、ストップコン<br>ディション生成終了                                           |

図 4.2 STSPSEL ビットの機能

図 4.3 各コンディション生成時のレジスタ設定手順

## 4.3 アービトレーション

SCLi の立ち上がり時に、自身の送信データとSDAi 端子からの入力データが一致しているかを判定し、一致していなければ出力を停止することによりアービトレーションを行います。

UiSMR レジスタ (i=0~5)の ABC ビットで UiRB レジスタの ABT ビットの更新タイミングを選択します。 ABC ビットが "0" (ビットごとに更新)の場合、判定時に不一致を検出すると同時に ABT ビットが "1" に、検出しないと "0" になります。 ABC ビットが "1" (バイトごとに更新)の場合、判定時に一度でも不一致が検出された場合、8 ビット目の SCLi の立ち下がりで ABT ビットが "1" (検出) になります。なお、バイトごとに更新する場合は、1 バイト目の ACK 検出完了後、ABT ビットを "0" (未検出)にしてから、次の1 バイトの送受信を開始してください。

UiSMR2レジスタのALSビットを"1"(SDA出力を停止する)にすると、アービトレーションロストが発生しABTビットが"1"になると同時にSDAi端子がハイインピーダンスになります。

#### 4.4 SCL制御とクロック同期化

$I^{2}C$  モードでの送受信は送受信クロックで行います。しかし、送受信クロックが速くなってくると、ACK の生成や送信データの準備に必要な時間を確保することが難しくなってきます。 $I^{2}C$  モードではこの時間を確保するためのウェイト挿入の機能、および他デバイスが挿入したウェイトに対しクロックを同期させる機能をサポートしています。

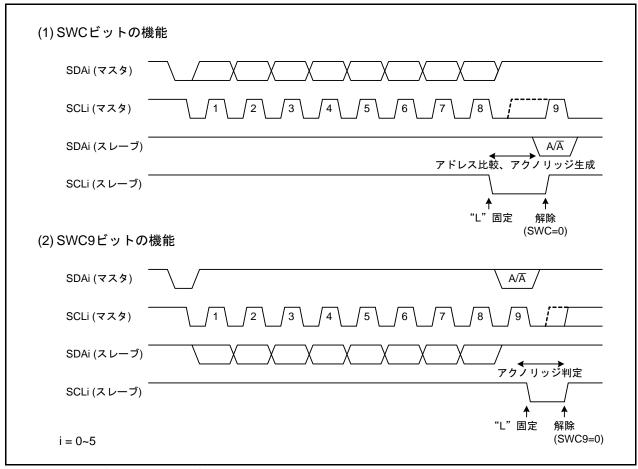

UiSMR2 レジスタ (i=0~5)の SWC ビットは、アクノリッジ生成のためのウェイトを挿入するときに使用します。 SWC ビットが "1" (8 ビット受信後、SCLi 端子を "L"に固定)の場合、8 ビット目の SCLi の立ち下がりで SCLi 端子が "L"固定になります。 SWC ビットを"0" (ウェイトなし/ウェイト解除)にすると、"L" 固定を解除できます。

UiSMR2 レジスタの SWC2 ビットを"1" (SCLi 端子を"L"に固定) にすると、送受信中でも SCLi 端子を"L"固定にできます。SWC2 ビットを"0" (SCLi 端子に送受信クロックを出力) にすると、SCLi 端子からの"L"固定は解除され、送受信クロックが出力されます。

UiSMR4レジスタのSWC9ビットは、受信したアクノリッジビットを判定するためのウェイトを挿入するときに使用します。UiSMR3レジスタのCKPHビットが"1"(クロック遅れあり)のとき、SWC9ビットを"1"(9ビット受信後、SCLi端子を"L"に固定)にすると、9ビット目のSCLiの立ち下がりでSCLi端子が"L"固定になります。SWC9ビットを"0"(ウェイトなし/ウェイト解除)にすると"L"固定を解除できます。

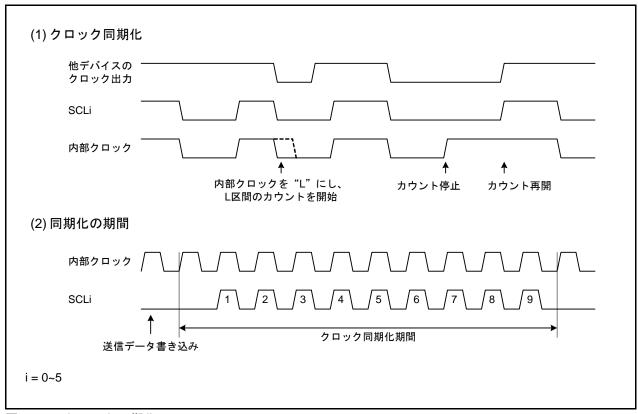

図 4.4 SWC ビット、SWC9 ビットによるウェイトの挿入

UiSMR2レジスタのCSCビットは、他のデバイスがウェイトを挿入するなどしたために、自身が出力したクロックとSCLi端子に入力されたクロックが異なったとき、内部で生成するクロックをSCLi端子から入力されるクロックに同期させるためのビットです。CSC ビットが"1"(クロック同期を実施する)の場合、内部生成クロックが"H"のときにSCLi 端子が"H"から"L"に変化すると、内部生成クロックを"L"にし、UiBRG レジスタの値をリロードしてL 区間のカウントを開始します。また、SCLi 端子が"L"のとき、内部生成クロックが"L"から"H"に変化するとカウントを停止し、SCLi端子が"H"になるとカウントを再開します。したがってUARTiの送受信クロックは、内部生成クロックとSCLi端子の信号の論理積になります。送受信クロックは、内部生成クロックの1クロック前から9クロック目まで同期化されます。CSCビットはUiMR レジスタのCKDIR ビットが"0"(内部クロック)のときのみ"1"にできます。

UiSMR4 レジスタの SCLHI ビットは、自身がマスタとして送受信を行っているときに他のマスタがストップコンディションを生成した場合に、SCLi 端子を開放するために使用します。SCLHI ビットを"1" (出力停止)にすると、ストップコンディション検出時にSCLi 端子を開放し(ハイインピーダンス)、クロック出力を停止します。

図 4.5 クロック同期化

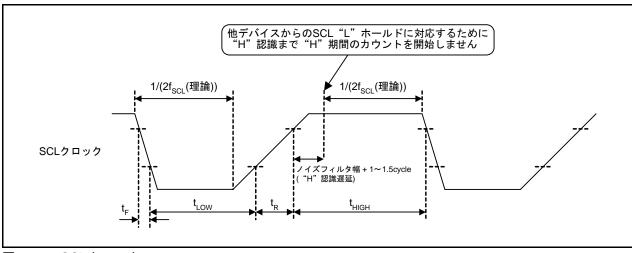

## 4.5 SCLクロックの周波数の考え方

$I^2$ Cモードで生成する SCL クロックの Duty は 50% です。そのため、 $I^2$ C バスの Fast-Mode の最大 SCL クロック (400kbps)を設定すると、SCL クロックの"L"幅は  $1.25\mu s$  となります。この値は、Fast-Mode の  $I^2$ C バス規格 ( $f_{LOW} = Min.1.3\mu s$ ) を満たしません。よって、SCL クロックの設定を 384.6kbps 以下とし、SCL クロックの"L"幅が  $1.3\mu s$  以上になるようにしてください。

クロック同期化機能(「図 4.5 クロック同期化」参照)を有効にすると、ノイズフィルタ幅+ UiBRG カウントソースの1~1.5 サイクルのサンプリング遅延が発生し、SCL クロックの"H"認識が遅れるため、SCL クロックの"H"幅が延びます。そのため、SCL クロックのビットレートの設定に対して、実際の SCL クロックは遅くなります。

また、SCLクロックの実効値を算出するためには、SCLクロック立ち上がり時間( $t_R$ )も考慮してください。

下記にSCLクロック実効値の算出例を示します。

<384.6kbps設定時のSCLクロック実効値の算出例>

- UiBRGカウントソース: f1 = 20MHz

- UiBRG レジスタの設定値: n = 26 1

- •SCLクロック立ち上がり時間:  $t_R = 100$ ns

- •SCLクロック立ち下がり時間: $t_F = 0$ ns

- ノイズフィルタ幅: t<sub>NF</sub> = 100ns (注1)

- ●サンプリング遅延:t<sub>SD</sub> = 1cycle

の場合、

$f_{SCL}(理論値) = f1/(2(n+1)) = 20MHz/(2(25+1)) = 384.6kbps$

$t_{LOW} = 1/(2f_{SCL}(2284.6)) = 1/(2×384.6) = 1.3$ μs

$t_{HIGH} = 1/(2f_{SCL}(\Xi_{high})) + t_{NF} + (t_{SD} \times 1/f1)$

$= 1/(2 \times 384.6 \text{kbps}) + 100 \text{ns} + (1 \times 1/20 \text{MHz})$

$= 1.45 \mu s$

$f_{SCL}($ 実效値 $)=1/(t_F+t_{LOW}+t_R+t_{HIGH})=1/(0ns+1.3\mu s+100ns+1.45\mu s)$  =350.8kbps

注1.最大200ns。

図 4.6 SCL クロック

## 4.6 SDA出力制御

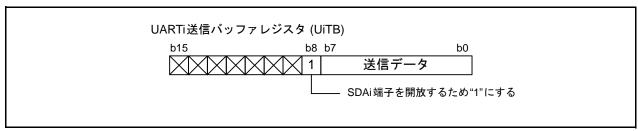

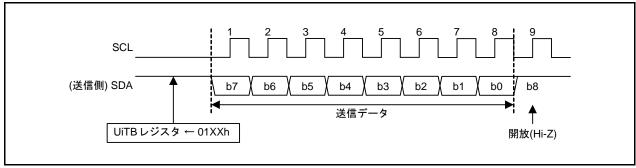

バイトデータを送信する場合、1ビット目~8ビット目はSDAi端子から送信データを出力し、9ビット目はアクノリッジを受信するためSDAi端子を開放します。

$I^2$ Cモードでは、UiTB レジスタに9ビットのデータを設定してください。9ビットデータの $b7\sim b0$ には 送信データを、b8には"1"を設定してください。

UiC0 レジスタのUFORM ビットを"1" (MSB ファースト)にして、UiTB レジスタに9 ビットデータを設定すると、 $b7 \rightarrow b6 \rightarrow \bullet \bullet \bullet \rightarrow b0 \rightarrow b8$ の順で、SDAi 端子からデータが出力されます。b8が"1"なので9 ビット目でSDAi 端子がハイインピーダンス状態になり、アクノリッジを受信できます。

図 4.7 UiTB レジスタの設定 (SDA 出力)

図 4.8 バイトデータの送信

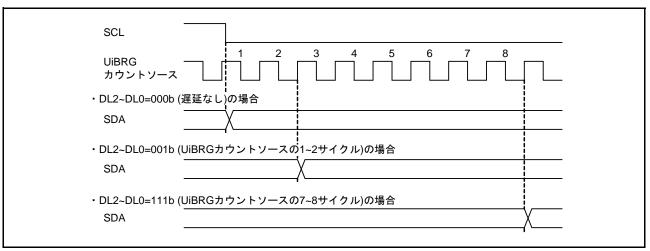

UiSMR3 レジスタの DL2~DL0 ビットにより SDAi の出力を遅延なし、または UiBRG カウントソースの 1~8 サイクルの遅延を設定できます。

UiSMR2 レジスタのSDHI ビットを"1" (SDA 出力禁止) にすると、SDAi 端子が強制的にハイインピーダンス状態になります。なお、SDHI ビットはUARTi の送受信クロックの立ち上がりのタイミングで書かないでください。UiRB レジスタのABT ビットが"1" (検出) になる場合があります。

### 4.7 SDA デジタル遅延機能

I<sup>2</sup>Cバスでデータ送信を行う場合、SCLクロックが"L"のときにデータを変化させてください。SCLクロックが"H"のときにSDAが変化すると、各コンディションと認識されます(「3.2.4.2 コンディション生成時のセットアップ時間およびホールド時間」参照)。

SDAデジタル遅延機能は、SDAi端子からの出力を遅延させる機能です。SDAの変化を遅延させることで、SCLクロックが"L"の期間にデータを変化させることができます。

SDA デジタル遅延機能は、UiSMR3 レジスタの DL2~DL0 ビットを "001b"~"111b" にすると有効になり、"000b"にすると無効になります。

図 4.9 DL2~DL0ビットの設定によるSDA出力切り替え

#### 4.8 SDA 入力

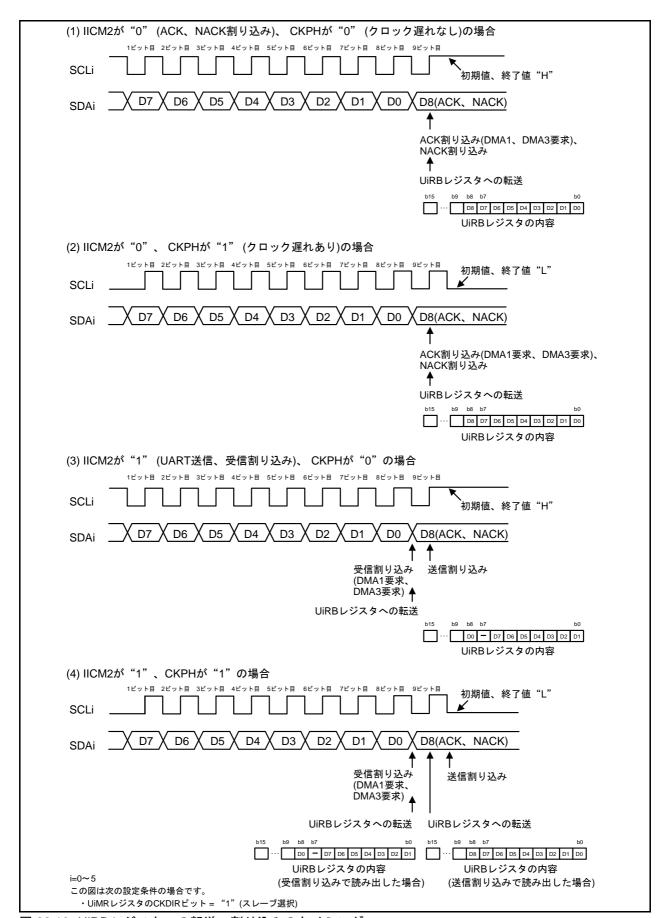

UiSMR2 レジスタ(i=0~5)のIICM2 ビットが"0" (ACK/NACK割り込みを使用)の場合、受信したデータの 1~8 ビット目 (D7~D0) を UiRB レジスタのビット 7~0 に、9 ビット目 (ACK/NACK) を UiRB レジスタのビット 8 に格納します。

IICM2 ビットが"1"のとき、受信したデータの1~7ビット目(D7~D1)をUiRB レジスタのビット6~0に、8ビット目(D0)をUiRB レジスタのビット8に格納します。IICM2 ビットが"1"のときでも、UiSMR3 レジスタのCKPH ビットが"1"であれば、9ビット目のクロックの立ち上がり後にUiRB レジスタを読み出すことにより、IICM2 ビットが"0"のときと同様のデータが読めます。

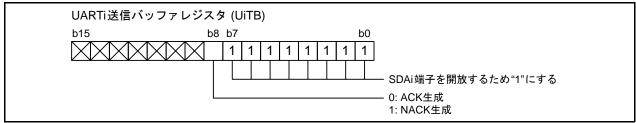

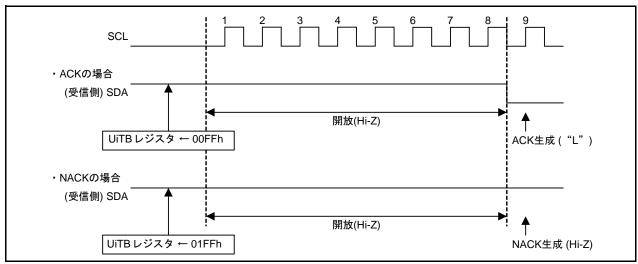

バイトデータを受信する場合、1ビット目~8ビット目はデータを受信するためSDAi端子を開放し、9ビット目はアクノリッジを生成します。マスタ時の最終バイトデータを受信するとき、またはスレーブ時のスレーブアドレス不一致のときはNACKを生成します。それ以外は、通常、ACKを生成します。

$I^2$ Cモードでは、UiTB レジスタに9ビットのデータを設定してください。9ビットデータのb7~b0には SDAi 端子を開放するため"FFh"を、b8はACKを生成する場合は"0"、NACKを生成する場合は"1"を設定してください。

UiTB レジスタに9ビットデータの"00FFh"または"01FFh"を設定すると、1ビット目~8ビット目はSDAi端子がハイインピーダンス状態になり、データを受信できます。9ビット目はACK またはNACK が生成されます。

受信したデータは UiRB レジスタから読み出してください。クロック遅延機能を使用すると、UiRB レジスタへのデータ転送が2回行われ、それぞれの UiRB レジスタの内容が異なります。

図 4.10 UiTB レジスタの設定 (SDA 入力)

図 4.11 バイトデータの受信

#### 4.9 ACK, NACK

データを受信することが確定している場合、UiTB レジスタに00FFh をダミーデータとして設定することで、8ビット受信後にACKが出力されます。また、UiSMR4 レジスタ(i=0~5) のSTSPSEL ビットが"0" (シリアル入出力回路選択)で、UiSMR4 レジスタのACKC ビットが"1" (ACK データ出力)の場合、UiSMR4 レジスタのACKD ビットの値がSDAi 端子から出力されます。

UiSMR2レジスタのIICM2ビットが"0"の場合、9ビット目のSCLiの立ち上がり時にSDAi端子が"H"であればNACK割り込み要求が、"L"であればACK割り込み要求が発生します。

DMA起動要因に「UARTi受信またはACK割り込み要求」を選択すると、ACK検出によってDMA転送を起動できます。

## 4.10 送受信初期化

この機能を使用する場合、送受信クロックは外部クロックを選択してください。

UiSMR2 レジスタの STAC ビットを"1" (スタートコンディション検出時、回路を初期化する)にし、スタートコンディションを検出すると次のように動作します。

- •送信シフトレジスタは初期化され、UiTBレジスタの値が送信シフトレジスタに転送されます。これにより、次に入力されたクロックを1ビット目として送信を開始します。ただし、UARTi出力値はクロックが入って1ビット目のデータが出力されるまでの間は変化せず、スタートコンディションを検出した時点の値のままです。

- ●受信シフトレジスタは初期化され、次に入力されたクロックを1ビット目として受信が開始されます。

SWC ビットが"1"(8 ビット受信後 SCL 端子を"L"に固定)になります。これにより、クロックの9 ビット目の立ち下がりで SCLi 端子が"L"になります。

なお、この機能を使用しUARTiの送受信を開始した場合、UiC1 レジスタのTI ビットは変化しません。 スレーブ時、UARTi 初期化機能を使用すると、スタートコンディション検出時に自動的に UARTi が初 期化されるため、スタートコンディション検出時に割り込みは必要ありません。

## 5. 参考ドキュメント

M16C/6C グループ ユーザーズアマニュアル ハードウェア編 Rev.2.00 (R01UH0138JJ0200)

アプリケーションノート

「2. はじめに」で示したものや、その他のモードに関するものを準備しています。

(最新版をルネサスエレクトロニクスホームページから入手してください。)

参考資料:従来のシリアルインタフェースUARTiの記述 資料の最後に、従来のマニュアルのシリアルインタフェースUARTiの章を示します。

## ホームページとサポート窓口

ルネサス エレクトロニクスホームページ

http://japan.renesas.com/

お問合せ先

http://japan.renesas.com/inquiry

| 改訂記録 | M16C/6C グループ                   |

|------|--------------------------------|

|      | シリアルインタフェース UARTi (i=0~5) 補足資料 |

| Rev.  | 発行日        |     | 改訂内容 |

|-------|------------|-----|------|

| itov. | 光打口        | ページ | ポイント |

| 1.00  | 2011.03.09 | _   | 初版発行 |

|       |            |     |      |

すべての商標および登録商標は、それぞれの所有者に帰属します。

#### 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意 事項については、本文を参照してください。なお、本マニュアルの本文と異なる記載がある場合は、本文の 記載が優先するものとします。

#### 1. 未使用端子の処理

【注意】未使用端子は、本文の「未使用端子の処理」に従って処理してください。

CMOS 製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI 周辺のノイズが印加され、LSI 内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。未使用端子は、本文「未使用端子の処理」で説明する指示に従い処理してください。

#### 2. 電源投入時の処置

【注意】電源投入時は、製品の状態は不定です。

電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。

外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の状態は保証できません。

同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットの かかる一定電圧に達するまでの期間、端子の状態は保証できません。

3. リザーブアドレス (予約領域) のアクセス禁止

【注意】リザーブアドレス(予約領域)のアクセスを禁止します。

アドレス領域には、将来の機能拡張用に割り付けられているリザーブアドレス(予約領域)があります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

4. クロックについて

【注意】リセット時は、クロックが安定した後、リセットを解除してください。

プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。

リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、 クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子 (または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定し てから切り替えてください。

5. 製品間の相違について

【注意】型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。

同じグループのマイコンでも型名が違うと、内部 ROM、レイアウトパターンの相違などにより、電気的特性の範囲で、特性値、動作マージン、ノイズ耐量、ノイズ輻射量などが異なる場合があります。型名が違う製品に変更する場合は、個々の製品ごとにシステム評価試験を実施してください。

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されて いる当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の 法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA機器、通信機器、計測機器、AV機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命維持を目的として設計されていない医療機器

(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療 行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム等

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を招えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制するRoHS指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社がその総株主の議決権の過半数を 直接または間接に保有する会社をいいます。

- 注2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

ルネサスエレクトロニクス株式会社

■営業お問合せ窓口

http://www.renesas.com

※営業お問合せ窓口の住所・電話番号は変更になることがあります。最新情報につきましては、弊社ホームページをご覧ください。

ルネサス エレクトロニクス販売株式会社 〒100-0004 千代田区大手町2-6-2(日本ビル)

(03)5201-5307

| ■技術的なお問合せ | および答料の         | ご請求け       | 下記ヘどうぞ。     |

|-----------|----------------|------------|-------------|

|           | 0200 0 25440   | C 114 2/10 |             |

| 終合お問合サ空口  | · http://ianar | renesas    | com/inquiry |

## 22. $\forall J$ $\forall J$

#### 22.1 概要

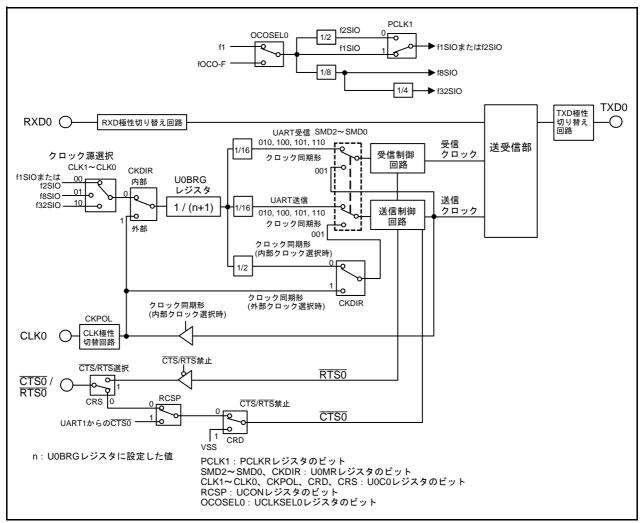

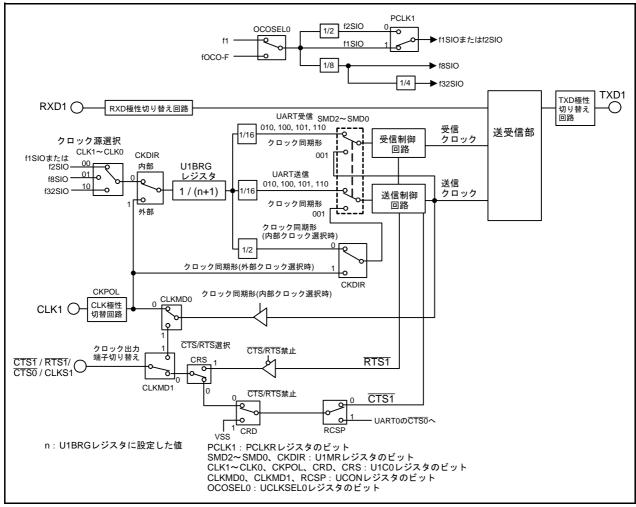

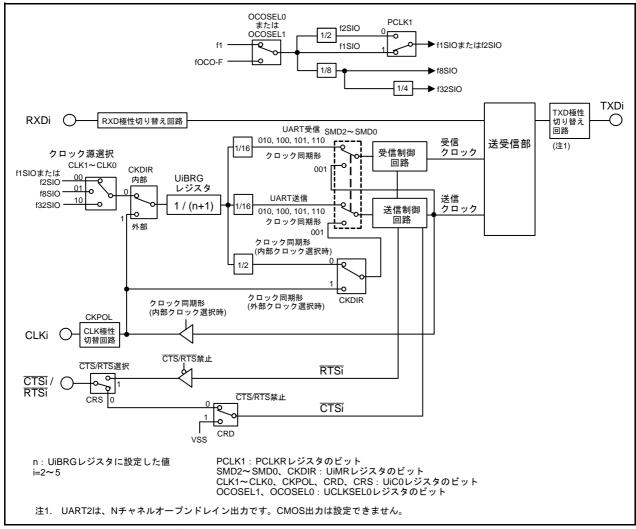

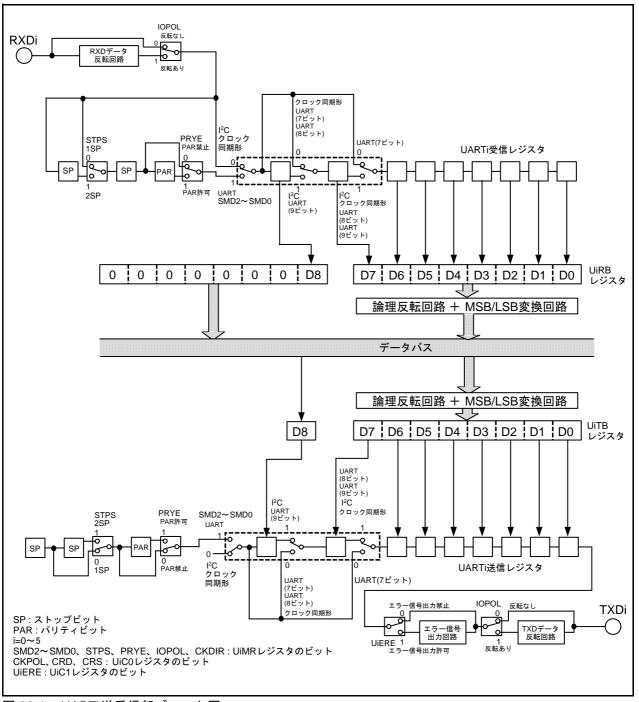

UARTiはそれぞれ専用の送受信クロック発生用タイマを持ち、独立して動作します。 表 22.1 にシリアルインタフェース UARTi ( $i=0\sim5$ )の仕様、表 22.2 にUARTO  $\sim$  UART5 の仕様の相違、 図 22.1~図 22.3にUARTiブロック図、図 22.4にUARTi送受信部ブロック図を示します。

表 22.1 シリアルインタフェース UARTi (i = 0~5)の仕様

| 項目    | 仕様                                      |

|-------|-----------------------------------------|

| 動作モード | • クロック同期形シリアルI/Oモード                     |

|       | ◆クロック非同期形シリアルI/Oモード(UARTモード)            |

|       | ●特殊モード1(I <sup>2</sup> Cモード)            |

|       | 簡易形I <sup>2</sup> Cバスインタフェースに対応したモードです。 |

|       | • 特殊モード2                                |

|       | 送受信クロックの極性と位相を選択できます。                   |

|       | ●特殊モード3(バス衝突検出機能、IEモード)                 |

|       | UARTモードの1バイトの波形でIEBusの1ビットに近似させるモードです。  |

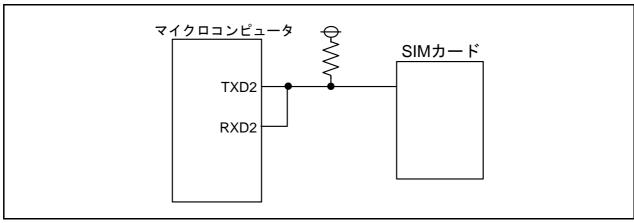

|       | ●特殊モード4(SIMモード)                         |

|       | UART2で使用できます。SIMインタフェースに対応するモードです。      |

#### 表 22.2 UART0~UART5の仕様の相違

| 項目                          | UART0 | UART1 | UART2 | UART3 | UART4 | UART5 |

|-----------------------------|-------|-------|-------|-------|-------|-------|

| クロック同期形シリアルI/Oモード           | あり    |       | あり    | あり    |       | あり    |

| クロック非同期形シリアルI/Oモード          | あり    |       | あり    | あり    |       | あり    |

| (UARTモード)                   |       |       |       |       |       |       |

| 特殊モード1(I <sup>2</sup> Cモード) | あり    |       | あり    | あり    |       | あり    |

| 特殊モード2                      | あり    |       | あり    | あり    |       | あり    |

| 特殊モード3(IEモード)               | あり    |       | あり    | あり    |       | あり    |

| 特殊モード4(SIMモード)              | なし    |       | あり    | なし    |       | なし    |

| メモリ拡張モードまたは                 | 使用でき  | きる    |       | 使用した  | いでく   | 使用で   |

| マイクロプロセッサモード時の使用            |       |       |       | ださい   |       | きる    |

図 22.1 UART0 ブロック図

UART1 ブロック図 図 22.2

図 22.3 UART2~UART5ブロック図

図 22.4 UARTi送受信部ブロック図

## 22.2 レジスタの説明

UART0~UART5 関連レジスタを表 22.3~表 22.4 レジスタ構成に示します。

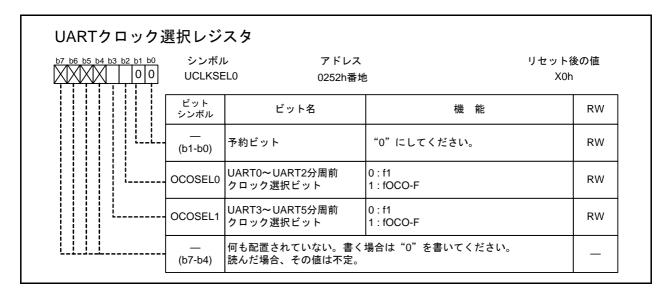

UCLKSEL0 レジスタの OCOSEL0 ビットまたは OCOSEL1 ビットを設定した後、その他の UART0 ~ UART5関連レジスタを設定してください。OCOSEL0ビットまたはOCOSEL1ビットを変更した後も、そ の他のUART0~UART5関連レジスタを再設定してください。

レジスタ、ビットの設定値は、各モードの「使用レジスタと設定値」を参照してください。

#### 表 22.3 レジスタ構成 (1/2)

| アドレス  | レジスタ名            | レジスタシンボル | リセット後の値    |

|-------|------------------|----------|------------|

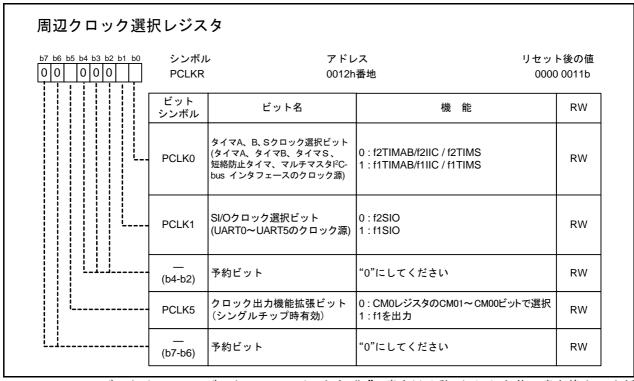

| 0012h | 周辺クロック選択レジスタ     | PCLKR    | 0000 0011b |

| 0244h | UART0特殊モードレジスタ4  | U0SMR4   | 00h        |

| 0245h | UART0特殊モードレジスタ3  | U0SMR3   | 000X 0X0Xb |

| 0246h | UART0特殊モードレジスタ2  | U0SMR2   | X000 0000b |

| 0247h | UART0特殊モードレジスタ   | U0SMR    | X000 0000b |

| 0248h | UART0送受信モードレジスタ  | U0MR     | 00h        |

| 0249h | UART0ビットレートレジスタ  | U0BRG    | XXh        |

| 024Ah | UART0送信バッファレジスタ  | U0TB     | XXh        |

| 024Bh |                  |          | XXh        |

| 024Ch | UART0送受信制御レジスタ0  | U0C0     | 0000 1000b |

| 024Dh | UART0送受信制御レジスタ1  | U0C1     | 00XX 0010b |

| 024Eh | UART0受信バッファレジスタ  | U0RB     | XXh        |

| 024Fh |                  |          | XXh        |

| 0250h | UART送受信制御レジスタ2   | UCON     | X000 0000b |

| 0252h | UARTクロック選択レジスタ   | UCLKSEL0 | X0h        |

| 0254h | UART1特殊モードレジスタ4  | U1SMR4   | 00h        |

| 0255h | UART1特殊モードレジスタ3  | U1SMR3   | 000X 0X0Xb |

| 0256h | UART1特殊モードレジスタ2  | U1SMR2   | X000 0000b |

| 0257h | UART1特殊モードレジスタ   | U1SMR    | X000 0000b |

| 0258h | UART1送受信モードレジスタ  | U1MR     | 00h        |

| 0259h | UART1 ビットレートレジスタ | U1BRG    | XXh        |

| 025Ah | UART1送信バッファレジスタ  | U1TB     | XXh        |

| 025Bh |                  |          | XXh        |

| 025Ch | UART1送受信制御レジスタ0  | U1C0     | 0000 1000b |

| 025Dh | UART1送受信制御レジスタ1  | U1C1     | 00XX 0010b |

| 025Eh | UART1 受信バッファレジスタ | U1RB     | XXh        |

| 025Fh |                  |          | XXh        |

| 0264h | UART2特殊モードレジスタ4  | U2SMR4   | 00h        |

| 0265h | UART2特殊モードレジスタ3  | U2SMR3   | 000X 0X0Xb |

| 0266h | UART2特殊モードレジスタ2  | U2SMR2   | X000 0000b |

| 0267h | UART2特殊モードレジスタ   | U2SMR    | X000 0000b |

| 0268h | UART2送受信モードレジスタ  | U2MR     | 00h        |

| 0269h | UART2ビットレートレジスタ  | U2BRG    | XXh        |

| 026Ah | UART2送信バッファレジスタ  | U2TB     | XXh        |

| 026Bh |                  |          | XXh        |

| 026Ch | UART2送受信制御レジスタ0  | U2C0     | 0000 1000b |

## 表 22.4 レジスタ構成 (2/2)

| アドレス  | レジスタ名            | レジスタシンボル | リセット後の値    |

|-------|------------------|----------|------------|

| 026Dh | UART2送受信制御レジスタ1  | U2C1     | 0000 0010b |

| 026Eh | UART2受信バッファレジスタ  | U2RB     | XXh        |

| 026Fh |                  |          | XXh        |

| 0284h | UART5特殊モードレジスタ4  | U5SMR4   | 00h        |

| 0285h | UART5特殊モードレジスタ3  | U5SMR3   | 000X 0X0Xb |

| 0286h | UART5特殊モードレジスタ2  | U5SMR2   | X000 0000b |

| 0287h | UART5特殊モードレジスタ   | U5SMR    | X000 0000b |

| 0288h | UART5送受信モードレジスタ  | U5MR     | 00h        |

| 0289h | UART5ビットレートレジスタ  | U5BRG    | XXh        |

| 028Ah | UART5送信バッファレジスタ  | U5TB     | XXh        |

| 028Bh |                  |          | XXh        |

| 028Ch | UART5送受信制御レジスタ 0 | U5C0     | 0000 1000b |

| 028Dh | UART5送受信制御レジスタ1  | U5C1     | 0000 0010b |

| 028Eh | UART5受信バッファレジスタ  | U5RB     | XXh        |

| 028Fh |                  |          | XXh        |

| 0294h | UART4特殊モードレジスタ4  | U4SMR4   | 00h        |

| 0295h | UART4特殊モードレジスタ3  | U4SMR3   | 000X 0X0Xb |

| 0296h | UART4特殊モードレジスタ2  | U4SMR2   | X000 0000b |

| 0297h | UART4特殊モードレジスタ   | U4SMR    | X000 0000b |

| 0298h | UART4送受信モードレジスタ  | U4MR     | 00h        |

| 0299h | UART4ビットレートレジスタ  | U4BRG    | XXh        |

| 029Ah | UART4送信バッファレジスタ  | U4TB     | XXh        |

| 029Bh |                  |          | XXh        |

| 029Ch | UART4送受信制御レジスタ 0 | U4C0     | 0000 1000b |

| 029Dh | UART4送受信制御レジスタ1  | U4C1     | 0000 0010b |

| 029Eh | UART4受信バッファレジスタ  | U4RB     | XXh        |

| 029Fh |                  |          | XXh        |

| 02A4h | UART3特殊モードレジスタ4  | U3SMR4   | 00h        |

| 02A5h | UART3特殊モードレジスタ3  | U3SMR3   | 000X 0X0Xb |

| 02A6h | UART3特殊モードレジスタ2  | U3SMR2   | X000 0000b |

| 02A7h | UART3特殊モードレジスタ   | U3SMR    | X000 0000b |

| 02A8h | UART3送受信モードレジスタ  | U3MR     | 00h        |

| 02A9h | UART3ビットレートレジスタ  | U3BRG    | XXh        |

| 02AAh | UART3送信バッファレジスタ  | U3TB     | XXh        |

| 02ABh |                  |          | XXh        |

| 02ACh | UART3送受信制御レジスタ0  | U3C0     | 0000 1000b |

| 02ADh | UART3送受信制御レジスタ1  | U3C1     | 0000 0010b |

| 02AEh | UART3受信バッファレジスタ  | U3RB     | XXh        |

| 02AFh |                  |          | XXh        |

#### UARTクロック選択レジスタ (UCLKSEL0) 22.2.1

## OCOSEL0 (UARTO~UART2分周前クロック選択ビット) (b2) OCOSEL1 (UART3~UART5分周前クロック選択ビット) (b3)

OCOSEL0 ビット、OCOSEL1 ビットは、UART0~UART5の送受信停止中に設定してください。 OCOSEL0ビットまたはOCOSEL1ビットを設定した後、その他のUART0~UART5関連レジスタを設 定してください。OCOSEL0ビットまたはOCOSEL1ビットを変更した後も、その他のUART0~UART5 関連レジスタを再設定してください。

#### 22.2.2 周辺クロック選択レジスタ (PCLKR)

PCLKR レジスタはPRCR レジスタのPRC0 ビットを "1" (書き込み許可)にした後で書き換えてくだ さい。

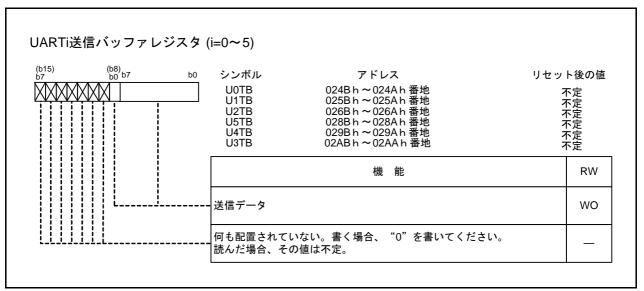

#### 22.2.3 UARTi送信バッファレジスタ (UiTB) (i=0~5)

このレジスタはMOV命令を使用して書いてください。

キャラクタ長が9ビットの場合は、16ビット単位で書くか、または8ビット単位で上位バイトを先に、 下位バイトを後で書いてください。

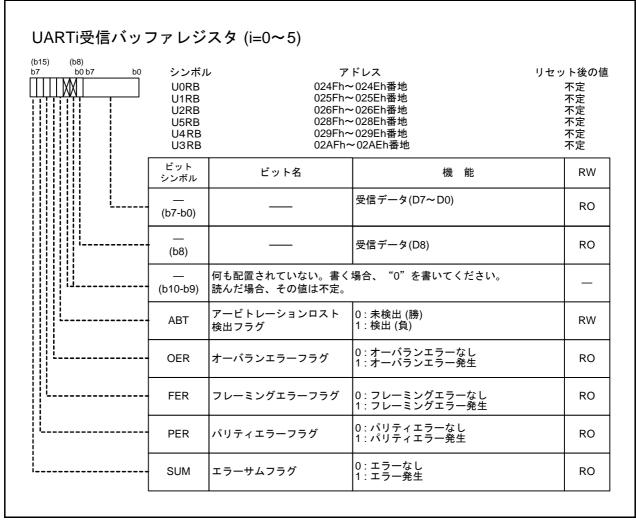

#### UARTi 受信バッファレジスタ (UiRB) (i = 0 ~ 5) 22.2.4

UiMR レジスタの SMD2~ SMD0ビットが"100b"、"101b" または"110b"の場合は、16ビット単位 で読み出すか、または8ビット単位で上位バイトを先に、下位バイトを後で読み出してください。下位 バイトを読み出すと上位バイトに配置されたFER,PERビットが"0"になります。

オーバランエラーが発生したとき、UiRBレジスタの受信データは不定です。

# ABT (アービトレーションロスト検出フラグ) (b11)

ABTビットはプログラムで"0"を書くと"0"になります("1"を書いても変化しません)。

## OER (オーバランエラーフラグ) (b12)

「"0"になる条件]

- •UiMR レジスタの SMD2~ SMD0 ビットが "000b" (シリアルインタフェースは無効)

- •UiC1 レジスタのREビットが "0" (受信禁止)

「"1"になる条件〕

• UiC1 レジスタのRI ビットが "1" (UiRB レジスタにデータあり)かつ次のデータの最終ビットを受 信

## FER (フレーミングエラーフラグ) (b13)

SMD2~SMD0ビットが"001b"(クロック同期形シリアルI/Oモード)または"010b"(I<sup>2</sup>Cモード)の 場合、FERビットは無効です。これらのモードで読んだ場合、その値は不定です。

["0"になる条件]

- UiMR レジスタの SMD2 ~ SMD0 ビットが "000b" (シリアルインタフェースは無効)

- •UiC1レジスタのREビットが0"(受信禁止)

- •UiRB レジスタの下位バイトを読む

「"1"になる条件]

• 設定した個数のストップビットが検出されない (受信データをUARTi受信レジスタからUiRBレジスタに転送するタイミングで検出)

### PER (パリティエラーフラグ) (b14)

SMD2~SMD0ビットが"001b"(クロック同期形シリアルI/Oモード)または"010b"(I2Cモード)の 場合、PERビットは無効です。これらのモードで読んだ場合、その値は不定です。

UiMR レジスタのPRYEビットが"1"(パリティ許可)の場合に有効です。

「"0"になる条件〕

- UiMR レジスタの SMD2 ~ SMD0 ビットが "000b" (シリアルインタフェースは無効)

- •UiC1 レジスタのREビットが0"(受信禁止)

- •UiRB レジスタの下位バイトを読む

["1"になる条件]

•パリティビットとキャラクタビット中の"1"の個数が設定した個数でない (受信データをUARTi受信レジスタからUiRBレジスタに転送するタイミングで検出)

## SUM (エラーサムフラグ) (b15)

SMD2~SMD0ビットが"001b"(クロック同期形シリアルI/Oモード)または"010b"(I<sup>2</sup>Cモード)の 場合は、SUMビット無効です。これらのモードで読んだ場合、その値は不定です。

「"0"になる条件】

- •UiMR レジスタのSMD2~SMD0 ビットが "000b" (シリアルインタフェースは無効)

- •UiC1 レジスタのREビットが0"(受信禁止)

- PER、FER、OER ビットがすべて "0" (エラーなし)

["1"になる条件]

• PER、FER、OER ビットのうち1つ以上が"1"(エラー発生)

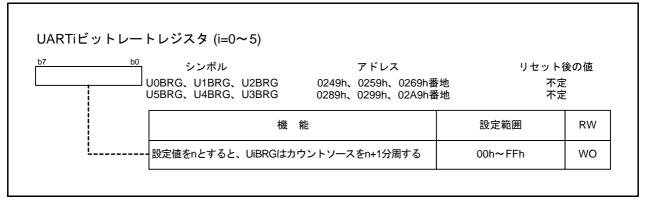

#### UARTi ビットレートレジスタ (UiBRG) $(i = 0 \sim 5)$ 22.2.5

送受信停止中に書いてください。

このレジスタはMOV命令を使用して書いてください。

このレジスタはUiC0レジスタのCLK1~CLK0ビットを設定した後に書いてください。

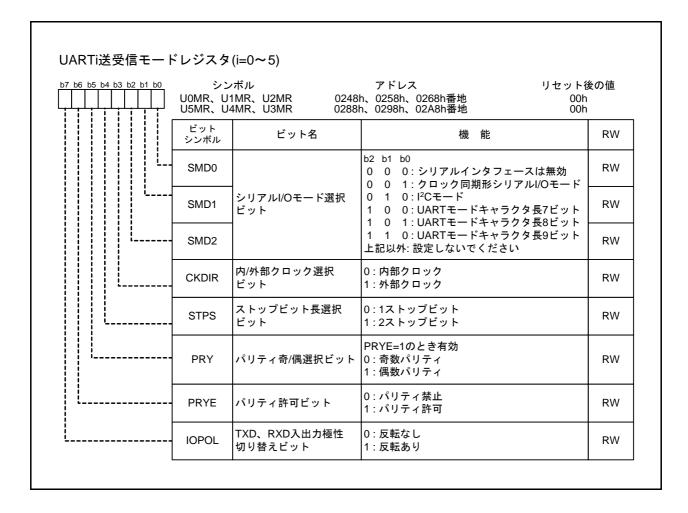

#### 22.2.6 UARTi送受信モードレジスタ (UiMR) (i = 0~5)

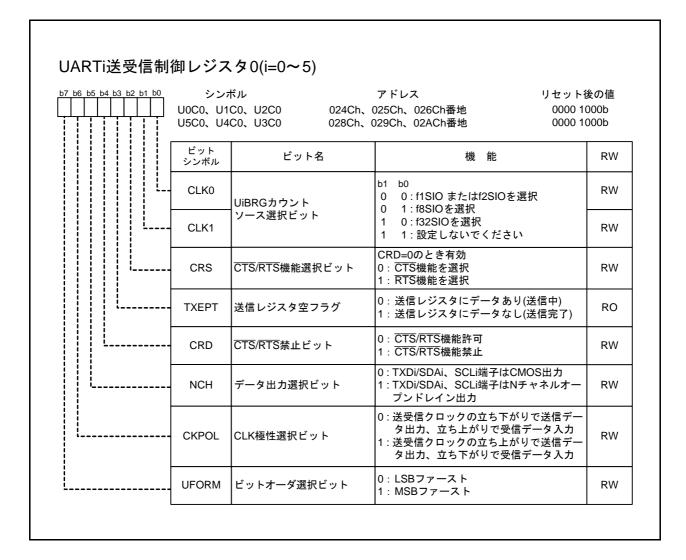

#### UARTi 送受信制御レジスタ 0 (UiC0) (i = 0 ~ 5) 22.2.7

## CLK1~CLK0 (UiBRGカウントソース選択ビット) (b1~b0)

"00b" (f1SIOまたはf2SIOを選択)のとき、PCLKR レジスタのPCLK1 ビットで選択してください。 UCLKSEL0、PCLKRレジスタを設定した後で、CLK1~CLK0を設定してください。 CLK1~CLK0ビットを変更した場合は、UiBRGレジスタを設定してください。

## CRS (CTS/RTS機能選択ビット) (b2)

CTSI/RTSI はUCON レジスタのCLKMD1 ビットが "0" (CLK 出力はCLK1のみ)、かつUCON レジスタ のRCSPビットが"0"(CTS0/RTS0分離しない)のとき使用できます。

## CRD (CTS/RTS禁止ビット) (b4)

CRD ビットが"1"(CTS/RTS 機能禁止)のとき、CTSI/RTSI 端子は入出力ポートとして使用できます。

## NCH (データ出力選択ビット) (b5)

TXD2/SDA2、SCL2は、Nチャネルオープンドレイン出力です。CMOS 出力は設定できません。U2C0 レジスタのNCHビットは、何も配置されていませんので、書く場合"0"を書いてください。

本機能はCMOS出力バッファのPチャネルトランジスタを常時オフにするものであり、TXDi/SDAi、 SCLi端子を完全にオープンドレインにする機能ではありません。

入力できる電圧の範囲については、電気的特性をご確認ください。

### UFORM (ビットオーダ選択ビット) (b7)

UFORM ビットはUiMR レジスタのSMD2 ~ SMD0 ビットが"001b" (クロック同期形シリアルI/Oモー ド)、または"101b"(UARTモードキャラクタ長8ビット)のとき有効です。

SMD2~SMD0ビットが"010b"(I<sup>2</sup>Cモード)のときは"1"に、"100b"(UARTモードキャラクタ長7 ビット)または"110b"(UARTモードキャラクタ長9ビット)のときは"0"にしてください。

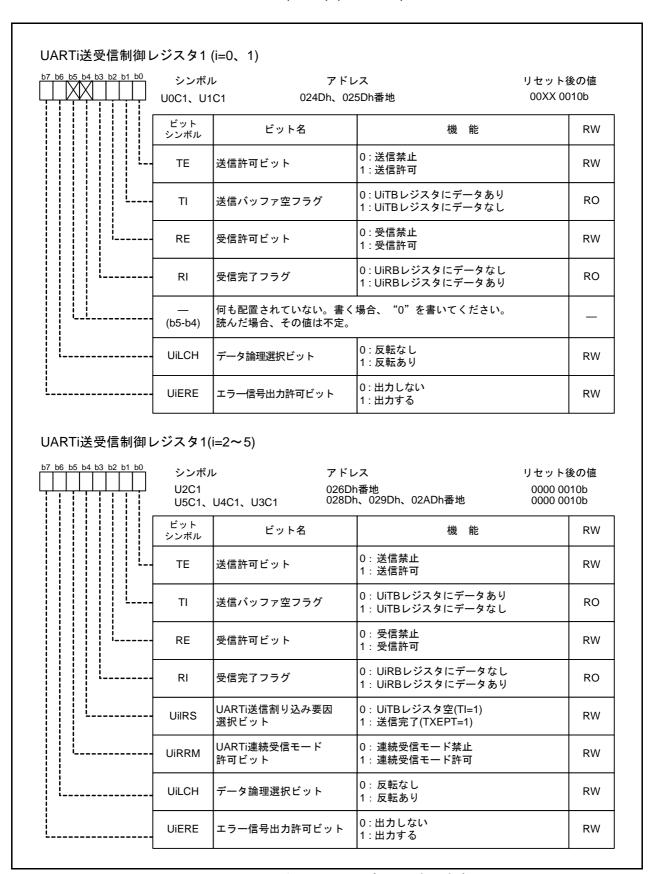

## 22.2.8 UARTi送受信制御レジスタ1 (UiC1) (i = 0~5)

UARTO、UART1のUiIRS、UiRRMビットはUCONレジスタにあります。

## UiLCH (データ論理選択ビット) (b6)

UiLCH ビットは、UiMR レジスタの SMD2 ~ SMD0 ビットが "001b" (クロック同期形シリアル I/O モード)、"100b" (UARTモードキャラクタ長7ビット)または "101b" (UARTモードキャラクタ長8ビッ ト)のとき有効です。SMD2~SMD0ビットが"010b"(I2Cモード)または"110b"(UARTモードキャラ クタ長9ビット)のときは"0"にしてください。

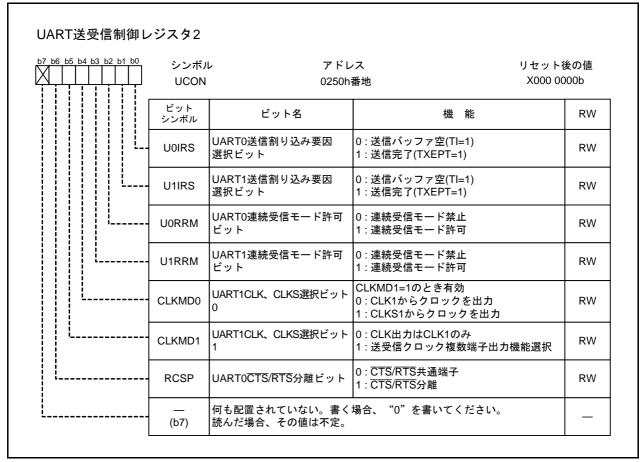

#### 22.2.9 UART送受信制御レジスタ2 (UCON)

UART2~UART5のUiRS、UiRRMビットはUiC1レジスタにあります。

#### CLKMD1 (UART1CLK、CLKS選択ビット1) (b5)

複数の送受信クロック出力端子を使用する場合、次の条件を満たしてください。 U1MR レジスタの CKDIR ビット=0 (内部クロック)

## 22.2.10 UARTi 特殊モードレジスタ (UiSMR) (i = 0~5)

| b7 b6 b5 b4 b3 b2 b1 b0 | UOSMR, U    |                                | アドレス リセット<br>7h、0257h、0267h番地 X000 0<br>7h、0297h、02A7h番地 X000 0 | 000b |

|-------------------------|-------------|--------------------------------|-----------------------------------------------------------------|------|

|                         | ビット<br>シンボル | ビット名                           | 機能                                                              | RW   |

|                         | IICM        | P <sup>2</sup> Cモード選択ビット       | 0: I <sup>2</sup> Cモード以外<br>1: I <sup>2</sup> Cモード              | RW   |

|                         | ABC         | アービトレーションロスト<br>検出フラグ制御ビット     | 0 : ビットごとに更新<br>1 : バイトごとに更新                                    | RW   |

|                         | BBS         | バスビジーフラグ                       | 0 : ストップコンディション検出<br>1 : スタートコンディション検出(ビジー)                     | RW   |

|                         | —<br>(b3)   | 予約ビット                          | "0" にしてください。                                                    | RW   |

|                         | ABSCS       | バス衝突検出サンプリング<br>クロック選択ビット      | 0 : 送受信クロックの立ち上がり<br>1 : タイマAjのアンダフロー信号                         | RW   |

|                         | ACSE        | 送信許可ビット自動クリア<br>機能選択ビット        | 0 : 自動クリア機能なし<br>1 : バス衝突発生時自動クリア                               | RW   |

|                         | SSS         | 送信開始条件選択ビット                    | 0:RXDiに同期しない<br>1:RXDiに同期する                                     | RW   |

|                         | <br>(b7)    | 何も配置されていない。書く<br>読んだ場合、その値は不定。 | 場合、"0"を書いてください。                                                 | _    |

## BBS (バスビジーフラグ) (b2)

BBSビットはプログラムで"0"を書くと"0"になります("1"を書いても変化しません)。

## ABSCS (バス衝突検出サンプリングクロック選択ビット) (b4)

ABSCS ビットが"1"の場合のUARTiとタイマAjの組み合わせは次のとおりです。

UART0、UART4:タイマA3のアンダフロー信号 UART1、UART3:タイマA4のアンダフロー信号 UART2、UART5:タイマA0のアンダフロー信号

## SSS (送信開始条件選択ビット) (b6)

送信が始まると、SSSビットは"0"(RXDiに同期しない)になります。

# 22.2.11 UARTi特殊モードレジスタ2 (UiSM2) (i=0~5)

| b7 b6 b5 b4 b3 b2 b1 b0 | U0SMR2、     | ンボル<br>U1SMR2、U2SMR2 024<br>U4SMR2、U3SMR2 028 | 6h、0256h、0266h番地 X00                 | ット後の値<br>00 0000b<br>00 0000b |

|-------------------------|-------------|-----------------------------------------------|--------------------------------------|-------------------------------|

|                         | ビット<br>シンボル | ビット名                                          | 機能                                   | RW                            |

|                         | IICM2       | I <sup>2</sup> Cモード選択ビット2                     | 「表 22.18 I <sup>2</sup> Cモード時の各機能 」参 | 照 RW                          |

|                         | CSC         | クロック同期化ビット                                    | 0:禁止1:許可                             | RW                            |

|                         | SWC         | SCLウェイト出力ビット                                  | 0:禁止1:許可                             | RW                            |

|                         | ALS         | SDA出力停止ビット                                    | 0:禁止<br>1:許可                         | RW                            |

|                         | STAC        | UARTi初期化ビット                                   | 0:禁止1:許可                             | RW                            |

| L                       | SWC2        | SCLウェイト出力ビット2                                 | 0 : 送受信クロック<br>1 : "L"出力             | RW                            |

|                         | SDHI        | SDA出力禁止ビット                                    | 0 : 許可<br>1 : 禁止(ハイインピーダンス)          | RW                            |

|                         | —<br>(b7)   | 何も配置されていない。書く<br>読んだ場合、その値は不定。                | 場合、"0"を書いてください。                      | _                             |

# 22.2.12 UARTi特殊モードレジスタ3 (UiSMR3) (i = 0~5)

| b7 b6 b5 b4 b3 b2 b1 b0 | U0SMR3、     | ンンボル<br>U1SMR3、U2SMR3<br>U4SMR3、U3SMR3 | アドレス リセット値<br>0245h、0255h、0265h番地 000X 0X<br>0285h、0295h、02A5h番地 000X 0X                      | 0Xb |

|-------------------------|-------------|----------------------------------------|-----------------------------------------------------------------------------------------------|-----|

|                         | ビット<br>シンボル | ビット名                                   | 機能                                                                                            | RW  |

| <u> </u>                | (b0)        | 何も配置されていない。<br>読んだ場合、その値は不足            | ・<br><b>書く場合、"0"を書いてください。</b><br>こ。                                                           |     |

|                         | СКРН        | クロック位相設定ビット                            | 0:クロック遅れなし<br>1:クロック遅れあり                                                                      | RW  |

|                         | —<br>(b2)   | 何も配置されていない。 書<br>読んだ場合、その値は不足          | ・<br>書く場合、"O"を書いてください。<br>E。                                                                  | _   |

|                         | NODC        | クロック出力選択ビット                            | 0 : CLKiはCMOS出力<br>1 : CLKiはNチャネルオープンドレイン出力                                                   | RW  |

|                         | —<br>(b4)   | 何も配置されていない。 書<br>読んだ場合、その値は不足          | ・<br>書く場合、 "0" を書いてください。<br>E。                                                                |     |

|                         | DL0         |                                        | b7 b6 b5<br>0 0 0:遅延なし<br>0 0 1: UiBRGカウントソースの1~2サイクル                                         | RW  |

|                         | DL1         | SDAiデジタル<br>遅延値設定ビット                   | 0 1 0: UiBRGカウントソースの2~3サイクル<br>0 1 1: UiBRGカウントソースの3~4サイクル<br>1 0 0: UiBRGカウントソースの4~5サイクル     | RW  |

|                         | DL2         |                                        | 1 0 1: UiBRGカウントソースの5~6サイクル<br>  1 1 0: UiBRGカウントソースの6~7サイクル<br>  1 1 1: UiBRGカウントソースの7~8サイクル | RW  |

# DL2~DL0 (SDAiデジタル遅延値設定ビット) (b7~b5)

DL2~DL0ビットはI2Cモードで、SDAi出力にデジタル的に遅延を発生させるものです。I2Cモード 以外の場合、"000b"(遅延なし)にしてください。

遅延量はSCLi端子、SDAi端子の負荷により変化します。また、外部クロックを使用した場合には、 100ns程度、遅延が大きくなります。

## NODC (クロック出力選択ビット) (b3)

本機能はCMOS 出力バッファのPチャネルトランジスタを常時オフにするものであり、CLKi 端子を 完全にオープンドレインにする機能ではありません。

入力できる電圧の範囲については、電気的特性をご確認ください。

# 22.2.13 UARTi特殊モードレジスタ4 (UiSMR4) (i = 0~5)

| 07 b6 b5 b4 b3 b2 b1 b0 | U0SMR4、     |                       | アドレス リセット<br>4h、0254h、0264h番地 00h<br>4h、0294h、02A4h番地 00h               |    |

|-------------------------|-------------|-----------------------|-------------------------------------------------------------------------|----|

|                         | ビット<br>シンボル | ビット名                  | 機能                                                                      | RW |

| <u> </u>                | STAREQ      | スタートコンディション<br>生成ビット  | 0: クリア<br>1: スタート                                                       | RW |

|                         | RSTAREQ     | リスタートコンディション<br>生成ビット | 0: クリア<br>1: スタート                                                       | RW |

|                         | STPREQ      | ストップコンディション<br>生成ビット  | 0: クリア<br>1: スタート                                                       | RW |

|                         | STSPSEL     | SCL、SDA出力選択ビット        | 0:スタートコンディション、ストップコ<br>ンディション出力しない<br>1:スタートコンディション、ストップコ<br>ンディション出力する | RW |

|                         | ACKD        | ACKデータビット             | 0 : ACK<br>1 : NACK                                                     | RW |

|                         | ACKC        | ACKデータ出力許可ビット         | 0:シリアルインタフェースデータ出力<br>1:ACKデータ出力                                        | RW |

|                         | SCLHI       | SCL出力停止許可ビット          | 0:禁止<br>1:許可                                                            | RW |

|                         | SWC9        | SCLウェイトビット3           | 0 : SCL "L" ホールド禁止<br>1 : SCL "L" ホールド許可                                | RW |

## STAREQ (スタートコンディション生成ビット) (b0)

スタートコンディションが生成されたとき、"0"になります。

# RSTAREQ (リスタートコンディション生成ビット) (b1)

リスタートコンディションが生成されたとき、"0"になります。

# STPREQ (ストップコンディション生成ビット) (b2)

ストップコンディションが生成されたとき、"0"になります。

## 22.3 動作説明

## 22.3.1 クロック同期形シリアルI/Oモード

クロック同期形シリアルI/Oモードは、送受信クロックを用いて送受信を行うモードです。表 22.5 に クロック同期形シリアルI/Oモードの仕様を示します。

表 22.5 クロック同期形シリアルI/Oモードの仕様

| 仕様                                                                |

|-------------------------------------------------------------------|

| キャラクタ長 8ビット                                                       |

| ●UiMR レジスタのCKDIR ビットが 0 (内部クロック):                                 |

| <u>fj</u>                                                         |

| $\overline{2(n+1)}$                                               |

| fj=f1SIO、f2SIO、f8SIO、f32SIO n=UiBRG レジスタの設定値 00h~FFh              |

| ●CKDIR ビットが1 (外部クロック):CLKi端子からの入力                                 |

| CTS機能、RTS機能、CTS/RTS機能禁止を選択可                                       |

| 送信開始には、次の条件が必要(注1)                                                |

| ● UiC1 レジスタの TE ビットが"1" (送信許可)                                    |

| •UiC1レジスタのTIビットが"0"(UiTBレジスタにデータあり)                               |

| ● CTS 機能を選択している場合、 CTSi 端子の入力が "L"                                |

| 受信開始には、次の条件が必要(注1)                                                |

| ● UiC1 レジスタの RE ビットが"1" (受信許可)                                    |

| ● UiC1 レジスタの TE ビットが"1" (送信許可)                                    |

| ●UiC1レジスタのTIビットが"0"(UiTBレジスタにデータあり)                               |

| 送信割り込み 次のいずれかを選択可                                                 |

| ●UilRS ビットが "0" (送信バッファ空):                                        |

| UiTB レジスタから UARTi 送信 レジスタヘデータ転送時 (送信開始時)                          |

|                                                                   |

| 受信割り込み                                                            |

| • UARTi 受信レジスタから UiRB レジスタヘデータ転送時 (受信完了時)                         |

| オーバランエラー (注2)<br>  UiRB レジスタを読む前に次のデータ受信を開始し、次のデータの7ビット目を受信       |

| OIRD レンスタを読む前に次のナータ受信を開始し、次のナータの7とット日を受信<br>すると発生                 |

| ● CLK 極性選択                                                        |

| * CLN極性選択<br>  データの出力と入力タイミングが、送受信クロックの立ち上がりか立ち下がりか               |

| を選択可                                                              |

| •LSBファースト、MSBファースト選択                                              |

| ビット0から送受信するか、またはビット7から送受信するかを選択可                                  |

| ●連続受信モード選択                                                        |

| UiRB レジスタを読むことで、同時に受信許可状態になる                                      |

| ●シリアルデータ論理切り替え<br>※※ほご、4の診理はよりによる####                             |

| 送受信データの論理値を反転する機能<br>・送受信クロック複数端子出力選択(UART1)                      |

| ▼送受信グロック複数端子出力選択(OARTT)<br>  UART1の送受信クロック端子を2本設定し、プログラムで出力端子を選択可 |

| Ontition                                                          |

| CTSOとRTSOを別の端子から入出力する                                             |

|                                                                   |

### i=0 **~** 5

- 注1. 外部クロックを選択している場合、UiCOレジスタのCKPOLビットが"0"(送受信クロックの立ち下がりで送信データ出力、立ち上がりで受信データ入力)のときは外部クロックが"H"の状態で、CKPOLビットが"1"(送受信クロックの立ち上がりで送信データ出力、立ち下がりで受信データ入力)のときは外部クロックが"L"の状態で条件を満たしてください。

- 注2. オーバランエラーが発生した場合、UiRBレジスタ受信データは不定になります。またSiRICレジスタのIRビットは変化しません。

表 22.6にクロック同期形シリアルI/Oモード時の入出力端子の機能を示します。表 22.6は、送受信ク ロック複数端子出力選択機能を非選択の場合です。また、表 22.7 にクロック同期形シリアルI/Oモード 時のP6 4端子の機能を示します。

なお、UARTiの動作モード選択後、送信開始までは、TXDi端子は"H"を出力します(Nチャネル オープンドレイン出力選択時はハイインピーダンス状態)。

表 22.6 クロック同期形シリアルI/Oモード時の入出力端子の機能(送受信クロック複数端子出力機能を 非選択の場合)

| 端子名       | 入出力 | 機 能       | 選択方法                                      |

|-----------|-----|-----------|-------------------------------------------|

| TXDi      | 出力  | シリアルデータ出力 | (受信だけを行うときはダミーデータを出力)                     |

| RXDi      | 入力  | シリアルデータ入力 | 端子を共用するポートの方向ビットを"0"にする                   |

|           | 入力  | 入力ポート     | ポートの方向ビットを "0" にする(送信だけを行うときは入力ポートとして使用可) |

| CLKi      | 出力  | 送受信クロック出力 | UiMR レジスタのCKDIR ビット=0                     |

|           | 入力  | 送受信クロック入力 | UiMR レジスタのCKDIR ビット=1                     |

|           |     |           | 端子を共用するポートの方向ビットを"0"にする                   |

| CTSi/RTSi | 入力  | CTS入力     | UiC0レジスタのCRDビット=0                         |

|           |     |           | UiC0 レジスタのCRS ビット=0                       |

|           |     |           | 端子を共用するポートの方向ビットを"0"にする                   |

|           | 出力  | RTS出力     | UiC0 レジスタのCRD ビット=0                       |

|           |     |           | UiC0 レジスタのCRS ビット=1                       |

|           | 入出力 | 入出力ポート    | UiC0 レジスタのCRD ビット=1                       |

$i=0 \sim 5$

表 22.7 クロック同期形シリアルI/Oモード時のP6\_4端子の機能

| 端子の機能     | ビットの設定値   |     |           |        |        |           |  |

|-----------|-----------|-----|-----------|--------|--------|-----------|--|

|           | U1C0 レジスタ |     | UCON レジスタ |        |        | PD6 レジスタ  |  |

|           | CRD       | CRS | RCSP      | CLKMD1 | CLKMD0 | PD6_4     |  |

| P6_4      | 1         | _   | 0         | 0      | _      | 入力:0、出力:1 |  |

| CTS1      | 0         | 0   | 0         | 0      | _      | 0         |  |

| RTS1      | 0         | 1   | 0         | 0      |        | _         |  |

| CTS0 (注1) | 0         | 0   | 1         | 0      | _      | 0         |  |

| CLKS1     | _         | _   | _         | 1(注2)  | 1      | _         |  |

-: "0" または "1"

- 注1. この他にU0C0 レジスタの CRD ビットを "0" (CTSO/RTSO 許可)、U0C0 レジスタの CRS ビットを "1" (RTSO選択)にしてください。

- 注2. CLKMD1 ビットが"1"でCLKMD0 ビットが"0"の場合は、次のレベルを出力します。

- U1C0 レジスタの CKPOL ビットが "0": H

- U1C0 レジスタの CKPOL ビットが "1": L

表 22.8にクロック同期形シリアルI/Oモード時の使用レジスタと設定値を示します。

表 22.8 クロック同期形シリアルI/Oモード時の使用レジスタと設定値 (注2)

| レジスタ     | ビット        | 機能                                   |  |  |  |

|----------|------------|--------------------------------------|--|--|--|

| UCLKSEL0 | OCOSEL0    | UART0~UART2の分周前クロックを選択してください。        |  |  |  |

|          | OCOSEL1    | UART3~UART5の分周前クロックを選択してください。        |  |  |  |

| PCLKR    | PCLK1      | UiBRGのカウントソースを選択してください。              |  |  |  |

| UiTB     | 0~7        | 送信データを設定してください                       |  |  |  |

|          | 8          | - (設定しないでよい) 書く場合は"0"にしてください         |  |  |  |

| UiRB     | 0~7        | 受信データが読めます                           |  |  |  |

|          | 8、11、13~15 | 読んだ場合、その値は不定                         |  |  |  |

|          | OER        | オーバランエラーフラグ                          |  |  |  |

| UiBRG    | 0~7        | ビットレートを設定してください                      |  |  |  |

| UiMR     | SMD2~SMD0  | "001b" にしてください                       |  |  |  |

|          | CKDIR      | 内部クロック、外部クロックを選択してください               |  |  |  |

|          | 4~6        | "0" にしてください                          |  |  |  |

|          | IOPOL      | "0" にしてください                          |  |  |  |

| UiC0     | CLK1~CLK0  | UiBRGのカウントソースを選択してください               |  |  |  |

|          | CRS        | CTS または RTS を使用する場合、どちらかを選択してください    |  |  |  |

|          | TXEPT      | 送信レジスタ空フラグ                           |  |  |  |

|          | CRD        | CTS または RTS 機能の許可、または禁止を選択してください     |  |  |  |

|          | NCH        | TXDi端子の出力形式を選択してください(注1)             |  |  |  |

|          | CKPOL      | 送受信クロックの極性を選択してください                  |  |  |  |

|          | UFORM      | LSBファースト、またはMSBファーストを選択してください        |  |  |  |

| UiC1     | TE         | 送受信を許可する場合、"1"にしてください                |  |  |  |

|          | TI         | 送信バッファ空フラグ                           |  |  |  |

|          | RE         | 受信を許可する場合、"1"にしてください                 |  |  |  |

|          | RI         | 受信完了フラグ                              |  |  |  |

|          | UjIRS      | UARTj送信割り込み要因を選択してください               |  |  |  |

|          | UjRRM      | 連続受信モードを使用する場合、"1"にしてください            |  |  |  |

|          | UiLCH      | データ論理反転を使用する場合、"1"にしてください            |  |  |  |

|          | UiERE      | "0" にしてください                          |  |  |  |

| UiSMR    | 0~7        | "0" にしてください                          |  |  |  |

| UiSMR2   | 0~7        | "0" にしてください                          |  |  |  |

| UiSMR3   | 0~2        | "0" にしてください                          |  |  |  |

|          | NODC       | クロック出力形式を選択してください                    |  |  |  |

|          | 4~7        | "0" にしてください                          |  |  |  |

| UiSMR4   | 0~7        | "0" にしてください                          |  |  |  |

| UCON     | U0IRS      | UARTO送信割り込み要因を選択してください               |  |  |  |

|          | U1IRS      | UART1送信割り込み要因を選択してください               |  |  |  |

|          | U0RRM      | 連続受信モードを使用する場合、"1"にしてください            |  |  |  |

|          | U1RRM      | 連続受信モードを使用する場合、"1"にしてください            |  |  |  |

|          | CLKMD0     | CLKMD1=1のとき送受信クロックを出力する端子を選択してください   |  |  |  |

|          | CLKMD1     | UART1の送受信クロックを2端子から出力する場合、"1"にしてください |  |  |  |

|          | RCSP       | UARTOのCTSO/RTSを分離する場合、"1"にしてください     |  |  |  |

|          | 7          | "0" にしてください                          |  |  |  |

$i=0 \sim 5$   $j=2 \sim 5$

- 注1. TXD2端子はNチャネルオープンドレインです。U2C0レジスタのNCHビットは、何も配置されてい ませんので、書く場合"0"を書いてください。

- 注2. この表は手順を示すものではありません。

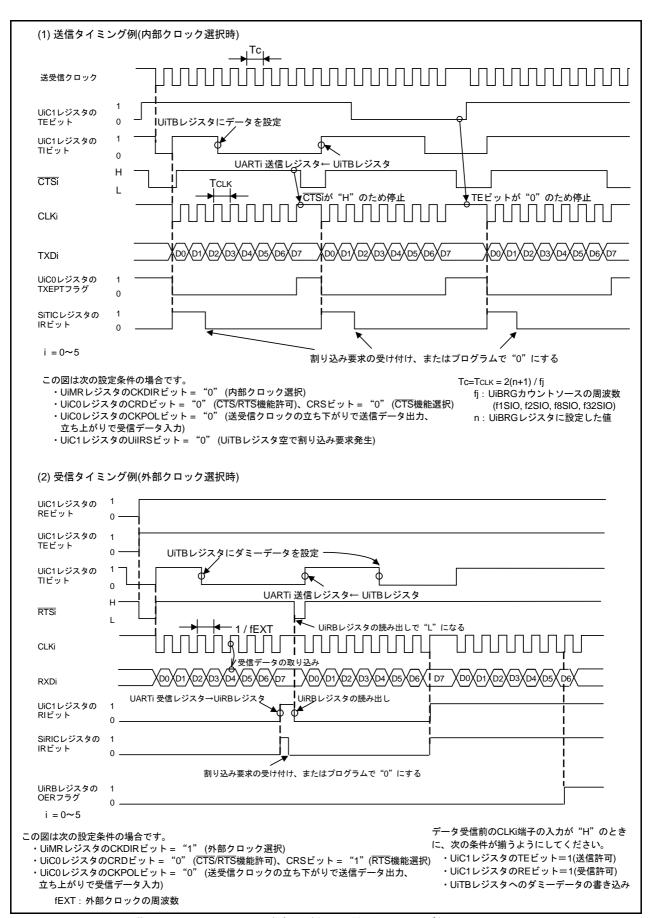

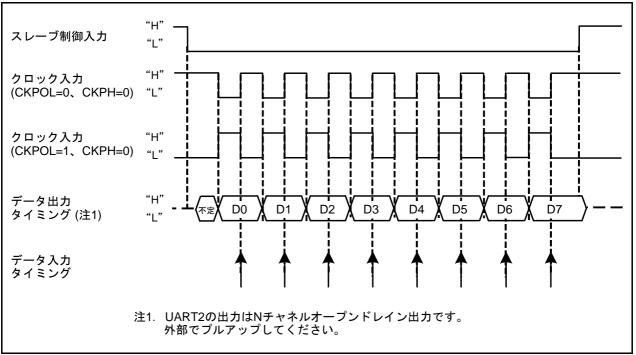

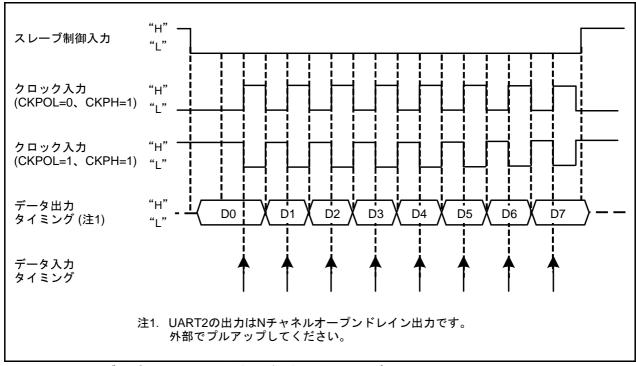

図 22.5 クロック同期形シリアルI/Oモード時の送信、受信タイミング例

#### 送受信レジスタの初期化 22.3.1.1

送受信中断などで、送受信レジスタを初期化する場合は、次のようにしてください。

- UiRB レジスタ (i = 0 ~ 5) の初期化手順

- (1)UiC1レジスタのREビットを "0" (受信禁止)にする。

- (2) UiMR レジスタのSMD2~SMD0 ビットを "000b" (シリアルインタフェース無効)にする。

- (3) UiMR レジスタの SMD2~SMD0 ビットを "001b" (クロック同期形シリアルI/Oモード)にする。

- (4)UiC1レジスタのREビットを"1"(受信許可)にする。

- •UiTB レジスタの初期化手順

- (1) UiMR レジスタのSMD2~SMD0 ビットを "000b" (シリアルインタフェース無効)にする。

- (2) UiMR レジスタの SMD2 ~ SMD0 ビットを "001b" (クロック同期形シリアルI/Oモード)にす

- (3) UiC1 レジスタのTEビットの値にかかわらず"1"(送信許可)を書き込む。

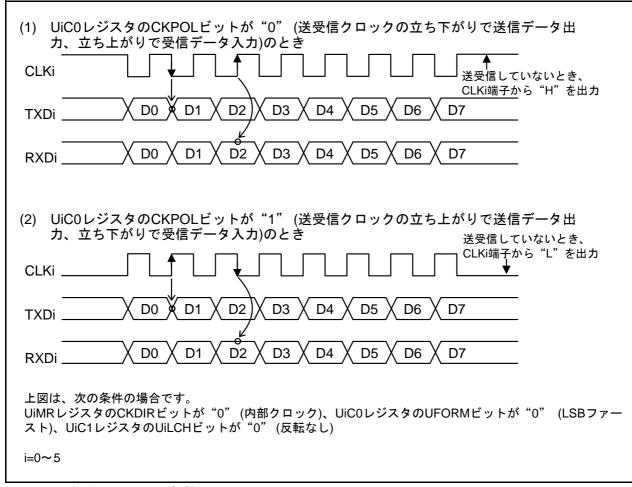

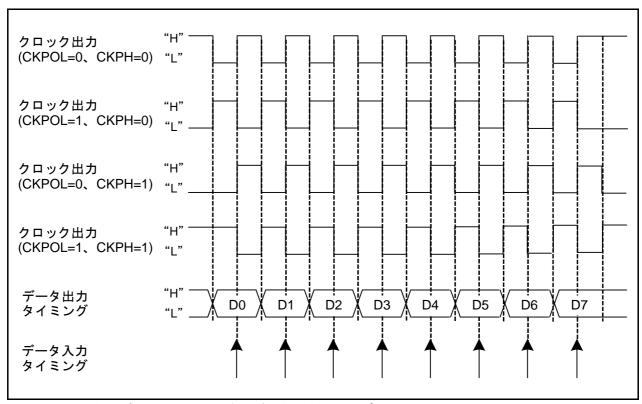

### 22.3.1.2 CLK極性選択

UiC0 レジスタ ( $i=0\sim5$ )のCKPOL ビットで送受信クロックの極性を選択できます。図 22.6に送受信 クロックの極性を示します。

図 22.6 送受信クロックの極性

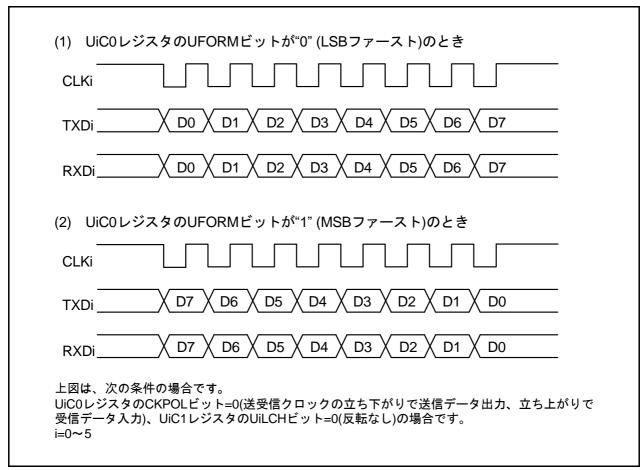

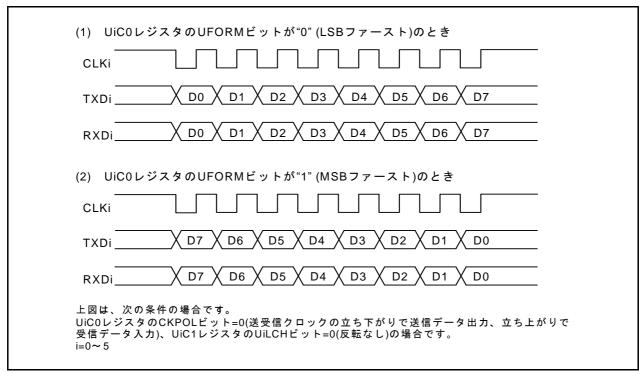

## 22.3.1.3 LSBファースト、MSBファースト選択

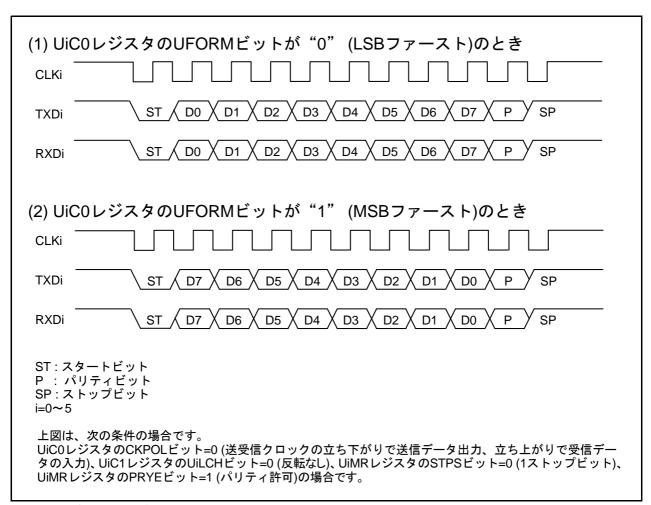

UiC0レジスタ ( $i=0\sim5$ )のUFORMビットでビットオーダを選択できます。図 22.7にビットオーダを 示します。

図 22.7 ビットオーダ

## 22.3.1.4 連続受信モード

連続受信モードは、受信バッファレジスタを読み出すことで受信許可状態になるモードです。このモードを選択すれば、受信許可状態にするために、送信バッファレジスタにダミーのデータを書き込む必要はありません。ただし、受信開始時には、ダミーで受信バッファレジスタを読み出す必要があります。

UiRRM ビット( $i=0\sim5$ )を"1"(連続受信モード)にすると、UiRB レジスタを読むことでUiC1 レジスタのTI ビットが0 (UiTB レジスタにデータあり)になります。UiRRM ビットが"1"の場合、プログラムでUiTB レジスタにダミーデータを書かないでください。

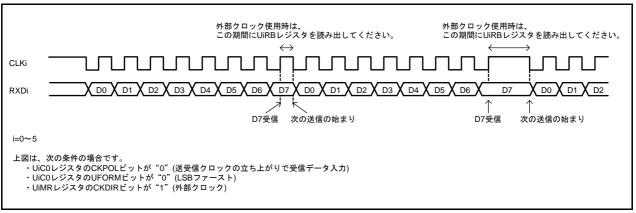

外部クロック使用時は、8ビット目のデータを受信してから、次の送信が始まるまでにUiRBレジスタを読み出してください。

図 22.8に連続受信モードの動作例を示します。

図 22.8 連続受信モードの動作例

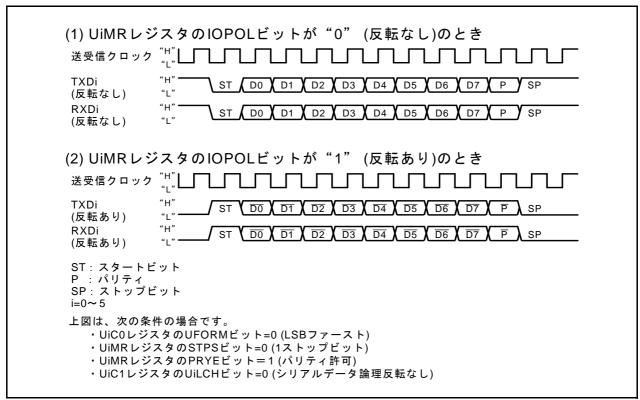

#### シリアルデータ論理切り替え 22.3.1.5

UiC1 レジスタ ( $i=0\sim5$ )のUiLCH ビットが"1"(反転あり)の場合、UiTB レジスタに書いた値の論理 を反転して送信します。UiRBレジスタを読むと、受信データの論理を反転した値が読めます。図 22.9 にシリアルデータ論理を示します。

図 22.9 シリアルデータ論理

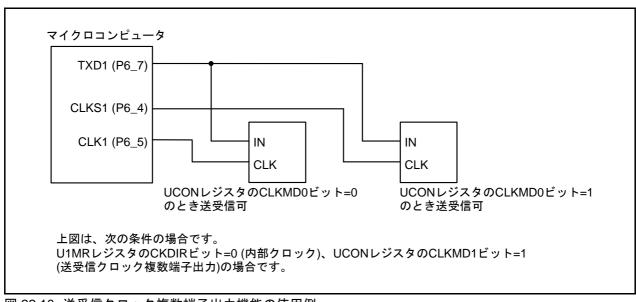

#### 送受信クロック複数端子出力選択 (UART1) 22.3.1.6

UCON レジスタの CLKMD1 ~ CLKMD0 ビットで2本の送受信クロック出力端子から1本を選択でき ます(図 22.10)。この機能は、UART1の送受信クロックが内部クロックの場合に使用できます。

図 22.10 送受信クロック複数端子出力機能の使用例

### 22.3.1.7 CTS/RTS機能

CTS 機能は、CTSi/RTSi(i=0~5)端子に "L" を入力すると、送受信を開始させる機能です。CTSi/RTSi 端子の入力レベルが "L" になると、送受信を開始します。送受信の最中に入力レベルを "H" にした 場合、次のデータから送受信を停止します。

RTS機能は、受信準備が整ったとき、CTSi/RTSi端子の出力レベルが"L"になります。CLKi端子の 最初の立ち下がりで出力レベルが"H"になります。

端子の機能選択は「表 22.6 クロック同期形シリアルI/Oモード時の入出力端子の機能(送受信クロッ ク複数端子出力機能を非選択の場合)」を参照してください。

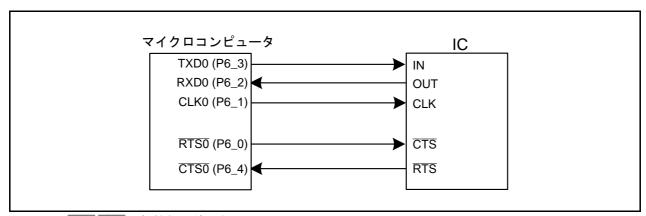

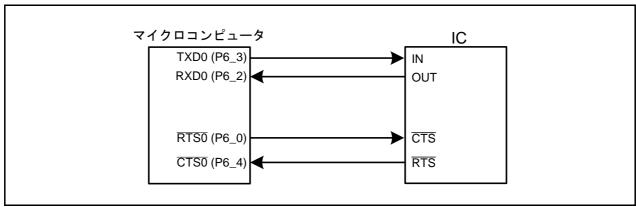

## 22.3.1.8 CTS/RTS 分離機能 (UARTO)

CTS0/RTS0を分離し、RTS0をP6\_0端子から出力、CTS0をP6\_4端子から入力する機能です。この機能 を使用する場合は次のようにしてください。

- U0C0 レジスタのCRD ビット=0 (UART0のCTS/RTS許可)

- U0C0 レジスタの CRS ビット=1 (UART0の RTS 出力)

- •U1C0レジスタのCRDビット=0(UART1のCTS/RTS許可)

- •U1C0レジスタのCRSビット=0(UART1のCTS入力)

- •UCON レジスタのRCSPビット=1(CTSOをP6 4端子から入力)

- •UCONレジスタのCLKMD1ビット=0(CLKS1を使用しない)

なお、CTS/RTS分離機能使用時、UART1のCTS/RTS機能は使用できません。

図 22.11 CTS/RTS 分離機能の使用例

# 22.3.2 クロック非同期形シリアルI/O (UART)モード

UARTモードは、任意のビットレート、ビットオーダを設定して送受信を行うモードです。表 22.9に UARTモードの仕様を示します。

表 22.9 UARTモードの仕様

| 項目                      |                                   | 仕様                                        |

|-------------------------|-----------------------------------|-------------------------------------------|

| データフォーマット               | • キャラクタビット                        | 7ビット、8ビット、9ビットを選択可                        |

|                         | •スタートビット                          | 1ビット                                      |

|                         | •パリティビット                          | 奇数、偶数、なしを選択可                              |

|                         | •ストップビット                          | 1ビット、2ビットを選択可                             |

| 送受信クロック                 | • UiMR レジスタの CKDIR                | ビットが0 (内部クロック) :                          |

|                         | fj                                |                                           |

|                         | 16(n+1)                           |                                           |

|                         | fj=f1SIO、f2SIO、f8SIO              | )、f32SIO n=UiBRG レジスタの設定値 00h~FFh         |

|                         | • CKDIR ビットが "1" (外               | 部クロック):                                   |

|                         | $\frac{\text{fEXT}}{16(n+1)}$     |                                           |

|                         | , ,                               | 入力 n=UiBRG レジスタの設定値 00h~FFh               |

| <b>・ソ によりなり</b> マ によりなり |                                   |                                           |

| 送信制御、受信制御               | CTS機能、RTS機能、CTS                   |                                           |

| 送信開始条件                  | 送信開始には、次の条件が<br>• UiC1 レジスタの TE ビ | ·                                         |

|                         |                                   | ットが 1 (医信計可)<br>ットが "0" (UiTB レジスタにデータあり) |

|                         |                                   | ・る場合、CTSi端子の入力が "L"                       |

|                         | 受信開始には、次の条件が                      |                                           |

| 文品册和末仟                  | • UiC1 レジスタのRE ビ                  |                                           |

|                         | <ul><li>スタートビットの検出</li></ul>      | ` ' '                                     |

| 割り込み要求発生タイミング           | 送信割り込み 次の条件の                      |                                           |

|                         | • UilRS ビットが "0" (違               |                                           |

|                         | •                                 | JARTi送信レジスタヘデータ転送時(送信開始時)                 |

|                         | 1                                 | 送信完了):UARTi送信レジスタからデータ送信完了時               |

|                         | 受信割り込み                            |                                           |

|                         |                                   | らUiRB レジスタヘデータ転送時 (受信完了時)                 |

| エラー検出                   | •オーバランエラー(注1)                     | UiRB レジスタを読む前に次のデータ受信を開始し、次               |

|                         |                                   | のデータの最終ストップビットの1つ前のビットを受信<br>すると発生        |

|                         | <br> •フレーミングエラー                   | 9 のこ光エ  <br>設定した個数のストップビットが検出されなかったと      |

|                         |                                   | きに発生                                      |

|                         | •パリティエラー                          | パリティ許可時にパリティビットとキャラクタビット                  |

|                         |                                   | 中の1の個数が設定した個数でなかったときに発生                   |

|                         | •エラーサムフラグ                         | オーバランエラー、フレーミングエラー、パリティエ                  |

| 755 TO 1919 PA          |                                   | ラーのうちいずれかが発生した場合"1"になる                    |

| 選択機能                    | ●LSBファースト、MSBフ                    | · · · · · · · · · · · · · · · · · · ·     |

|                         | - ビットUから送信、受信:<br>- シリアルデータ論理切り   | するか、またはビット7から送信、受信するかを選択可                 |

|                         |                                   | 音ん<br>豆転する機能。スタートビット、ストップビットは反転しない。       |

|                         | ●TXD、RXD入出力極性切                    |                                           |

|                         | TXD端子出力とRXD端子                     | 一入力を反転する機能。入出力するデータのレベルがすべ                |

|                         | て反転する。                            |                                           |

|                         | ● CTS/RTS 分離機能(UAR                |                                           |

|                         | CTS0とRTS0を別の端子                    | -から人田刀する。                                 |

i = 0 ~ 5

注1. オーバランエラーが発生した場合、UiRBレジスタ受信データは不定になります。またSiRICレジスタのIRビッ トは変化しません。

表 22.10にUARTモード時の入出力端子の機能を示します。表 22.11にUARTモード時のP6\_4端子の 機能を示します。なお、UARTiの動作モード選択後、送信開始までは、TXDi端子は"H"を出力しま す(Nチャネルオープンドレイン出力選択時はハイインピーダンス状態)。

表 22.10 UARTモード時の入出力端子の機能

| 端子名   | 入出力 | 機能        | 選択方法                         |

|-------|-----|-----------|------------------------------|

| TXDi  | 出力  | シリアルデータ出力 | (受信だけを行うときは "H"を出力)          |

| RXDi  | 入力  | シリアルデータ入力 | 端子を共用するポートの方向ビットを"0"にする      |

|       | 入力  | 入力ポート     | 端子を共用するポートの方向ビットを"0"にする(送信だけ |

|       |     |           | を行うときは入力ポートとして使用可)           |

| CLKi  | 入出力 | 入出力ポート    | UiMR レジスタのCKDIR ビット=0        |

|       | 入力  | 送受信クロック入力 | UiMR レジスタのCKDIR ビット=1        |

|       |     |           | 端子を共用するポートの方向ビットを"0"にする      |

| CTSi/ | 入力  | CTS入力     | UiC0レジスタのCRDビット=0            |

| RTSi  |     |           | UiC0レジスタのCRSビット=0            |

|       |     |           | 端子を共用するポートの方向ビットを"0"にする      |

|       | 出力  | RTS出力     | UiC0レジスタのCRDビット=0            |

|       |     |           | UiC0 レジスタのCRS ビット=1          |

|       | 入出力 | 入出力ポート    | UiC0 レジスタの CRD ビット=1         |

i=0 **~** 5

表 22.11 UARTモード時のP6\_4端子の機能

|           | ビットの設定値   |     |           |        |           |  |

|-----------|-----------|-----|-----------|--------|-----------|--|

| 端子の機能     | U1C0 レジスタ |     | UCON レジスタ |        | PD6 レジスタ  |  |

|           | CRD       | CRS | RCSP      | CLKMD1 | PD6_4     |  |

| P6_4      | 1         | _   | 0         | 0      | 入力:0、出力:1 |  |

| CTS1      | 0         | 0   | 0         | 0      | 0         |  |

| RTS1      | 0         | 1   | 0         | 0      | _         |  |

| CTS0 (注1) | 0         | 0   | 1         | 0      | 0         |  |

<sup>-: &</sup>quot;0" または "1"

注1. この他にU0C0 レジスタの CRD ビットを "0" (CTSO/RTSO 許可)、U0C0 レジスタの CRS ビットを "1" (RTSO選択)にしてください。

表 22.12にUARTモード時の使用レジスタと設定値(注4)を示します。

## 表 22.12 UARTモード時の使用レジスタと設定値 (注4)

| レジスタ     | ビット             | 機能                                                                      |

|----------|-----------------|-------------------------------------------------------------------------|

| UCLKSEL0 | OCOSEL0         | UART0~UART2の分周前クロックを選択してください。                                           |

|          | OCOSEL1         | UART 3~UART 5の分周前クロックを選択してください。                                         |

| PCLKR    | PCLK1           | UiBRGのカウントソースを選択してください。                                                 |

| UiTB     | 0~8             | 送信データを設定してください(注1)                                                      |

| UiRB     | 0~8             | 受信データが読めます(注1、3)                                                        |

|          | 11              | 読んだ場合、その値は不定                                                            |

|          | OER、FER、PER、SUM | エラーフラグ                                                                  |

|          | 11              | 読んだ場合、その値は不定                                                            |

| UiBRG    | 0~7             | ビットレートを設定してください                                                         |

| UiMR     | SMD2~SMD0       | キャラクタ長が7ビットの場合、"100b"を設定してください。                                         |

|          |                 | キャラクタ長が8ビットの場合、"101b"を設定してください。                                         |

|          |                 | キャラクタ長が9ビットの場合、"110b"を設定してください。                                         |

|          | CKDIR           | 内部クロック、外部クロックを選択してください                                                  |

|          | STPS            | ストップビットを選択してください                                                        |

|          | PRY、PRYE        | パリティの有無、偶数奇数を選択してください                                                   |

|          | IOPOL           | TXD / RXD入出力極性を選択してください                                                 |

| UiC0     | CLK0、CLK1       | UiBRGのカウントソースを選択してください                                                  |

|          | CRS             | CTS または RTS 機能を使用する場合、どちらかを選択してください                                     |

|          | TXEPT           | 送信レジスタ空フラグ                                                              |

|          | CRD             | CTS / RTS機能の許可または禁止を選択してください                                            |

|          | NCH             | TXDi端子の出力形式を選択してください(注2)                                                |

|          | CKPOL           | "0" にしてください                                                             |

|          | UFORM           | キャラクタ長8ビット時、LSBファースト、MSBファーストを選択できます。<br>キャラクタ長7ビットまたは9ビット時は"0"にしてください。 |

| UiC1     | TE              | 送信を許可する場合、"1"にしてください                                                    |

|          | TI              | 送信バッファ空フラグ                                                              |

|          | RE              | 受信を許可するとき、"1"にしてください                                                    |

|          | RI              | 受信完了フラグ                                                                 |

|          | UjIRS           | UARTj送信割り込み要因を選択してください                                                  |

|          | UjRRM           | "0" にしてください                                                             |

|          | UiLCH           | データ論理反転を使用する場合、"1"にしてください                                               |

|          | UiERE           | "0" にしてください                                                             |

| UiSMR    | 0~7             | "0" にしてください                                                             |

| UiSMR2   | 0~7             | "0" にしてください                                                             |

| UiSMR3   | 0~7             | "0" にしてください                                                             |

| UiSMR4   | 0~7             | "O" にしてください                                                             |

| UCON     | U0IRS           | UARTO送信割り込み要因を選択してください                                                  |

|          | U1IRS           | UART1送信割り込み要因を選択してください                                                  |

|          | U0RRM           | "0"にしてください                                                              |

|          | U1RRM           | "0"にしてください                                                              |

|          | CLKMD0          | CLKMD1=0なので無効                                                           |

|          | CLKMD1          | "0"にしてください                                                              |

|          | RCSP            | UARTOのCTSO信号をP6_4端子から入力する場合、"1"にしてください                                  |

|          | 7               | "0"にしてください                                                              |

|          | 2015            | 0 10001200                                                              |

$i=0 \sim 5$   $j=2 \sim 5$

- 注1. 使用するビットは次のとおりです。キャラクタ長7ビット:ビット0~6、キャラクタ長8ビット:ビット0~7、キャ ラクタ長9ビット:ビット0~8

- 注2. TXD2端子はNチャネルオープンドレインです。U2C0レジスタのNCHビットは、何も配置されていませんので、書く 場合"0"を書いてください。

- 注3. キャラクタ長7ビットの場合、ビット7、8の内容は不定です。 キャラクタ長8ビットの場合、ビット8の内容は不定です。

- この表は手順を示すものではありません。 注4.

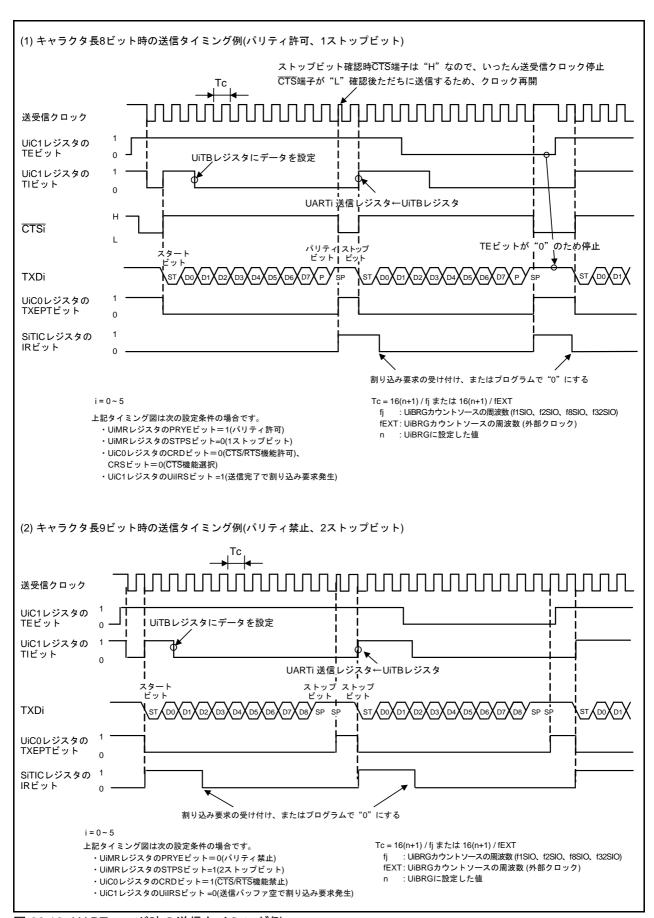

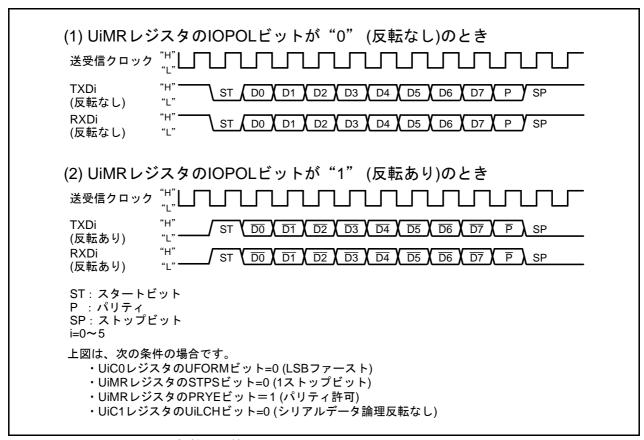

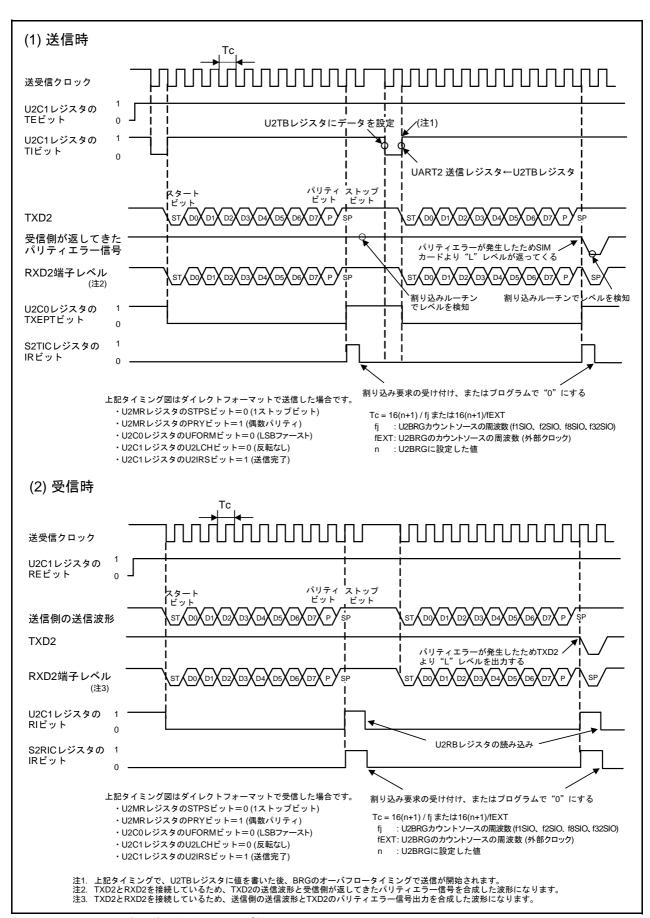

図 22.12 UARTモード時の送信タイミング例

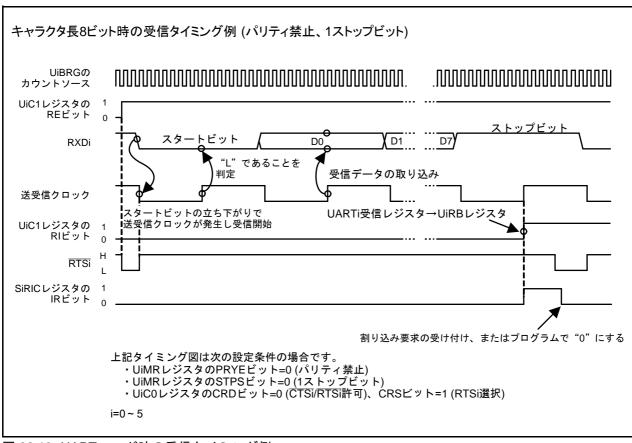

図 22.13 UARTモード時の受信タイミング例

# 22.3.2.1 ビットレート

UARTモードは、UiBRGレジスタ( $i=0\sim5$ )で分周した周波数の16分周がビットレートになります。 UiBRGレジスタの設定値(n)は次の式で求められます。

$$n = \frac{fj}{\text{"Yhv-h (bps) x 16}} - 1$$

fj = f1SIO, f2SIO, f8SIO, f32SIO

$n = 00h \sim FFh$

表 22.13 にビットレートの設定例を示します。

表 22.13 ビットレート

| ビットレート | UiBRGの  | 周辺機能クロッ           | クf1: 16 MHz     | 周辺機能クロッ           | クf1: 24 MHz     |

|--------|---------|-------------------|-----------------|-------------------|-----------------|

| (bps)  | カウントソース | UiBRG の<br>設定値: n | ビットレート<br>(bps) | UiBRG の<br>設定値: n | ビットレート<br>(bps) |

| 1200   | f8SIO   | 103 (67h)         | 1202            | 155 (9Bh)         | 1202            |

| 2400   | f8SIO   | 51 (33h)          | 2404            | 77 (4Dh)          | 2404            |

| 4800   | f8SIO   | 25 (19h)          | 4808            | 38 (26h)          | 4808            |

| 9600   | f1SIO   | 103 (67h)         | 9615            | 155 (9Bh)         | 9615            |

| 14400  | f1SIO   | 68 (44h)          | 14493           | 103 (67h)         | 14423           |

| 19200  | f1SIO   | 51 (33h)          | 19231           | 77 (4Dh)          | 19231           |

| 28800  | f1SIO   | 34 (22h)          | 28571           | 51 (33h)          | 28846           |

| 31250  | f1SIO   | 31 (1Fh)          | 31250           | 47 (2Fh)          | 31250           |

| 38400  | f1SIO   | 25 (19h)          | 38462           | 38 (26h)          | 38462           |

| 51200  | f1SIO   | 19 (13h)          | 50000           | 28 (1Ch)          | 51724           |

注1. UCLKSEL0 レジスタのOCOSEL0 ビットまたはOCOSEL1 ビットが "0" (f1) の場合です。

## 22.3.2.2 送受信レジスタの初期化

送受信中断などで、送受信レジスタを初期化する場合は、次のようにしてください。

- •UiRB レジスタ(i=0~5)の初期化手順

- (1)UiC1レジスタのREビットを "0" (受信禁止)にする。

- (2)UiC1レジスタのREビットを"1"(受信許可)にする。

- •UiTB レジスタの初期化手順

- (1) UiMR レジスタの SMD2~SMD0 ビットを "000b" (シリアルインタフェース無効)にする。

- (2) UiMR レジスタの SMD2~SMD0 ビットを再設定("001b"、"101b"、"110b")にする。

- (3)UiC1レジスタのTEビットの値にかかわらず"1"(送信許可)を書き込む。

# 22.3.2.3 LSBファースト、MSBファースト選択

図 22.14に示すように、UiCOレジスタのUFORMビットでビットオーダを選択できます。この機能は キャラクタ長8ビットのときに有効です。

図 22.14 ビットオーダ

## 22.3.2.4 シリアルデータ論理切り替え

UiTB レジスタに書いた値の論理を反転して送信します。UiRB レジスタを読むと、受信データの論理 を反転した値が読めます。図22.15にシリアルデータ論理を示します。

図 22.15 シリアルデータ論理

#### TXD、RXD入出力極性切り替え機能 22.3.2.5

TXDi端子出力とRXDi端子入力を反転する機能です。入出力するデータのレベルがすべて(スタート ビット、ストップビット、パリティビットを含む)反転します。図 22.16にTXD、RXD入出力極性切り 替えを示します。

図 22.16 TXD、RXD入出力極性切り替え

### 22.3.2.6 CTS/RTS機能

CTS 機能は、CTSi/RTSi(i = 0 ~ 5) 端子に "L" を入力すると、送信を開始させる機能です。 CTSi/RTSi 端子の入力レベルが "L" になると、送信を開始します。送信の最中に入力レベルを "H" にした場合、 次のデータから送信を停止します。

RTS機能は、受信準備が整ったとき、CTSi/RTSi 端子の出力レベルが "L" になります。スタートビッ トの検出で出力レベルが"H"になります。

端子の機能選択は「表 22.10 UARTモード時の入出力端子の機能」を参照してください。

## 22.3.2.7 CTS/RTS 分離機能 (UARTO)

CTS0/RTS0を分離し、RTS0をP6\_0端子から出力、CTS0をP6\_4端子から入力する機能です。この機能 を使用する場合は次のようにしてください。

- U0C0 レジスタのCRD ビット=0 (UART0のCTS/RTS許可)

- •U0C0レジスタのCRSビット=1(UART0のRTS出力)

- •U1C0レジスタのCRDビット=0(UART1の $\overline{\text{CTS}}/\overline{\text{RTS}}$ 許可)

- •U1C0レジスタのCRSビット=0(UART1の $\overline{\text{CTS}}$ 入力)

- •UCON レジスタの RCSP ビット=1(CTSOをP6 4端子から入力)

- •UCON レジスタのCLKMD1 ビット=0 (CLKS1を使用しない)

なお、CTS/RTS分離機能使用時、UART1のCTS/RTS機能は使用できません。

図 22.17 CTS/RTS 分離機能の使用例

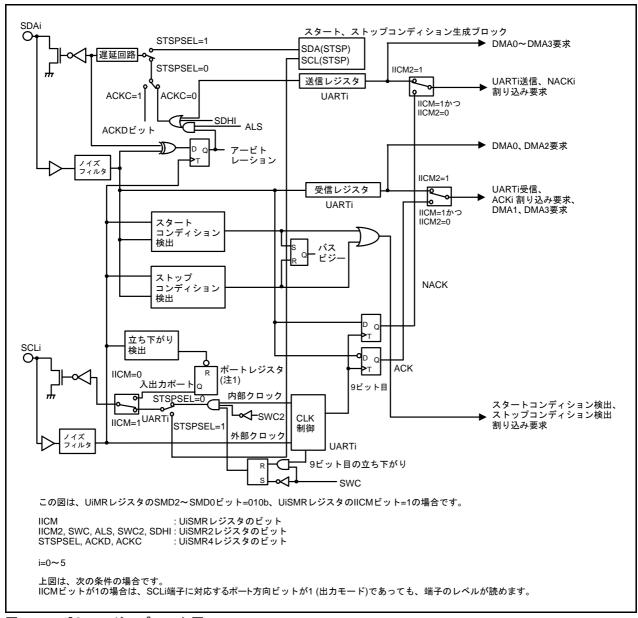

# 22.3.3 特殊モード1 (I<sup>2</sup>Cモード)

I<sup>2</sup>Cモードは、簡易形I<sup>2</sup>Cインタフェースに対応したモードです。表 22.14にI<sup>2</sup>Cモードの仕様を、表 22.16~表 22.17にI<sup>2</sup>Cモード時の使用レジスタと設定値を、表 22.18にI<sup>2</sup>Cモード時の各機能を、図 22.18 にI<sup>2</sup>Cモードのブロック図を、図 22.19にSCLiタイミングを示します。

表 22.18に示すように、SMD2~SMD0ビットを"010b"に、IICMビットを1にするとI<sup>2</sup>Cモードにな ります。SDAi送信出力には遅延回路が付加されますので、SCLiが"L"になり安定した後、SDAi出力 が変化します。

### 表 22.14 I<sup>2</sup>Cモードの仕様

| 項目                   | 仕様                                                          |

|----------------------|-------------------------------------------------------------|

| データフォーマット            | キャラクタ長 8ビット                                                 |

| 送受信クロック              | ●マスタ時<br>UiMR レジスタのCKDIR ビットが 0 (内部クロック):                   |

|                      | fi fi                                                       |

|                      | $\frac{1}{2(n+1)}$                                          |

|                      | fj=f1SIO、f2SIO、f8SIO、f32SIO n=UiBRG レジスタの設定値 00h~FFh        |

|                      | •スレーブ時                                                      |

|                      | CKDIR ビットが1 (外部クロック):SCLi端子からの入力                            |

| 送信開始条件               | 送信開始には、次の条件が必要(注1)                                          |

|                      | ●UiC1 レジスタのTE ビットが"1" (送信許可)                                |

|                      | ●UiC1レジスタのTIビットが"0"(UiTBレジスタにデータあり)                         |

| 受信開始条件               | 受信開始には、次の条件が必要(注1)                                          |

|                      | ●UiC1 レジスタのRE ビットが "1" (受信許可)                               |

|                      | ●UiC1 レジスタのTE ビットが"1" (送信許可)                                |

|                      | ●UiC1レジスタのTIビットが"O"(UiTBレジスタにデータあり)                         |

| 割り込み要求発生タイミング        | 送信割り込み                                                      |

|                      | <ul><li>●アクノリッジ未検出、または送信</li></ul>                          |

|                      | 受信割り込み                                                      |

|                      | ●アクノリッジ未検出、または受信                                            |

|                      | スタートコンディション検出、ストップコンディション検出割り込み                             |

| т = <del>1</del> 6-ш | ●スタートコンディション、ストップコンディション検出                                  |

| エラー検出                | オーバランエラー (注2)<br>  UiRB レジスタを読む前に次のデータ受信を開始し、次のデータの8ビット目を受信 |

|                      | すると発生                                                       |

| 選択機能                 | • アービトレーションロスト                                              |

|                      | UiRB レジスタの ABT ビットの更新タイミングを選択可                              |

|                      | • SDAi デジタル遅延                                               |

|                      | デジタル遅延なし、またはUiBRGカウントソースの2~8サイクルの遅延を選択                      |

|                      | 可                                                           |

|                      | • クロック位相設定                                                  |

|                      | クロック遅れあり、なしを選択可                                             |

i=0 **~** 5

- 注1. 外部クロックを選択している場合、外部クロックが"H"の状態で条件を満たしてください。

- 注2. オーバランエラーが発生した場合、UiRBレジスタ受信データは不定になります。

図 22.18 I<sup>2</sup>Cモードのブロック図

表 22.15 I<sup>2</sup>Cモード時の入出力端子

| 端子        | 入出力 | 機能      |

|-----------|-----|---------|

| SCLi (注1) | 入出力 | クロック入出力 |

| SDAi (注1) | 入出力 | データ入出力  |

$i = 0 \sim 5$

注1. CLKi、CTSi/RTSi 端子は使用しません (入出カポートに使用できます)。

表 22.16 12Cモード時の使用レジスタと設定値(1/2)(注3)

|             | . * .        | 機                                    |                                            |

|-------------|--------------|--------------------------------------|--------------------------------------------|

| レジスタ        | ビット          | マスタ時                                 | スレーブ時                                      |

| UCLKSEL0    | OCOSEL0      | UART0~UART2の分周前クロックを選択して             | UART0~UART2の分周前クロックを選択して                   |

|             |              | ください                                 | ください                                       |

|             | OCOSEL1      | UART3~UART5の分周前クロックを選択して             | UART3~UART5の分周前クロックを選択して                   |

| 501165      | D01144       | ください                                 | ください                                       |

| PCLKR       | PCLK1        | UiBRGのカウントソースを選択してください               | UiBRGのカウントソースを選択してください                     |

| UiTB        | 0~7          | 送信データを設定してください                       | 送信データを設定してください                             |

|             | 8            | - (設定しないでよい)                         | - (設定しないでよい)                               |

| UiRB        | 0~7          | 受信データが読めます                           | 受信データが読めます                                 |

|             | 8            | ACK、NACKが入ります                        | ACK、NACKが入ります                              |

|             | ABT          | アービトレーションロスト検出フラグ                    | 無効                                         |

|             | OER          | オーバランエラーフラグ                          | オーバランエラーフラグ                                |

| LUBBO       | 13~15        | 読んだ場合、その値は不定                         | 読んだ場合、その値は不定                               |

| UiBRG       | 0~7          | ビットレートを設定してください                      | 無効                                         |

| UiMR        | SMD2~SMD0    | "010b" にしてください                       | "010b" にしてください                             |

|             | CKDIR        | "0" にしてください                          | "1"にしてください                                 |

|             | 4~6          | "0" にしてください                          | "0" にしてください                                |

|             | IOPOL        | "0" にしてください                          | "0" にしてください                                |

| UiC0        | CLK1 ~ CLK0  | UiBRGのカウントソースを選択してください               | 無効                                         |

|             | CRS          | CRD=1 なので無効                          | CRD=1 なので無効                                |

|             | TXEPT        | 送信レジスタ空フラグ                           | 送信レジスタ空フラグ                                 |

|             | CRD(注2)      | "1"にしてください                           | "1" にしてください                                |

|             | NCH          | "1"にしてください(注1)                       | "1"にしてください(注1)                             |

|             | CKPOL        | "0" にしてください                          | "0" にしてください                                |

|             | UFORM        | "1" にしてください                          | "1" にしてください                                |

| UiC1        | TE           | 送信を許可する場合、"1"にしてください                 | 送信を許可する場合、"1"にしてください                       |

|             | TI           | 送信バッファ空フラグ                           | 送信バッファ空フラグ                                 |

|             | RE           | 受信を許可する場合、"1"にしてください                 | 受信を許可する場合、"1"にしてください                       |

|             | RI           | 受信完了フラグ                              | 受信完了フラグ                                    |

|             | UjIRS        | "1"にしてください                           | "1"にしてください                                 |

|             | UjRRM.       | "0" にしてください                          | "0" にしてください                                |

|             | UiLCH, UiERE |                                      |                                            |

| UiSMR       | IICM         | "1"にしてください                           | "1"にしてください                                 |

|             | ABC          | アービトレーションロスト検出タイミングを選                | 無効                                         |

|             |              | 択してください                              |                                            |

|             | BBS          | バスビジーフラグ                             | バスビジーフラグ                                   |

|             | 3~7          | "0" にしてください                          | "0" にしてください                                |

| UiSMR2      | IICM2        | 「表 22.18 I <sup>2</sup> Cモード時の各機能」参照 | 「表 22.18 I <sup>2</sup> Cモード時の各機能」参照       |

|             | CSC          | クロック同期化を許可する場合、"1"にしてく               | "0" にしてください                                |

|             | 014/0        | ださい                                  |                                            |

|             | SWC          | クロックの9ビット目の立ち下がりでSCLi出力              | クロックの9ビット目の立ち下がりでSCLi出力                    |

|             |              | を "L" 出力固定にする場合、"1" にしてくだ            | を "L" 出力固定にする場合、"1" にしてくだ                  |

|             | ALS          | さい                                   | さい<br>"o" にしてください                          |

| 1           | ALS          | アービトレーションロスト検出時にSDAiの出               | "0" にしてください                                |

|             | STAC         | 力を停止する場合 "1" にしてください                 | 7 h     -   -   -   -   -   -   -   -   -  |

|             | SIAC         | "0" にしてください                          | スタートコンディション検出でUARTiを初期化<br>する場合、"1"にしてください |

|             | SWC2         | <br>  SCLiの出力を強制的に "L" にする場合、"1"     | SCLiの出力を強制的に "L" にする場合、"1"                 |

|             |              | にしてください                              | にしてください                                    |

|             | SDHI         | SDAi 出力を禁止をする場合、"1"にしてくだ             | SDAi出力を禁止をする場合、"1"にしてくだ                    |

|             |              | さい                                   | さい                                         |

|             | 7            | "0"にしてください                           | "0"にしてください                                 |

| i=0 ~ 5 i=2 | 2~5          |                                      | <u> </u>                                   |

i=0 ~ 5 j=2 ~ 5

- 注1. TXD2 端子は N チャネルオープンドレインです。U2C0 レジスタの NCH ビットは、何も配置されていませんので、書く場合 "0"を書いてください。

- 注2. UART1 を I<sup>2</sup>C モードで使用しているときに、UART0 の CTS/RTS 分離機能を許可する場合、U1C0 レジスタの CRD ビットを "0" (CTS/RTS許可)、CRSビットを"0" (CTS入力)にしてください。

- 注3. この表は手順を示すものではありません。

表 22.17 12Cモード時の使用レジスタと設定値(2/2)(注1)

| レジスタ   | ビット           | 機能                                      |                                                            |  |  |

|--------|---------------|-----------------------------------------|------------------------------------------------------------|--|--|

|        |               | マスタ時                                    | スレーブ時                                                      |  |  |

| UiSMR3 | 0、2、4<br>NODC | "0" にしてください                             | "0" にしてください                                                |  |  |

|        | СКРН          | 「表 22.18 I <sup>2</sup> Cモード時の各機能」参照    | 「表 22.18 I <sup>2</sup> Cモード時の各機能」参照                       |  |  |

|        | DL2~DL0       | SDAiのデジタル遅延値を設定してください                   | SDAiのデジタル遅延値を設定してください                                      |  |  |

| UiSMR4 | STAREQ        | スタートコンディションを生成する場合、"1"<br>にしてください       | "0" にしてください。                                               |  |  |

|        | RSTAREQ       | リスタートコンディションを生成する場合、"1"<br>にしてください      | "0" にしてください。                                               |  |  |

|        | STPREQ        | ストップコンディションを生成する場合、"1"<br>にしてください       | "0" にしてください。                                               |  |  |

|        | STSPSEL       | 各コンディション出力時に"1"にしてください                  | "0" にしてください。                                               |  |  |

|        | ACKD          | ACK、NACKを選択してください                       | ACK、NACKを選択してください                                          |  |  |

|        | ACKC          | ACKデータを出力する場合、"1" にしてください               | ACKデータを出力する場合、"1"にしてください                                   |  |  |

|        | SCLHI         | ストップコンディション検出時にSCLi出力を停止する場合、"1"にしてください | "0" にしてください。                                               |  |  |

|        | SWC9          | "0" にしてください                             | クロックの9ビット目の次の立ち下がりでSCLi<br>を "L" ホールドにする場合、"1" にしてくださ<br>い |  |  |

| UCON   | U0IRS         | "1" にしてください                             | "1" にしてください                                                |  |  |

|        | U1IRS         | "1" にしてください                             | "1" にしてください                                                |  |  |

|        | U0RRM         | "0" にしてください                             | "0" にしてください                                                |  |  |

|        | U1RRM         | "0" にしてください                             | "0" にしてください                                                |  |  |

|        | CLKMD0        | "0" にしてください                             | "0" にしてください                                                |  |  |

|        | CLKMD1        | "0" にしてください                             | "0" にしてください                                                |  |  |

|        | RCSP          | "0" にしてください                             | "0" にしてください                                                |  |  |

|        | 7             | "0" にしてください                             | "0" にしてください                                                |  |  |

i=0 **~** 5

注1. この表は手順を示すものではありません。

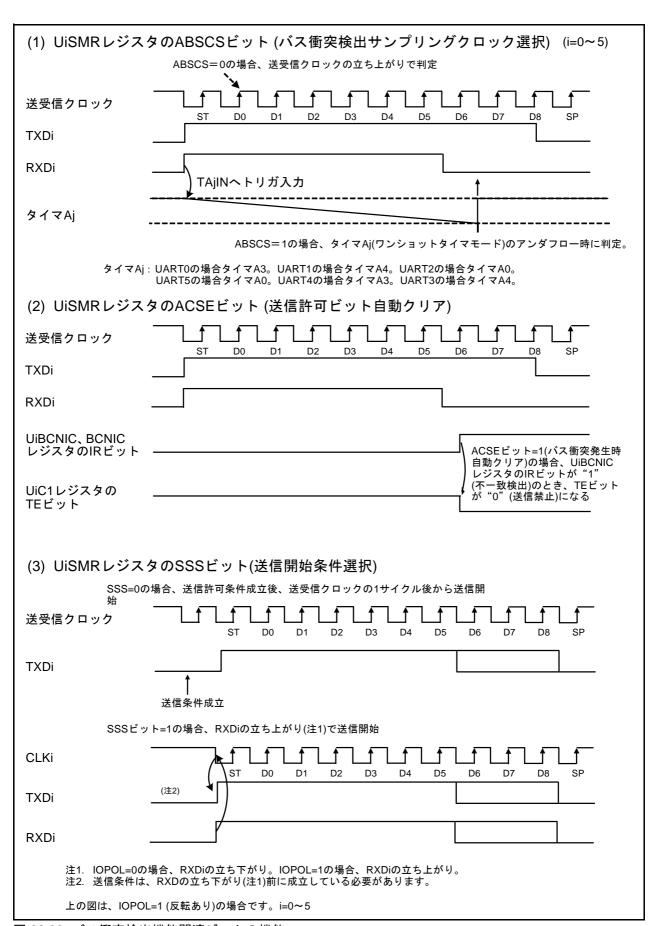

I<sup>2</sup>C モードでは、UiSMR2 レジスタの IICM2 ビットと UiSMR3 レジスタの CKPH ビットの組み合わせ で、機能やタイミングが変わります。図 22.19 に UiRB レジスタへの転送、割り込みのタイミングを示 します。UiRB レジスタへの転送タイミング、UiRB レジスタに格納されるデータのビット位置、割り 込みの種類、割り込み要求とDMA要求の発生タイミングは、この図を参照してください。

その他の機能のクロック同期シリアルI/Oモードとの比較を、表 22.18にI2Cモード時の各機能示しま す。

### 表 22.18 I<sup>2</sup>Cモード時の各機能

|                                                 | クロック同期シリアル                                               |                                         | I <sup>2</sup> Cモード(SMD2~    | SMD0=010b,IICM=1)                                                   |                                                                                                                                                     |