## How to Meet 112G PAM-4 SerDes Jitter Requirements with FemtoClock™ 3 and FemtoClock 3 Wireless Devices

### Introduction

The FemtoClock 3 (FC3) and FemtoClock 3 Wireless (FC3W) families of devices are ultra-high performance clock generators, jitter cleaners, and clock synchronizers that can generate outputs with < 60fs of RMS jitter to be used as reference clocks for 112G PAM-4 SerDes. FC3 and FC3W generated outputs have low phase noise capable of meeting the 112G PAM-4 SerDes phase noise requirements at 10kHz, 100kHz, 1MHz, and > 10MHz with several dBc/Hz of margin.

### Contents

|                                                                                                |    |

|------------------------------------------------------------------------------------------------|----|

| 1. Overview .....                                                                              | 2  |

| 2. 112G Reference Clock Requirements .....                                                     | 2  |

| 3. Meeting 112G Reference Clock Requirements with FC3.....                                     | 4  |

| 3.1    FC3 With a 4MHz High Pass Filter Using the Rohde & Schwarz FSWP .....                   | 5  |

| 3.2    FC3 With a 4MHz High Pass Filter Using the Keysight E5052B .....                        | 6  |

| 4. Meeting 112G Reference Clock Requirements with FC3W .....                                   | 11 |

| 4.1    FC3W With a 4MHz High Pass Filter Using the Rohde & Schwarz FSWP.....                   | 12 |

| 4.2    FC3W With a 4MHz High Pass Filter Using the Keysight E5052B.....                        | 13 |

| 5. Crystal Recommendations for FC3 to Meet 112G PAM-4 SerDes Reference Clock Requirements..... | 18 |

| 6. Revision History .....                                                                      | 19 |

### Tables

|                                                                                                                           |    |

|---------------------------------------------------------------------------------------------------------------------------|----|

| Table 1. Maximum Allowable Transmitter Output Jitter for Various Serial Link Interfaces.....                              | 3  |

| Table 2. 112G Reference Clock Requirements .....                                                                          | 3  |

| Table 3. RMS Multipliers for Bit Error Rates of $10^{-3}$ to $10^{-15}$ .....                                             | 4  |

| Table 4. FC3 and FC3W Crystal Recommendations to Meet Requirements for a 312.5MHz 112G PAM-4 SerDes Reference Clock ..... | 18 |

| Table 5. FC3 and FC3W XO Recommendations to Meet Requirements for a 312.5MHz 112G PAM-4 SerDes Reference Clock .....      | 18 |

## 1. Overview

The FC3 and FC3W families of devices are ultra-high performance clock generators, jitter cleaners, and clock synchronizers. The RC32xxx and RC38xxx series have advanced reference clock selection and hitless switching features to meet the stringent ITU-T requirements of communications infrastructure applications. The ultra-low jitter performance of these devices minimizes bit error rates (BER) in applications involving high-speed serial links, such as 112G PAM-4 SerDes.

The FC3 family of devices feature a single-channel synchronizer that can synchronize to one of four differential or single-ended reference clock inputs. Similarly, the FC3W family of devices feature up to three single-channel synchronizers that can synchronize to one of four differential clock inputs. The synchronizer is accompanied by an Analog Phase Locked-Loop (APLL) domain that features Renesas' new generation, ultra-low phase noise VCO, and generates  $< 60\text{fs rms}$  typical jitter in the frequency band of 12kHz to 20MHz for a 312.5MHz output; both of which exceed the 112G PAM-4 reference clock needs as specified in the standards and for the switch ASICs.

There are additional FOD domains that can be used to generate unrelated frequencies either locked to the reference clock input or the free-run XO input and generates  $< 120\text{fs rms}$  typical jitter. FC3 and FC3W can generate up to 12 high-performance output clocks with up to four different frequencies.

## 2. 112G Reference Clock Requirements

The overall allowable jitter in a serial link is dictated by the applicable standard, such as IEEE or OIF. [Table 1](#) displays the maximum allowable transmitter output jitter for various serial link interfaces. The maximum allowable values are obtained from the applicable standards in terms of UI, where 1 UI is equal to the period of the baud rate. The equivalent time domain jitter has been calculated for each interface in [Table 1](#). For example, IEEE 802.3df (800GAUI-8) has a maximum allowable transmitter output jitter of  $0.023 \times \text{UI}$  and uses a baud rate of 53.125Gbd. One period of the baud rate is therefore equal to  $1/(53.125 \times 10^9) = 18.8235\text{ps}$ . Therefore, the maximum allowable jitter is  $0.023 \times 18.8235\text{ps} = 433\text{fs}$  (rounded to nearest fs). Only a portion of the overall allowable jitter is allocated to the reference clock. Many SerDes ASIC vendors with 112G PAM4 SerDes require a maximum reference clock jitter of 100fs RMS.

[Table 2](#) displays the phase noise requirements for a 112G receiver.

[Table 2](#) also contains the 112G PAM-4 reference clock Gaussian jitter requirement. The Gaussian jitter, also known as random jitter requirement for a 112G PAM-4 reference clock, is defined as  $0.009 \times \text{UI}$  (RMS), where 1 UI is equal to the period of the reference clock. For a 312.5MHz reference clock,  $1 \text{ UI} = 1/(312.5 \times 10^6) = 3.2\text{ns}$ . The random jitter requirement is therefore  $0.009 \times 3.2\text{ns} = 28.8\text{ps}$ .

For a gaussian distribution, it is possible to predict the peak-to-peak random jitter ( $\text{RJ}_{\text{PP}}$ ) using the measured random RMS jitter ( $\text{RJ}_{\text{rms}}$ ) and an RMS multiplier (N), where  $\text{RJ}_{\text{PP}} = N \times \text{RJ}_{\text{rms}}$ . The RMS multiplier is determined using the required bit error rate (BER) and data transition density (DTD). [Table 3](#) shows the RMS multiplier for bit error rates of  $10^{-3}$  to  $10^{-15}$  for DTD = 0.5 and DTD = 1.

## How to Meet 112G PAM-4 SerDes Jitter Requirements with FemtoClock 3 and FemtoClock 3 Wireless Devices

**Table 1. Maximum Allowable Transmitter Output Jitter for Various Serial Link Interfaces**

| Interface                | Baud Rate                     | Maximum Allowable Transmitter Output Jitter                                                       | Description                                                                                                                          |

|--------------------------|-------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| CEI-112G-XSR-PAM4        | Between 36Gsym/s and 58Gsym/s | 0.0224*UI <sup>[1]</sup> (RMS)<br>= 622fs for 36Gsym/s<br>= 386fs for 58Gsym/s                    | From OIF-CEI-05.1, section 24<br>“CEI-112G-XSR-PAM4 Extra Short Reach Interface”                                                     |

| CEI-112G-MR-PAM4         |                               | 0.023 × 5 UI (RMS)<br>= 638fs for 36Gsym/s<br>= 396fs for 58Gsym/s                                | From OIF-CEI-05.1, section 26<br>“CEI-112G-MR-PAM4 Medium Reach Interface” and section 27<br>“CEI-112G-LR-PAM4 Long Reach Interface” |

| CEI-112G-LR-PAM4         |                               | 0.023*UI (RMS)<br>= 892fs for 25.78125 GBd,<br>= 866fs for 26.5625 GBd,<br>= 433fs for 53.125 GBd | From IEEE Std 802.3ck™-2022,<br>IEEE Std 802.3cu™-2021, IEEE<br>P802.3df™/D2.0                                                       |

| IEEE 802.3ck             | 25.78125 or 26.5625 GBd       |                                                                                                   |                                                                                                                                      |

| IEEE 802.3cu             | 26.5625 or 53.125 GBd         |                                                                                                   |                                                                                                                                      |

| IEEE 802.3df (800GAUI-8) | 53.125 GBd                    |                                                                                                   |                                                                                                                                      |

**Table 2. 112G Reference Clock Requirements**

| Interface                                             | Reference Clock                         | Description                                                                                                                                        |

|-------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| High Frequency Uncorrelated Unbounded Gaussian Jitter | 0.009*UI (RMS)<br>= 28.8ps for 312.5MHz | The reference clock is typically set to be 1/64th of the baud rate. However, most 112G SerDes or Switch ASICs use 312.5 MHz for a reference clock. |

| Single Side Band (SSB) Phase Noise                    | -131 dBc/Hz                             | At 10kHz offset                                                                                                                                    |

|                                                       | -137 dBc/Hz                             | At 100kHz offset                                                                                                                                   |

|                                                       | -143 dBc/Hz                             | At 1MHz offset                                                                                                                                     |

|                                                       | -158 dBc/Hz                             | At >10MHz offset                                                                                                                                   |

1. 1 Ui is equal to the period of the baud rate.

Table 3. RMS Multipliers for Bit Error Rates of  $10^{-3}$  to  $10^{-15}$

| BER        | RMS Multiplier (N), DTD = 0.5 | RMS Multiplier (N), DTD = 1 |

|------------|-------------------------------|-----------------------------|

| $10^{-3}$  | 6.180                         | 6.582                       |

| $10^{-4}$  | 7.438                         | 7.782                       |

| $10^{-5}$  | 8.530                         | 8.834                       |

| $10^{-6}$  | 9.507                         | 9.784                       |

| $10^{-7}$  | 10.399                        | 10.654                      |

| $10^{-8}$  | 11.224                        | 11.462                      |

| $10^{-9}$  | 11.996                        | 12.218                      |

| $10^{-10}$ | 12.723                        | 1.934                       |

| $10^{-11}$ | 13.412                        | 13.614                      |

| $10^{-12}$ | 14.069                        | 14.260                      |

| $10^{-13}$ | 14.698                        | 14.882                      |

| $10^{-14}$ | 15.301                        | 15.478                      |

| $10^{-15}$ | 15.883                        | 16.028                      |

### 3. Meeting 112G Reference Clock Requirements with FC3

For a 312.5MHz SerDes reference clock, Renesas recommends using of a 62.5MHz crystal along with an APLL VCO frequency of 10GHz to attain the best jitter and phase noise when using FC3 in synthesizer mode. When using FC3 in jitter attenuator mode to generate a 312.5MHz SerDes reference clock, Renesas recommends the use of a 49.152MHz crystal along with an APLL VCO frequency of 10GHz.

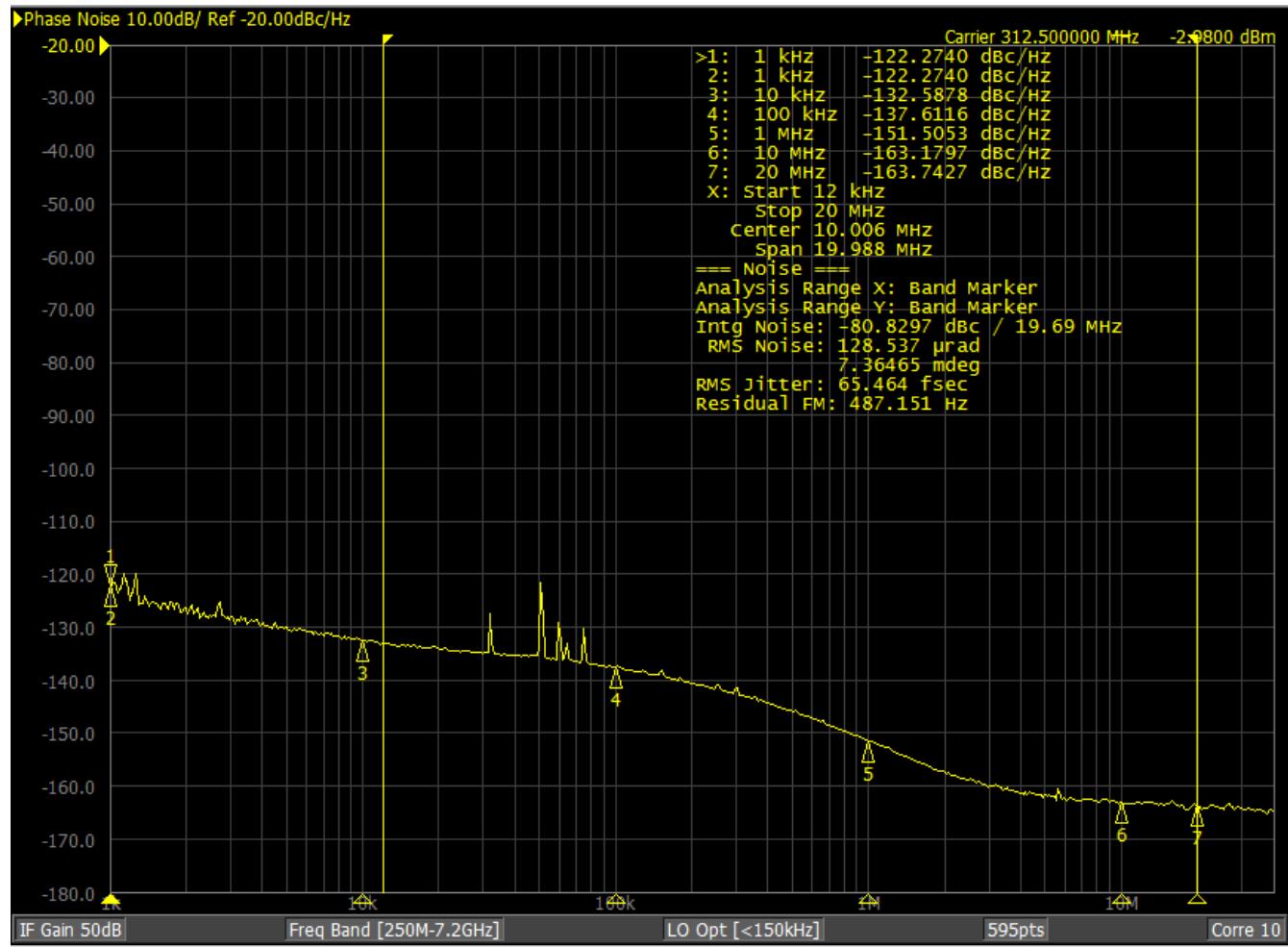

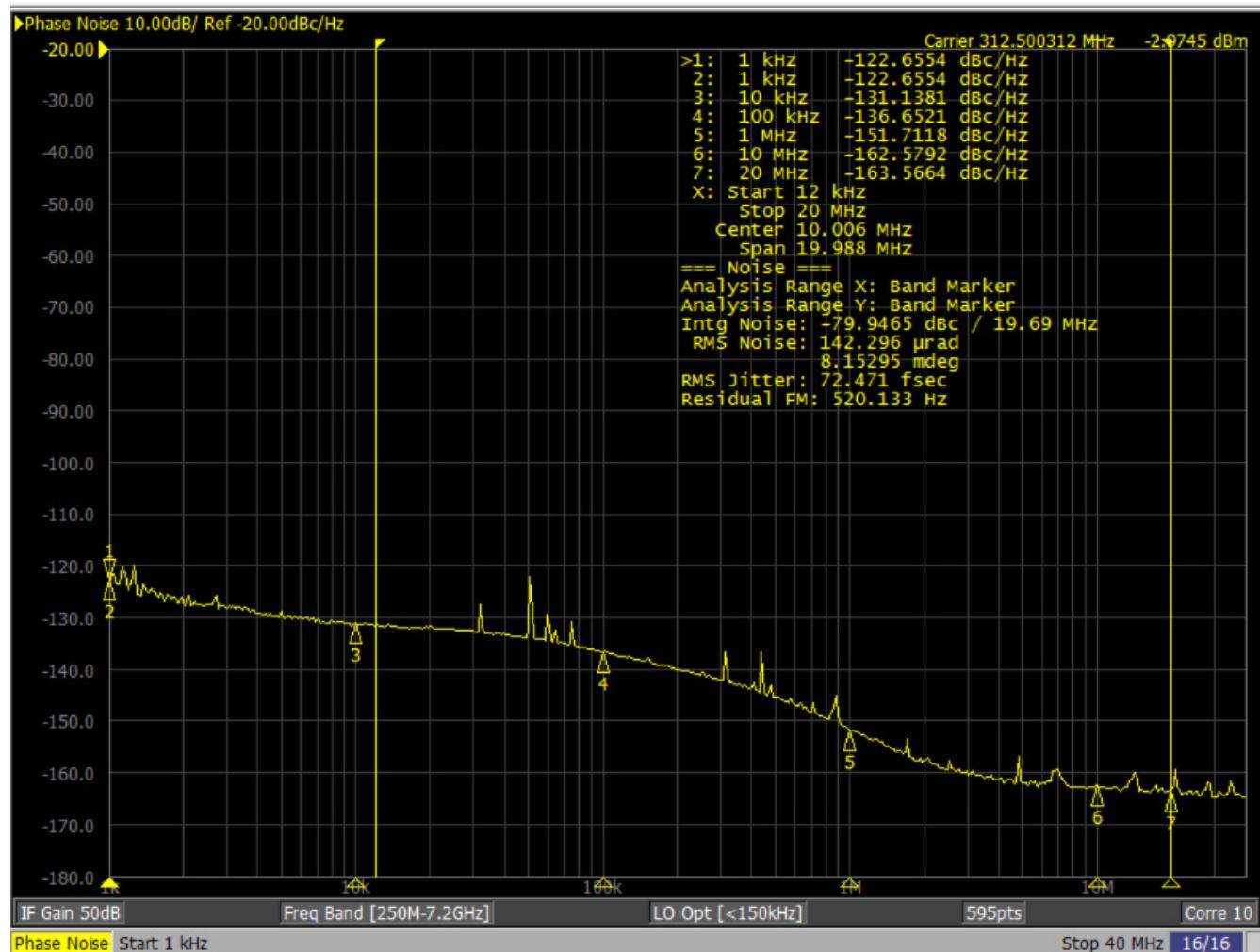

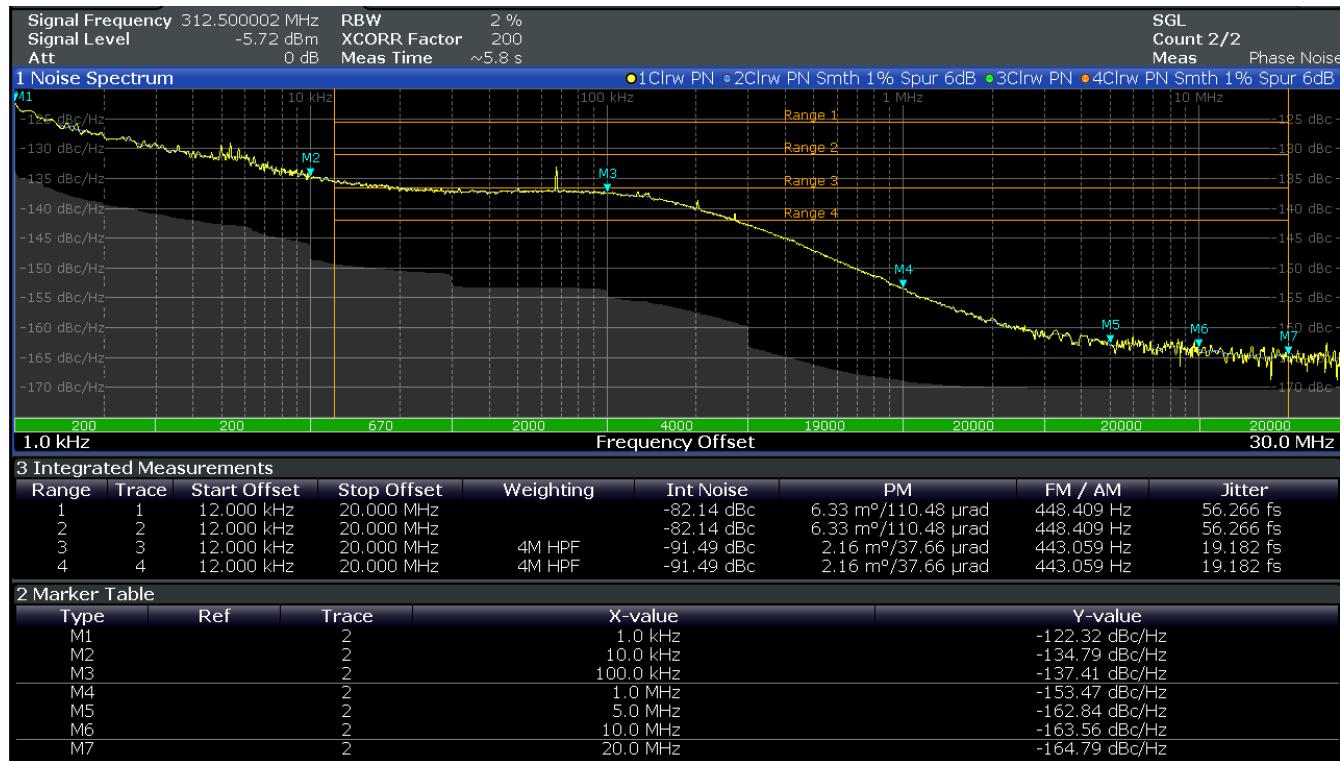

Figure 1 shows the phase noise plot for a 312.5MHz FC3 output with a crystal input frequency of 62.5MHz (synthesizer mode) measured using a Rohde & Schwarz FSWP. Figure 2 shows the phase noise plot for a 312.5MHz FC3 output with a crystal input frequency of 49.152MHz (jitter attenuator mode) and a reference input clock frequency of 25MHz. The RMS jitter value of a 312.5MHz output is approximately 56fs when using synthesizer mode with a 62.5MHz crystal, and approximately 66fs when using jitter attenuator mode with a 49.152MHz crystal. Therefore, the RMS jitter of FC3 is far below the typical maximum of 100fs used for many SerDes ASICs. Comparing Figure 1, Figure 2, Figure 3, and Figure 5 to Table 2, which displays the phase noise requirements for a 112G receiver, FC3 meets the requirements at 10kHz, 100kHz, 1MHz, and > 10MHz with several dBc/Hz of margin.

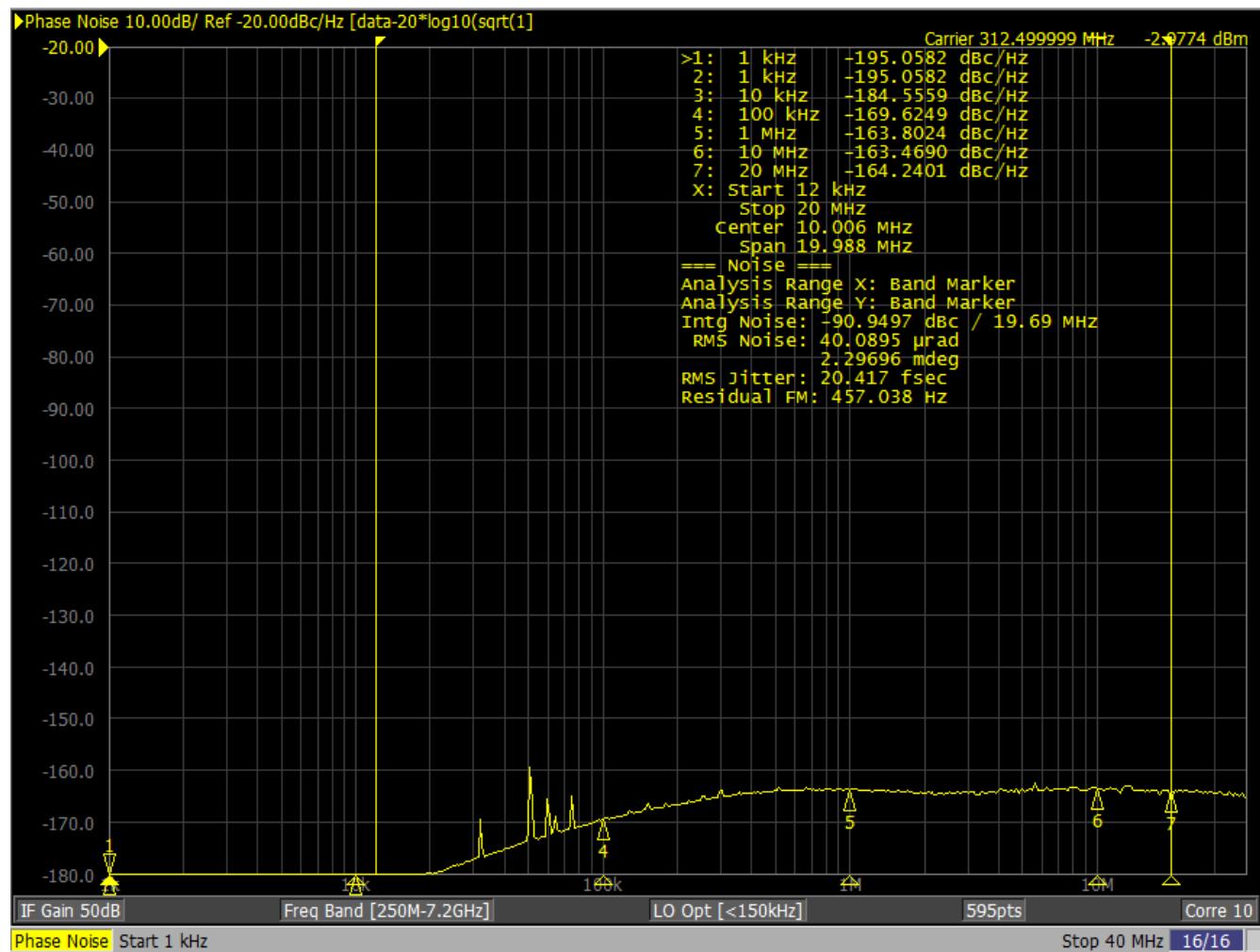

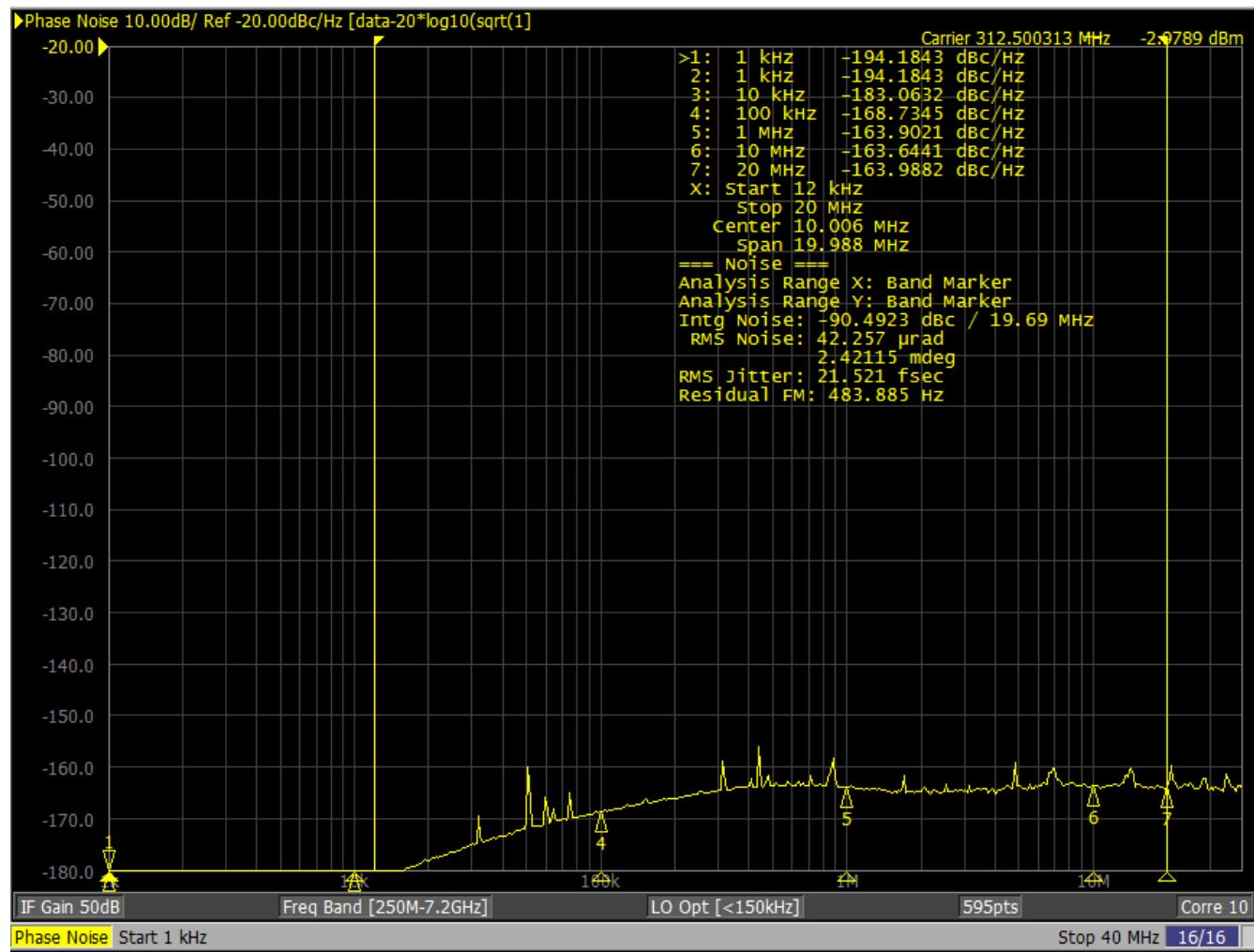

112G PAM-4 SerDes uses a CDR bandwidth of 4MHz, which acts as a high-pass filter on the reference clock. Depending on the method used to simulate this 4MHz high-pass filter, a 312.5MHz FC3 output clock will have RMS jitter of ~18fs to 21.5fs.

Using Table 3, for the case where  $BER = 10^{-15}$  and  $DTD = 1$ , which will yield the highest RMS multiplier of  $N = 16.028$ , and using  $RJ_{rms} = 65.464\text{fs}$  as shown in Figure 3,  $RJ_{PP} = 16.028 \times 65.464\text{fs} = 1.049\text{ps}$  for synthesizer mode with a 62.5MHz crystal and a 312.5MHz output. For jitter attenuator mode with a 49.152MHz crystal, a 312.5MHz output has  $RJ_{rms} = 72.471\text{fs}$ , as shown in Figure 5. Thus,  $RJ_{PP} = 16.028 \times 72.471\text{fs} = 1.161\text{ps}$  and the random jitter produced by a FC3W output is far below the recommended maximum of 28.8ps for a 312.5MHz SerDes reference clock.

## How to Meet 112G PAM-4 SerDes Jitter Requirements with FemtoClock 3 and FemtoClock 3 Wireless Devices

Renesas primarily uses two phase noise measurement instruments, the Keysight E5052B and the Rohde & Schwarz FSWP. Each instrument simulates filters differently. The Keysight E5052B can simulate a 4MHz high pass filter by using its equation editor feature to apply a high-pass filter equation to the data trace. The Rohde & Schwarz can simulate a 4MHz high pass filter by using its weighting filter feature. For more details on how to set up these features, see the [Applying Filters to Phase Noise Measurements with Keysight E5052 and Rohde & Schwarz FSWP](#) application note.

### 3.1 FC3 With a 4MHz High Pass Filter Using the Rohde & Schwarz FSWP

Simulating a 4MHz high pass filter using the Rohde & Schwarz FSWP involves applying a weighting filter to integrated measurement. The weighting filter feature only has an effect on the integrated measurement results and has no effect in the noise diagram or other numerical results.

Figure 1. Phase Noise Plot for a 312.5MHz Output from an RC32312 FC3 Device Operating in Synthesizer Mode, using a 62.5MHz Crystal along with an APLL VCO Frequency of 10GHz, measured using a Rohde & Schwarz FSWP; RMS Jitter also displayed

## How to Meet 112G PAM-4 SerDes Jitter Requirements with FemtoClock 3 and FemtoClock 3 Wireless Devices

**Figure 2. Phase Noise Plot for a 312.5MHz Output from an RC32312 FC3 Device Operating in Jitter Attenuator Mode, using a 49.152MHz Crystal along with an APLL VCO Frequency of 10GHz, and a 25MHz + 1ppm Reference Input, measured using a Rohde & Schwarz FSWP; RMS Jitter also displayed**

### 3.2 FC3 With a 4MHz High Pass Filter Using the Keysight E5052B

Simulating a 4MHz high pass filter using the Keysight E5052B involves applying a mathematical function to the measured data for an integration range of 12kHz to 20MHz. The mathematical function to apply to the data is as follows:

$$F(x) = \text{data} - 20 \log_{10} \sqrt{1 + \frac{F_c^2}{x^2}}$$

**Equation 1. Function Used to Approximate a 4MHz High-Pass Filter For FC3**

Where  $F_c$  is the corner frequency in Hz, which is equal to 4000000 in this case, and  $x$  is the offset frequency in Hz. **Figure 4** shows the phase noise after applying [Equation 1](#) to the data shown in [Figure 3](#). Similarly, **Figure 6** shows the phase noise after applying [Equation 1](#) to the data shown in [Figure 5](#). Using this method, the approximate RMS jitter on the receiver after the 4MHz high-pass filter will be ~20.4fs when using synthesizer mode with a 62.5MHz crystal, and ~21.5fs when using jitter attenuator mode with a 49.152MHz crystal.

## How to Meet 112G PAM-4 SerDes Jitter Requirements with FemtoClock 3 and FemtoClock 3 Wireless Devices

Figure 3. Phase Noise Plot for a 312.5MHz Output from an RC32312 FC3 Device Operating in Synthesizer Mode, using a 62.5MHz Crystal along with an APLL VCO Frequency of 10GHz; RMS Jitter also displayed

## How to Meet 112G PAM-4 SerDes Jitter Requirements with FemtoClock 3 and FemtoClock 3 Wireless Devices

Figure 4. Phase Noise Plot with a 4MHz High-Pass Filter applied on a 312.5MHz Output from an RC32312 FC3 Device Operating in Synthesizer Mode using a 62.5MHz Crystal along with an APLL VCO Frequency of 10GHz; RMS Jitter also displayed

## How to Meet 112G PAM-4 SerDes Jitter Requirements with FemtoClock 3 and FemtoClock 3 Wireless Devices

Figure 5. Phase Noise Plot for a 312.5MHz Output from an RC32312 FC3 Device Operating in Jitter Attenuator Mode, using a 49.152MHz Crystal along with an APLL VCO Frequency of 10GHz, and a 25MHz + 1ppm Reference Clock Input; RMS Jitter also displayed

## How to Meet 112G PAM-4 SerDes Jitter Requirements with FemtoClock 3 and FemtoClock 3 Wireless Devices

Figure 6. Phase Noise Plot with a 4MHz High Pass Filter applied on a 312.5MHz Output from an RC32312 FC3 Device Operating in Jitter Attenuator Mode using a 49.152MHz Crystal and a 25MHz Reference Clock Input; RMS Jitter also displayed

## 4. Meeting 112G Reference Clock Requirements with FC3W

For a 312.5MHz SerDes reference clock, Renesas recommends using of a 62.5MHz crystal along with an APLL VCO frequency of 9.375GHz to attain the best jitter and phase noise when using FC3W in synthesizer mode. When using FC3W in jitter attenuator mode to generate a 312.5MHz SerDes reference clock, Renesas recommends the use of a 49.152MHz, 54MHz, or 73MHz crystal along with an APLL VCO frequency of 9.375GHz. This document explores an example of using a 49.152MHz crystal for jitter attenuator mode.

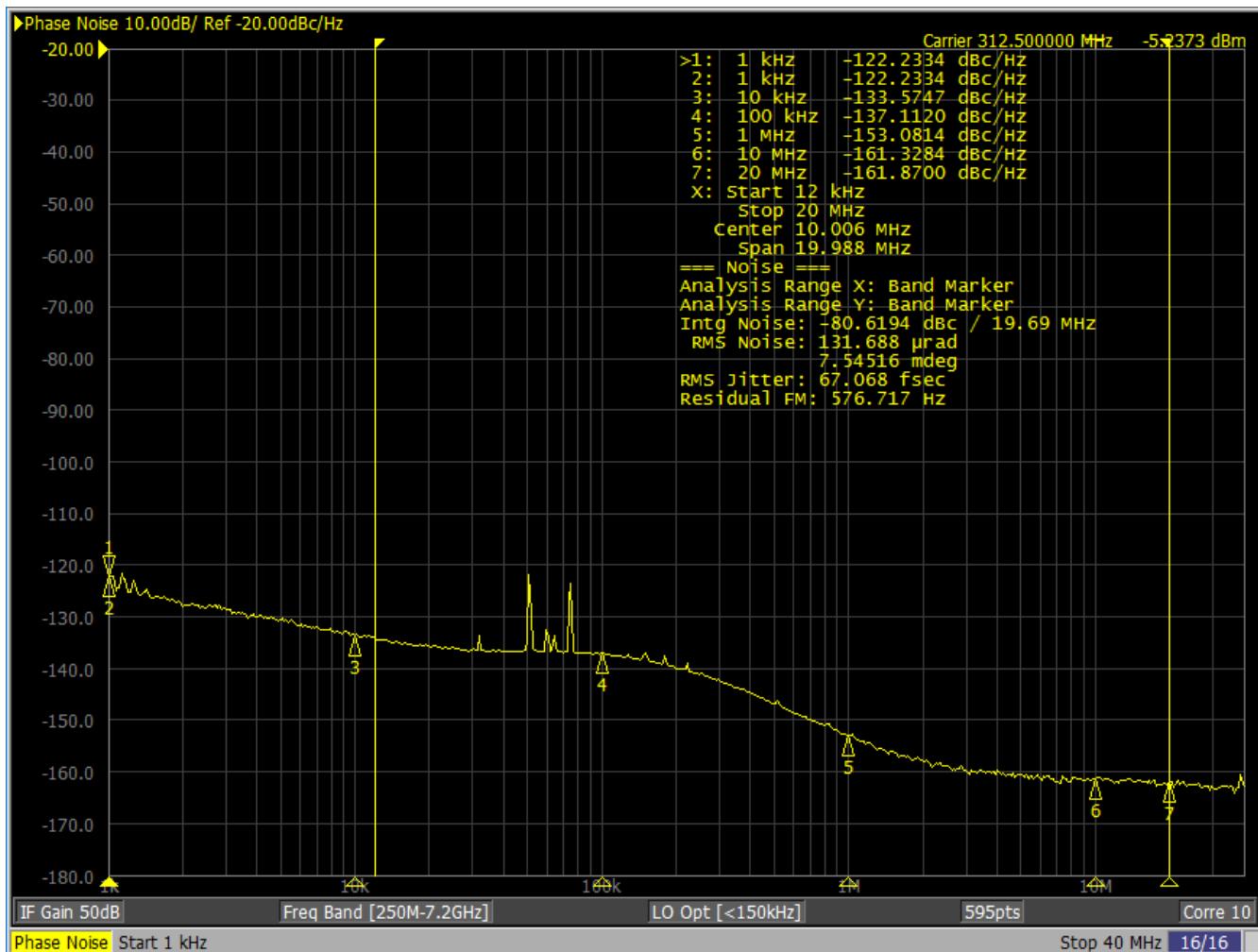

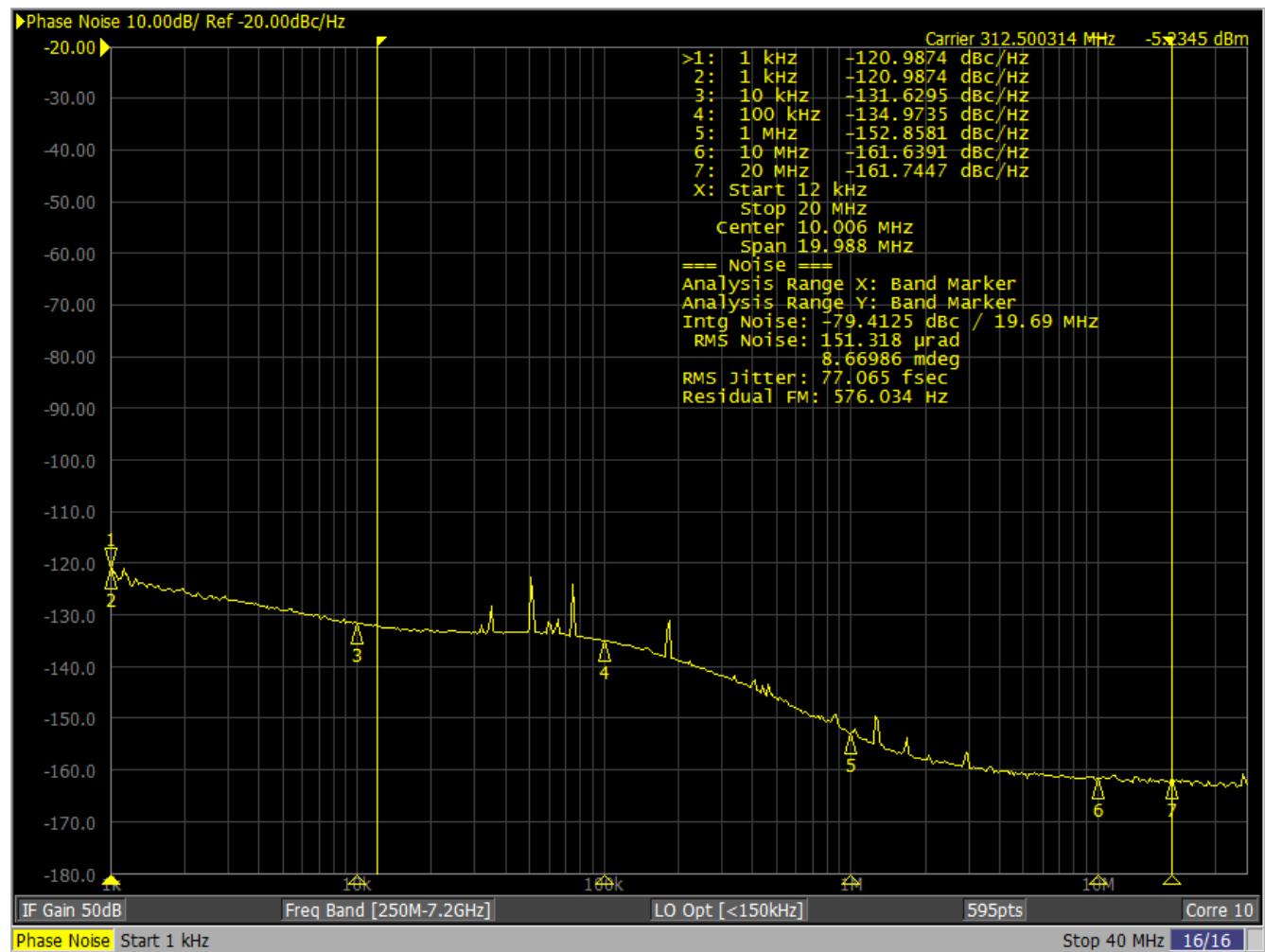

[Figure 7](#) shows the phase noise plot for a 312.5MHz FC3W output with a crystal input frequency of 62.5MHz (synthesizer mode) measured using a Rohde & Schwarz FSWP. [Figure 8](#) shows the phase noise plot for a 312.5MHz FC3 output with a crystal input frequency of 54MHz (jitter attenuator mode) and a reference input clock frequency of 25MHz measured using a Rohde & Schwarz FSWP. The RMS jitter value of a 312.5MHz output is approximately 56.3fs when using synthesizer mode with a 62.5MHz crystal, and approximately 68.6fs when using jitter attenuator mode with a 49.152MHz crystal. Therefore, the RMS jitter of FC3W is far below the typical maximum of 100fs used for many SerDes ASICs. Comparing [Figure 7](#), [Figure 8](#), [Figure 9](#), and [Figure 11](#) to [Table 2](#), which displays the phase noise requirements for a 112G receiver, FC3W meets the requirements at 10kHz, 100kHz, 1MHz, and > 10MHz.

112G PAM-4 SerDes uses a CDR bandwidth of 4MHz, which acts as a high-pass filter on the reference clock. Depending on the method used to simulate this 4MHz high-pass filter, a 312.5MHz FC3W output clock will have RMS jitter of ~19.4fs to ~23.7fs.

Renesas primarily uses two phase noise measurement instruments, the Keysight E5052B and the Rohde & Schwarz FSWP. Each instrument simulates filters differently. The Keysight E5052B can simulate a 4MHz high-pass filter by using its equation editor feature to apply a high-pass filter equation to the data trace. The Rohde & Schwarz can simulate a 4MHz high-pass filter by using its weighting filter feature. For more details on how to set up these features, see the [Applying Filters to Phase Noise Measurements with Keysight E5052 and Rohde & Schwarz FSWP](#) application note.

Using [Table 3](#) for the case where  $BER = 10^{-15}$  and  $DTD = 1$ , which will yield the highest RMS multiplier of  $N = 16.028$ , and using  $RJ_{rms} = 67.068\text{fs}$  as shown in [Figure 9](#),  $RJ_{PP} = 16.028 \times 67.068\text{fs} = 1.075\text{ps}$  for synthesizer mode with a 62.5MHz crystal and a 312.5MHz output. For jitter attenuator mode with a 49.152MHz crystal, a 312.5MHz output has  $RJ_{rms} = 77.065$ , as shown in [Figure 11](#). Thus,  $RJ_{PP} = 16.028 \times 77.065 = 1.235\text{ps}$  and the random jitter produced by a FC3W output is far below the recommended maximum of 28.8ps for a 312.5MHz SerDes reference clock.

## 4.1 FC3W With a 4MHz High Pass Filter Using the Rohde & Schwarz FSWP

Simulating a 4MHz high-pass filter using the Rohde & Schwarz FSWP involves applying a weighting filter to integrated measurement. The weighting filter feature only has an effect on the integrated measurement results and has no effect in the noise diagram or other numerical results.

Figure 7. Phase Noise Plot of a 312.5MHz Output from an RC38312 FC3W Device Operating in Synthesizer Mode using a 62.5MHz Crystal with an APPLL VCO Frequency of 9.375GHz; measured using a Rohde & Schwarz FSWP. Range 1 and 2 show Unfiltered RMS Jitter. Range 3 and 4 show RMS Jitter with a 4MHz High-Pass Filter applied

## How to Meet 112G PAM-4 SerDes Jitter Requirements with FemtoClock 3 and FemtoClock 3 Wireless Devices

**Figure 8. Phase Noise Plot of a 312.5MHz Output from an RC38312 FC3W Device Operating in Jitter Attenuator Mode using a 49.152MHz Crystal with an APLL VCO Frequency of 9.375GHz and a 25MHz + 1ppm Reference Input; measured using a Rohde & Schwarz FSWP. Range 1 and 2 show Unfiltered RMS Jitter. Range 3 and 4 show RMS Jitter with a 4MHz High-Pass Filter applied**

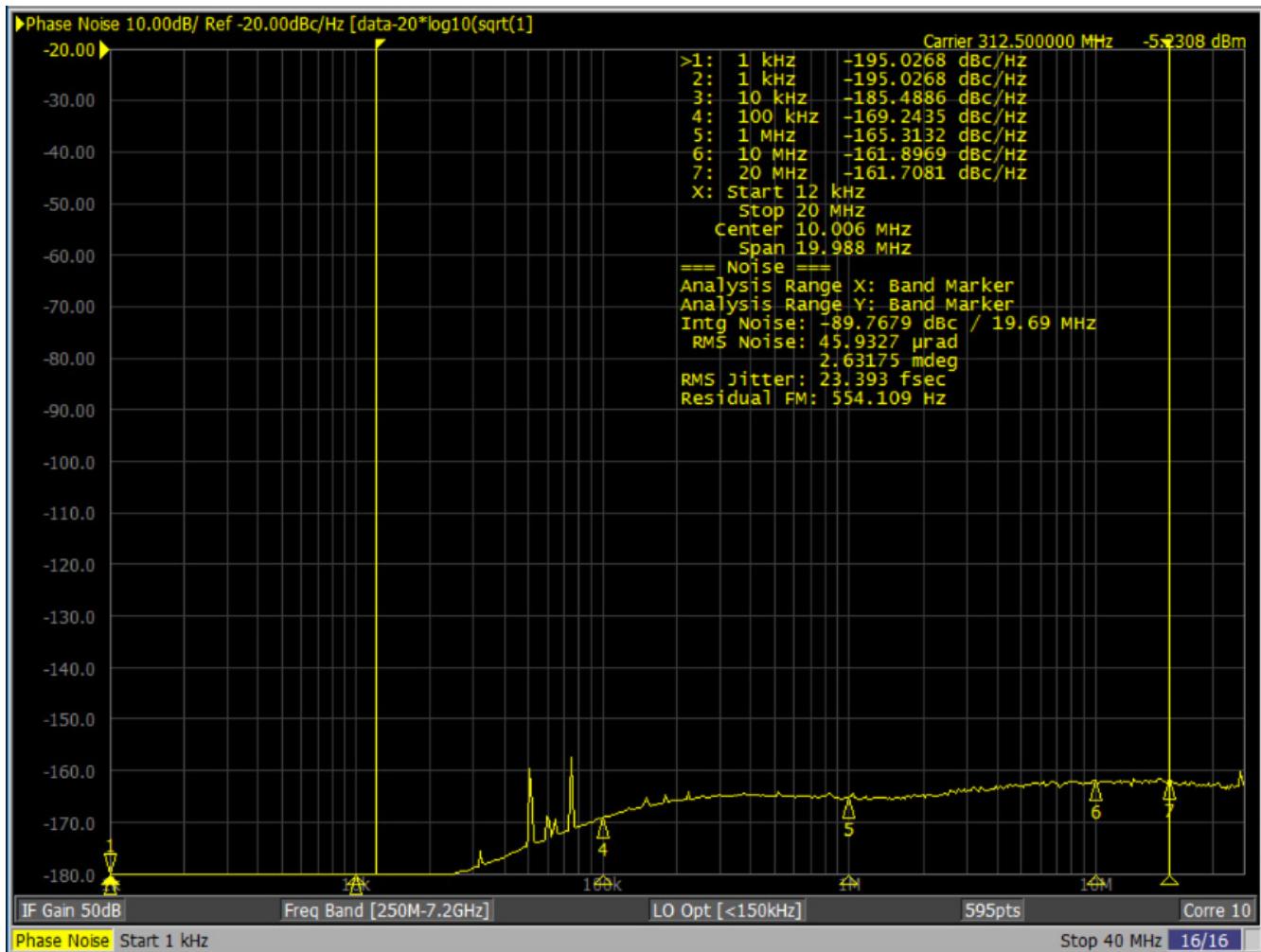

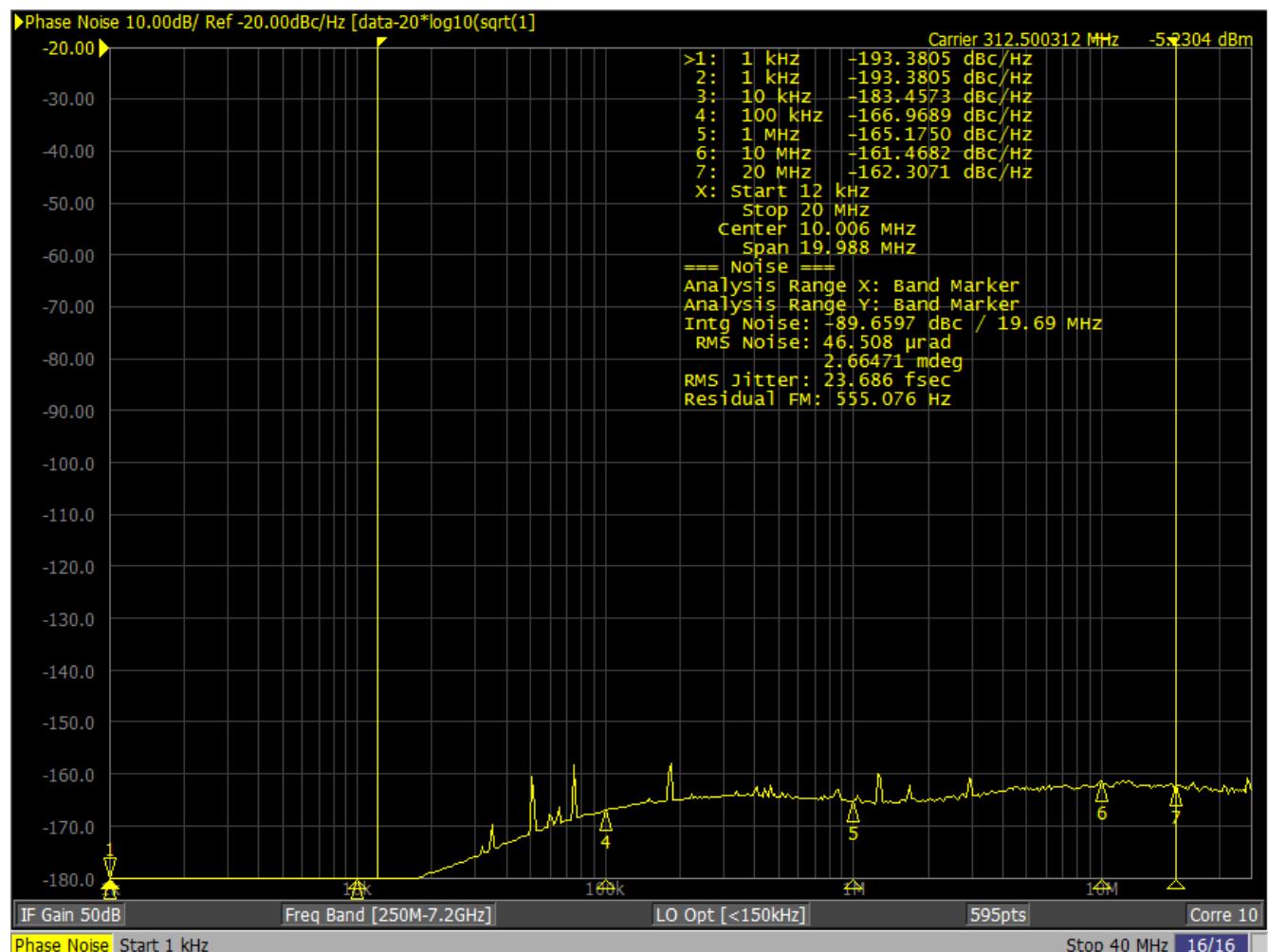

## 4.2 FC3W With a 4MHz High Pass Filter Using the Keysight E5052B

Simulating a 4MHz high-pass filter using the Keysight E5052B involves applying a mathematical function to the measured data for an integration range of 12kHz to 20MHz. The mathematical function to apply to the data is as follows:

$$F(x) = \text{data} - 20 \log_{10} \sqrt{1 + \frac{F_c^2}{x^2}}$$

**Equation 2. Function Used to Approximate a 4MHz High-Pass Filter for FC3W**

Where  $F_c$  is the corner frequency in Hz, which is equal to 4000000 in this case, and  $x$  is the offset frequency in Hz. [Figure 10](#) shows the phase noise after applying [Equation 2](#) to the data shown in [Figure 9](#). Similarly, [Figure 12](#) shows the phase noise after applying [Equation 2](#) to the data shown in [Figure 11](#). Using this method, the approximate RMS jitter on the receiver after the 4MHz high-pass filter will be ~23.4fs when using synthesizer mode with a 62.5MHz crystal, and ~23.7fs when using jitter attenuator mode with a 49.152MHz crystal.

## How to Meet 112G PAM-4 SerDes Jitter Requirements with FemtoClock 3 and FemtoClock 3 Wireless Devices

Figure 9. Phase Noise Plot for a 312.5MHz Output from an RC38312 FC3W Device Operating in Synthesizer Mode using a 62.5MHz Crystal with an APLL VCO Frequency of 9.375GHz; RMS Jitter also displayed

## How to Meet 112G PAM-4 SerDes Jitter Requirements with FemtoClock 3 and FemtoClock 3 Wireless Devices

Figure 10. Phase Noise Plot using a Keysight E5052B to Approximate the Effects of a 4MHz High-Pass Filter on a 312.5MHz Output from an RC38312 FC3W device Operating in Synthesizer Mode using a 62.5MHz Crystal along with an APLL VCO Frequency of 9.375GHz; RMS Jitter also displayed

## How to Meet 112G PAM-4 SerDes Jitter Requirements with FemtoClock 3 and FemtoClock 3 Wireless Devices

Figure 11. Phase Noise Plot for a 312.5MHz Output from an RC38312 FC3 Device Operating in Jitter Attenuator Mode using a 49.152MHz Crystal along with an APLL VCO Frequency of 9.375GHz, and a 25MHz + 1ppm Reference Clock Input; RMS Jitter also displayed

## How to Meet 112G PAM-4 SerDes Jitter Requirements with FemtoClock 3 and FemtoClock 3 Wireless Devices

Figure 12. Phase Noise Plot using a Keysight E5052B to Approximate the Effects of a 4MHz High-Pass Filter on a 312.5MHz Output from an RC38312 FC3W Device Operating in Jitter Attenuator Mode using a 49.152MHz crystal, and a 25MHz + 1ppm Reference Clock Input; RMS jitter also displayed

## 5. Crystal Recommendations for FC3 to Meet 112G PAM-4 SerDes Reference Clock Requirements

FC3 crystal requirements are explained in the [Choosing the Correct Crystal or XO for FemtoClock™3](#) application note. For a 312.5MHz 112G PAM-4 reference clock using FC3, Renesas recommends using a crystal or XO with a frequency of 62.5MHz if using synthesizer mode or a frequency of 49.152MHzMHz if using jitter attenuator mode. When using FC3W, Renesas recommends using a crystal or XO with a frequency of 62.5MHz if using synthesizer mode or a frequency of 54MHz if using jitter attenuator mode.

[Table 4](#) and [Table 5](#) list several crystals and XOs that Renesas recommends that will allow FC3 and FC3W to meet the SerDes reference clock requirements.

**Table 4. FC3 and FC3W Crystal Recommendations to Meet Requirements for a 312.5MHz 112G PAM-4 SerDes Reference Clock**

| Manufacturer | Type | Part Number    | Product Size (mm) | Freq. (MHz) | ESR (Ω) | C <sub>L</sub> (pF) | Typical Drive Level (μW) | Freq. Tolerance (ppm) | Frequency Stability (ppm) | Aging (ppm/year at 25°C) | Temperature Range (°C) |

|--------------|------|----------------|-------------------|-------------|---------|---------------------|--------------------------|-----------------------|---------------------------|--------------------------|------------------------|

| TXC          | XTAL | 7M49172003     | 3.2 × 2.5         | 49.152      | 20      | 8                   | 300                      | ±10                   | ±15                       | ±5                       | -40 to +85             |

| TXC          | XTAL | 8Y49172005     | 2.0 × 1.6         | 49.152      | 30      | 12                  | 100                      | ±10                   | ±15                       | ±1                       | -40 to +85             |

| TXC          | XTAL | 7M54072002     | 3.2 × 2.5         | 54          | 50      | 8                   | 100                      | ±12                   | ±15                       | ±3                       | -40 to +85             |

| TXC          | XTAL | 8Y62572002     | 2.0 × 1.6         | 62.5        | 40      | 8                   | 100                      | -5 to 12              | -15 to 12                 | ±1                       | -40 to +85             |

| TXC          | XTAL | 8Z62572001     | 2.5 × 2.0         | 62.5        | 40      | 8                   | 100                      | -5 to 12              | -15 to 12                 | ±1                       | -40 to +85             |

| TXC          | XTAL | 8Y73072002     | 2.0 × 1.6         | 73          | 40      | 8                   | 100                      | -5 to 12              | -15 to 12                 | ±1                       | -40 to 85              |

| NDK          | XTAL | EXS00A-CS15295 | 2.0 × 1.6         | 62.5        | 35      | 9                   | 200                      | ±30                   | -                         | -                        | -40 to +85             |

**Table 5. FC3 and FC3W XO Recommendations to Meet Requirements for a 312.5MHz 112G PAM-4 SerDes Reference Clock**

| Manufacturer | Type | Part Number | Product Size (mm) | Frequency (MHz) | Voltage (V) | Total Frequency Stability (ppm) | Temperature Range (°C) |

|--------------|------|-------------|-------------------|-----------------|-------------|---------------------------------|------------------------|

| TXC          | XO   | 8W49170004  | 2.5 × 2.0         | 49.152          | 3.3         | ±25                             | -40~+85                |

| TXC          | XO   | 8W62570006  | 2.5 × 2.0         | 62.5            | 3.3         | ±50                             | -40~+105               |

| TXC          | XO   | 8W73070001  | 2.5 × 2.0         | 73              | 3.3         | ±50                             | -40~+105               |

| NDK          | XO   | RNA5024A    | 2.5 × 2.0         | 54              | 3.3         | ±30                             | -40~+105               |

## 6. Revision History

| Revision | Date         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.04     | Jan 8, 2025  | <ul style="list-style-type: none"><li>▪ Replaced all screen shots with updated images and data.</li><li>▪ Updated sections <a href="#">3</a> and <a href="#">4</a> with revised text and new sub-sections.</li></ul>                                                                                                                                                                                                                                                                                                                 |

| 1.03     | Jun 14, 2024 | <ul style="list-style-type: none"><li>▪ Updated descriptive text in section <a href="#">4</a>.</li><li>▪ Added two entries of 49.152MHz XTAL specifications (part numbers 7M49172003 and 8Y49172005) to <a href="#">Table 4</a>.</li><li>▪ Added 73MHz XTAL specification (part number 8Y73072002) to <a href="#">Table 4</a>.</li><li>▪ Added 49.152MHz XO specification (part number 8W49170004) to <a href="#">Table 5</a>.</li><li>▪ Added 73MHz XO specification (part number 8W73070001) to <a href="#">Table 5</a>.</li></ul> |

| 1.02     | Jun 6, 2024  | <ul style="list-style-type: none"><li>▪ Updated document title to include FemtoClock 3 Wireless.</li><li>▪ Added FemtoClock 3 Wireless (FC3W) content throughout.</li></ul>                                                                                                                                                                                                                                                                                                                                                          |

| 1.01     | Nov 2, 2023  | Updated the titles of Figures 4, 5, and 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.00     | Nov 1, 2023  | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit [www.renesas.com/contact-us/](http://www.renesas.com/contact-us/).