# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# H8S/2378, H8S/2378R グループ

# ユーザプログラムモード時のフラッシュ書き込み/消去を効率よくデバッグする方法

#### 要旨

本アプリケーションノートは、H8S/2378R をユーザプログラムモードで動作させて、フラッシュメモリ( $0.18 \, \mu \, \text{m}$  F-ZTAT 版)の書き込み/消去の各処理の要所要所にエラーチェック手順を埋め込み、エミュレータの画面を使用しながら効率よくデバッグする方法を説明します。

本書の適用範囲は、フラッシュメモリ(0.18  $\mu$  m F-ZTAT 版)内蔵の H8S/2378 グループ、H8S/2378R グループとなっていますが、注意すべき項目ならびに着眼点は他の同類マイコンを使ったデバッグ作業時にも応用が可能です。

#### 目次

| 1.         | 仕様                                         | 2   |

|------------|--------------------------------------------|-----|

| 2.         | 動作概要                                       | 3   |

| 3.         | 開発環境                                       | 4   |

| 4.         | 使用機能説明                                     | 5   |

| 5.         | ソフトウェア説明                                   |     |

| 5.1        | 関数一覧                                       |     |

| 5.2<br>5.3 | ベクタテーブルセクション                               |     |

| 5.4        | マクロ定数                                      |     |

| 5.5        | H8S_2378R_MAIN.cファイル内関数の機能説明               |     |

| 5.6        | H8S_FlashPRG.cファイル内関数の機能説明                 |     |

| 5.7        | H8S_iic_sr.c <mark>.</mark> 関数の機能説明        |     |

| 5.8        | メモリマップ                                     | 31  |

| 6.         | 動作説明                                       | 33  |

| 6.1        | High-performance Embedded Workshop(HEW)の起動 |     |

| 6.2        | ワークスペースを開く                                 |     |

| 6.3        | サンプルプログラムの動作説明                             |     |

| 6.4        | フラッシュメモリ消去エラーチェック方法                        |     |

| 6.5        | フラッシュメモリ書き込みエラーチェック方法                      |     |

| 6.6        | エラー発生事象例                                   | 84  |

| 7.         | サンプルプログラムリスト                               | 87  |

| 8.         | よくある質問                                     | 102 |

| 9.         | 関連ドキュメント                                   | 105 |

| 付録         | to IIC マスタ送信側プログラム                         | 106 |

#### 1. 仕様

本アプリケーションノートでは、H8S/2378Rをユーザプログラムモードで動作させて、本書で説明するサンプルプログラムを使ってフラッシュメモリ( $0.18\,\mu\,\text{m}$  F-ZTAT版)の書き込み/消去を行い、各処理の要所要所に埋め込んだエラーチェック手順をE10A-USBエミュレータの画面を使って確認しながら正常に書き込み/消去が完了するまでを解説します。

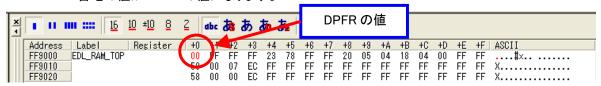

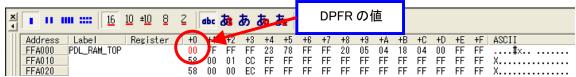

フラッシュメモリの書き込み/消去を行なう上で必要な処理として、H8S/2378Rに内蔵されている書き込み/消去プログラムの内蔵RAMへのダウンロード処理、初期化処理、書き込み/消去処理、書き込み終了処理があります。各処理には、エラーチェックのためのパラメータ(DPFR: ダウンロードパス・フェイルリザルトパラメータ、FPFR: フラッシュパス・フェイルパラメータ)があり、そのパラメータの戻り値を参照することで各処理が正常に行なえているか確認できます。

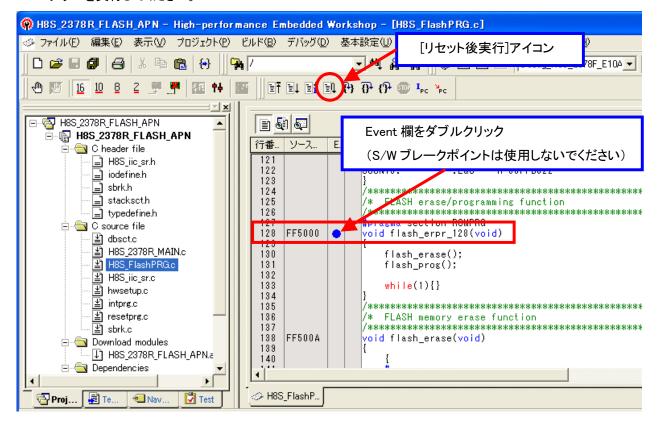

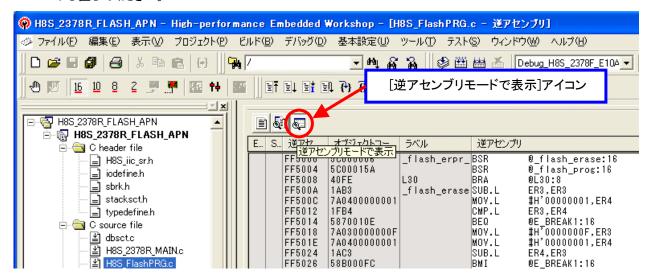

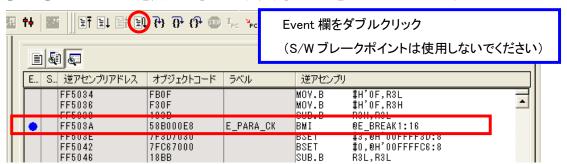

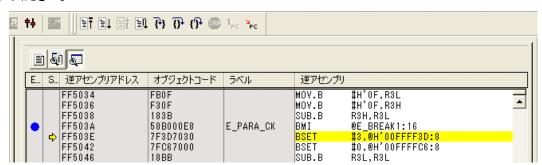

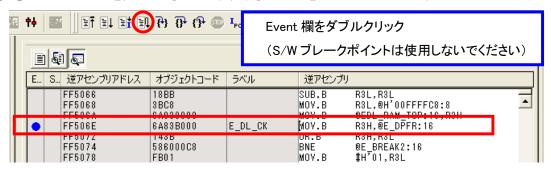

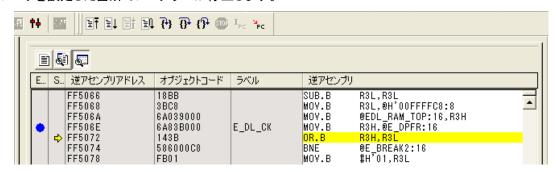

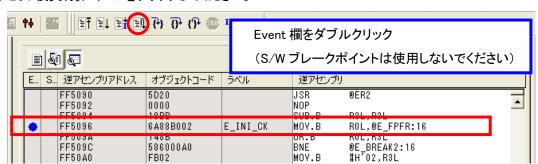

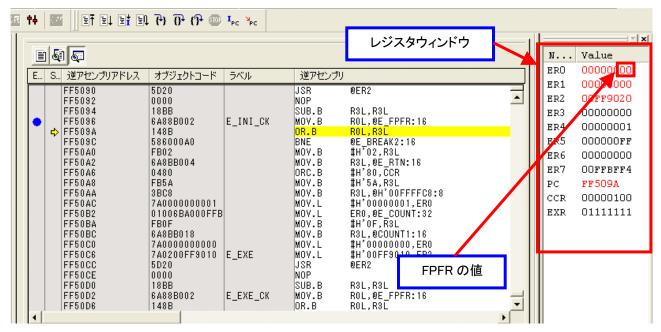

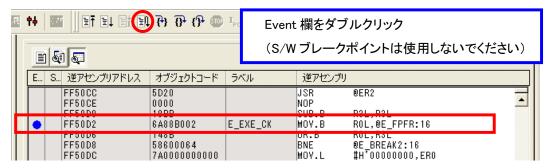

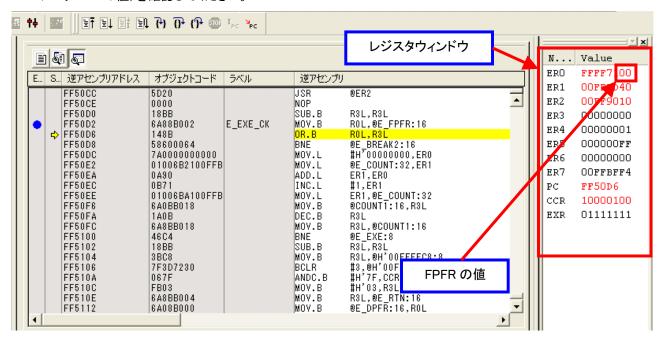

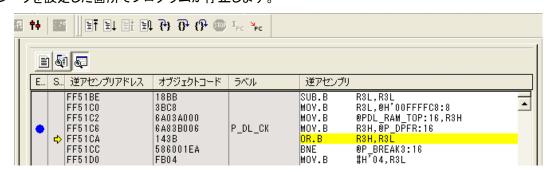

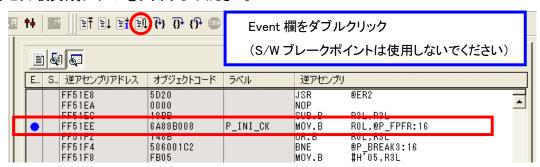

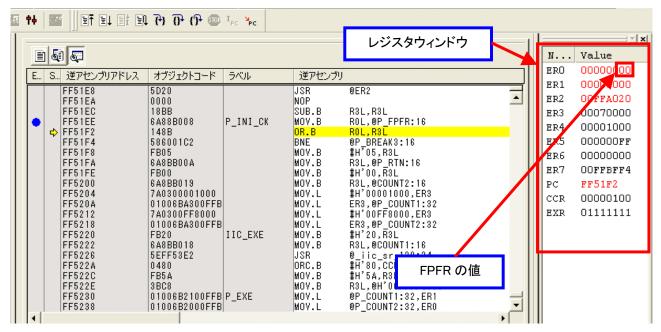

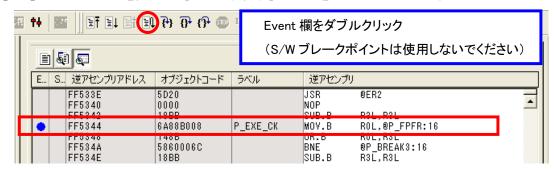

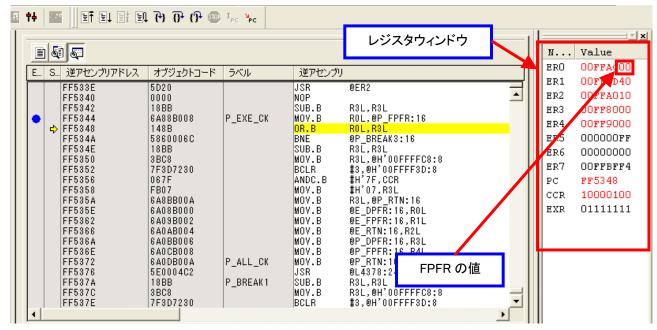

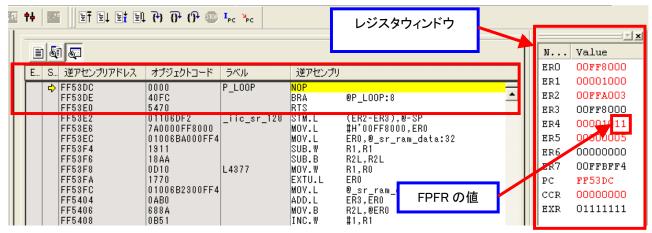

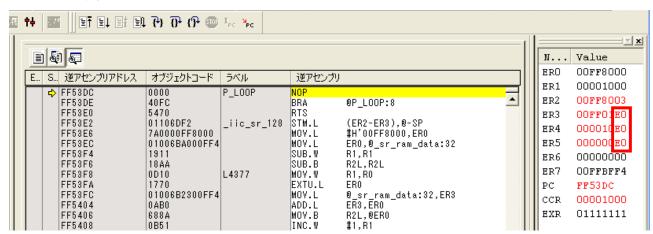

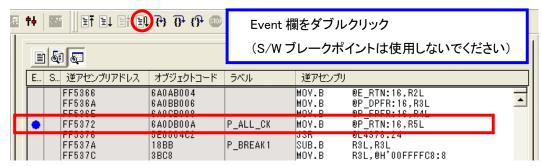

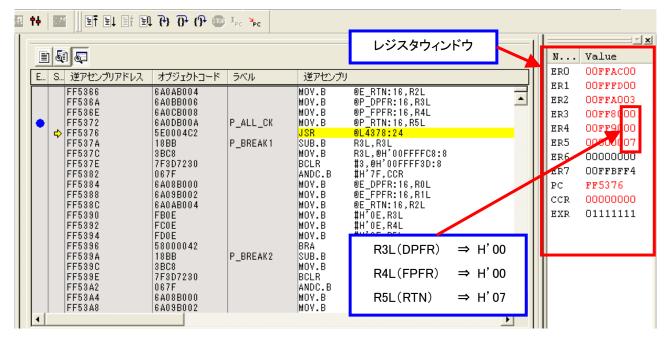

本サンプルプログラムでは、フラッシュメモリの書き込み/消去の各処理後にDPFRもしくはFPFRの戻り値を確認してエラーチェックを行うシーケンスになっています。本書の説明では、E10A-USBエミュレータのブレークコンディション機能を使用して各処理のエラーチェック後にブレークを設定し、ブレーク箇所でのDPFRもしくはFPFRの戻り値を確認してエラーチェックを行います。

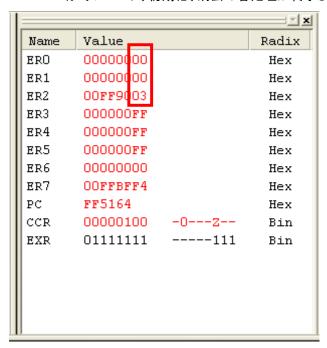

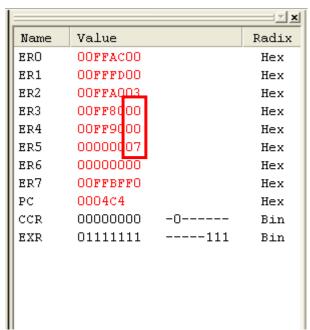

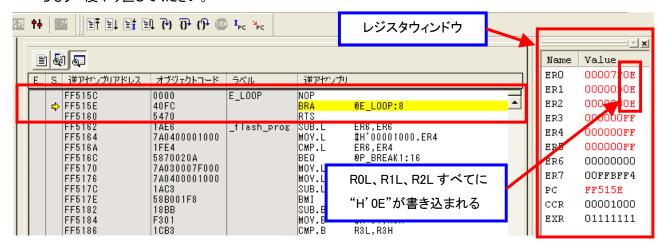

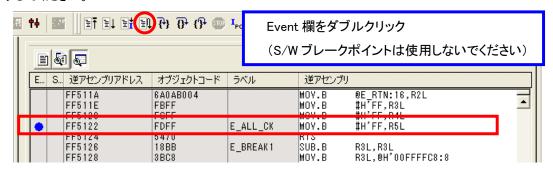

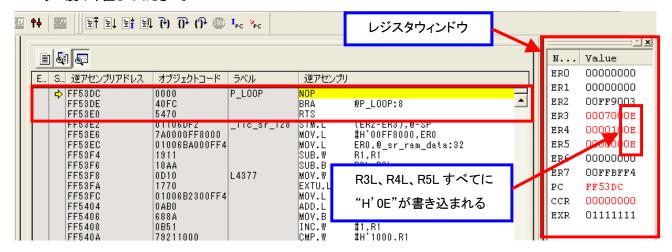

また、本サンプルプログラムではプログラム正常終了後、エラー発生後に汎用レジスタに下記パラメータを書き込むシーケンスになっていますので、汎用レジスタによってエラーチェック結果を確認することもできます。

- ・ROL → 消去プログラムのダウンロード処理エラーチェック結果(DPFR)の値

- ・R1L → 消去プログラムの初期化・消去処理エラーチェック結果(FPFR)の値

- •R2L → 消去プログラムの RTN の値

- ・R3L → 書き込みプログラムのダウンロード処理エラーチェック結果(DPFR)の値

- ・R4L → 書き込みプログラムの初期化・消去処理エラーチェック結果(FPFR)の値

- ·R5L → 書き込みプログラムの RTN の値

RTN とは各処理が行われ、終了すると 1 ずつ加算するパラメータで、どの処理でエラーが発生したか明確にする為に本サンプルプログラムで定義したシンボルです。

#### 【本アプリケーションノート(サンプルプログラム)を使用する上での注意事項】

- フラッシュメモリの書き込み/消去処理中は高電圧がフラッシュメモリに印加されるため、処理中はフラッシュメモリへのアクセスは禁止となっています。間違って処理中にフラッシュメモリへアクセスすると正常に処理が行われず、フラッシュメモリにダメージを与え破壊する可能性があります。

- よって、プログラム領域の内容はフラッシュメモリの書き込み/消去を行う前にフラッシュメモリ以外の領域に転送して実行する必要があります。本サンプルプログラムでは、内蔵RAMにプログラム領域の内容を転送して、内蔵RAM上でフラッシュメモリの書き込み/消去を行うプログラムを実行しています。

- ブレークする箇所は必ず書き込み/消去の各処理後とし、処理中の箇所にブレーク設定を行わないでください。また、書き込み処理と書き込み終了処理は一連の処理となっていますので、書き込み処理と書き込み終了処理の間にブレーク設定を行わないでください。

- 事き込み/消去の各処理中の箇所でシングルステップ実行を行わないでください。

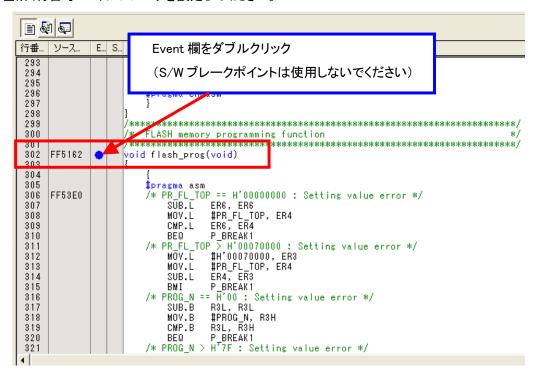

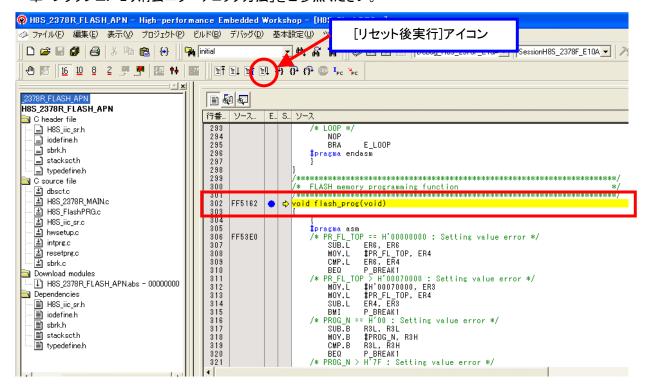

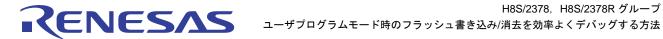

- E10A-USBエミュレータのソフトウェアブレークは使用しないでください。(フラッシュメモリへの書き 換えが発生してしまうため)

#### 2. 動作概要

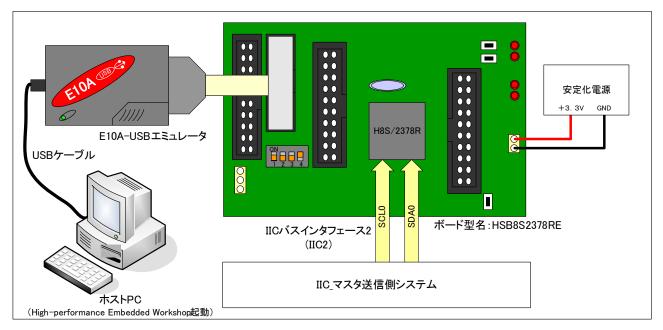

本章では、フラッシュメモリ書き込み/消去エラーチェックの動作概要を説明します。図 2.1 に動作環境を示します。

図 2.1 動作環境

- ① ボード(型名: HSB8S2378RE)上の H-UDI コネクタ(14ピンタイプ)に E10A-USB エミュレータを接続して、電源コネクタから 3.3V を供給します。

- ② ホストコンピュータで High-performance Embedded Workshop (HEW)を起動させて、本書で説明するサンプルプログラムをダウンロードして実行します。

- ③ 最初にサンプルプログラム内で設定したユーザマットのブロック番号に対応するフラッシュメモリのエリアを消去します。

- HEW を使って、各処理後(消去プログラムのダウンロード、初期化、消去)の DPFR(ダウンロードパス・フェイルリザルトパラメータ)、FPFR(フラッシュパス・フェイルパラメータ)の戻り値を確認してエラーチェックを行います。

- ④ フラッシュメモリ書き込みを行うため、書き込みプログラムのダウンロード処理、初期化処理を行います。各処理後、DPFR、FPFRの戻り値を確認してエラーチェックを行います。

- ⑤ 初期化処理終了後、IIC バスインタフェース 2 のチャネル 0(IIC2\_0)を使用して、IIC\_マスタ送信側から H8S/2378R(スレーブ受信)側へフラッシュメモリに書き込むデータを送信します。H8S/2378R 側で受信した データは内蔵 RAM に格納されます。1 回の通信で受信するデータサイズは 4k バイトとなっています。

- なお、フラッシュメモリに書き込むデータを送信する(IIC\_マスタ送信側)プログラムは、参考例として「付録 IIC\_マスタ送信側プログラム」に載せています。

- ⑥ 受信後、内蔵 RAM に格納されたデータ(4k バイト)をフラッシュメモリに書き込みます。書き込み処理後、FPFR の戻り値を確認してエラーチェックを行います。

- ⑦ サンプルプログラム内で設定した書き込み回数分、⑤・⑥の処理を繰り返します。最大 508k バイト(※1)のデータをフラッシュメモリに書き込むことができます。

- すべての書き込みが終わると、書き込み終了処理を行います。書き込み終了処理後、FPFR の戻り値を確認してエラーチェックを行います。

- ※1. このサンプルプログラムは、フラッシュメモリの H'000000~H'000FFF 番地をプログラム領域として使用しているため書き込めない仕様となっています。よって、プログラム領域の 4k バイト分を除いた 508k バイトが最大書き込みデータサイズとなります。

## 3. 開発環境

## 3.1 ハードウェア開発環境

表 3.1 にハードウェア開発環境の詳細を示します。

#### 表 3.1 ハードウェア開発環境

| 項目     | 内容                                   |

|--------|--------------------------------------|

| CPU 種類 | H8S/2378R(デバイス型名:HD64F2378R)         |

| メモリ容量  | ROM: 512k バイト、RAM: 32k バイト           |

| 使用ボード  | HSB シリーズ CPU ボード(ボード型名: HSB8S2378RE) |

| 電源電圧   | 3.3V                                 |

| 動作周波数  | 外部クロック: 8.25MHz、システムクロック: 33MHz      |

| 動作モード  | モード 7(シングルチップモード)(※1)                |

|        | MD2 = 1, $MD1 = 1$ , $MD0 = 1$       |

| エミュレータ | E10A-USB エミュレータ(製品型名:HS0005KCU02H)   |

<sup>※1.</sup> ユーザプログラムモードにするため、SYSCR(システムコントロールレジスタ)の FLSHE = 1 にしてください。

# 3.2 ソフトウェア開発環境

表 3.2 にソフトウェア開発環境の詳細を示します。

表 3.2 ソフトウェア開発環境

| 項目                    | 内容                                                                                                                 |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|

| 開発ツール                 | High-performance Embedded Workshop Ver. 4.03.00.001                                                                |

| C/C++コンパイラ            | H8S,H8/300 Standard Toolchain 6.2.0.0                                                                              |

| コンパイラオプション            | -cpu=2000A:24 -code=asmcode<br>-object="\$(CONFIGDIR)\pmax\\$(FILELEAF).src" -debug -nolist -chgincpath<br>-nologo |

| E10A-USB エミュレータソフトウェア | E10A-USB エミュレータソフトウェア V2.10 Release 01                                                                             |

#### 4. 使用機能説明

#### 4.1 IIC バスインタフェース 2 機能

本書で使用するサンプルプログラムは、フラッシュメモリに書き込むデータを H8S/2378R のオプション機能である IIC バスインタフェース 2 のチャネル 0(IIC2\_0)を使用して取得しています。表 4.1 に今回使用した IIC2\_0 の機能仕様を示します。

| 項目           | 内容                         |

|--------------|----------------------------|

| 使用シリアルクロック端子 | IIC2_0 シリアルクロック入出力端子(SCL0) |

| 使用シリアルデータ端子  | IIC2_0 シリアルデータ入出力端子(SDA0)  |

| 転送レート        | 98.2kbps                   |

| 通信モード        | スレーブ受信モード                  |

| スレーブアドレス     | H' 08                      |

| 受信データサイズ     | 4k バイト                     |

表 4.1 IIC バスインタフェース 2(IIC2) 機能仕様

#### 4.2 フラッシュメモリ書き込み/消去機能

本書で使用するサンプルプログラムは、ユーザプログラムモードでユーザマットの書き込み/消去を行っております。 あらかじめマイコン内に内蔵されているプログラムをダウンロードして書き込み/消去を実施します。

なお、書き込み/消去処理中はフラッシュメモリ内部に高電圧が印加されていますので、書き込み/消去処理中にはリセット、ハードウェアスタンバイへの遷移は行わないようにしてください。フラッシュメモリにダメージを与え、破壊する可能性があります。誤ってリセットしてしまった場合は、100  $\mu$  s の通常より長いリセット入力期間のあとにリセットリリースしてください。

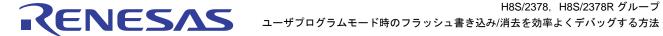

#### 4.2.1 フラッシュメモリ書き込み/消去実行時の内蔵 RAM アドレス

ダウンロードの要求、書き込み/消去の手順、結果の判定などのユーザで作成してもらう手続きプログラムの一部 は必ず内蔵 RAM 上で実行する必要があります。また、ダウンロードされる内蔵プログラムはすべて内蔵 RAM 上に 存在します。これらが重複することのないように、内蔵 RAM 上の領域管理に気を付けてください。図 4.1 にダウンロー ドされる書き込み/消去プログラムの領域を示します。

図 4.1 フラッシュメモリ書き込み/消去実行時の内蔵 RAM アドレスマップ

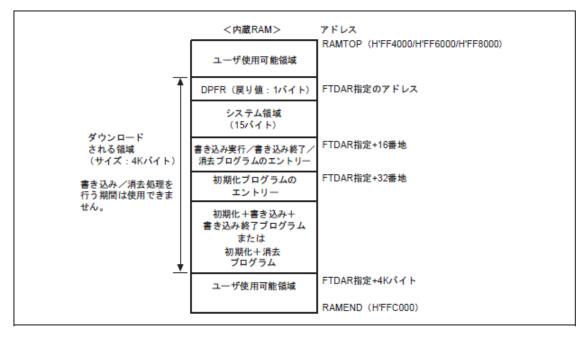

#### 4.2.2 ユーザプログラムモード時のフラッシュメモリ書き込み手順

図 4.2 にフラッシュメモリ書き込み手順を示します。

図 4.2 フラッシュメモリ書き込み手順

手続きプログラムは、書き込み対象のフラッシュメモリ以外で実行してください。特に、ダウンロードのために FCCS の SCO ビットを 1 に設定する部分は、必ず内蔵 RAM 上で実行するようにしてください。

1回の書き込み処理では128バイトの書き込みを行います。128バイトを超える書き込みを行う場合は、書き込み先アドレス/書き込みデータのパラメータを128バイト単位で更新して書き込みを繰り返します。

128 バイト未満の書き込みの場合も無効データを埋め込んで 128 バイトにそろえる必要があります。埋め込む無効データを H'FF にすると書き込み処理時間を短縮できます。

## 4.2.3 ユーザプログラムモード時のフラッシュメモリ消去手順

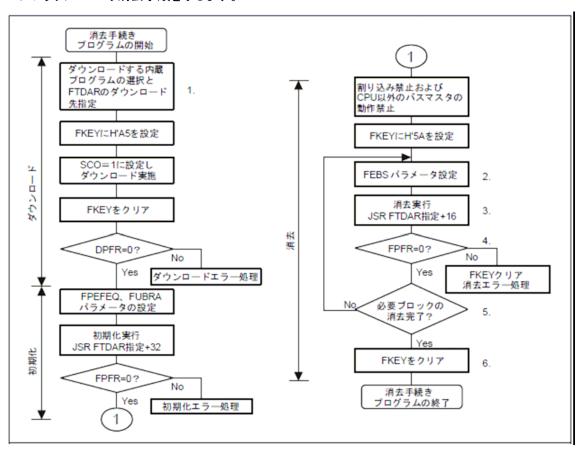

図 4.3 にフラッシュメモリ消去手順を示します。

図 4.3 フラッシュメモリ消去手順

手順プログラムは、消去対象のユーザマット以外で実行してください。特に、ダウンロードのために FCCS の SCO ビットを 1 に設定する部分は、必ず内蔵 RAM 上で実行するようにしてください。

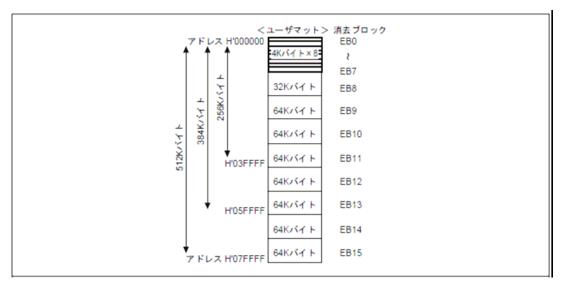

1回の消去処理では1分割ブロックの消去を行います。2ブロック以上の消去を行う場合は、消去ブロック番号を更新して消去を繰り返します。図4.4にユーザマットのブロック分割を示します。

図 4.4 ユーザマットのブロック分割

# 5. ソフトウェア説明

# 5.1 関数一覧

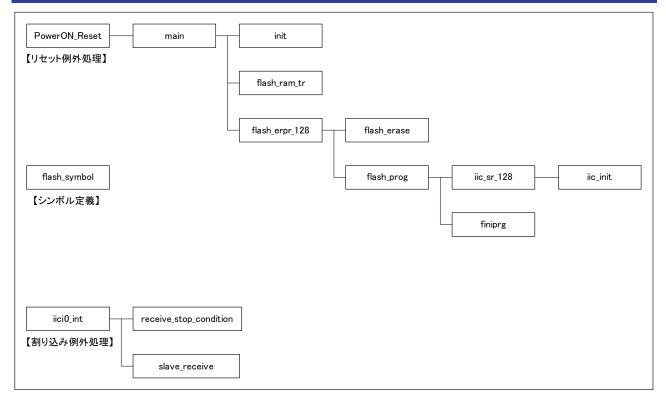

本書で使用するサンプルプログラムの関数一覧を表 5.1~表 5.3、階層構造図を図 5.1 に示します。

表 5.1 H8S\_2378R\_MAIN.c ファイル関数一覧

| 関数名          | 内容                                                                                                               |

|--------------|------------------------------------------------------------------------------------------------------------------|

| main         | フラッシュメモリに格納されたサンプルプログラムを内蔵 RAM へ転送する関数 (flash_ram_tr)と、フラッシュメモリ書き込み/消去を行う関数をコールする関数 (flash_erpr_128)をコールするメイン関数。 |

| init         | クロック設定、モジュールストップ解除を行う。                                                                                           |

| flash_ram_tr | フラッシュメモリに格納されたサンプルプログラムを内蔵 RAM へ転送。                                                                              |

| finiprg      | フラッシュメモリ書き込み/消去の正常終了時の分岐先。                                                                                       |

## 表 5.2 H8S\_FlashPRG.c ファイル関数一覧

| 関数名            | 内容                                                                                    |

|----------------|---------------------------------------------------------------------------------------|

| flash_symbol   | フラッシュメモリ書き込み/消去で使用するシンボルを定義。                                                          |

|                | (アセンブリ言語で記述)                                                                          |

| flash_erpr_128 | フラッシュメモリ書き込み/消去を行う関数(flash_erase、flash_prog)をコール。                                     |

| flash_erase    | フラッシュメモリの消去を行う。                                                                       |

|                | (アセンブリ言語で記述)                                                                          |

| flash_prog     | IIC バスインタフェース 2 のチャネル 0(IIC2_0)を使用(iic_sr_128 関数をコール)してデータを受信し、受信したデータをフラッシュメモリに書き込む。 |

|                | (アセンブリ言語で記述)                                                                          |

## 表 5.3 H8S\_iic\_sr.c ファイル関数一覧

| 関数名                    | 内容                                                        |

|------------------------|-----------------------------------------------------------|

| iic_sr_128             | IIC_マスタ送信側から送信されたデータに対して、スレーブ受信を開始する。                     |

| iic_init               | IIC バスインタフェース 2 のチャネル 0(IIC2_0)の初期化関数。                    |

| iici0_int              | IIC バスインタフェース 2 のチャネル 0(IIC2_0)の割り込み関数。                   |

| receive_stop_condition | 停止条件検出処理関数。                                               |

| slave_receive          | IIC バスインタフェース 2 のチャネル 0(IIC2_0)割り込み処理からコールされるスレーブ受信処理を行う。 |

図 5.1 サンプルプログラム階層構造図

## 5.2 ベクタテーブル

本書で使用するサンプルプログラムで使用している例外処理ベクタテーブルを表 5.4 に示します。

表 5.4 例外処理ベクタテーブル

| 例外処理要因     | ベクタ番号 | ベクタテーブルアドレス | 割り込み先関数       |

|------------|-------|-------------|---------------|

| リセット       | 0     | H' 000000   | PowerON_Reset |

| IICIO 割り込み | 116   | H' 0001D0   | iici0_int     |

# 5.3 セクション

本書で使用するサンプルプログラムのセクション詳細を表 5.5 に示します。

表 5.5 セクション

| セクション名    | アドレス                  | 内容                                 |

|-----------|-----------------------|------------------------------------|

| PResetPRG | H'000400 ~ H'000415   | リセットスタート領域                         |

| PIntPRG   | H'000416 ~ H'0004C1   | 割り込み領域                             |

| PFiniPRG  | H'0004C2 ~ H'0004C3   | finiprg 関数領域                       |

| Р         | H'000800 ~ H'0008E3   | プログラム領域                            |

| PROMPRG   | H'0008E4 ~ H'000DE1   | 内蔵 RAM へ転送するプログラム領域                |

| C\$DSEC   | H'000DE2 ~ H'000DED   | 初期化データセクションのアドレス領域                 |

| C\$BSEC   | H'000DEE ~ H'000DF5   | 未初期化データセクションのアドレス領域                |

| D         | H'000DF6 ~ H'000DF9   | 初期化データ領域                           |

| В         | H' FF4000 ~ H' FF4427 | 未初期化データ領域                          |

| R         | H' FF4428 ~ H' FF442B | セクション"D"の内蔵 RAM へのマップ先領域           |

| PRAMPRG   | H'FF5000 ~ H'FF54FD   | セクション"PROMPRG"の内蔵 RAM へのマップ先<br>領域 |

| S         | H'FFBE00 ∼ H'FFBFFF   | スタック領域                             |

# 5.4 マクロ定数

本書で使用するサンプルプログラム内で定義しているマクロ定数を表 5.6、表 5.7 に示します。

表 5.6 マクロ定数(IIC バスインタフェース 2(IIC2)関連)

| 定数名        | 設定値     | 内容                                     | 使用関数名                                      |

|------------|---------|----------------------------------------|--------------------------------------------|

| SLAVE_ADDR | H' 08   | スレーブアドレス                               | iic_init                                   |

| MODE_ST    | 2       | サンプルプログラム内での処理状態<br>スレーブ送信モード          | iici0_int                                  |

| MODE_SR    | 1       | サンプルプログラム内での処理状態<br>スレーブ受信モード          | iici0_int                                  |

| MODE_IDLE  | 0       | サンプルプログラム内での処理状態<br>アイドルモード            | iic_init、iici0_int、 receive_stop_condition |

| DTNUM      | H' 1000 | 受信データサイズ<br>(1 バイト * H' 1000 = 4k バイト) | iic_sr_128                                 |

#### 表 5.7 マクロ定数(フラッシュ書き込み/消去関連)

| シンボル名         | 設定値         | 内容                                   | 使用関数名       |

|---------------|-------------|--------------------------------------|-------------|

| BLOCK_NUM(%1) | H' 0000001  | 消去開始ブロック番号                           | flash_erase |

|               |             | 設定範囲:H'00000001~H'0000000F           |             |

| ERASE_N(※2)   | H'0F        | 消去回数                                 | flash_erase |

|               |             | 設定範囲:BLOCK_NUM の設定値に依存               |             |

|               |             | (6.3.1 章の表 6.2 をご参照ください)             |             |

| PR_FL_TOP     | H' 00001000 | フラッシュメモリ書き込み先の先頭アドレス                 | flash_prog  |

|               |             | 設定範囲:H'00001000~H'0007F000           |             |

| PROG_N(※3)    | H' 01       | 書き込み回数                               | flash_prog  |

|               |             | 測定範囲:PR_FL_TOP の設定値に依存               |             |

|               |             | (6.3.2 章の表 6.3 をご参照ください)             |             |

| PROG_SIZE     | H' 20       | 書き込み回数 1 回あたりのデータサイズ                 | flash_prog  |

|               |             | (128 バイト * H' 20 = 4k バイト)           |             |

| DATA_RAM_TOP  | H' 00FF8000 | 受信データバッファの先頭アドレス                     | flash_prog  |

| EDL_RAM_TOP   | H' 00FF9000 | 消去プログラムダウンロード先の先頭アドレス                | flash_erase |

| PDL_RAM_TOP   | H'00FFA000  | 書き込みプログラムダウンロード先の先頭アドレス              | flash_prog  |

| E_DPFR        | H'00FFB000  | 消去時のダウンロードパス・フェイルリザルトパ<br>ラメータアドレス   | flash_erase |

| E_FPFR        | H' 00FFB002 | 消去時のフラッシュパス・フェイルパラメータアド<br>レス        | flash_erase |

| E_RTN         | H' 00FFB004 | 消去処理実行結果チェックパラメータアドレス                | flash_erase |

| P_DPFR        | H'00FFB006  | 書き込み時のダウンロードパス・フェイルリザル<br>トパラメータアドレス | flash_prog  |

| P_FPFR        | H'00FFB008  | 書き込み時のフラッシュパス・フェイルパラメー<br>タアドレス      | flash_prog  |

| P_RTN         | H'00FFB00A  | 書き込み処理実行結果チェックパラメータアドレス              | flash_prog  |

|               |             |                                      |             |

<sup>※1.</sup> BLOCK\_NUM は、フラッシュメモリの消去を開始するブロック番号(EB1~EB15)を指定します。このサンプルプログラムは、 EB0 をプログラム領域として使用しているため消去できない仕様となっています。

<sup>※2.</sup> ERASE\_N は、BLOCK\_NUM で指定したブロック番号から数えて順番に、ブロック単位で消去を何回行うか指定します。例えば、BLOCK\_NUM を"H'00000001"、ERASE\_N を"H'0F"と設定すると EB1~EB15 を消去対象ブロックとします。

<sup>※3.</sup> PROG\_N は、4k バイトのデータを繰り返し何回書き込むか指定します。最大で 508kバイトのデータ(設定値"H'7F")をフラッシュメモリに書き込むことができます。

# 5.5 H8S\_2378R\_MAIN.c ファイル内関数の機能説明

本章では、H8S\_2378R\_MAIN.c ファイル内の関数について機能と使用レジスタを説明します。

#### 5.5.1 init 関数

#### 表 5.8 init 関数の機能説明

| 機能                       | 戻り値 | 引数 |

|--------------------------|-----|----|

| ・分周器の分周比選択               | なし  | なし |

| ・PLL 回路の逓倍率設定            |     |    |

| ・IIC2_0 を除く全てのモジュールをストップ |     |    |

#### 【使用レジスタ】

システムクロックコントロールレジスタ(SCKCR)

アドレス:H'FFFF3B

| ビット | ビット名 | 初期値 | R/W | 説明                               |

|-----|------|-----|-----|----------------------------------|

| 3   | STCS | 0   | R/W | 周波数逓倍率切り替えモード選択                  |

|     |      |     |     | PLL 回路の周波数逓倍率変更時の動作を選択します。       |

|     |      |     |     | 0:変更した逓倍率は、ソフトウェアスタンバイモード遷移後に有効  |

|     |      |     |     | 1:変更した逓倍率は、STC1、STC0 ビット書き換え後に有効 |

| 2   | SCK2 | 0   | R/W | システムクロックセレクト 2~0                 |

| 1   | SCK1 | 0   | R/W | 分周比を選択します。                       |

| 0   | SCK0 | 0   | R/W | 000:1/1                          |

|     |      |     |     | 001:1/2                          |

|     |      |     |     | 010:1/4                          |

|     |      |     |     | 011:1/8                          |

|     |      |     |     | 100:設定禁止                         |

|     |      |     |     | 101:設定禁止                         |

|     |      |     |     | 11X:設定禁止                         |

#### PLL コントロールレジスタ(PLLCR)

アドレス:H'FFFF45

| ビット | ビット名 | 初期値 | R/W | 説明                   |

|-----|------|-----|-----|----------------------|

| 1   | STC1 | 0   | R/W | 周波数逓倍率設定             |

| 0   | STC0 | 0   | R/W | PLL 回路の周波数逓倍率を設定します。 |

|     |      |     |     | 00: ×1               |

|     |      |     |     | 01:×2                |

|     |      |     |     | 10: × 4              |

|     |      |     |     | 11:設定禁止              |

モジュールストップコントロールレジスタ H、L(MSTPCRH、MSTPCRL)

アドレス:H'FFFF40

1 のとき対応するモジュールはモジュールストップモードになり、クリアするとモジュールストップモードは解除され ます。

#### **MSTPCRH**

| ビット | ビット名   | 初期値 | R/W | 説明                                                                                                     |

|-----|--------|-----|-----|--------------------------------------------------------------------------------------------------------|

| 15  | ACSE   | 0   | R/W | 全モジュールクロックストップモードイネーブル                                                                                 |

|     |        |     |     | MSTPCR で制御されるすべての内蔵周辺機能、または TMR 以外の内蔵周辺機能をモジュールストップモードにし、SLEEP 命令実行後の全モジュールクロックストップモードへの遷移を許可または禁止します。 |

|     |        |     |     | 0:全モジュールクロックストップモードを禁止                                                                                 |

|     |        |     |     | 1:全モジュールクロックストップモードを許可                                                                                 |

| 14  | MSTP14 | 0   | R/W | EXDMA コントローラ(EXDMAC)                                                                                   |

| 13  | MSTP13 | 0   | R/W | DMA コントローラ(DMAC)                                                                                       |

| 12  | MSTP12 | 0   | R/W | データトランスファコントローラ(DTC)                                                                                   |

| 11  | MSTP11 | 1   | R/W | 16 ビットタイマパルスユニット(TPU)                                                                                  |

| 10  | MSTP10 | 1   | R/W | プログラマブルパルスジェネレータ(PPG)                                                                                  |

| 9   | MSTP9  | 1   | R/W | D/A 変換器(チャネル 0、1)                                                                                      |

| 8   | MSTP8  | 1   | R/W | D/A 変換器(チャネル 2、3)                                                                                      |

#### **MSTPCRL**

| ビット | ビット名  | 初期値 | R/W | 説明                            |

|-----|-------|-----|-----|-------------------------------|

| 7   | MSTP7 | 1   | R/W | D/A 変換器(チャネル 4、5)             |

| 6   | MSTP6 | 1   | R/W | A/D 変換器                       |

| 5   | MSTP5 | 1   | R/W | シリアルコミュニケーションインタフェース 4(SCI_4) |

| 4   | MSTP4 | 1   | R/W | シリアルコミュニケーションインタフェース 3(SCI_3) |

| 3   | MSTP3 | 1   | R/W | シリアルコミュニケーションインタフェース 2(SCI_2) |

| 2   | MSTP2 | 1   | R/W | シリアルコミュニケーションインタフェース 1(SCI_1) |

| 1   | MSTP1 | 1   | R/W | シリアルコミュニケーションインタフェース 0(SCI_0) |

| 0   | MSTP0 | 1   | R/W | 8 ビットタイマ (TMR)                |

エクステンションモジュールストップコントロールレジスタ H、L(EXMSTPCRH、EXMSTPCRL) アドレス:H'FFFF42

1 のとき対応するモジュールはモジュールストップモードになり、クリアするとモジュールストップモードは解除され ます。

## **EXMSTPCRH**

| ビット   | ビット名   | 初期値 | R/W | 説明                              |

|-------|--------|-----|-----|---------------------------------|

| 15~12 | -      | 1   | R/W | リザーブビット                         |

|       |        |     |     | リード/ライト可能ですがライト時は 1 をライトしてください。 |

| 11    | MSTP27 | 1   | R/W | -                               |

| 10    | MSTP26 | 1   | R/W | _                               |

| 9     | MSTP25 | 1   | R/W | _                               |

| 8     | MSTP24 | 1   | R/W | _                               |

#### **EXMSTPCRL**

| ビット | ビット名   | 初期値 | R/W | 説明                         |

|-----|--------|-----|-----|----------------------------|

| 7   | MSTP23 | 1   | R/W | -                          |

| 6   | MSTP22 | 1   | R/W | -                          |

| 5   | MSTP21 | 1   | R/W | -                          |

| 4   | MSTP20 | 1   | R/W | IIC バスインタフェース 2_1 (IIC2_1) |

| 3   | MSTP19 | 1   | R/W | IIC バスインタフェース 2_0(IIC2_0)  |

| 2   | MSTP18 | 1   | R/W | -                          |

| 1   | MSTP17 | 0   | R/W | -                          |

| 0   | MSTP16 | 1   | R/W | -                          |

# 5.5.2 main 関数

## 表 5.9 main 関数の機能説明

| 機能                                     | 戻り値 | 引数 |

|----------------------------------------|-----|----|

| ・RAM 転送関数(flash_ram_tr)のコール            | なし  | なし |

| ・フラッシュメモリ書き込み/消去関数(flash_erpr_128)のコール |     |    |

## 【使用レジスタ】

なし

# 5.5.3 flash\_ram\_tr 関数

## 表 5.10 flash\_ram\_tr 関数の機能説明

| 機能                                                             | 戻り値 | 引数 |

|----------------------------------------------------------------|-----|----|

| ・フラッシュメモリに格納されるセクション"PROMPRG"のプログラムを内蔵 RAM 上のセクション"PRAMPRG"に転送 | なし  | なし |

## 【使用レジスタ】

なし

# 5.5.4 finiprg 関数

## 表 5.11 finiprg 関数の機能説明

| 機能                                    | 戻り値 | 引数 |

|---------------------------------------|-----|----|

| ・フラッシュメモリ書き込み/消去が正常に終了した時の戻り(ジャンプ先)関数 | なし  | なし |

## 【使用レジスタ】

なし

# 5.6 H8S\_FlashPRG.c ファイル内関数の機能説明

本章では、H8S\_FlashPRG.c ファイル内の関数について機能と使用レジスタを説明します。

## 5.6.1 flash\_symbol 関数

表 5.12 flash\_symbol 関数の機能説明

| 機能                                        | 戻り値 | 引数 |

|-------------------------------------------|-----|----|

| ・フラッシュメモリ書き込み/消去で使用するシンボルを定義し、インライン展開している | なし  | なし |

#### 【使用レジスタ】

なし

## 5.6.2 flash\_erpr\_128 関数

表 5.13 flash\_erpr\_128 関数の機能説明

| 機能                              | 戻り値 | 引数 |

|---------------------------------|-----|----|

| ・フラッシュメモリ消去関数(flash_erase)のコール  | なし  | なし |

| ・フラッシュメモリ書き込み関数(flash_prog)のコール |     |    |

#### 【使用レジスタ】

なし

# 5.6.3 flash\_erase 関数

表 5.14 flash\_erase 関数の機能説明

| 機能                          | 戻り値 | 引数 |

|-----------------------------|-----|----|

| ・消去処理で使用するシンボルの設定値チェック      | なし  | なし |

| ・ユーザプログラムモードへの遷移(FLSHE = 1) |     |    |

| ・消去プログラムのダウンロード処理           |     |    |

| ・フラッシュメモリの初期化処理             |     |    |

| ・フラッシュメモリの消去処理              |     |    |

| ・各処理のエラーチェック                |     |    |

## 【使用レジスタ】

#### システムコントロールレジスタ(SYSCR)

| ビット | ビット名  | 初期値 | R/W | 説明                                                                                                                                                                                |

|-----|-------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | FLSHE | 0   | R/W | フラッシュメモリコントロールレジスタイネーブル                                                                                                                                                           |

|     |       |     |     | フラッシュメモリの制御レジスタの CPU アクセスを制御します。このビットを 1 にセットすると、フラッシュメモリの制御レジスタをリード/ライトすることができます。 0 にクリアするとフラッシュメモリの制御レジスタは非選択となります。このとき、フラッシュメモリの制御レジスタの内容は保持されています。 フラッシュメモリ版以外は 0 をライトしてください。 |

|     |       |     |     | 0:アドレス H'FFFFC4~H'FFFFCF のエリアはフラッシュメモリのレジスタを非選択                                                                                                                                   |

|     |       |     |     | 1:アドレス H'FFFFC4~H'FFFFCF のエリアはフラッシュメモリのレジスタを選択                                                                                                                                    |

## フラッシュイレーズコードセレクトレジスタ(FECS)

アドレス:H'FFFFC6

アドレス:H'FFFF3D

| ビット | ビット名 | 初期値 | R/W | 説明                       |

|-----|------|-----|-----|--------------------------|

| 0   | EPVB | 0   | R/W | イレーズパルスベリファイブロック         |

|     |      |     |     | 消去プログラムを選択します。           |

|     |      |     |     | 0:内蔵消去プログラムを選択しません。      |

|     |      |     |     | [クリア条件] 転送が終了するとクリアされます。 |

|     |      |     |     | 1:内蔵消去プログラムを選択します。       |

### フラッシュトランスファディスティネーションアドレスレジスタ(FTDAR)

アドレス:H'FFFFCA

| ビット | ビット名 | 初期値 | R/W | 説明                                                                                                                                                                                                                       |

|-----|------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TDER | 0   | R/W | トランスファディスティネーションアドレス設定エラー                                                                                                                                                                                                |

|     |      |     |     | TDA6~TDA0 ビットで指定するダウンロード先頭アドレス指定にエラーがあった場合、1 がセットされます。アドレス指定のエラー判定は、FCCS のSCO ビットを 1 にして、ダウンロード処理が実行されたときに、TDA6~TDA0の値がH'00~H'03の範囲にあるかどうかを判定します。SCOビットを 1 に設定する前に、本ビットの値を 0 にすることも含めて、FTDAR の値を H'00~H'03 の範囲に設定してください。 |

|     |      |     |     | 0:TDA6~TDA0 の設定は、正常値です。                                                                                                                                                                                                  |

|     |      |     |     | 1:TDER、TDA6~TDA0 の設定値が H'04~H'FF であり、ダウンロード<br>は中断したことを示します。                                                                                                                                                             |

フラッシュトランスファディスティネーションアドレスレジスタ(FTDAR)

アドレス:H'FFFFCA

| ビット | ビット名 | 初期値 | R/W | 説明                                                                     |

|-----|------|-----|-----|------------------------------------------------------------------------|

| 6   | TDA6 | 0   | R/W | トランスファディスティネーションアドレス                                                   |

| 5   | TDA5 | 0   | R/W | ダウンロード先頭アドレスを指定します。設定可能な値はH'00~H'03で、4Kバイト単位で内蔵RAM 上のダウンロード先頭アドレスを指定でき |

| 4   | TDA4 | 0   | R/W | ます。                                                                    |

| 3   | TDA3 | 0   | R/W | H'00:ダウンロード先頭アドレスをH'FF9000に設定<br>H'01:ダウンロード先頭アドレスをH'FFA000に設定         |

| 2   | TDA2 | 0   | R/W | H'02:ダウンロード先頭アドレスをH'FFB000に設定                                          |

| 1   | TDA1 | 0   | R/W | H'03:ダウンロード先頭アドレスをH'FF8000に設定<br>H'04~H'7F:設定しないでください。この値が設定された場合、ダウン  |

| 0   | TDA0 | 0   | R/W | ロード処理において、TDER ビットが1になり、内蔵プログラ                                         |

|     |      |     |     | ムのダウンロード処理は中断されます。                                                     |

ダウンロードパス・フェイルリザルトパラメータ(DPFR: FTDAR レジスタで指定した内蔵 RAM の先頭アドレス 1 バイト) ダウンロード結果の戻り値です。ダウンロードが実行できたかどうかは、本パラメータの値で判断します。

| ビット | ビット名 | 初期値 | R/W | 説明                                                                                                                                                                                         |

|-----|------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7~3 | -    | -   | -   | 未使用ビット<br>値 0 が戻されます。                                                                                                                                                                      |

| 2   | SS   | -   | R/W | ソースセレクトエラー検出ビット<br>ダウンロード可能な内蔵プログラムは1種類のみ指定できます。2種類以<br>上の選択を行った場合、選択されていない場合、およびマッピングされて<br>いない選択の場合にはエラーとなります。<br>0:ダウンロードプログラムの選択関係は正常<br>1:ダウンロードエラー発生(多重選択または、マッピングされていないプ<br>ログラム選択) |

| 1   | FK   | _   | R/W | フラッシュキーレジスタエラー検出ビット<br>FKEYの値が、H'A5であるかどうかをチェックした結果を返すビットです。<br>0:FKEYの設定は正常(FKEY = H'A5)<br>1:FKEYの設定値エラー(FKEY は、H'A5 以外の値)                                                               |

| 0   | SF   | -   | R/W | サクセス/フェイルビット<br>ダウンロードが正常に終了したかどうかを戻すビットです。内蔵RAM上に<br>ダウンロードしたプログラムをリードバックし、内蔵RAM上に転送できてい<br>るかの判定結果です。<br>0:内蔵プログラムのダウンロードは正常終了(エラーなし)<br>1:内蔵プログラムのダウンロードが異常終了(エラーが発生している)               |

フラッシュキーコードレジスタ(FKEY)

アドレス:H'FFFFC8

| ビット | ビット名 | 初期値 | R/W | 説明                                                                      |

|-----|------|-----|-----|-------------------------------------------------------------------------|

| 7   | K7   | 0   | R/W | キーコード                                                                   |

| 6   | K6   | 0   | R/W | H'A5を書き込んだ場合にのみ、SCOビットの書き込みが有効になります。H'A5以外の値がFKEYに書かれている場合、SCOビットに1を書き込 |

| 5   | K5   | 0   | R/W | むことができないため、内蔵RAMへのダウンロードができません。また、                                      |

| 4   | K4   | 0   | R/W | H' 5Aを書き込んだ場合のみ、書き込み/消去が可能になります。内蔵の書き込み/消去プログラムを実行しても、H' 5A以外の値がFKEYレジ  |

| 3   | K3   | 0   | R/W | スタに書かれている場合はフラッシュメモリの書き込み/消去はできませ                                       |

| 2   | K2   | 0   | R/W | ん。<br>H'A5:SCOビットの書き込みを許可します。(H'A5以外ではSCOビット                            |

| 1   | K1   | 0   | R/W | のセットはできません)                                                             |

| 0   | К0   | 0   | R/W | H' 5A:書き込み/消去を許可します。(H' 5A以外ではソフトウェアプロテクト状態)<br>H' 00:初期値               |

#### フラッシュコードコントロール・ステータスレジスタ(FCCS)

アドレス:H'FFFFC4

| ビット | ビット名 | 初期値 | R/W   | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | SCO  | 0   | (R)/W | ソースプログラムコピーオペレーション 内蔵書き込み/消去プログラムを内蔵RAMにダウンロードする要求ビットです。本ビットに1を書き込むと、FPCS/FECSレジスタで選択した内蔵プログラムが、FTDARレジスタで指定された内蔵RAMの領域に自動的にダウンロードされます。本ビットに1を書き込むためには、FKEYへのH'A5の書き込み、および内蔵RAM上での実行が必要です。本ビットに1を書き込んだ直後には、4個のNOP命令を必ず実行するようにしてください。なお、ダウンロード完了時点では本ビットは0クリアされているため、本ビットの1状態を読み出すことはできません。ダウンロード中は、すべての割り込みを禁止する必要があります。ユーザのシステム上で割り込みが入らないようにしてください。  0:内蔵されている書き込み/消去プログラムの内蔵RAMへのダウンロードは行いません 「クリア条件」ダウンロードが完了するとクリアされます。 1:内蔵されている書き込み/消去プログラムの内蔵RAMへのダウンロードリクエストを発生します。 「セット条件」以下の条件がすべて満足されている状態で、1を書き込んだとき (1) FKEYにH'A5が書かれていること (2) 内蔵RAM 上で実行中であること |

## フラッシュプログラム/イレーズ周波数パラメータ(FPEFEQ: CPU の汎用レジスタ ER0)

| ビット   | ビット名     | 初期値 | R/W | 説明                                                                                                                                                                                                                                                                         |

|-------|----------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31~16 | FUBE15~0 | I   | R/W | フラッシュユーザブランチイネーブルビット<br>ユーザブランチ機能を有効にするときは、H'AA55に設定してください。<br>それ以外はH'0000に設定してください。                                                                                                                                                                                       |

| 15~0  | F15∼F0   |     | R/W | 周波数設定ビット CPUの動作周波数を設定します。設定値は以下のように算出してください。 ・MHz単位で表現した動作周波数を小数点第3位で四捨五入し、小数点第2位までとする。 ・100倍した値を2進数に変換し、FPEFEQパラメータ(汎用レジスタERO)に書き込む。 具体例として、CPUの動作周波数が35.000MHzの場合には、以下のようになります。 ・35.00の小数点第3位を四捨五入し、35.00 ・35.00×100 = 3500を2進数変換し、B'0000 1101 1010 1100 (H'0DAC)をROに設定。 |

## フラッシュユーザブランチアドレス設定パラメータ(FUBRA: CPU の汎用レジスタ ER1)

| ビット  | ビット名         | 初期値 | R/W | 説明                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|--------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31~0 | UA31~<br>UA0 | -   | R/W | ユーザブランチ先は、内蔵プログラムが転送されているRAM領域以外のRAM空間または外部バス空間としてください。<br>実行コードのない領域にブランチして暴走しないように注意し、内蔵プログラムのダウンロード領域やスタック領域を破壊しないようにしてください。暴走やダウンロード領域/スタック領域の破壊が発生した場合、フラッシュメモリの値の保証もできません。ユーザブランチ先の処理では、内蔵プログラムのダウンロード、初期化、書き込み/消去プログラムを起動しないでください。ユーザブランチ先から復帰時の書き込み/消去の保証ができません。また、すでに準備していた書き込みデータを書き換えないでください。さらに、ユーザブランチ先の処理で書き込み/消去インタフェースレジスタの書き換えを行わないでください。ユーザブランチ処理終了後は、RTS命令で書き込み/消去プログラムに戻ってください。 |

## フラッシュパス/フェイルパラメータ(FPFR: CPU の汎用レジスタ ROL)

#### 初期化結果の戻り値です。

| ビット | ビット名 | 初期値 | R/W | 説明                                                                                                                                      |

|-----|------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------|

| 7~3 | -    | -   | -   | 未使用ビット<br>値 0 が戻されます。                                                                                                                   |

| 2   | BR   | -   | R/W | ユーザブランチエラー検出ビット<br>指定されたユーザブランチ先アドレスが、ダウンロードされている書き込み/消去関係プログラムの格納領域以外であるかをチェックした結果を戻します。<br>0:ユーザブランチアドレス設定は正常値<br>1:ユーザブランチアドレス設定が異常値 |

| 1   | FQ   | -   | R/W | 周波数エラー検出ビット<br>指定されたCPU動作周波数が、サポートしている動作周波数の範囲にあるかをチェックした結果を戻します。<br>0:動作周波数の設定は正常値<br>1:動作周波数の設定が異常値                                   |

| 0   | SF   | -   | R/W | サクセス/フェイルビット<br>初期化が正常に終了したかどうかを戻すビットです。<br>0:初期化は正常終了(エラーなし)<br>1:初期化が異常終了(エラーが発生している)                                                 |

## フラッシュパス/フェイルパラメータ(FPFR: CPU の汎用レジスタ ROL)

## 消去処理結果の戻り値です。

| ビット | ビット名 | 初期値 | R/W | 説明                                                                                                                                                                                                                                                                                                                                                          |

|-----|------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | -    | -   | -   | 未使用ビット<br>値 0 が戻されます。                                                                                                                                                                                                                                                                                                                                       |

| 6   | MD   | -   | R/W | 消去モード関連設定エラー検出ビット<br>エラープロテクト状態でないことのチェック結果を返します。エラープロテクト状態になっている場合、1が書き込まれます。これらの状態は、FCCSのFLERで確認できます。<br>0:FLER状態は正常(FLER = 0)<br>1:FLER = 1 であり、消去できない状態                                                                                                                                                                                                 |

| 5   | EE   | -   | R/W | 消去実行時エラー検出ビット<br>ユーザマットの消去ができなかったり、ユーザブランチ処理から戻った時<br>点でフラッシュ関連レジスタの一部が書き換えられている場合に、本ビッ<br>トには1が返されます。これらが原因で、本ビットが1になった場合、ユー<br>ザマットは途中まで消去されている可能性が高いため、エラーになる原<br>因を取り除いた後、再度消去を実施し直してください。また、FMATSレジ<br>スタの値がH'AAとなっており、ユーザブートマット選択状態のときに消去<br>を実施しても、消去実行時エラーとなります。この場合は、ユーザマット/<br>ユーザブートマットともに、消去されてはいません。ユーザブートマットの<br>消去はブートモードまたはライタモードで実施してください。 |

## フラッシュパス/フェイルパラメータ(FPFR: CPU の汎用レジスタ ROL)

#### 消去処理結果の戻り値です。

| ビット | ビット名 | 初期値 | R/W | 説明                                                                                                                   |

|-----|------|-----|-----|----------------------------------------------------------------------------------------------------------------------|

| 4   | FK   | -   | R/W | フラッシュキーレジスタエラー検出ビット<br>消去処理開始前にFKEYの値をチェックした結果を戻します。<br>0:FKEYの設定は正常(FKEY = H'5A)<br>1:FKEYの設定値エラー(FKEY は、H'5A 以外の値) |

| 3   | EB   | -   | R/W | イレーズブロックセレクトエラー検出ビット<br>指定された消去ブロック番号が、ユーザマットのブロック範囲内であるかのチェック結果です。<br>0:消去ブロック番号の設定は正常値<br>1:消去ブロック番号の設定が異常値        |

| 2   | -    | _   | _   | 未使用ビット                                                                                                               |

| 1   | -    | -   | -   | 値 0 が戻されます。                                                                                                          |

| 0   | SF   | _   | R/W | サクセス/フェイルビット<br>消去処理が正常に終了したかどうかを戻すビットです。<br>0:消去は正常終了(エラーなし)<br>1:消去が異常終了(エラーが発生している)                               |

## フラッシュイレーズブロックセレクトパラメータ(FEBS: CPU の汎用レジスタ ERO)

| ビット  | ビット名   | 初期値 | R/W | 説明                                                                                  |

|------|--------|-----|-----|-------------------------------------------------------------------------------------|

| 31~8 | -      | -   | _   | 未使用ビット                                                                              |

|      |        |     |     | 値0を設定してください。                                                                        |

| 7~0  | EBN7∼0 | -   | R/W | イレーズブロック番号                                                                          |

|      |        |     |     | 0~15 の範囲で消去ブロック番号を設定します。                                                            |

|      |        |     |     | EBO ブロックを選択するときは H'00 を、EB15 ブロックを選択するときは H'0F を設定してください。H'00~H'0F 以外の設定ではエラーになります。 |

## 5.6.4 flash\_prog 関数

## 表 5.15 flash\_prog 関数の機能説明

| 機能                                            | 戻り値 | 引数 |

|-----------------------------------------------|-----|----|

| ・書き込み処理で使用するシンボルの設定値チェック                      | なし  | なし |

| ・ユーザプログラムモードへの遷移(FLSHE = 1)                   |     |    |

| ・書き込みプログラムのダウンロード処理                           |     |    |

| ・フラッシュメモリの初期化処理                               |     |    |

| ・IIC2_0 によるスレーブ受信処理                           |     |    |

| ・フラッシュメモリの書き込み処理                              |     |    |

| <ul><li>・フラッシュメモリに書き込んだデータのコンペアチェック</li></ul> |     |    |

| ・フラッシュメモリの書き込み終了処理                            |     |    |

| ・各処理のエラーチェック                                  |     |    |

## 【使用レジスタ】(flash\_erase 関数内でも使用している同じレジスタは省略しています)

フラッシュプログラムコードセレクトレジスタ(FPCS)

アドレス:H'FFFFC5

| ビット | ビット名 | 初期値 | R/W | 説明                       |

|-----|------|-----|-----|--------------------------|

| 0   | PPVS | 0   | R/W | プログラムパルスベリファイ            |

|     |      |     |     | 書き込みプログラムを選択します。         |

|     |      |     |     | 0:内蔵の書き込みプログラムを選択しません。   |

|     |      |     |     | [クリア条件] 転送が終了するとクリアされます。 |

|     |      |     |     | 1:内蔵の書き込みプログラムを選択します。    |

## フラッシュマルチパーパスアドレスエリアパラメータ(FMPAR: CPU の汎用レジスタ ER1)

| ビット  | ビット名               | 初期値 | R/W | 説明                                                                                                                                 |

|------|--------------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------|

| 31~0 | MOA31<br>~<br>MOA0 | -   | R/W | ユーザマット上の書き込み先の先頭アドレスを格納します。ここで指定されたユーザマットの先頭アドレスから連続128バイトの書き込みが行われます。<br>よって、指定する書き込み先の先頭アドレスは128バイト境界となり、<br>MOA6~MOA0は常に0になります。 |

#### フラッシュマルチパーパスデータデスティネーションパラメータ(FMPDR: CPU の汎用レジスタ ERO)

| ビット  | ビット名  | 初期値 | R/W | 説明                                  |

|------|-------|-----|-----|-------------------------------------|

| 31~0 | MOD31 | -   | R/W | ユーザマットへの書き込みデータが格納されている領域の先頭アドレス    |

|      | ~     |     |     | を格納します。ここで指定された先頭アドレスから連続128バイトのデータ |

|      | MOD0  |     |     | が、ユーザマットに対して書き込まれます。                |

フラッシュパス/フェイルパラメータ(FPFR: CPU の汎用レジスタ ROL)

書き込み処理結果の戻り値です。

| ビット | ビット名 | 初期値 | R/W | 説明                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | -    | _   | -   | 未使用ビット<br>値 0 が戻されます。                                                                                                                                                                                                                                                                                                                                                                              |

| 6   | MD   | -   | R/W | 書き込みモード関連設定エラー検出ビット<br>エラープロテクト状態でないことのチェック結果を返します。エラープロテクト状態になっている場合、1が書き込まれます。これらの状態は、FCCSのFLERビットで確認できます。<br>0:FLER状態は正常(FLER = 0)<br>1:FLER = 1 であり、書き込みできない状態                                                                                                                                                                                                                                 |

| 5   | EE   | -   | R/W | 書き込み実行時エラー検出ビット ユーザマットが消去されていないために、指定データを書き込めなかったり、ユーザブランチ処理から戻った時点でフラッシュ関連レジスタの一部が書き換えられている場合に、本ビットには1が返されます。これらが原因で、本ビットが1になった場合、ユーザマットは途中まで書き換えられている可能性が高いため、エラーになる原因を取り除いた後、消去から実施し直してくだい。また、FMATS レジスタの値がH 'AAとなっており、ユーザブートマット選択状態のときに書き込みを実施しても、書き込み実行時エラーとなります。この場合は、ユーザマット/ユーザブートマットともに、書き換えられてはいません。ユーザブートマットの書き込みはブートモードまたはライタモードで実施してください。  0:書き込み処理は正常終了  1:書き込み処理が異常終了し、書き込み結果は保証できない |

| 4   | FK   | -   | R/W | フラッシュキーレジスタエラー検出ビット<br>書き込み処理開始前にFKEY の値をチェックした結果を戻します。<br>0:FKEYの設定は正常(FKEY = H'5A)<br>1:FKEY の設定値エラー(FKEY は、H'5A 以外の値)                                                                                                                                                                                                                                                                           |

| 3   | -    | _   | R/W | 未使用ビット<br>値 0 が戻されます。                                                                                                                                                                                                                                                                                                                                                                              |

| 2   | WD   | -   | R/W | ライトデータアドレス検出ビット<br>書き込みデータの格納先の先頭アドレスとして、フラッシュメモリ領域のアドレスが指定された場合にはエラーとなります。<br>0:書き込みデータアドレス設定は正常値<br>1:書き込みデータアドレス設定が異常値                                                                                                                                                                                                                                                                          |

| 1   | WA   | -   | R/W | ライトアドレスエラー検出ビット<br>書き込み先先頭アドレスとして、以下が指定された場合にはエラーとなります。<br>・フラッシュメモリの領域外が書き込み先アドレスとして指定された場合<br>・指定されたアドレスが128バイト境界でない(A6~A0が0でない)場合<br>0:書き込み先アドレス設定は正常値<br>1:書き込み先アドレス設定が異常値                                                                                                                                                                                                                     |

| 0   | SF   | -   | R/W | サクセス/フェイルビット<br>書き込み処理が正常に終了したかどうかを戻すビットです。<br>0:書き込みは正常終了(エラーなし)<br>1:書き込みが異常終了(エラーが発生している)                                                                                                                                                                                                                                                                                                       |

# 5.7 H8S\_iic\_sr.c 関数の機能説明

本章では、H8S\_iic\_sr.c ファイル内の関数について機能と使用レジスタを説明します。

## 5.7.1 iic\_sr\_128 関数

#### 表 5.16 iic\_sr\_128 関数の機能説明

| 機能                          | 戻り値 | 引数 |

|-----------------------------|-----|----|

| ・IIC2_0 初期化関数(iic_init)のコール | なし  | なし |

| ・IIC2_0 によるスレーブ受信を開始        |     |    |

## 【使用レジスタ】

なし

# 5.7.2 iic\_init 関数

## 表 5.17 iic\_init 関数の機能説明

| 機能           | 戻り値 | 引数 |

|--------------|-----|----|

| ·IIC2_0 の初期化 | なし  | なし |

## 【使用レジスタ】

IIC バスコントロールレジスタ A\_0(ICCRA\_0)

アドレス:H'FFFD58

| ビット | ビット名 | 初期値 | R/W | 説明                                         |

|-----|------|-----|-----|--------------------------------------------|

| 7   | ICE  | 0   | R/W | IIC バスインタフェースイネーブル                         |

|     |      |     |     | 0: 本モジュールは機能停止状態                           |

|     |      |     |     | 1:本モジュールは転送動作可能状態(SCL/SDA はバス駆動状態)         |

| 6   | RCVD | 0   | R/W | 受信ディスエーブル                                  |

|     |      |     |     | TRS = 0の状態でICDRRをリードしたときに次の動作の継続/禁止を設定します。 |

|     |      |     |     | 0:次の受信動作を継続                                |

|     |      |     |     | 1:次の受信動作を禁止                                |

## IIC バスコントロールレジスタ A\_0(ICCRA\_0)

アドレス:H'FFFD58

| ビット | ビット名 | 初期値 | R/W | 説明                                                                                                                                                                                                                                                                            |

|-----|------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | MST  | 0   | R/W | マスタ/スレーブ選択                                                                                                                                                                                                                                                                    |

| 4   | TRS  | 0   | R/W | 送信/受信選択<br>マスタモードでバス競合負けをすると、MST、TRS共にハードウェアによっ<br>てリセットされてスレーブ受信モードに変わります。なおTRSの変更は転<br>送フレーム間で行ってください。また、スレーブ受信モードで開始条件後<br>の7ビットがSARに設定したスレーブアドレスと一致し、8ビット目が1の場<br>合、TRSが自動的に1にセットされます。<br>MSTとTRSとの組み合わせにより、以下の動作モードになります。<br>00:スレーブ受信モード<br>01:スレーブ送信モード<br>10:マスタ受信モード |

| 3   |      | 0   | R/W | 転送クロック選択3~0                                                                                                                                                                                                                                                                   |

| 2   |      | 0   | R/W | マスタモードのとき、必要な転送レート(表5.18参照)にあわせて設定してください。スレーブモードでは、送信モード時のデータセットアップ時間の                                                                                                                                                                                                        |

| 1   |      | 0   | R/W | 確保に使用されます。この時間はCKS3 = 0のとき10Tcyc、CKS3 = 1のと                                                                                                                                                                                                                                   |

| 0   |      | 0   | R/W | き20Tcycとなります。                                                                                                                                                                                                                                                                 |

表 5.18 転送レート

| ビット3 | ビット2 | ビット1 | ビットロ | クロック  |          |          |          | 転送レート    |          |          |                     |

|------|------|------|------|-------|----------|----------|----------|----------|----------|----------|---------------------|

| CKS3 | CKS2 | CKS1 | CKS0 |       | $\phi =$            |

|      |      |      |      |       | 8MHz     | 10MHz    | 20MHz    | 25MHz    | 33MHz    | 34MHz*1  | 35MHz* <sup>2</sup> |

| 0    | 0    | 0    | 0    | φ/28  | 286kHz   | 357kHz   | 714kHz   | 893kHz   | 1179kHz  | 1214kHz  | 1250kHz             |

|      |      |      | 1    | φ/40  | 200kHz   | 250kHz   | 500kHz   | 625kHz   | 825kHz   | 850kHz   | 875kHz              |

|      |      | 1    | 0    | φ/48  | 167kHz   | 208kHz   | 417kHz   | 521kHz   | 688kHz   | 708kHz   | 729kHz              |

|      |      |      | 1    | φ/64  | 125kHz   | 156kHz   | 313kHz   | 391kHz   | 516kHz   | 531kHz   | 547kHz              |

|      | 1    | 0    | 0    | φ/168 | 47.6kHz  | 59.5kHz  | 119kHz   | 149kHz   | 196kHz   | 202kHz   | 208kHz              |

|      |      |      | 1    | φ/100 | 80.0kHz  | 100kHz   | 200kHz   | 250kHz   | 330kHz   | 340kHz   | 350kHz              |

|      |      | 1    | 0    | φ/112 | 71.4kHz  | 89.3kHz  | 179kHz   | 223kHz   | 295kHz   | 304kHz   | 313kHz              |

|      |      |      | 1    | φ/128 | 62.5kHz  | 78.1kHz  | 156kHz   | 195kHz   | 258kHz   | 266kHz   | 273kHz              |

| 1    | 0    | 0    | 0    | φ/56  | 143kHz   | 179kHz   | 357kHz   | 446kHz   | 589kHz   | 607kHz   | 625kHz              |

|      |      |      | 1    | φ/80  | 100kHz   | 125kHz   | 250kHz   | 313kHz   | 413kHz   | 425kHz   | 438kHz              |

|      |      | 1    | 0    | φ/96  | 83.3kHz  | 104kHz   | 208kHz   | 260kHz   | 344kHz   | 354kHz   | 365kHz              |

|      |      |      | 1    | φ/128 | 62.5kHz  | 78.1kHz  | 156kHz   | 195kHz   | 258kHz   | 266kHz   | 273kHz              |

|      | 1    | 0    | 0    | φ/336 | 23.8kHz  | 29.8kHz  | 59.5kHz  | 74.4kHz  | 98.2kHz  | 101kHz   | 104kHz              |

|      |      |      | 1    | φ/200 | 40.0kHz  | 50.0kHz  | 100kHz   | 125kHz   | 165kHz   | 170kHz   | 175kHz              |

|      |      | 1    | 0    | φ/224 | 35.7kHz  | 44.6kHz  | 89.3kHz  | 112kHz   | 147kHz   | 152kHz   | 156kHz              |

|      |      |      | 1    | φ/256 | 31.3kHz  | 39.1kHz  | 78.1kHz  | 97.7kHz  | 129kHz   | 133kHz   | 137kHz              |

%1. H8S/2378 0.18  $\mu$  m F-ZTAT グループ、H8S/2378R 0.18  $\mu$  m F-ZTAT グループのみサポートしています。

※2. H8S/2378 のみサポートしています。

## スレーブアドレスレジスタ\_0(SAR\_0)

アドレス:H'FFFD5D

| ビット | ビット名   | 初期値 | R/W | 説明                                    |

|-----|--------|-----|-----|---------------------------------------|

| 7~1 | SVA6~0 | 0   | R/W | スレーブアドレス 6~0                          |

|     |        |     |     | IIC バスにつながる他のスレーブと異なるユニークなアドレスを設定します。 |

| 0   | _      | 0   | R/W | リザーブビット                               |

|     |        |     |     | リード/ライト可能ですが、必ず 0 をライトしてください。         |

## IIC バスインタラプトイネーブルレジスタ\_0(ICIER\_0)

アドレス:H'FFFD5B

| ビット | ビット名  | 初期値 | R/W | 説明                                                                                                                                                                                               |

|-----|-------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TIE   | 0   | R/W | トランスミットインタラプトイネーブル<br>ICSRのTDREがセットされたとき、送信データエンプティ割り込み(TXI)を<br>許可/禁止します。<br>0:送信データエンプティ割り込み要求(TXI)の禁止<br>1:送信データエンプティ割り込み要求(TXI)の許可                                                           |

| 6   | TEIE  | 0   | R/W | トランスミットエンドインタラプトイネーブル<br>TEIEは、ICSRのTDREが1の状態で9クロック目が立ち上がったとき、送信<br>終了割り込み(TEI)の許可/禁止を選択します。なおTEIは、TENDを0にク<br>リアするか、TEIEを0にクリアすることで解除できます。<br>0:送信終了割り込み要求(TEI)の禁止<br>1:送信終了割り込み要求(TEI)の許可      |

| 5   | RIE   | 0   | R/W | レシーブインタラプトイネーブル RIEは受信データがICDRSからICDRRに転送され、ICSRのRDRFが1に セットされたとき、受信データフル割り込み要求(RXI)の許可/禁止を選択 します。なおRXIは、RDRFを0にクリアするか、またはRIEを0にクリアする ことで解除できます。 0:受信データフル割り込み要求(RXI)の禁止 1:受信データフル割り込み要求(RXI)の許可 |

| 4   | NAKIE | 0   | R/W | NACK 受信インタラプトイネーブル NAKIEは、ICSRのNACKFおよびALがセットされたとき、NACK受信割り込み要求(NAKI)の許可/禁止を選択します。なおNAKIは、NACKFまたはALを0にクリアするか、またはNAKIEを0にクリアすることで解除できます。0:NACK 受信割り込み要求(NAKI)の禁止1:NACK 受信割り込み要求(NAKI)の許可         |

| 3   | STIE  | 0   | R/W | 停止条件検出インタラプトイネーブル<br>0:停止条件検出割り込み要求(STPI)の禁止<br>1:停止条件検出割り込み要求(STPI)の許可                                                                                                                          |

| 2   | ACKE  | 0   | R/W | アクノリッジビット判定選択<br>0:受信アクノリッジの内容を無視して連続的に転送を行う。<br>1:受信アクノリッジが 1 の場合、転送を中断する。                                                                                                                      |

| 1   | ACKBR | 0   | R   | 受信アクノリッジ<br>送信モード時、受信デバイスから受け取ったアクノリッジビットの内容を格納しておくビットです。ライトは無効です。<br>0: 受信アクノリッジ = 0<br>1: 受信アクノリッジ = 1                                                                                         |

## IIC バスインタラプトイネーブルレジスタ\_0(ICIER\_0)

アドレス:H'FFFD5B

| ビット | ビット名  | 初期値 | R/W | 説明                                                                                           |

|-----|-------|-----|-----|----------------------------------------------------------------------------------------------|

| 0   | ACKBT | 0   | R/W | 送信アクノリッジ<br>受信モード時、アクノリッジのタイミングで送出するビットを設定します。<br>0:アクノリッジのタイミングで0を送出<br>1:アクノリッジのタイミングで1を送出 |

## IIC バスステータスレジスタ\_0(ICSR\_0)

アドレス:H'FFFD5C

| ビット | ビット名  | 初期値 | R/W | 説明                                                                                                                                                                                |

|-----|-------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TDRE  | 0   | R/W | トランスミットデータエンプティ [セット条件] ・ICDRTからICDRSにデータ転送が行われ、ICDRTがエンプティになった とき ・TRSをセットしたとき ・開始条件(再送含む)を発行したとき ・スレーブモードで受信モードから送信モードになったとき [クリア条件] ・1の状態をリードした後、0をライトしたとき ・ICDRT ヘデータをライトしたとき |

| 6   | TEND  | 0   | R/W | トランスミットエンド [セット条件] ・TDREが1の状態でSCLの9クロック目が立ち上がったとき [クリア条件] ・1の状態をリードした後、0をライトしたとき ・ICDRT ヘデータをライトしたとき                                                                              |

| 5   | RDRF  | 0   | R/W | レシーブデータレジスタフル<br>[セット条件]<br>・ICDRSからICDRRに受信データが転送されたとき<br>[クリア条件]<br>・1の状態をリードした後、0をライトしたとき<br>・ICDRR をリードしたとき                                                                   |

| 4   | NACKF | 0   | R/W | ノーアクノリッジ検出フラグ [セット条件] ・ICIERのACKE = 1の状態で、送信時、受信デバイスからアクノリッジがなかったとき [クリア条件] ・1 の状態をリードした後、0 をライトしたとき                                                                              |

| 3   | STOP  | 0   | R/W | 停止条件検出フラグ [セット条件] ・マスタモード時、フレームの転送の完了後に停止条件を検出したとき ・スレーブモード時、ゼネラルコール後および開始条件検出後の第1バイトのスレーブアドレスとSARに設定したアドレスが一致した後、停止条件を検出したとき [クリア条件] ・1 の状態をリードした後、0 をライトしたとき                    |

## IIC バスステータスレジスタ\_0(ICSR\_0)

アドレス:H'FFFD5C

| ビット | ビット名 | 初期値 | R/W | 説明                                                                                                                                                                                                                                                                               |

|-----|------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | AL   | 0   | R/W | アービトレーションロストフラグ ALは、マスタモード時にバス競合負けをしたことを示します。 複数のマスタがほぼ同時にバスを占有しようとしたときにIICバスインタ フェースはSDAをモニタし、自分が出したデータと異なった場合、ALフラグ を1にセットしてバスが他のマスタによって占有されたことを示します。 [セット条件] ・マスタ送信モードの場合、SCLの立ち上がりで内部SDAとSDA端子のレベルが不一致のとき ・マスタモードの場合、開始条件検出時、SDA端子がハイレベルのとき [クリア条件] ・1 の状態をリードした後、0 をライトしたとき |

| 1   | AAS  | 0   | R/W | スレーブアドレス認識フラグ スレーブ受信モードで開始条件直後の第1フレームがSARのSVA6~ SVA0と一致した場合にセットされます。 [セット条件] ・スレーブ受信モードでスレーブアドレスを検出したとき ・スレーブ受信モードでゼネラルコールアドレスを検出したとき [クリア条件] ・1 の状態をリードした後、0 をライトしたとき                                                                                                           |

| 0   | ADZ  | 0   | R/W | ゼネラルコールアドレス認識フラグ<br>スレーブ受信モードのとき有効<br>[セット条件]<br>・スレーブ受信モードかつゼネラルコールアドレスを検出したとき<br>[クリア条件]<br>・1 の状態をリードした後、0 をライトしたとき                                                                                                                                                           |

# 5.7.3 iici0\_int 関数

表 5.19 iici0\_int 関数の機能説明

| 機能                                                                      | 戻り値 | 引数 |

|-------------------------------------------------------------------------|-----|----|

| ・割り込み例外処理ベクタ IICIO(ベクタ番号 116)を使用した<br>IIC2_0 の割り込み処理                    | なし  | なし |

| ・IIC2_0 の割り込み処理中に停止条件を検出時に停止処理関数 (receive_stop_condition)をコール           |     |    |

| ・lic2_0 の割り込み処理中に IIC_マスタ送信側からデータが送信された場合にスレーブ受信処理関数(slave_receive)をコール |     |    |

## 【使用レジスタ】

iic\_init 関数内で使用している ICSR\_0 の STOP ビット、ICCRA\_0 の TRS ビットを使用しているため詳細は省略。

# 5.7.4 receive\_stop\_condition 関数

#### 表 5.20 receive\_stop\_condition 関数の機能説明

| 機能                                                                 | 戻り値 | 引数 |

|--------------------------------------------------------------------|-----|----|

| ・IIC2_0 割り込み処理で停止条件を検出した場合(ICSR_0 の<br>STOP ビットが 1)にコールされ、停止処理を行う。 | なし  | なし |

#### 【使用レジスタ】

iic\_init 関数内で使用している ICSR\_0、ICCRA\_0、ICIER\_0 を使用しているため詳細は省略。

## 5.7.5 slave\_receive 関数

#### 表 5.21 slave\_receive 関数の機能説明

| 機能                                                         | 戻り値 | 引数 |

|------------------------------------------------------------|-----|----|

| ・IIC2_0 割り込み処理で IIC_マスタ送信側からデータが送信された場合にコールされ、スレーブ受信処理を行う。 | なし  | なし |

## 【使用レジスタ】

IIC バスインタラプトイネーブルレジスタ\_0(ICIER\_0)

アドレス:H'FFFD5B

| ビット | ビット名  | 初期値 | R/W | 説明                                                                                           |

|-----|-------|-----|-----|----------------------------------------------------------------------------------------------|

| 0   | ACKBT | 0   | R/W | 送信アクノリッジ<br>受信モード時、アクノリッジのタイミングで送出するビットを設定します。<br>0:アクノリッジのタイミングで0を送出<br>1:アクノリッジのタイミングで1を送出 |

# IIC バス受信データレジスタ\_0(ICDRR\_0)

アドレス:H'FFFD5F

| ビット | ビット名  | 初期値 | R/W | 説明                                                                                                                            |

|-----|-------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------|

| 7~0 | ICDRR | FF  | R   | 受信データを格納する 8 ビットのレジスタです。1 バイトのデータの受信が終了すると、受信したデータを ICDRS から ICDRR へ転送し、次のデータを受信可能にします。なお ICDRR は受信専用レジスタですので、CPU からライトできません。 |

# 5.8 メモリマップ

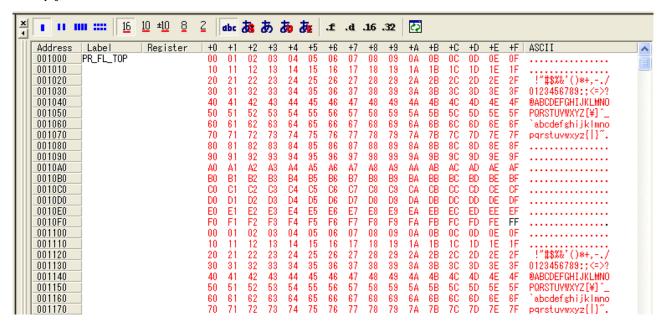

図 5.2 にフラッシュメモリ(0.18  $\mu$  m F-ZTAT 版)、図 5.3 に内蔵 RAM のアドレスマップを示します。

| H'000000                   |                                                                             | H'000000                 |                                                                              |

|----------------------------|-----------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------|

|                            | プログラム領域(EB0ブロック)(※1)                                                        | H'0001DC                 | ベクタ領域(\$VECT0~\$VECT118)                                                     |

| H'001000                   |                                                                             | H'000400                 |                                                                              |

|                            |                                                                             | H'0004C4                 | リセット・割込み領域(PResetPRG、PIntPRG)(※2)                                            |

|                            |                                                                             | H'000800                 |                                                                              |

|                            |                                                                             | H'0008B2                 | Main関数、RAM転送プログラム領域(セクション"P")                                                |

|                            |                                                                             |                          | IIC、フラッシュメモリ書き込み/消去開始プログラム、<br>データ領域<br>(セクション"PROMPRG"、"C\$DSEC"、"C\$BSEC") |

|                            |                                                                             | H'000DC4                 |                                                                              |

|                            |                                                                             |                          |                                                                              |

|                            |                                                                             | \ H'000FFF               |                                                                              |

|                            | データ書き込み領域<br>(EB1~EB15ブロック)                                                 |                          |                                                                              |

|                            |                                                                             |                          |                                                                              |

|                            |                                                                             |                          |                                                                              |

|                            |                                                                             |                          |                                                                              |

|                            |                                                                             |                          |                                                                              |

|                            |                                                                             |                          |                                                                              |

|                            |                                                                             |                          |                                                                              |

| H'07FFFF                   |                                                                             |                          |                                                                              |

| ※1. H'00000<br>※2. H'00040 | 10番地〜H'000FFFまではプログラム領域の為、データの書<br>24番地〜H'0004C5番地はセクション"PFiniPRG"(finiprg関 | 書き込み/消去は行れ<br> 数領域)が配置され | っないでください。<br>ています。                                                           |

図 5.2 フラッシュメモリ(0.18  $\mu$  m F-ZTAT 版)アドレスマップ

| H'FF4000             | データ領域(セクション"B")                |          |

|----------------------|--------------------------------|----------|

| H'FF4007             |                                | †        |

|                      |                                |          |

| H'FF5000             |                                |          |

| H'FF54FE             | 転送後プログラム領域(セクション"PRAMPRG")(※1) |          |

|                      |                                | <u> </u> |

|                      |                                |          |

|                      |                                |          |

|                      |                                |          |

|                      |                                |          |

|                      |                                |          |

|                      |                                |          |

|                      |                                |          |

|                      |                                |          |

|                      |                                |          |

| H'FF8000             |                                | -        |

|                      |                                |          |

|                      | フラッシュメモリ書き込みデータ格納領域(※2)        |          |

|                      |                                |          |

| H'FF9000             |                                |          |

|                      | フラッシュメモリ消去プログラム領域              |          |

|                      | (H8S内蔵プログラム)                   |          |

| H'FFA000             |                                |          |

|                      |                                |          |

|                      | フラッシュメモリ書き込みプログラム領域            |          |

|                      | (H8S内蔵プログラム)                   |          |

| H'FFB000<br>H'FFB024 | エラーフラグ領域(※3)                   | <br> -   |

| 1111 0024            | -/ /// BK%\\\\\                | 1        |

|                      |                                |          |

| H'FFBE00             |                                |          |

| H'FFBFFF             | スタック領域(セクション"S")               | 1        |

図 5.3 内蔵 RAM アドレスマップ

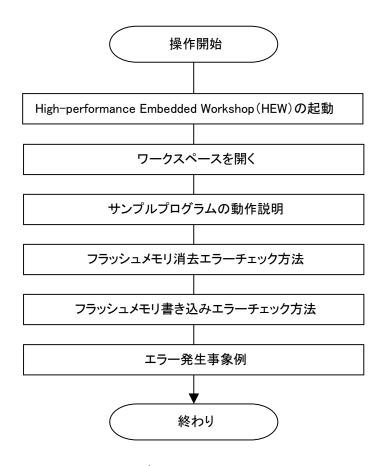

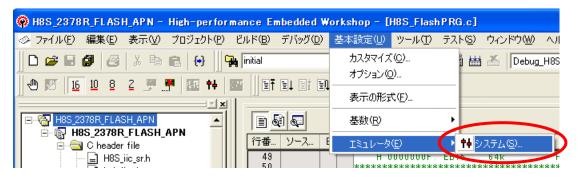

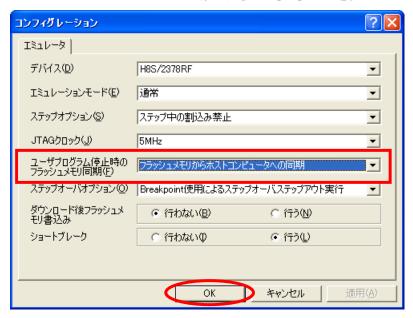

### 6. 動作説明

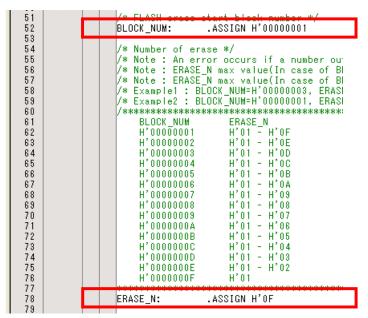

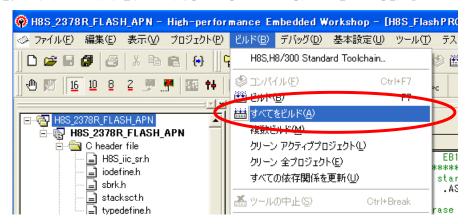

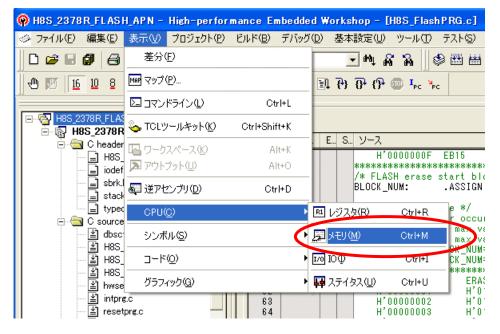

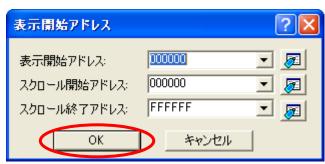

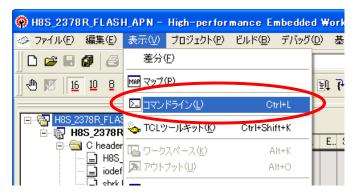

本章では、High-performance Embedded Workshop (HEW)を起動し、サンプルプログラムを使ってフラッシュメモリ (0.18μm F-ZTAT 版)の書き込み/消去を行った場合に、正常に書き込み/消去が行なえているか確認する方法を 説明します。説明順序としては以下のようになります。

図 6.1 本アプリケーションノートの説明順序

#### High-performance Embedded Workshop (HEW)の起動

まず、始めにユーザシステムを接続したE10A-USBエミュレータとホストコンピュータをUSBケーブルで接続し、デ バッグ操作が可能であることを確認してください。

次にHigh-performance Embedded Workshopを起動します。

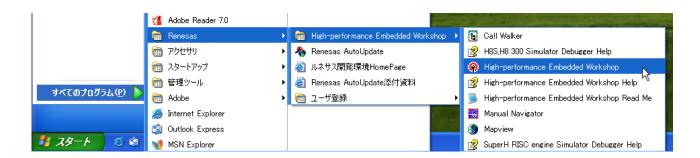

[スタート]メニューの[すべてのプログラム]から[Renesas]→[High-performance Embedded Workshop]→

[High-performance Embedded Workshop]で起動できます。

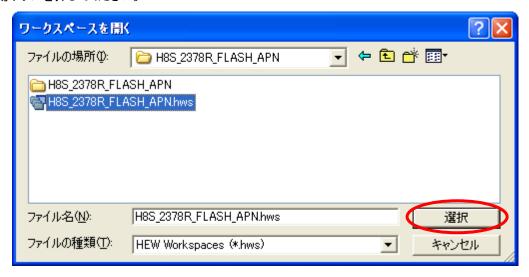

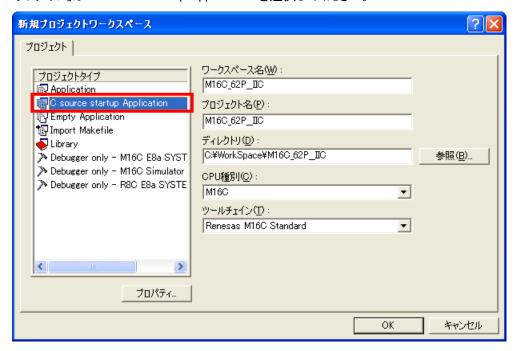

## 6.2 ワークスペースを開く

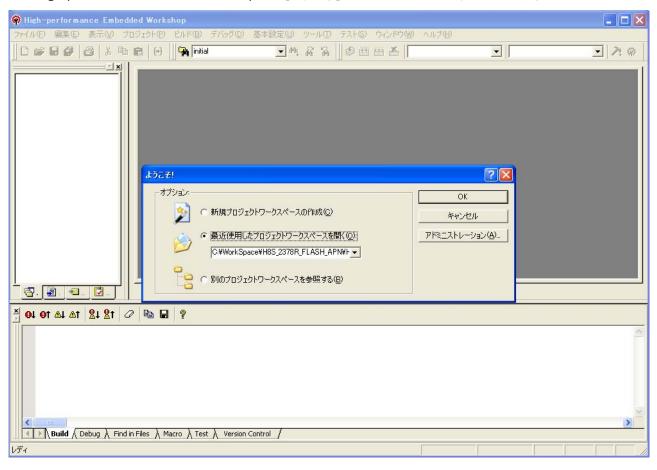

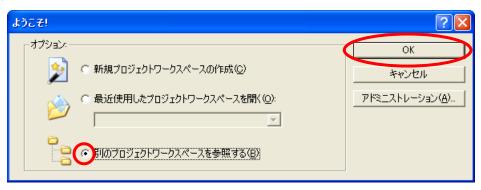

(1) High-performance Embedded Workshop 上に[ようこそ!]ダイアログボックスが表示されます。

[ようこそ!]ダイアログボックス内の[別のプロジェクトワークスペースを参照する]ラジオボタンを選択して[OK]ボタンを 押してください。

(2) [ワークスペースを開く]ダイアログボックスが表示されます。ファイル"H8S\_2378R\_FLASH\_APN.hws"を指定して [選択]ボタンを押してください。

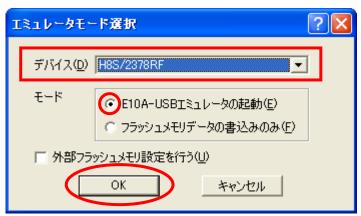

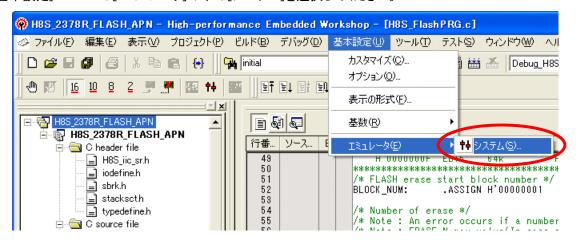

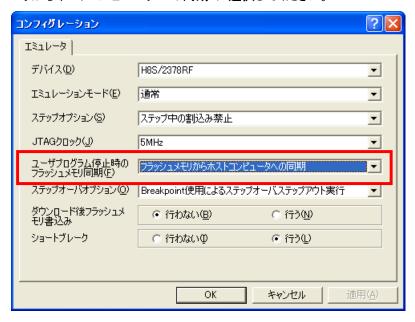

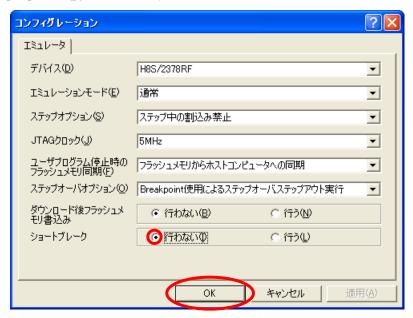

(3) [エミュレータモード選択]ダイアログボックスが表示されるので、[デバイス]欄を"H8S/2378RF"、[モード]欄を "E10A-USB エミュレータの起動"に選択して[OK]ボタンを押してください。

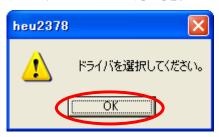

(4) 初回のみ[heu2378]ダイアログボックスが表示されるので、[OK]を押してください。

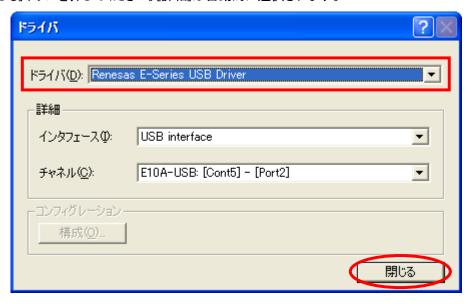

(5) 初回のみ[ドライバ]ダイアログボックスが表示されるので、[ドライバ]欄を"Renesas E-Series USB Driver"に選択して[閉じる]ボタンを押してください。[詳細]は自動的に選択されます。

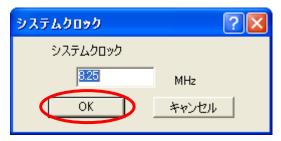

(6) [システムクロック]ダイアログボックスが表示されるので、外部クロック周波数の値を入力して[OK]ボタンを押してください。今回は、本書で使用しているボード"HSB8S2378RE"の外部クロック周波数"8.25MHz"を入力します。

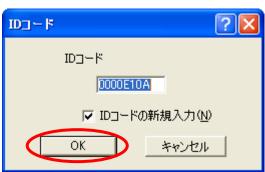

(7) [ID コード]ダイアログボックスが表示されるので、デフォルトのまま変更せずに[OK]ボタンを押してください。

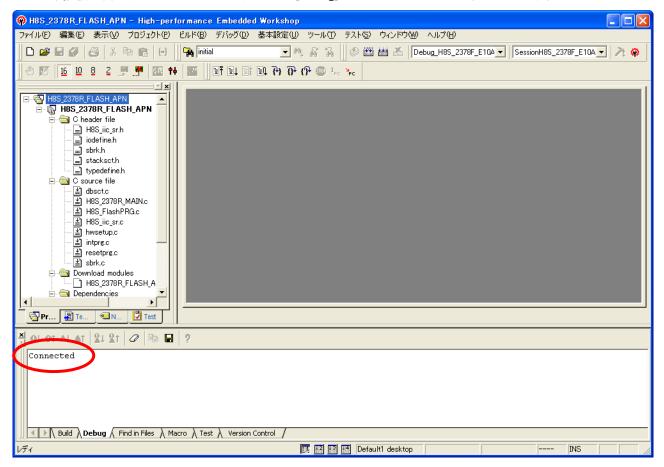

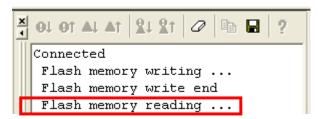

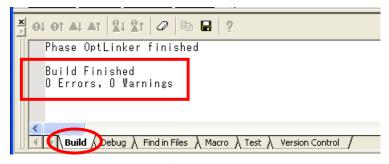

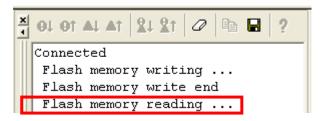

(8) E10A-USB エミュレータの接続が完了して High-performance Embedded Workshop の画面が操作可能になります。接続が完了するとアウトプットウィンドウの[Debug]タブ上に"Connected"と表示されます。

- (9) 本サンプルプログラムを動作させる前に以下の変更がされているか確認してください。

- •H8S, H8/300 Standard Toolchain のコンパイラ、セクション設定変更

- ・割り込みプログラムファイル(intprg.c)の内容変更

#### 【H8S, H8/300 Standard Toolchain の変更箇所】

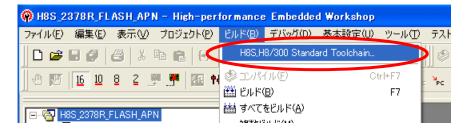

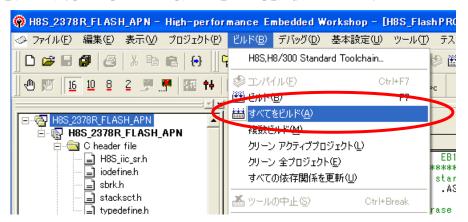

[ビルド]メニューの[H8S, H8/300 Standard Toolchain..]を選択してください。

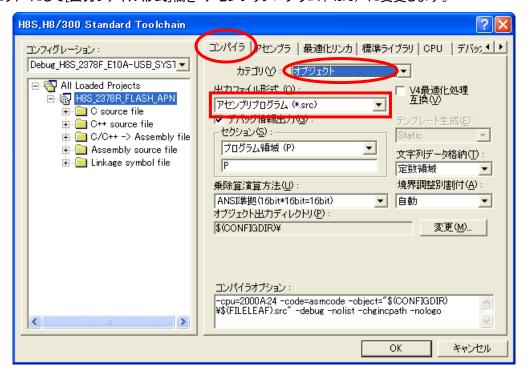

[H8S, H8/300 Standard Toolchain]ダイアログボックスが表示されるので、[コンパイラ]タブの[カテゴリ]欄を"オブジェクト"にして[出力ファイル形式]欄を"アセンブリプログラム(\*.src)"に変更します。

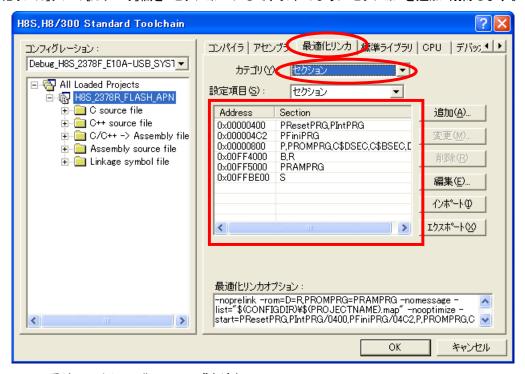

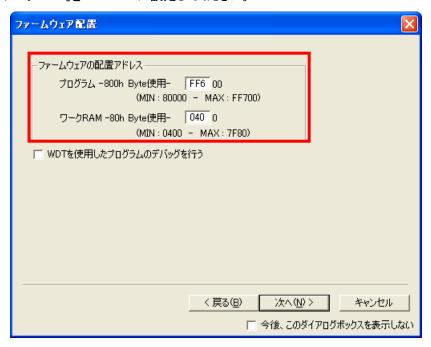

[最適化リンカ]タブの[カテゴリ]欄を"セクション"にして、以下のようにセクションを追加・削除します。

- •0x000004C2 番地にセクション"PFiniPRG"を追加。

- ・0x00000800 番地のセクション"C"を削除して、セクション"P"の次にセクション"PROMPRG"を追加。

- •0x00FF5000 番地にセクション"PRAMPRG"を追加。

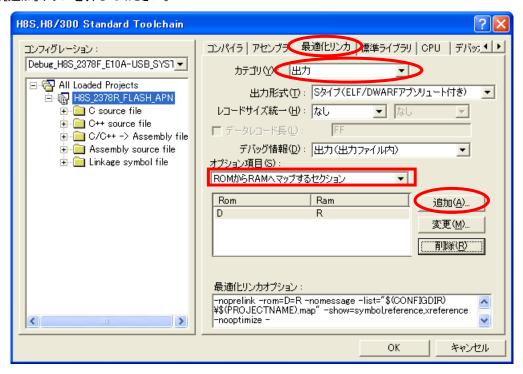

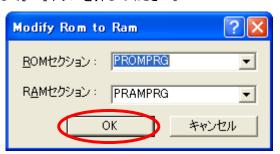

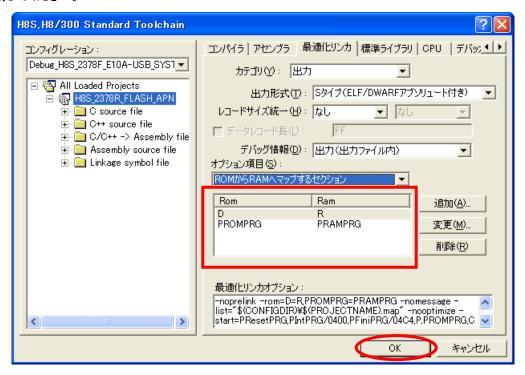

[最適化リンカ]タブの[カテゴリ]欄を"出力"にし、[オプション項目]欄を"ROM から RAM ヘマップするセクション" にして[追加]ボタンを押してください。

[Modify Rom to Ram]ダイアログボックスが表示されるので、[ROM セクション]欄に"PROMPRG"、[RAM セクション]欄に"PRAMPRG"を入力して[OK]ボタンを押してください。

以下のように表示され、フラッシュメモリ領域にあるセクション"PROMPRG"が、内蔵 RAM 領域にセクション "PRAMPRG"としてマッピングされます。[OK]ボタンを押して[H8S, H8/300 Standard Toolchain]ダイアログボック スを閉じてください。

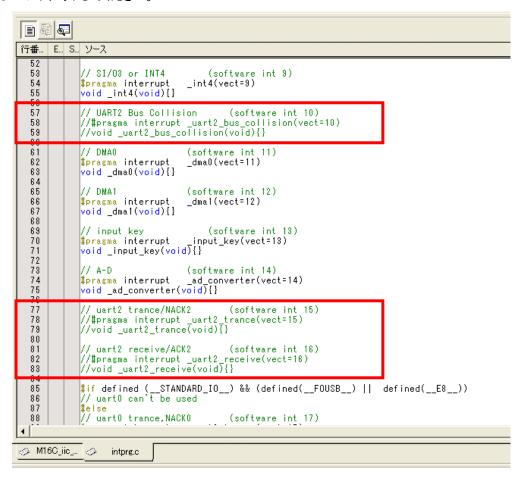

### 【割り込みプログラムファイル(intprg.c)の変更箇所】

"vector 116 IICIO"は IIC2\_0 スレーブ受信プログラムファイル(H8S\_iic\_sr.c)内で使用しているため、コメントアウトにしてください。

```

247

// vector 115 Reserved

248

249

vector 116 IICIO

interrupt(vect=116) void INT IICIO(void) {/* sleep(); */}

250

// vector 117 Reserved

251

252

253

// vector 118 IICI1

_interrupt(vect=118)    void INT_IICI1(void) {/* sleep(); */}

254

255

|√/ vector 119 Reserved

256

// vector 120 Reserved

257

258

```

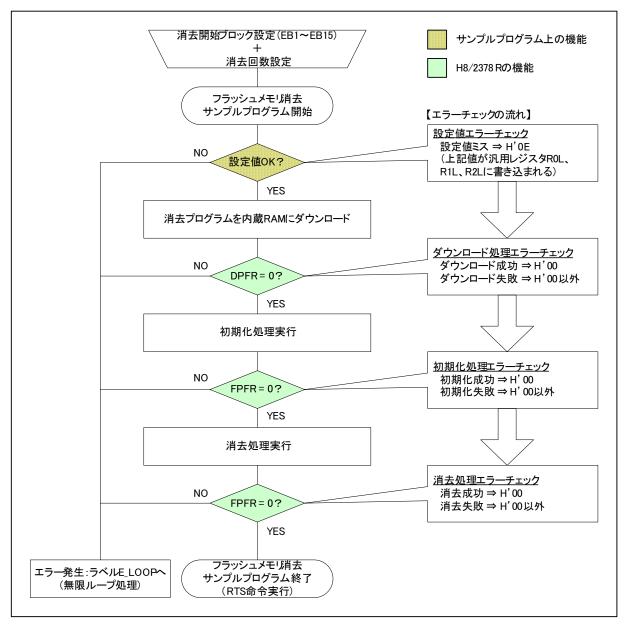

### 6.3 サンプルプログラムの動作説明

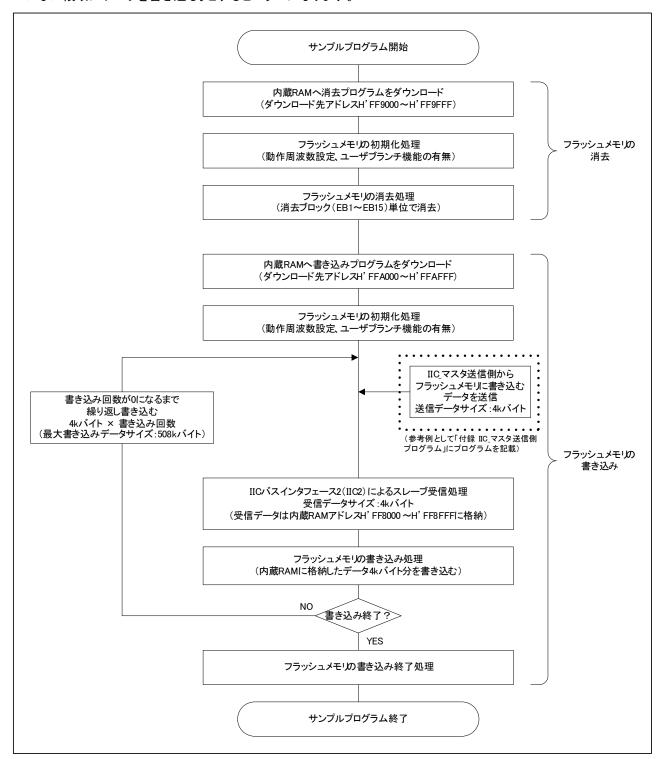

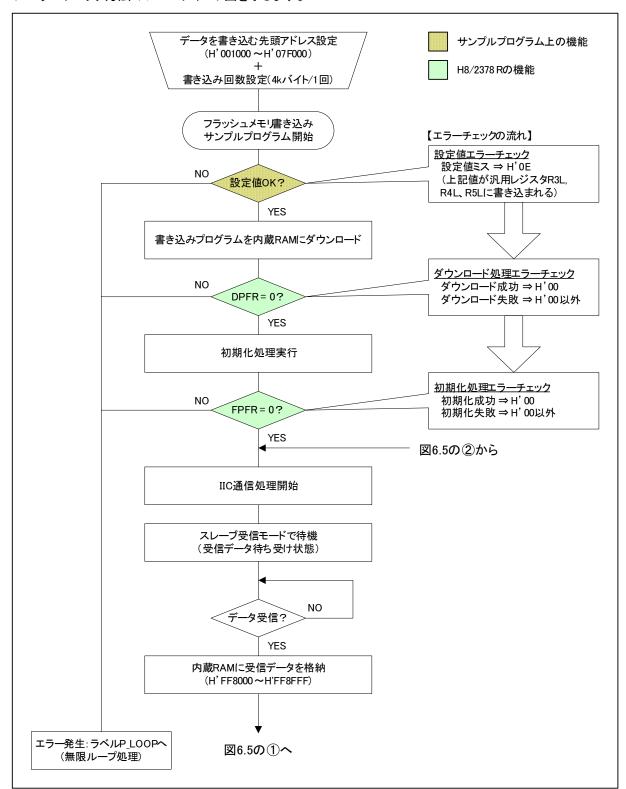

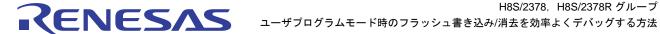

本章では、サンプルプログラムの下記一連の動作について説明します。図6.2にサンプルプログラムの流れを示し ます。

- フラッシュメモリの消去

- フラッシュメモリの書き込み

なお、フラッシュメモリの書き込みを行う場合は、書き込む領域を必ず消去してから実行してください。消去されて いない領域にデータを書き込もうとするとエラーになります。

図 6.2 サンプルプログラムの流れ

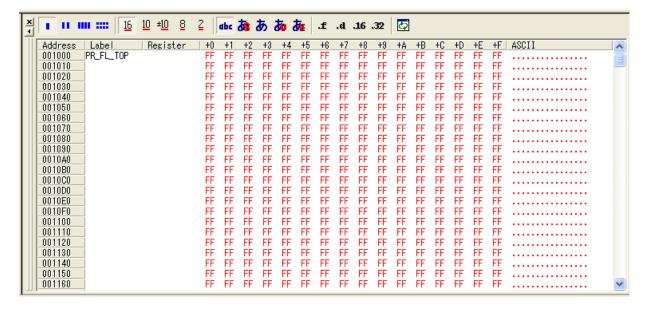

### 6.3.1 フラッシュメモリの消去

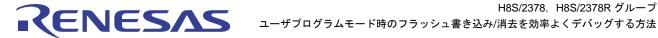

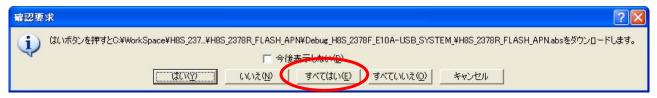

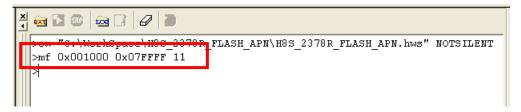

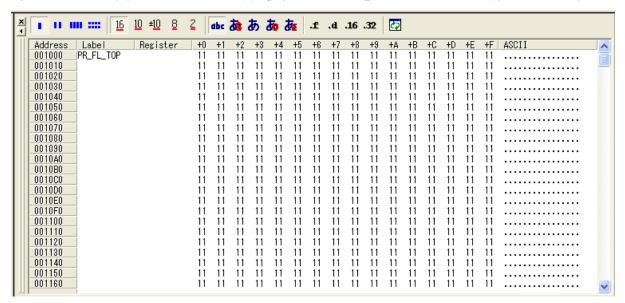

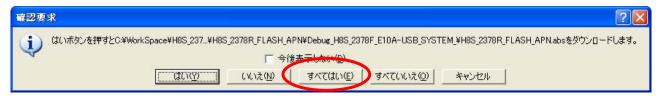

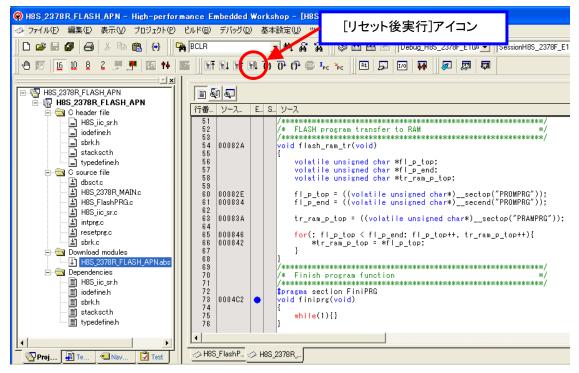

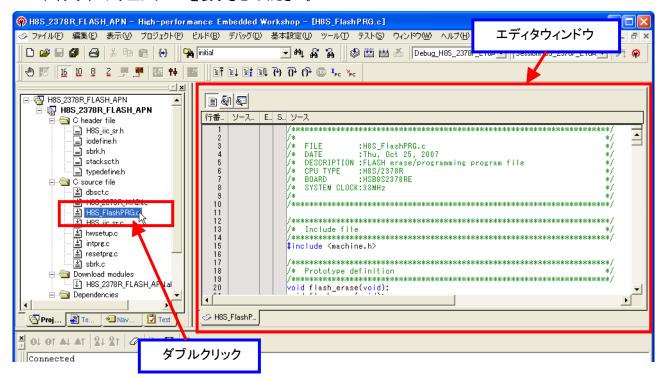

(1) 最初にワークスペースウィンドウ上の[Download modules]フォルダ内のファイル"H8S\_2378R\_FLASH\_APN.abs -00000000"をダブルクリックして、サンプルプログラムをダウンロードしてください。

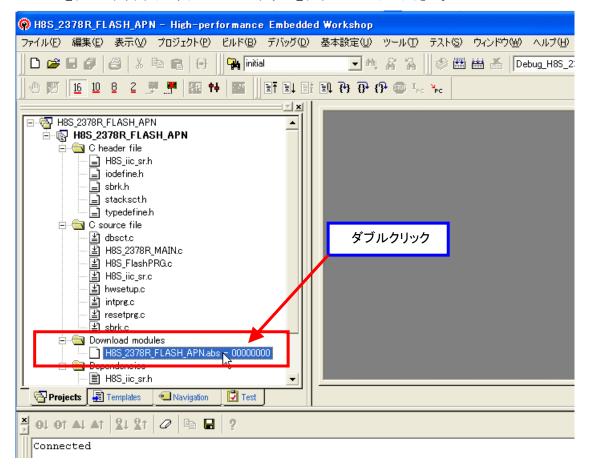

ダウンロードが終了すると以下のように下矢印が表示されます。

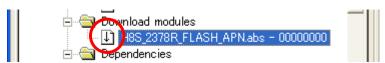

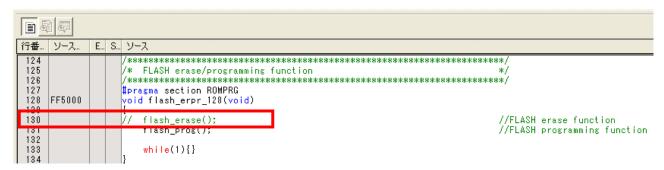

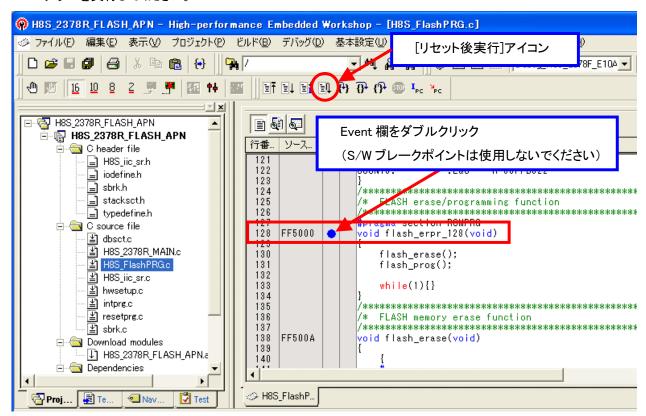

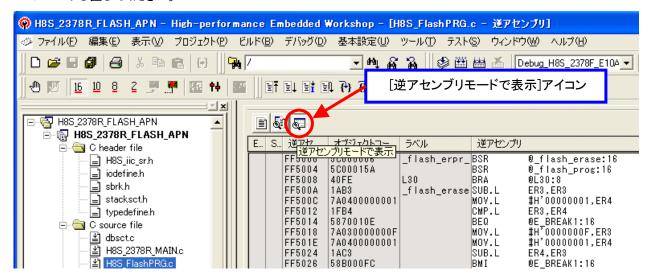

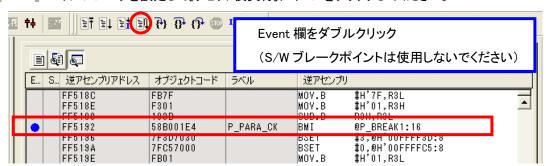

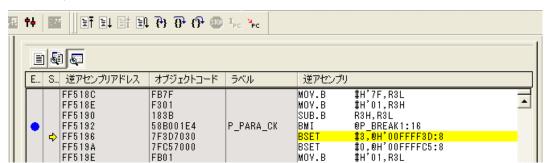

(2) ワークスペースウィンドウ上の[C source file]フォルダ内のファイル"H8S\_FlashPRG.c"をダブルクリックして、エディタウィンドウ上にソースを表示させてください。

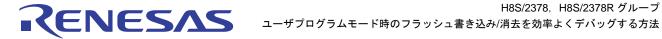

(3) フラッシュメモリの消去を行う上で必要なパラメータ"BLOCK\_NUM(消去開始ブロック番号)"、"ERASE\_N(消去 回数)"の設定を行います。各パラメータは、"H8S\_FlashPRG.c"ファイル内の"flash\_symbol"関数内にあります。

```

行番... ソース...

E... S... ソース

23

24

/x Asemble symbols definition

25

#pragma inline_asm(flash_symbol)

27

void flash_symbol(void)

28

29

000832

30

3.1

32

33

BLOCK_NUM

Block

Size(byte)

H'00000-H'000FFF

H'001000-H'001FFF

H'002000-H'002FFF

H'003000-H'003FFF

H'004000-H'004FFF

H'00000000

34

EB0

4k

H'00000001

35

4k

EB1

H'00000002

36

H'00000003

37

EB3

4k

H'00000004

38

FR4

4k

H'005000-H'005FFF

H'006000-H'006FFF

H'007000-H'007FFF

H'00000005

39

EB5

40

H'00000006

H'00000007

41

42

FR7

4k

H'007000-H'007FFF

H'008000-H'00FFFF

H'010000-H'01FFFF

H'020000-H'02FFFF

H'080000-H'03FFFF

H'040000-H'05FFFF

H'050000-H'05FFFFF

H'00000008

32k

43

H'000000009

EB9

44

H'0000000A

EB10

64k

45

H'OOOOOOR

FR11

844

46

H'0000000C

EB12

64k

47

64k

H'0000000D

48

H'0000000F

FR14

844

H'070000-H'07FFFF

49

H'0000000F

FB15

64k

50

51

/* FLASH erase start block number

52

53

BLOCK_NUM:

.ASSIGN H'00000001

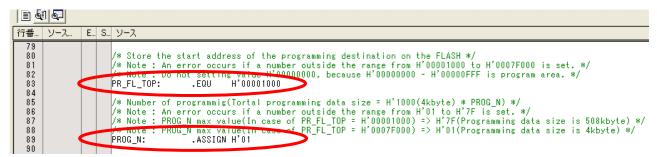

```

BLOCK\_NUM は、消去を開始するブロック番号(アドレス)を設定するパラメータで、設定範囲は "H'00000001 ~H'0000000F"です。設定範囲以外の値を設定してサンプルプログラムを実行するとエラーが発生します。また、サンプルプログラムではブロック EBO の範囲をプログラム領域として使用しているため消去できない仕様となっています。

表 6.1 に BLOCK\_NUM の詳細を示します。

#### 表 6.1 BLOCK\_NUM パラメータについて

| BLOCK_NUM の設定値 | 消去開始ブロック | メモリ容量   | 消去開始アドレス  |

|----------------|----------|---------|-----------|

| H' 0000001     | EB1      | 4k バイト  | H' 001000 |

| H' 00000002    | EB2      | 4k バイト  | H' 002000 |

| H' 00000003    | EB3      | 4k バイト  | H' 003000 |

| H' 0000004     | EB4      | 4k バイト  | H' 004000 |

| H' 0000005     | EB5      | 4k バイト  | H' 005000 |

| H' 0000006     | EB6      | 4k バイト  | H' 006000 |

| H' 0000007     | EB7      | 4k バイト  | H' 007000 |

| H' 00000008    | EB8      | 32k バイト | H' 008000 |

| H' 00000009    | EB9      | 64k バイト | H' 010000 |

| H' 0000000A    | EB10     | 64k バイト | H' 020000 |

| H' 0000000B    | EB11     | 64k バイト | H' 030000 |

| H' 000000C     | EB12     | 64k バイト | H' 040000 |

| H' 000000D     | EB13     | 64k バイト | H' 050000 |

| H' 0000000E    | EB14     | 64k バイト | H' 060000 |

| H'000000F      | EB15     | 64k バイト | H' 070000 |

```

行番... ソース...

E... S... ソース

50

51

52

53

54

55

/* FLASH erase start block number */

BLOCK_NUM:

.ASSIGN H'00000001

/* Number of erase */

/* Note : An error occurs if a number outside the range from H'01 to H'0F is set. */

/* Note : ERASE_N max value(In case of BLOCK_NUM = H'00000001) => H'0F */

/* Note : ERASE_N max value(In case of BLOCK_NUM = H'0000000F) => H'01 */

/* Example1 : BLOCK_NUM=H'00000003, ERASE_N=H'04 => EB3 - EB6 block area erase. */

/* Example2 : BLOCK_NUM=H'00000001, ERASE_N=H'0F => All area(EB1 - EB15 block) erase. */

56

57

58

59

60

ERASE_N

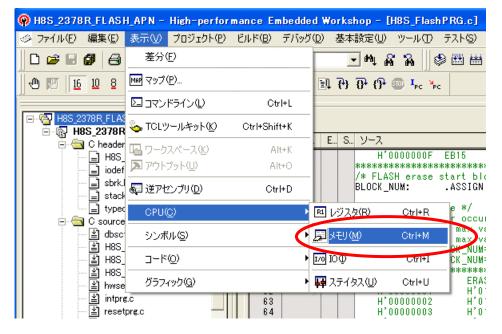

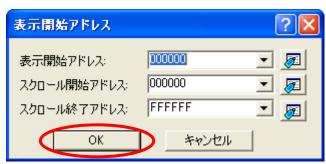

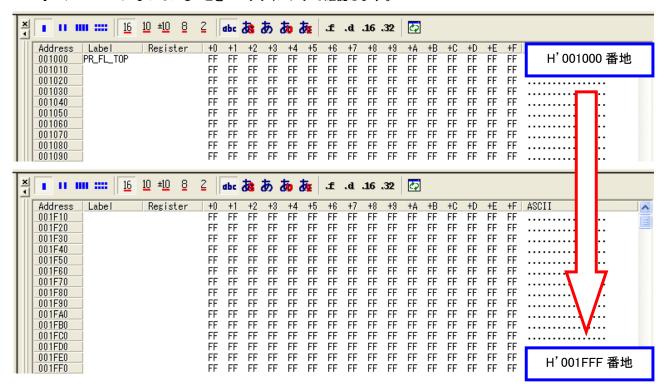

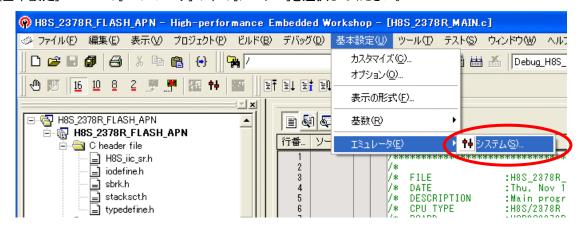

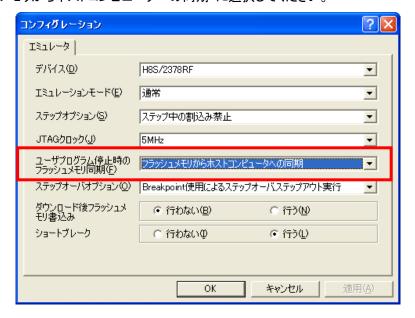

H'01 - H'0F