# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# H8/38602R グループ

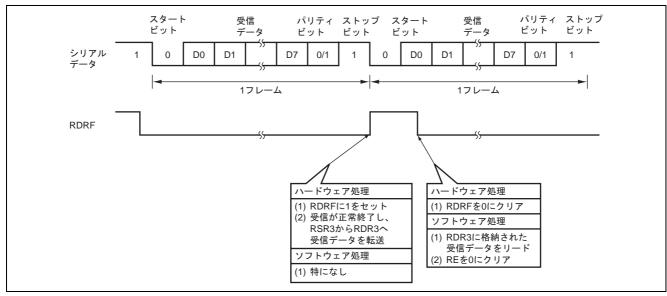

調歩同期式シリアル通信 (38.4kHz 動作時, 2400bit/s)

## 要旨

サブアクティブモードに遷移し,調歩同期式シリアル通信を行います。サブクロック周波数に 38.4kHz を使用し、ビットレートを 2400bit/s とし,4 バイトのデータ送信,および受信を行います。

## 動作確認デバイス

H8/38602R

## 目次

| 1. | 仕様       | 2    |

|----|----------|------|

| 2. | 使用機能説明   | 3    |

| 3. | 動作説明     | 7    |

| 4. | ソフトウェア説明 | 8    |

| 5. | フローチャート  | . 15 |

## 1. 仕様

- サブアクティブモードに遷移し,動作周波数をサブクロック(38.4kHz)に設定します。

- 4 バイトのデータの送信, および受信を行います。

- 本タスク例の通信フォーマットは,データ長8ビット,ストップビット長1ビットです。

- ビットレートは 2400bit/s です。

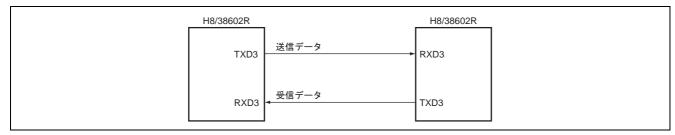

図1 調歩同期式シリアル通信

#### 2. 使用機能説明

## 2.1 使用機能

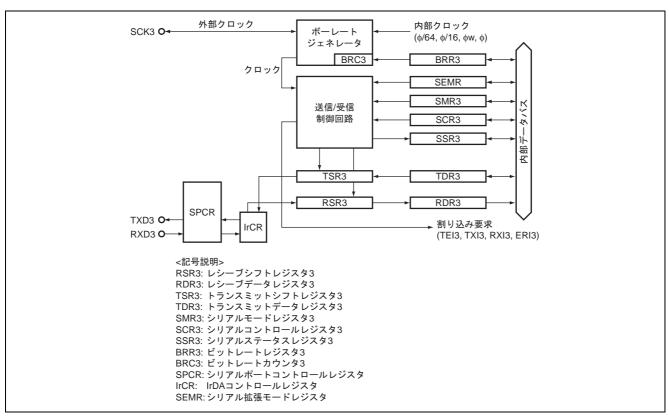

本タスク例では, SCI3 (Serial Communication Interface 3) を用いて,調歩同期式シリアル通信を行います。 図 2 に SCI3 ブロック図を示し,以下に本タスクで使用する機能説明をします。

#### 2.1.1 SCI3 モジュール

H8/38602R マイコンにより 4 バイトのデータを 2400bit/s のビットレートで送受信します。

- 動作周波数

- 本タスク例では,サブアクティブモードに遷移し,サブクロック38.4kHzで動作します。

- 調歩同期式モード

- キャラクタ単位で同期をとる調歩同期方式で,シリアル通信をします。Universal Asynchronous Receiver/Transmitter (UART) や,Asynchronous Communication Interface Adapter (ACIA) などの標準の調歩同期式通信用 LSI とのシリアルデータ通信ができます。

- 内部クロックφw

内蔵周辺機能を動作させるための基準クロックであり、クロック発振器により生成されます。

図2 SCI3のブロック図

- シリアルポートコントロールレジスタ (SPCR) TXD3 端子機能の切り換えを行います。

- シリアルモードレジスタ 3 (SMR3)

シリアルデータ通信フォーマットの設定と,内蔵ボーレートジェネレータのクロックソースを選択するための 8 ビットのレジスタです。

- ビットレートレジスタ 3 (BRR3) ビットレートを調整するための 8 ビットのレジスタです。SCI3 は ,チャネルごとにボーレートジェネレー タが独立しているため , それぞれ異なるビットレートを設定可能です。設定値 ,実行レートの関係等 ,詳

- 細はハードウェアマニュアルを参照してください。

シリアルコントロールレジスタ 3 (SCR3)

送受信制御と割り込み制御,および送受信クロックソースの選択を行うためのレジスタです。

- トランスミットデータレジスタ3 (TDR3)

送信データを格納する8 ビットのレジスタです。TSR3 に空きを検出すると, TDR3 にライトしたデータは自動的に TSR3 に転送され,シリアルデータ送信を開始します。また,TDR3 と TSR3 はダブルバッファ構造ですので,1 フレーム分のデータを送信したときに,TDR3 に次のデータがライトされていると TSR3へと転送され,連続送信が可能です。TDR3 は常に CPU からのリード/ライトが可能ですが,ライトはシリアルステータスレジスタ (SSR3) の TDRE ビットが1であることを確認して行ってください。

- シリアルステータスレジスタ 3 (SSR3) SCI3 のステータスフラグと,送受信マルチプロセッサビットで構成されています。TDRE, RDRF, OER, FER, PER はクリアのみ可能です。

- レシーブデータレジスタ 3 (RDR3) 受信したシリアルデータを格納する 8 ビットのレジスタです。1 フレーム分のデータを受信すると,自動的に RSR3 からデータが転送されます。RSR3 と RDR3 はダブルバッファ構造ですので,連続受信動作が可能です。RDR3 は,受信専用レジスタのため,CPU からのリードのみ可能です。

- レシーブシフトレジスタ 3 (RSR3)

シリアルデータを受信するためのレジスタです。RSR3 に RXD3 端子から入力されたシリアルデータを , LSB (ビット 0) から受信した順にセットし , パラレルデータに変換します。1 フレーム分のデータを受信 すると , データは自動的にレシープデータレジスタ (RDR3) へと転送されます。CPU からのアクセスは 行えません。

- トランスミットシフトレジスタ 3 (TSR3)

シリアルデータを送信するためのレジスタです。1 フレーム分のデータを送信すると,トランスミットデータレジスタ (TDR3) から TSR3 へと転送され,TXD3 端子から送信データが出力されます。CPU からのアクセスは行えません。

- シリアル拡張モードレジスタ (SEMR) 調歩同期式モード時の基本クロックの設定を行います。

#### 2.1.2 ウォッチドッグタイマ機能

H8/38602R はウォッチドッグタイマを内蔵しており,リセット後,ウォッチドッグタイマはオンになります。タイマカウンタ WD (TCWD) はカウントアップ動作を行い,TCWD がオーバフローすると H8/38602R 内部をリセットします。本タスク例では,ウォッチドッグタイマ機能を使用しないため,ウォッチドッグタイマ機能を停止させます。

タイマコントロール/ステータスレジスタ WD1 (TCSRWD1)

TCSRWD1 は TCSRWD1 自身と TCWD の書き込み制御を行うレジスタです。また,ウォッチドッグタイマの動作制御と動作状態を示します。本レジスタの書き換えは MOV 命令で行ってください。ビット操作命令では,設定値の変更ができません。

#### 2.1.3 低消費電力モード機能

サブアクティブモードでは,システムクロック発振器が停止し,IIC2以外の内蔵周辺モジュールは動作します。規定の電圧が与えられている限り,一部の内蔵周辺モジュールの内部レジスタ値は保持されます。

サブアクティブモードは ,SLEEP 命令を実行すると解除されます。解除後のモードは ,システムコントロールレジスタ 1 (SYSCR1) の SSBY ビットと LSON ビット , TMA3 ビット , システムコントロールレジスタ 2 (SYSCR2) の MSON ビットと DTON ビットの組み合わせによりサブスリープモード , アクティブモード , ウォッチモードへ遷移します。なお , コンディションコードレジスタ (CCR) の 1 ビットが 1 の場合 , あるいは割り込みイネーブルレジスタにより当該割り込み受け付けが禁止されている場合は , サブアクティブモードは解除されません。

サブアクティブモードの動作周波数は SYSCR2 の SA1, SA0 ビットにより ,ウォッチクロック  $(\phi_w)$  ,ウォッチクロックの 2 分周 , 4 分周 , 8 分周から選択できます。動作周波数は SLEEP 命令実行後 , SLEEP 命令実行前に設定した周波数に切り換わります。

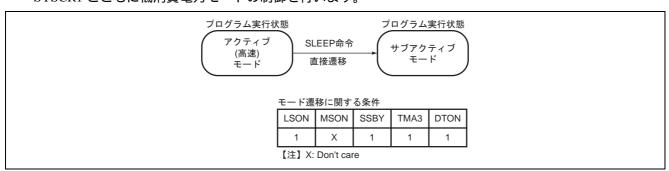

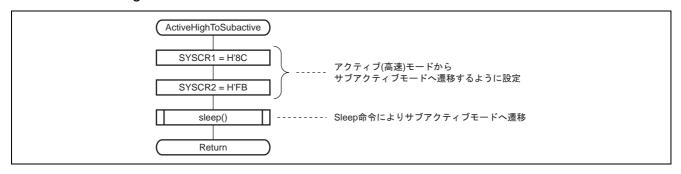

本タスク例では,アクティブ(高速)モードからサブアクティブモードへ直接遷移します。CPU がプログラムを実行している動作モードにはアクティブモードとサブアクティブモードがあります。直接遷移はこの2つの動作モード間で実行を停止することなく遷移します。SYSCR2のDTON ビットを1にセットして SLEEP命令を実行すると直接遷移します。アクティブモード,サブアクティブモードで動作周波数を変更する場合にも有効です。遷移後は直接遷移割り込み例外処理を開始します。CCR の I ビットを 1 の状態で直接遷移を行うとスリープモード,またはウォッチモードに遷移した後,割り込みによる解除ができませんので注意してください。

アクティブ (高速) モードからサブアクティブモードへの直接遷移は,アクティブ (高速) モードで SYSCR1 の SSBY ビットを 1, TMA3 ビットを 1, LSON ビットを 1, SYSCR2 の DTON を 1 にセットした状態で SLEEP 命令を実行すると,ウォッチモードを経由してサブアクティブモードに遷移します。

図3にアクティブ(高速)モードからサブアクティブモードへの直接遷移のブロック図を示します。

- システムコントロールレジスタ 1 (SYSCR1) SYSCR2 とともに低消費電力モードの制御を行います。

- システムコントロールレジスタ 2 (SYSCR2) SYSCR1 とともに低消費電力モードの制御を行います。

図3 アクティブ (高速) モードからサブアクティブモードへの直接遷移

#### 2.1.4 モジュールスタンバイ機能

モジュールスタンバイ機能により , SCI3 はリセット解除後モジュールスタンバイ状態に設定されています。 クロック停止レジスタ 1 (CKSTPR1) の S3CKSTP を 1 に設定することにより ,SCI3 のモジュールスタンバイ 状態を解除します。

◆ クロック停止レジスタ 1 (CKSTPR1)内蔵周辺モジュールをモジュール単位でスタンバイ状態を制御します。

## 2.2 機能割り付け

表 1 に本タスク例の機能割り付けを示します。表 1 に示すように機能を割り付け,サブアクティブモードに遷移し,動作周波数をサブクロック (38.4kHz) に設定します。調歩同期式シリアル通信により,ビットレートは 2400bit/s で 4 バイトの 8 ビットデータの送信,および受信を行います。

表1 機能割り付け

| 機能      | 分類    | 機能割り付け                                       |  |  |  |

|---------|-------|----------------------------------------------|--|--|--|

| SCK3    | 端子    | SCI3 のクロック入出力端子                              |  |  |  |

| TXD3    | 端子    | SCI3 の送信データ出力端子                              |  |  |  |

| RXD3    | 端子    | SCI3 の受信データ入力端子                              |  |  |  |

| SMR3    | SCI3  | 通信フォーマットを調歩同期式モードに設定                         |  |  |  |

|         |       | 内蔵ボーレートジェネレータのクロックソースを <sub>Φw</sub> クロックに設定 |  |  |  |

| BRR3    | SCI3  | 通信のビットレートを 2400bps に設定                       |  |  |  |

| SCR3    | SCI3  | 送信,受信動作許可                                    |  |  |  |

| TDR3    | SCI3  | 送信データを格納するレジスタ                               |  |  |  |

| SSR3    | SCI3  | SCI3 の動作状態を示すステータスフラグ                        |  |  |  |

| RDR3    | SCI3  | 受信データを格納するレジスタ                               |  |  |  |

| RSR3    | SCI3  | シリアルデータを受信するためのレジスタ                          |  |  |  |

| TSR3    | SCI3  | シリアルデータを送信するためのレジスタ                          |  |  |  |

| SPCR    | SCI3  | TXD3 端子機能に設定                                 |  |  |  |

| SEMR    | SCI3  | 調歩同期式モードにおける1ビット期間の基本クロックを転送レートの8倍           |  |  |  |

|         |       | の周波数に設定                                      |  |  |  |

| SYSCR1  | 低消費電力 | SYSCR2 と合わせて,サブアクティブモードへ遷移                   |  |  |  |

| SYSCR2  | 低消費電力 | SYSCR1 と合わせて,サブアクティブモードへ遷移                   |  |  |  |

| CKSTPR1 | 低消費電力 | SCI3 モジュールスタンバイ状態を解除                         |  |  |  |

| TCSRWD1 | WDT   | ウォッチドッグタイマの停止                                |  |  |  |

#### 3. 動作説明

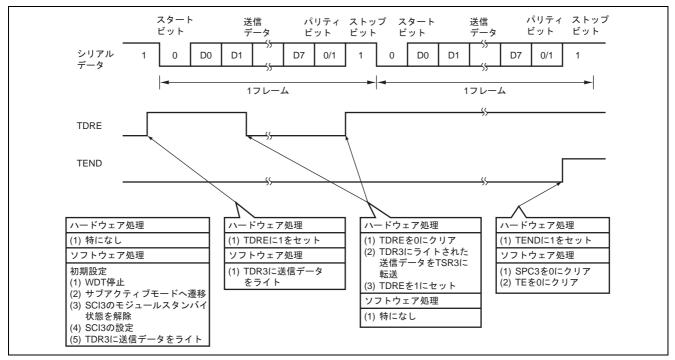

## 3.1 調歩同期式シリアルデータ送信

図 4 に動作説明を示します。図 4 に示すようなハードウェア処理, ソフトウェア処理により調歩同期式シリアル送信を行います。本タスク例では, ビットレートを 2400bit/s に設定します。

図 4 調歩同期式シリアルデータ送信の動作説明

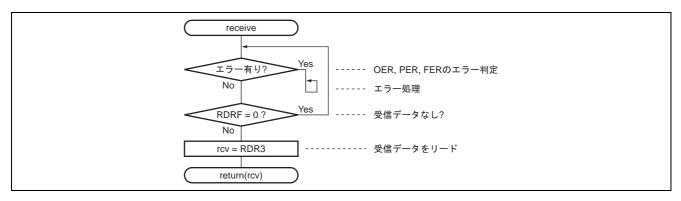

#### 3.2 調歩同期式シリアルデータ受信

図 5 に動作説明を示します。図 5 に示すようなハードウェア処理, ソフトウェア処理により調歩同期式シリアル受信を行います。本タスク例では, ビットレートを 2400bit/s に設定します。

図 5 調歩同期式シリアルデータ受信の動作説明

## 4. ソフトウェア説明

## 4.1 モジュール説明

本タスク例のモジュールを表2に示します。

表2 モジュール説明

| 関数名                   | 機能                                       |

|-----------------------|------------------------------------------|

| main                  | ウォッチドッグタイマの停止 , 使用 RAM 領域の初期化 , 割り込み制御 , |

|                       | 調歩同期式シリアルデータ通信                           |

| SCI3_init             | SCI3 の初期化,SCI3 のモジュールスタンバイ状態を解除          |

| transmit              | シリアルデータ送信                                |

| receive               | シリアルデータ受信                                |

| ActiveHighToSubactive | アクティブ (高速) モードからサブアクティブモードへ遷移            |

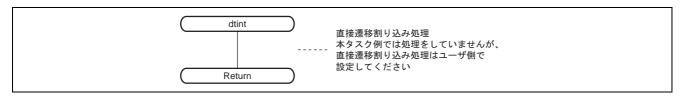

| dtint                 | 直接遷移割り込み処理                               |

## 4.2 引数の説明

表3に本タスク例の引数を示します。

表 3 引数説明

| ラベル名                   | 説明    | 使用関数名    |

|------------------------|-------|----------|

| unsigned char trs_data | 送信データ | transmit |

## 4.3 使用レジスタ説明

以下に,本タスク例で使用する内部レジスタを示します。なお,設定値は本タスク例において使用している値であり,初期値とは異なります。

#### • SPCR シリアルポートコントロールレジスタ アドレス: HFF91

| ビット | ビット名 | 設定値 | R/W | 機能                                                               |

|-----|------|-----|-----|------------------------------------------------------------------|

| 4   | SPC3 | 1   | R/W | P32/TXD3/IrTXD 端子切り換え                                            |

|     |      |     |     | P32/TXD3/IrTXD 端子を P32 端子として使用するか<br>TXD3/IrTXD 端子として使用するか選択します。 |

|     |      |     |     | 1:TXD3/IrTXD 出力端子として使用                                           |

|     |      |     |     | 本ビットを 1 に設定した後に SCR3 の TE ビットを設定してください。                          |

• SMR3 シリアルモードレジスタ 3 アドレス: H'FF98

| ビット | ビット名 | 設定値 | R/W | 機能                                   |

|-----|------|-----|-----|--------------------------------------|

| 7   | COM  | 0   | R/W | コミュニケーションモード                         |

|     |      |     |     | 0:調歩同期式モードで動作します。                    |

|     |      |     |     | 1:クロック同期式モードで動作します。                  |

| 6   | CHR  | 0   | R/W | キャラクタレングス (調歩同期式モードのみ有効)             |

|     |      |     |     | 0:データ長 8 ビットのフォーマットで送受信します。          |

|     |      |     |     | 1:データ長7ビットのフォーマットで送受信します。            |

| 5   | PE   | 0   | R/W | パリティイネーブル (調歩同期式モードのみ有効)             |

|     |      |     |     | このビットが1のとき,送信時はパリティビットを付加し,受         |

|     |      |     |     | 信時はパリティチェックを行います。                    |

| 3   | STOP | 0   | R/W | ストップビットレングス (調歩同期式モードのみ有効)           |

|     |      |     |     | 送信時のストップビットの長さを選択します。                |

|     |      |     |     | 0:1ストップビット                           |

|     |      |     |     | 1:2ストップビット                           |

|     |      |     |     | 受信時はこのビットの設定値に関わらず , ストップビットの 1 ビッ   |

|     |      |     |     | ト目のみチェックし,2 ビット目が 0 の場合は次の受信キャラクタ    |

|     |      |     |     | のスタートビットとみなします。                      |

| 1   | CKS1 | 0   | R/W | クロックセレクト 1, 0                        |

| 0   | CKS0 | 1   | R/W | 内蔵ボーレートジェネレータのクロックソースを選択します。         |

|     |      |     |     | 00:φクロック (n = 0)                     |

|     |      |     |     | 01:φ <sub>W</sub> クロック (n = 0)       |

|     |      |     |     | 10:φ/16 クロック (n = 2)                 |

|     |      |     |     | 11:φ/64 クロック (n = 3)                 |

|     |      |     |     | このビットの設定値とボーレートの関係については , ハードウェア     |

|     |      |     |     | マニュアルの「ビットレートレジスタ (BRR)」を参照してくださ     |

|     |      |     |     | い。n は設定値の 10 進表示で,「ビットレートレジスタ (BRR)」 |

|     |      |     |     | 中の n の値を表します。                        |

• BRR3 ビットレートレジスタ 3 アドレス: H'FF99

| ビット | ビット名 | 設定値 | R/W | 機能                                    |

|-----|------|-----|-----|---------------------------------------|

| 7   | bit7 | 0   | R/W | ビットレートを設定するリード/ライト可能な 8 ビットのレジスタ      |

| 6   | bit6 | 0   | R/W | です。                                   |

| 5   | bit5 | 0   | R/W | 調歩同期式モードにおける SMR3 の CKS1, CKS0 で選択される |

| 4   | bit4 | 0   | R/W | ボーレートジェネレータの動作クロックと合わせたビットレート         |

| 3   | bit3 | 0   | R/W | を 2400bit/s に設定                       |

| 2   | bit2 | 0   | R/W |                                       |

| 1   | bit1 | 0   | R/W |                                       |

| 0   | bit0 | 0   | R/W |                                       |

● SCR3 シリアルコントロールレジスタ 3 アドレス: H'FF9A

| ビット | ビット名 | 設定値 | R/W | 機能                                                    |

|-----|------|-----|-----|-------------------------------------------------------|

| 5   | TE   | 1   | R/W | トランスミットイネーブル                                          |

|     |      |     |     | このビットが1のとき,送信動作が可能になります。                              |

| 4   | RE   | 1   | R/W | レシーブイネーブル                                             |

|     |      |     |     | このビットが1のとき,受信動作が可能になります。                              |

| 1   | CKE1 | 0   | R/W | クロックイネーブル 1, 0                                        |

| 0   | CKE0 | 0   | R/W | クロックソースを選択します。                                        |

|     |      |     |     | 00 : 内部ボーレートジェネレータ (SCK3 端子は入出力ポート<br>機能となります)        |

|     |      |     |     | 01 : 内部ボーレートジェネレータ (SCK3 端子からビットレートと同じ周波数のクロックを出力します) |

|     |      |     |     | 10:外部クロック (SCK3 端子からビットレートの 16 倍の周波数のクロックを入力してください)   |

|     |      |     |     | 10:外部クロック (SCK3 端子からビットレートの 1                         |

## • TDR3 トランスミットデータレジスタ 3 アドレス: H'FF9B

| ビット | ビット名 | 設定値 | R/W | 機能                              |

|-----|------|-----|-----|---------------------------------|

| 7   | bit7 | 不定  | R/W | 送信データを格納するリード/ライト可能な 8 ビットのレジスタ |

| 6   | bit6 | 不定  | R/W | です。                             |

| 5   | bit5 | 不定  | R/W |                                 |

| 4   | bit4 | 不定  | R/W |                                 |

| 3   | bit3 | 不定  | R/W |                                 |

| 2   | bit2 | 不定  | R/W |                                 |

| 1   | bit1 | 不定  | R/W |                                 |

| 0   | bit0 | 不定  | R/W |                                 |

• SSR3 シリアルステータスレジスタ 3 アドレス: H'FF9C

| ビット | ビット名 | 設定値 | R/W    | 機能                                           |

|-----|------|-----|--------|----------------------------------------------|

| 7   | TDRE | 不定  | R/(W)* | トランスミットデータレジスタエンプティ                          |

|     |      |     |        | TDR3 内の送信データの有無を表示します。                       |

|     |      |     |        | [セット条件]                                      |

|     |      |     |        | SCR3 の TE が 0 のとき                            |

|     |      |     |        | TDR3 から TSR3 にデータが転送されたとき                    |

|     |      |     |        | [クリア条件]                                      |

|     |      |     |        | 1 の状態をリードした後,0 をライトしたとき                      |

|     |      |     |        | TDR3 へ送信データをライトしたとき                          |

| 6   | RDRF | 不定  | R/(W)* | レシーブデータレジスタフル                                |

|     |      |     |        | RDR3 内の受信データの有無を表示します。                       |

|     |      |     |        | [セット条件]                                      |

|     |      |     |        | 受信が正常終了し ,RSR3 から RDR3 へ受信データが転送された<br>とき    |

|     |      |     |        | [クリア条件]                                      |

|     |      |     |        | -<br>1 の状態をリードした後,0 をライトしたとき                 |

|     |      |     |        | RDR3 のデータをリードしたとき                            |

| 5   | OER  | 0   | R/(W)* | オーバランエラー                                     |

|     |      |     | , ,    | [セット条件]                                      |

|     |      |     |        | -<br>受信中にオーバランエラーが発生したとき                     |

|     |      |     |        | [クリア条件]                                      |

|     |      |     |        | -<br>1 の状態をリードした後,0 をライトしたとき                 |

| 4   | FER  | 0   | R/(W)* | フレーミングエラー                                    |

|     |      |     |        | [セット条件]                                      |

|     |      |     |        | 受信中にフレーミングエラーが発生したとき                         |

|     |      |     |        | [クリア条件]                                      |

|     |      |     |        | 1 の状態をリードした後,0 をライトしたとき                      |

| 3   | PER  | 0   | R/(W)* | パリティエラー                                      |

|     |      |     |        | [セット条件]                                      |

|     |      |     |        | 受信中にパリティエラーが発生したとき                           |

|     |      |     |        | [クリア条件]                                      |

|     |      |     |        | 1 の状態をリードした後,0 をライトしたとき                      |

| 2   | TEND | 不定  | R      | トランスミットエンド                                   |

|     |      |     |        | [セット条件]                                      |

|     |      |     |        | SCR3 の TE が 0 のとき                            |

|     |      |     |        | 送信キャラクタの最後尾ビットの送信時,TDRE が1のとき                |

|     |      |     |        | [クリア条件]                                      |

|     |      |     |        | TDRE = 1 の状態をリードした後,TDRE フラグに 0 をライトし<br>たとき |

|     |      |     |        | TDR3 へ送信データをライトしたとき                          |

【注】 \* フラグをクリアするための0ライトのみ可能です。

• RDR3 レシーブデータレジスタ 3 アドレス: H'FF9D

| ビット | ビット名 | 設定値 | R/W | 機能                             |

|-----|------|-----|-----|--------------------------------|

| 7   | bit7 | 不定  | R   | 受信データを格納するリードのみ可能な8ビットのレジスタです。 |

| 6   | bit6 | 不定  | R   |                                |

| 5   | bit5 | 不定  | R   |                                |

| 4   | bit4 | 不定  | R   |                                |

| 3   | bit3 | 不定  | R   |                                |

| 2   | bit2 | 不定  | R   |                                |

| 1   | bit1 | 不定  | R   |                                |

| 0   | bit0 | 不定  | R   |                                |

• SEMR シリアル拡張モードレジスタ アドレス:H'FFA6

| ビット | ビット名 | 設定値 | R/W | 機能                                                                                                                                                                  |

|-----|------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | ABCS | 1   | R/W | 調歩同期式基本クロックセレクト<br>調歩同期式モードにおける 1 ビット期間の基本クロックを選択します。<br>ABCS の設定は調歩同期式モード (SMR3 の COM = 0) のとき有効です。<br>0: 転送レートの 16 倍の周波数の基本クロックで動作<br>1: 転送レートの 8 倍の周波数の基本クロックで動作 |

• TCSRWD1 タイマコントロール/ステータスレジスタ WD1 アドレス: H'FFB1

| ビット | ビット名   | 設定値 | R/W       | 機能                                                                      |

|-----|--------|-----|-----------|-------------------------------------------------------------------------|

| 7   | B6WI   | 1   | R/W       | ビット 6 書き込み禁止                                                            |

|     |        |     |           | このビットへの書き込み値が 0 のときだけ,このレジスタのビッ                                         |

|     |        |     |           | ト 6 に対する書き込みが有効となります。リードすると常に 1 が                                       |

|     |        |     |           | 読み出されます。                                                                |

| 6   | TCWE   | 0   | R/W       | タイマカウンタ WD 書き込み許可                                                       |

|     |        |     |           | このビットが 1 のとき TCWD がライトイネーブルとなります。こ<br>のビットにデータを書き込むときはビット 7 の書き込み値は 0 に |

|     |        |     |           | してください                                                                  |

| 5   | B4WI   | 1   | R/W       | ビット4書き込み禁止                                                              |

|     |        |     |           | このビットへの書き込み値が0のときだけ,このレジスタのビッ                                           |

|     |        |     |           | ト 4 に対する書き込みが有効となります。リードすると常に 1 が                                       |

|     |        |     |           | 読み出されます。                                                                |

| 4   | TCSRWE | 0   | R/W       | タイマコントロール/ステータスレジスタ WD1 書き込み許可                                          |

|     |        |     |           | このビットが1のとき,このレジスタのビット2およびビット0                                           |

|     |        |     |           | がライトイネーブルになります。このビットにデータを書き込む<br>ときはビット5の書き込み値は0にしてください。                |

| 3   | B2WI   | 1   | R/W       | ビット2書き込み禁止                                                              |

|     | DZVVI  | '   | 1 1 7 7 7 | こう   と     このが宗正<br>  このビットへの書き込み値が 0 のときだけ,このレジスタのビッ                   |

|     |        |     |           | ト2に対する書き込みが有効となります。リードすると常に1が                                           |

|     |        |     |           | 読み出されます。                                                                |

| 2   | WDON   | 0   | R/W       | ウォッチドッグタイマオン                                                            |

|     |        |     |           | このビットを 1 にセットすると,TCWD がカウントアップを開始                                       |

|     |        |     |           | します。0 にクリアすると TCWD はカウントアップを停止します。                                      |

|     |        |     |           |                                                                         |

|     |        |     |           | TCSRWE = 1 の状態で B2WI に 0, WDON に 0 をライトしたとき<br>[セット条件]                  |

|     |        |     |           | 「セット赤什」                                                                 |

|     |        |     |           | TCSRWE = 1 の状態で B2WI に 0, WDON に 1 をライトしたとき                             |

| 1   | B0WI   | 1   | R/W       | ビットの書き込み禁止                                                              |

|     |        |     |           | このビットへの書き込み値が 0 のときだけ,このレジスタのビッ                                         |

|     |        |     |           | ト 0 に対する書き込みが有効となります。リードすると常に 1 が                                       |

|     |        |     |           | 読み出されます。                                                                |

| 0   | WRST   | 0   | R/W       | ウォッチドッグタイマリセット                                                          |

|     |        |     |           | [クリア条件]                                                                 |

|     |        |     |           | RES 端子によるリセット                                                           |

|     |        |     |           | TCSRWE = 1 の状態で , B0WI に 0, WRST に 0 をライトしたとき                           |

|     |        |     |           | [セット条件]                                                                 |

|     |        |     |           | TCWD がオーバフローし,内部リセット信号が発生したとき                                           |

• SYSCR1 システムコントロールレジスタ1 アドレス: H'FFF0

| ビット | ビット名 | 設定値 | R/W | 機能                                                                                              |

|-----|------|-----|-----|-------------------------------------------------------------------------------------------------|

| 7   | SSBY | 1   | R/W | ソフトウェアスタンバイ                                                                                     |

|     |      |     |     | SLEEP 命令実行後の遷移先を選択します。                                                                          |

|     |      |     |     | 1:スタンバイモードあるいはウォッチモードに遷移                                                                        |

| 3   | LSON | 1   | R/W | ウォッチモードを解除したときに CPU の動作クロックをシステム<br>クロック (φ) にするか , サブクロックにするか (φ <sub>W</sub> ) にするか選<br>択します。 |

|     |      |     |     | 1:CPU の動作クロックはサブクロック(φ <sub>W</sub> )                                                           |

| 2   | TMA3 | 1   | R/W | このビットは SYSCR1 の SSBY, LSON, SYSCR2 の DTON, MSON との組み合わせにより , SLLEP 命令実行後の遷移先を選択します。             |

• SYSCR2 システムコントロールレジスタ 2 アドレス: H'FFF1

| ビット | ビット名 | 設定値 | R/W | 機能                                        |

|-----|------|-----|-----|-------------------------------------------|

| 3   | DTON | 1   | R/W | ダイレクトトランスファオンフラグ                          |

|     |      |     |     | このビットはSYSCR1のSSBY, LSON,TMA3, SYSCR2のMSON |

|     |      |     |     | との組み合わせにより、SLLEP命令実行後の遷移先を選択します。          |

| 1   | SA1  | 1   | R/W | サブアクティブモードクロックセレクト 1, 0                   |

| 0   | SA0  | 1   | R/W | サブアクティブモードおよびサブスリープモードの動作クロック             |

|     |      |     |     | 周波数を選択します。クロックは SLEEP 命令実行後 , 設定した周       |

|     |      |     |     | 波数に切り換わります。                               |

|     |      |     |     | $SA1 = 1$ , $SA0 = 1$ : $\phi_W$          |

● CKSTPR1 クロック停止レジスタ 1 アドレス: H'FFFA

| ビット | ビット名    | 設定値 | R/W | 機能                                                        |

|-----|---------|-----|-----|-----------------------------------------------------------|

| 6   | S3CKSTP | 1   | R/W | SCI3 モジュールスタンバイ                                           |

|     |         |     |     | このビットが 0 のとき 、SCI3 はモジュールスタンバイ状態になります。<br>1:モジュールスタンバイを解除 |

## 4.4 使用 RAM 説明

本タスク例の使用 RAM を表 4 に示します。

表 4 使用 RAM 説明

| ラベル名                | 機能                | メモリ消費量 | 使用関数名 |

|---------------------|-------------------|--------|-------|

| m_trs[0] ~ m_trs[3] | 調歩同期式シリアル送信データを格納 | 4バイト   | main  |

| m_rcv[0] ~ m_rcv[3] | 調歩同期式シリアル受信データを格納 | 4バイト   | main  |

## 5. フローチャート

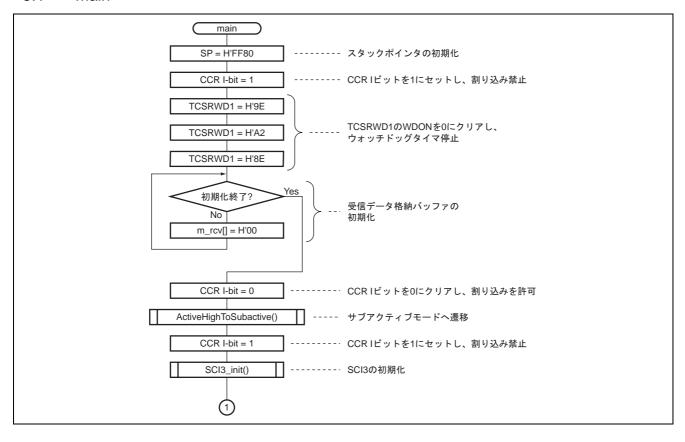

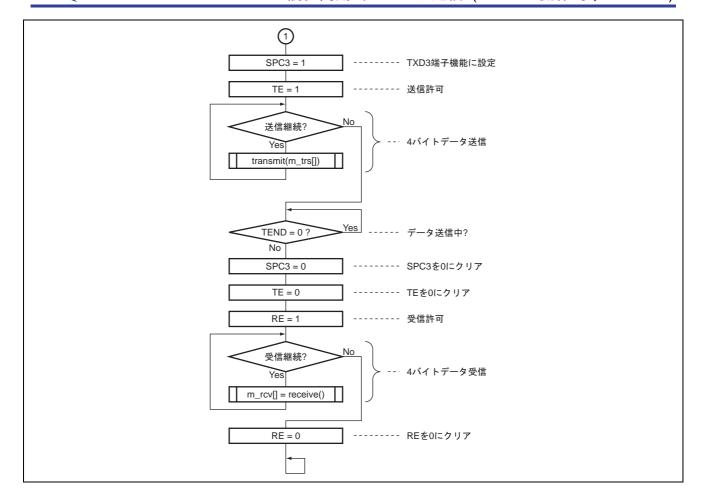

#### 5.1 main

## 5.2 SCI3\_init

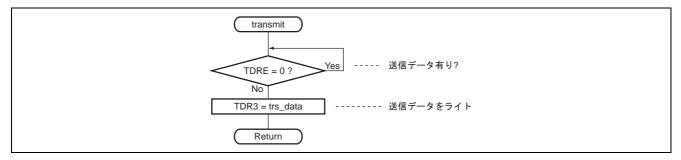

#### 5.3 transmit

## 5.4 receive

## 5.5 ActiveHighToSubactive

#### 5.6 dtint

#### 5.7 リンクアドレス指定

| セクション名 | アドレス   |

|--------|--------|

| CVECT  | H'0000 |

| Р      | H'0100 |

| D, B   | H'FB80 |

## 改訂記録

|      |            |     | 改訂内容 |

|------|------------|-----|------|

| Rev. | 発行日        | ページ | ポイント |

| 1.00 | 2005.03.18 | _   | 初版発行 |

|      |            |     |      |

|      |            |     |      |

|      |            |     |      |

|      |            |     |      |

#### 安全設計に関するお願い ■

1. 弊社は品質、信頼性の向上に努めておりますが、半導体製品は故障が発生したり、誤動作する場合があります。弊社の半導体製品の故障又は誤動作によって結果として、人身事故、火災事故、社会的損害などを生じさせないような安全性を考慮した冗長設計、延焼対策設計、誤動作防止設計などの安全設計に十分ご留意ください。

## 本資料ご利用に際しての留意事項

- 1. 本資料は、お客様が用途に応じた適切なルネサス テクノロジ製品をご購入いただくための参考資料であり、本資料中に記載の技術情報についてルネサス テクノロジが所有する知的財産権その他の権利の実施、使用を許諾するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例の使用に起因する損害、第三者所有の権利に対する侵害に関し、ルネサステクノロジは責任を負いません。

- 3. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他全ての情報は本資料発行時点のものであり、ルネサステクノロジは、予告なしに、本資料に記載した製品または仕様を変更することがあります。ルネサステクノロジ半導体製品のご購入に当たりましては、事前にルネサステクノロジ、ルネサス販売または特約店へ最新の情報をご確認頂きますとともに、ルネサステクノロジホームページ(http://www.renesas.com)などを通じて公開される情報に常にご注意ください。

- 4. 本資料に記載した情報は、正確を期すため、慎重に制作したものですが万一本資料の記述誤りに 起因する損害がお客様に生じた場合には、ルネサステクノロジはその責任を負いません。

- 5. 本資料に記載の製品データ、図、表に示す技術的な内容、プログラム及びアルゴリズムを流用する場合は、技術内容、プログラム、アルゴリズム単位で評価するだけでなく、システム全体で十分に評価し、お客様の責任において適用可否を判断してください。ルネサステクノロジは、適用可否に対する責任は負いません。

- 6. 本資料に記載された製品は、人命にかかわるような状況の下で使用される機器あるいはシステムに用いられることを目的として設計、製造されたものではありません。本資料に記載の製品を運輸、移動体用、医療用、航空宇宙用、原子力制御用、海底中継用機器あるいはシステムなど、特殊用途へのご利用をご検討の際には、ルネサステクノロジ、ルネサス販売または特約店へご照会ください。

- 7. 本資料の転載、複製については、文書によるルネサス テクノロジの事前の承諾が必要です。

- 8. 本資料に関し詳細についてのお問い合わせ、その他お気付きの点がございましたらルネサステクノロジ、ルネサス販売または特約店までご照会ください。