# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

## ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# H8/38124 グループ

# 低電圧検出回路を使用した低電圧検出 (内部基準電圧使用)

## 要旨

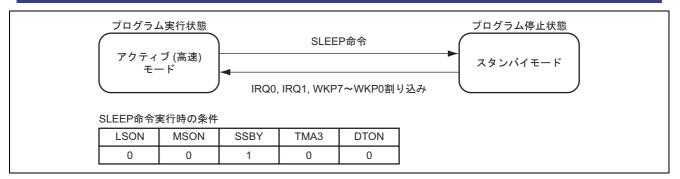

低電圧検出回路により電源電圧降下を検出します。基準電圧に内部基準電圧を,電源電圧の検出レベルには内蔵ラダー抵抗で生成した電圧を使用します。電源電圧が電源立ち下がり検出電圧 (Vint (D)) まで降下するとアクティブ (高速) モードからスタンバイモードに遷移します。また,電源電圧がリセット検知電圧 (Vreset1) まで降下せずに,電源立ち上がり検出電圧 (Vint (U)) まで再上昇するとスタンバイモードを解除してアクティブ (高速) モードに復帰し,低電圧検出回路を解除して処理を終了します。

## 動作確認デバイス

H8/38124

## 目次

| 1. | 仕様       | 2  |

|----|----------|----|

| 2. | 使用機能説明   | 3  |

| 3. | 動作説明     | 9  |

| 4. | ソフトウェア説明 | 10 |

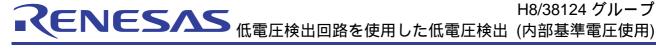

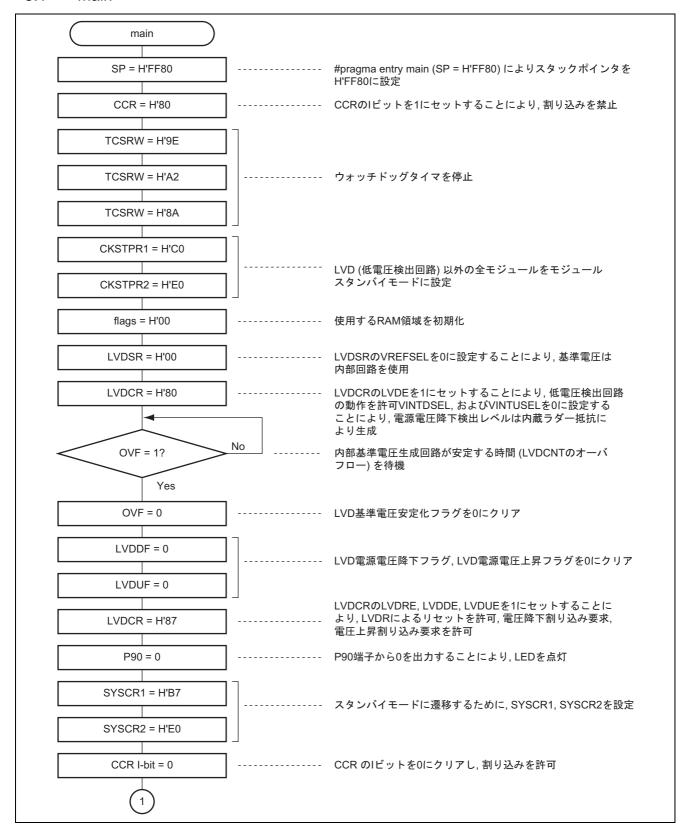

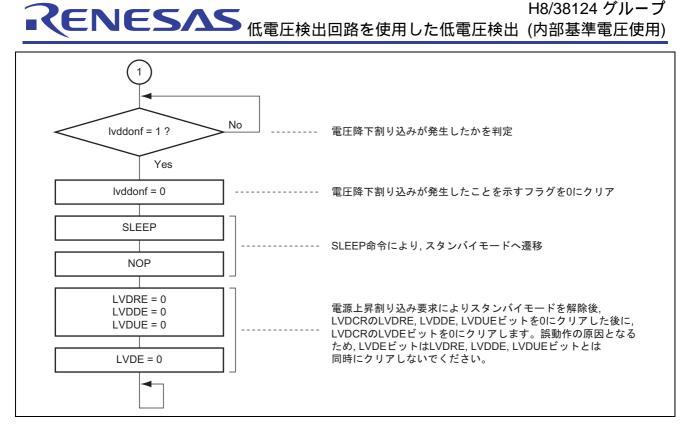

| 5. | フローチャート  | 17 |

## 1. 仕様

- 低電圧検出割り込み回路 (LVDI) を使用して電源電圧の降下を検出します。

- 電源立ち下がり検出電圧 (Vint (D)), および電源立ち上がり検出電圧 (Vint (U)) は内蔵ラダー抵抗で生成した電圧を,低電圧検出回路基準電圧は内部基準電圧を使用します。

- アクティブ (高速) モード時に電源電圧が電源立ち下がり検出電圧 (Vint (D)) まで降下すると ,アクティブ (高速) モードからスタンバイモードへ遷移します。その後 ,電源電圧がリセット検知電圧 (Vreset1) まで降下せずに ,電源立ち上がり検出電圧 (Vint (U)) まで再上昇するとスタンバイモードからアクティブ (高速) モードへ復帰し , 低電圧検出回路を停止して処理を終了します。

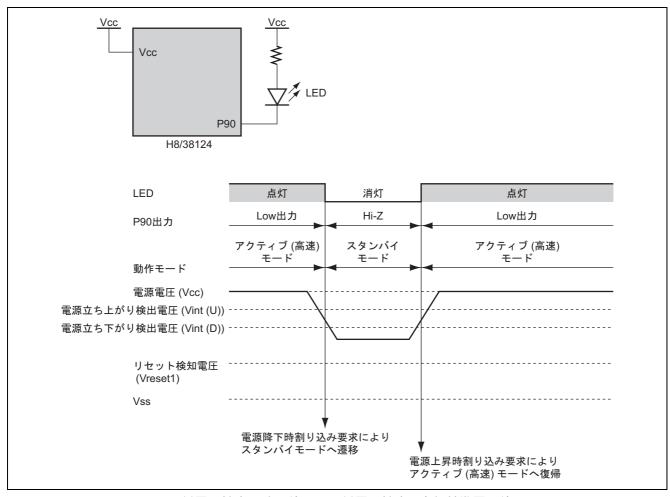

- P90 端子に LED を接続して P90 から Low 出力を行なうことにより LED を点灯させます。スタンバイモード時にはポート出力はハイインピーダンスになるため, LED は消灯します。

- 図1に低電圧検出回路を使用した低電圧検出(内部基準電圧使用)を示します。

図1 低電圧検出回路を使用した低電圧検出 (内部基準電圧使用)

## 2. 使用機能説明

#### 2.1 使用機能

本タスク例における H8/38124 の使用機能について説明します。

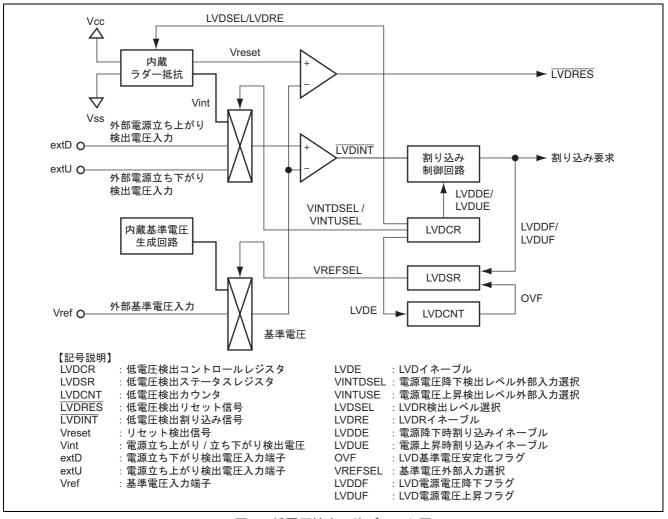

### (1) 低電圧検出回路

低電圧検出回路は,低電圧検出割り込み回路 (LVDI: Interrupt by Low Voltage Detect) と,低電圧検出リ セット回路 (LVDR: Reset by Low Voltage Detect) から構成されます。低電圧検出回路は,電源電圧降下に よる LSI の異常動作 (暴走) を防ぎ,かつ電源電圧の再上昇時に電源電圧降下前の状態を再現するために 使用する回路です。

電源電圧が降下しても,動作保証電圧以上でかつ正常動作中にスタンバイモードに遷移することで,電源 電圧が動作保証電圧以下へ降下したときの不安定な状態をなくし,システムの安全性を高められます。さ らに電源電圧が降下してしまった場合には自動的にリセット状態に遷移します。再度電源電圧が上昇する と一定時間リセット状態を保持してからアクティブモードに自動的に遷移します。

低電圧検出回路の特長を以下に示します。

- 低電圧検出リセット回路:電源電圧を監視して、一定電圧以下になった場合に内部リセット信号を発生

- 低電圧検出割り込み回路:電源電圧を監視して、一定電圧より降下または上昇した場合に割り込みを発生

リセット発生電圧を検出するレベルは、低電圧検出リセット回路のみ使用する場合と、低電圧検出割り込 み回路と低電圧検出リセット回路を併用する場合の2種類選択できます。また,電源立ち上がり/立ち下が り検出電圧および基準電圧を LSI の外部から入力できるため,検出レベルを自由に設定できます。

低電圧検出回路のレジスタについて以下に示します。

#### ● 低電圧検出コントロールレジスタ (LVDCR)

LVDCR は8ビットのリード / ライト可能なレジスタで,低電圧検出回路を使用するかしないか(LVDE ビット)、電源電圧降下および上昇時の検出レベルの外部入力設定 (VINTDSEL, VINTUSEL ビット)、低電 圧検出リセット回路 (LVDR) 検出レベルの設定 (LVDSEL ビット), 低電圧検出リセット回路 (LVDR) によるリセットを許可 / 禁止 (LVDRE ビット)、電源電圧降下および上昇による割り込み許可 / 禁止 (LVDDE, LVDUE ビット) の制御を行ないます。

### ● 低電圧検出ステータスレジスタ (LVDSR)

LVDSR は8ビットのリード / ライト可能なレジスタで 基準電圧の外部入力の選択 (VREFSEL ビット), 基準電圧の安定化 (OVF ビット) および電源電圧が ,ある一定電圧より降下または上昇したことを示しま す (LVDDF, LVDUF ビット)。

#### ● 低電圧検出カウンタ (LVDCNT)

LVDCNT はリードのみ可能な 8 ビットのアップカウンタです。LVDCR レジスタの LVDE ビットに 1 をラ イトするとカウントを開始します。φ/4 をクロックソースとしてカウントアップし ,HFF から H'00 にオー バフローすると,LVDSR レジスタの OVF ビットに 1 がセットされ,内部基準電圧生成回路が安定したこ とを示します。LVD 機能を使用する場合,本カウンタがオーバフローするまでの期間は待機する必要が あります。LVDCNT の初期値は H'00 です。

低電圧検出回路のブロック図を図2に示します。

低電圧検出回路を使用した低電圧検出 (内部基準電圧使用)

図2 低電圧検出回路ブロック図

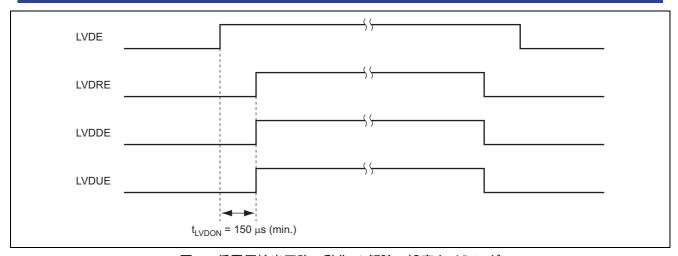

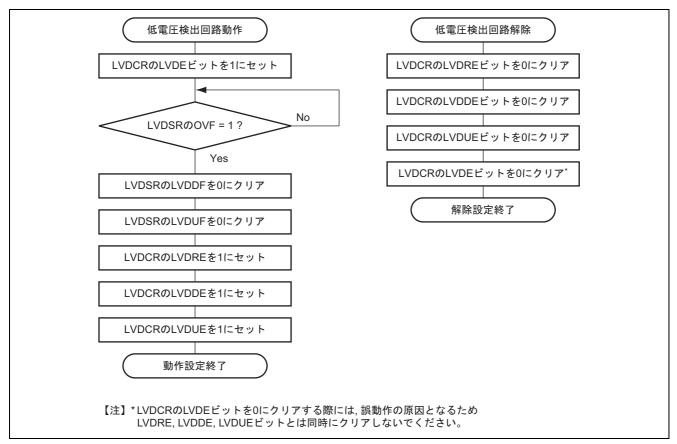

低電圧検出回路を正常に動作または解除させるためには,以下の手順で設定してください。低電圧検出回 路の動作および解除を設定する場合の設定タイミングを図3に,そのときの手順を図4に示します。

- 1. 低電圧検出回路を動作させる場合は,まずLVDCRレジスタのLVDEビットを1にセットします。

- 2. 基準電圧および低電圧検出電源が安定するまでの時間 (tuyoon = 150 μs) を LVDCNT のオーバフローで 待った後,LVDSR レジスタの LVDDF と LVDUF ビットを 0 にクリアして,必要に応じて LVDCR レ ジスタの LVDRE, LVDDE, LVDUE ビットを 1 にセットします。

- 3. 低電圧検出回路を解除する場合は LVDRE, LVDDE, LVDUE ビットをすべて 0 にクリアした後 LVDE ビットを 0 にクリアします。 誤動作の原因となるため ,LVDE ビットは LVDRE, LVDDE, LVDUE ビッ トと同時にクリアしないでください。

図3 低電圧検出回路の動作/解除の設定タイミング

図 4 低電圧検出回路の動作 / 解除の手順フロー

### (2) ウォッチドッグタイマ

H8/38124 はウォッチドッグタイマを内蔵しており,リセット解除後,ウォッチドッグタイマはオンされ ています。タイマカウンタ W (TCW) はカウントアップ動作を行ない, TCW がオーバフローすると H8/38124 内部をリセットします。本タスク例では,ウォッチドッグタイマ機能を使用しないため,ウォッ チドッグタイマ機能を停止させます。以下にウォッチドッグタイマのレジスタについて示します。

● タイマコントロール / ステータスレジスタ W (TCSRW)

TCSRW は8ビットのリード / ライト可能なレジスタで TCSRW, TCW の書き込み制御 (B6WI, TCWE, B4WI, TCSRWE, B2WI, B0WI ビット), ウォッチドッグタイマの動作制御 (WDON ビット), 動作状態 (WRST ビット) を示すレジスタです。

• タイマカウンタ W (TCW)

TCW は8ビットのリード / ライト可能なアップカウンタで,入力する内部クロックによりカウントアッ プされます。入力するクロックはPMR2(ポートモードレジスタ2)のWDCKS(ウォッチドッグタイマソー スクロック選択) が0のときタイマモードレジスタW (TMW) の設定によりクロックが選択され、1のと きow/32です。TCWの値はCPUから常にリード/ライトできます。TCWがオーバフロー (H'FF→H'00) す ると、内部リセット信号を発生し、TCSRW レジスタの WRST ビットが 1 にセットされます。リセット時, TCW は H'00 に初期化されます。

● タイマモードレジスタ W (TMW)

TMW はCKS3~CKS0(クロックセレクト) の組み合わせによりTCW の入力クロックの選択を行ないます。 なお CKS3~CKS0 による TCW の入力クロックの選択は PMR2の WDCKS が0の場合にのみ有効です。

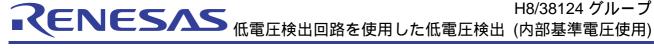

### (3) 低消費電力モード (スタンバイモード)

アクティブモードでシステムコントロールレジスタ 1 (SYSCR1) の SSBY が 1, LSON が 0, および TMA の TMA3 が 0 のとき SLEEP 命令を実行すると, スタンバイモードへ遷移します。スタンバイモードでは クロック発生回路からのクロック供給を停止するため, CPU および内蔵周辺機能が停止します。規定の 電圧が与えられている限り , CPU のレジスタと一部の内蔵周辺機能の内部レジスタ , および内蔵 RAM の データは保持されます。さらに, RAM データ保持電圧で規定した電圧が与えられている限り内蔵 RAM のデータは保持されます。このとき I/O ポートはハイインピーダンス状態となります。

スタンバイモードの解除は 割り込み (IRQ1, IRQ0, WKP7~WKP0), RES 信号入力によって行なわれます。 割り込みによる解除では、割り込み要求が発生すると、システムクロックの発振が開始され、SYSCR1の STS2~STS0により設定された時間が経過した後,安定したシステムクロックがLSI全体に供給されて, スタンバイモードは解除され,割り込み例外処理を開始します。システムコントロールレジスタ2 (SYSCR2) の MSON が 0 のときはアクティブ (高速) モードに , 1 のときはアクティブ (中速) モードへ 遷移します。なお , コンディションコードレジスタ (CCR) の I ビットが 1 のとき , あるいは割り込み許 可レジスタの設定により当該割り込みの受付が禁止されている場合は ,スタンバイモードは解除されませ

RES 端子による解除では, RES 端子を Low レベルにすると,システムクロックの発振が開始されます。 発振安定時間経過後, RES 端子を High レベルにすると, CPU はリセット例外処理を開始します。なお, システムクロックの発振開始と同時に LSI 全体にシステムクロックが供給されます。RES 端子は必ずシス テムクロックの発振が安定するまで,Low レベルを保持してください。

以下に低消費電力モードのレジスタについてしまします。また、図5にアクティブ(高速)モードからス タンバイモードへの遷移のブロック図を示します。

- システムコントロールレジスタ 1 (SYSCR1) SYSCR1 レジスタは SYSCR2 レジスタとともに低消費電力モードの制御を行ないます。

- システムコントロールレジスタ 2 (SYSCR2) SYSCR2 レジスタは SYSCR1 レジスタとともに低消費電力モードの制御を行ないます。

図5 アクティブ (高速) モードからスタンバイモードへの遷移

### (4) 低消費電力モード (モジュールスタンバイモード)

モジュールスタンバイモードは各周辺機能ごとに設定します。 搭載されているすべての周辺モジュールは モジュールスタンバイモードに設定可能です。 モジュールスタンバイモードに設定されると, モジュール へのシステムクロックの供給は停止され、機能は停止し、スタンバイモードと同じ状態になります。 モジュールスタンバイモードの設定はクロック停止レジスタ 1 (CKSTPR1) とクロック停止レジスタ 2 (CKSTPR2) の各ビットを 0 に設定することにより行ないます。

本タスク例では,LVD(低電圧検出回路)以外の周辺モジュールはすべてモジュールスタンバイモードに 設定します。

以下にモジュールスタンバイモードのレジスタについて示します。

### クロック停止レジスタ 1 (CKSTPR1)

タイマ A のモジュールスタンバイモードの設定 (TACKSTP ビット), タイマ C のモジュールスタンバイ モードの設定 (TCCKSTPビット), タイマFのモジュールスタンバイモードの設定 (TFCKSTPビット), タ イマ G のモジュールスタンバイモードの設定 (TGCKSTP ビット), A/D コンバータのモジュールスタンバ イモードの設定 (ADCKSTP ビット), SCI3 のモジュールスタンバイモードの設定 (S32CKSTP ビット)を 制御します。各ビットを0に設定することによりモジュールスタンバイモードに設定します。各ビットを 1に設定するとモジュールスタンバイモードは解除されます。なお,リセット解除後,CKSTPR1レジス タは H'FF に初期化されます。

## クロック停止レジスタ 2 (CKSTPR2)

LCD のモジュールスタンバイモードの設定 (LDCKSTP ビット), PWM1 のモジュールスタンバイモードの 設定 (PW1CKSTP ビット). ウォッチドッグタイマのモジュールスタンバイモードの設定 (WDCKSTP ビット)、非同期イベントカウンタのモジュールスタンバイモードの設定 (AECKSTP ビット)、PWM2 のモ ジュールスタンバイモードの設定 (PW2CKSTP ビット), LVD (低電圧検出回路) のモジュールスタンバイ モードの設定 (LVDCKSTP ビット) を制御します。各ビットを 0 に設定することによりモジュールスタン バイモードに設定します。各ビットを1に設定するとモジュールスタンバイモードは解除されます。なお, リセット解除後, CKSTPR2レジスタはHFFに初期化されます。

#### (5) 例外処理 (IROO 割り込み)

本タスク例で使用する電圧降下時 / 電圧上昇時の割り込み要求は ,IRO0 割り込み要求として要求されま す。

#### (6) I/O ポート (ポート 9)

本タスク例では , P90 端子に LED を接続し , P90 端子から Low を出力することにより LED の点灯を制御 します。スタンバイモードに遷移した場合, P90 端子はハイインピーダンス状態となります。以下にポー ト9のレジスタについて示します。

### ● ポートデータレジスタ 9 (PDR9)

PDR9 はポート 9 の各端子 P95~P90 のデータを格納する 8 ビットのレジスタです。リセット時, PDR9 は H'FF に初期化されます。

#### 機能割り付け 2.2

本タスク例の機能割り付けを表1に示します。

表1 機能割り付け

| 機能      | 機能割り付け                                                  |

|---------|---------------------------------------------------------|

| LVDCR   | 低電圧検出回路の使用許可,電源電圧降下検出レベル/電源電圧上昇検出レベルを内蔵ラ                |

|         | ダー抵抗で生成した電圧に設定 , リセット検知電圧を 2.3 V (typ.) に設定 , LVDR によるリ |

|         | セットを許可,電圧降下 / 上昇時の割り込みを許可                               |

| LVDSR   | 基準電圧の安定化の判定,基準電圧を内部回路に設定,電源電圧の降下/上昇の判定                  |

| LVDCNT  | カウンタのオーバフローを待つことにより、内部基準電圧生成回路の安定化を判定                   |

| TCSRW   | ウォッチドッグタイマの動作を禁止に設定                                     |

| SYSCR1  | SYSCR2 とともに,アクティブ (高速) モードとスタンバイモード間の遷移を制御              |

| SYSCR2  | SYSCR1 とともに,アクティブ (高速) モードとスタンバイモード間の遷移を制御              |

| CKSTPR1 | タイマ A,タイマ C,タイマ F,タイマ G,A/D コンバータ,SCl3 をモジュールスタンバイ      |

|         | モードに設定                                                  |

| CKSTPR2 | LCD, PWM1, ウォッチドッグタイマ, 非同期イベントカウンタ, PWM2 をモジュールスタ       |

|         | ンバイモードに設定 , LVD (低電圧検出回路) のモジュールスタンバイモードの解除             |

| PDR9    | P90 出力端子の出力データを設定                                       |

## 3. 動作説明

図6に低電圧検出回路を使用した低電圧検出(内部基準電圧使用)の動作説明を示します。

#### (1) 初期設定

低電圧検出割り込み回路 (LVDI) は、パワーオンリセット解除後、モジュールスタンバイモードになります。 LVDIを動作させるためには、LVDCRのLVDEビットを1にセットし、基準電圧および低電圧検出電源が安定するまでの時間  $t_{LVDON}$  (150  $\mu$ s) LVDCNTのオーバフローなどで待った後、LVDCRのLVDDE、LVDUEビットを1にセットします。必ずこの後にポートの出力設定を行なってください。

#### (2) 電源電圧降下時

LVDIは電源電圧が降下してVint (D) (typ. = 3.7 V) 電圧以下になると, LVDSRのLVDDFビットが1にセットされます。このとき, LVDDEビットが1であれば, IRQ0割り込み要求を発生します。IRQ0割り込み処理後, LVDDFを0にクリアして, スタンバイモードへ遷移します。

### (3) 電源電圧上昇時

電源電圧がVreset1 (typ. = 2.3 V) 電圧まで降下せず, Vint (U) (typ. = 4.0 V) 電圧以上に上昇すると, LVDUEビットが1であれば, LVDSRのLVDUFビットが1にセットされます。同時にIRQ0割り込み要求を発生します。IRQ0割り込み処理後, LVDUFを0にクリアして, アクティブ (高速) モードへ復帰します。

### 【注】

電源電圧がVreset1 (typ. = 2.3 V) 電圧以下へ降下した場合は、H8/38124は低電圧検出リセット動作になり、プリスケーラSがリセットされます。パワーオンリセットが働かない限り、低電圧検出リセット状態を継続します。電源電圧が再度Vreset1電圧以上に上昇すると、プリスケーラSはカウントアップを始め、 $\phi$ を131,072回カウントし、内部リセット信号が解除されます。このとき、LVDCRレジスタのLVDE、LVDSEL、LVDREビットは初期化されません。ただし、電源電圧がVLVDRmin = 1.0 V以下に低下し、そこから立ち上がった場合、低電圧検出リセットがかからない場合があります。また、電源電圧がVpor = 100 mV以下になるとH8/38124はパワーオンリセット動作になります。

図 6 動作説明

## 4. ソフトウェア説明

## 4.1 モジュール説明

本タスク例のモジュール説明を表2に示します。

表2 モジュール説明

| 関数名      | 機能                                                                                                              |

|----------|-----------------------------------------------------------------------------------------------------------------|

| main     | ウォッチドッグタイマの停止,モジュールスタンバイモードの設定,低電圧検出回路<br>初期設定,LED 出力設定,割り込み許可,スタンバイモードへの遷移,アクティブ(高<br>速)モードへの遷移,低電圧検出回路の解除を行なう |

| int_irq0 | IRQ0&LVD 割り込み処理ルーチン,電圧降下時 / 電圧上昇時の判定を行なう                                                                        |

#### 使用内部レジスタ説明 4.2

本タスク例の使用内部レジスタを以下に示します。

#### 低電圧検出コントロールレジスタ アドレス:H'FF86 • LVDCR

| ビット | ビット名     | 初期値 | R/W | 機能                        | 設定値 |

|-----|----------|-----|-----|---------------------------|-----|

| 7   | LVDE     | 0*  | R/W | LVD イネーブル                 | 1   |

|     |          |     |     | 低電圧検出回路の動作 / 停止を制御        |     |

|     |          |     |     | 0: 低電圧検出回路は未使用 (スタンバイ状態)  |     |

|     |          |     |     | 1:低電圧検出回路を使用              |     |

| 5   | VINTDSEL | 0   | R/W | 電源電圧降下 (LVDD) 検出レベル外部入力選択 | 0   |

|     |          |     |     | 電源電圧降下検出レベルを選択            |     |

|     |          |     |     | 0 : LVDD 検出レベルは内蔵ラダー抵抗で生成 |     |

|     |          |     |     | 1 : LVDD 検出レベルは extD 端子入力 |     |

| 4   | VINTUSEL | 0   | R/W | 電源電圧上昇 (LVDU) 検出レベル外部入力選択 | 0   |

|     |          |     |     | 電源電圧上昇検出レベルを選択            |     |

|     |          |     |     | 0 : LVDU 検出レベルは内蔵ラダー抵抗で生成 |     |

|     |          |     |     | 1 : LVDU 検出レベルは extU 端子入力 |     |

| 3   | LVDSEL   | 0*  | R/W | LVDR 検出レベル選択              | 0   |

|     |          |     |     | LVDR 検出レベルを選択             |     |

|     |          |     |     | 0:リセット検知電圧 2.3 V (typ.)   |     |

|     |          |     |     | 1:リセット検知電圧 3.3 V (typ.)   |     |

| 2   | LVDRE    | 0*  | R/W | LVDR イネーブル                | 1   |

|     |          |     |     | LVDR によるリセットの許可 / 禁止を制御   |     |

|     |          |     |     | 0 : LVDR によるリセットを禁止       |     |

|     |          |     |     | 1 : LVDR によるリセットを許可       |     |

| 1   | LVDDE    | 0   | R/W | 電圧降下時割り込み要求イネーブル          | 1   |

|     |          |     |     | 電圧降下時の割り込み要求の許可 / 禁止を制御   |     |

|     |          |     |     | 0:電圧降下時の割り込み要求を禁止         |     |

|     |          |     |     | 1:電圧降下時の割り込み要求を許可         |     |

| 0   | LVDUE    | 0   | R/W | 電圧上昇時割り込み要求イネーブル          | 1   |

|     |          |     |     | 電圧上昇時の割り込み要求の許可 / 禁止を制御   |     |

|     |          |     |     | 0:電圧上昇時の割り込み要求を禁止         |     |

|     |          |     |     | 1:電圧上昇時の割り込み要求を許可         |     |

【注】 \* LVDR によるリセットでは初期化されません。パワーオンリセット, ウォッチドッグタイマリセッ トで初期化されます。

#### アドレス: H'FF87 LVDSR 低電圧検出ステータスレジスタ

| ビット | ビット名    | 初期値 | R/W | 機能                                   | 設定値 |

|-----|---------|-----|-----|--------------------------------------|-----|

| 7   | OVF     | 0*  | R/W | LVD 基準電圧安定化フラグ                       | 0   |

|     |         |     |     | 低電圧検出カウンタ (LVDCNT) がオーバフローしたこ        |     |

|     |         |     |     | とを示す                                 |     |

|     |         |     |     | [クリア条件]                              |     |

|     |         |     |     | 1 の状態をリードした後,0 をライトしたとき              |     |

|     |         |     |     | [セット条件]                              |     |

|     |         |     |     | 低電圧検出カウンタ (LVDCNT) がオーバフローした<br>とき   |     |

| 3   | VREFSEL | 0   | R/W | 基準電圧外部入力選択                           | 0   |

|     |         |     |     | 基準電圧を選択                              |     |

|     |         |     |     | 0:基準電圧は内部回路を使用                       |     |

|     |         |     |     | 1:基準電圧を Vref 端子から外部入力                |     |

| 1   | LVDDF   | 0*  | R/W | LVD 電源電圧降下フラグ                        | 0   |

|     |         |     |     | 電源電圧降下を検出したことを示す                     |     |

|     |         |     |     | [クリア条件]                              |     |

|     |         |     |     | 1 の状態をリードした後,0 をライトしたとき              |     |

|     |         |     |     | [セット条件]                              |     |

|     |         |     |     | 電源電圧が Vint (D) 以下に降下したとき             |     |

| 0   | LVDUF   | 0*  | R/W | LVD 電源電圧上昇フラグ                        | 0   |

|     |         |     |     | 電源電圧上昇を検出したことを示す                     |     |

|     |         |     |     | [クリア条件]                              |     |

|     |         |     |     | 1 の状態をリードした後,0 をライトしたとき              |     |

|     |         |     |     | [セット条件]                              |     |

|     |         |     |     | LVDCR の LVDUE ビットを 1 にセットした状態で ,電    |     |

|     |         |     |     | 源電圧が Vint (D) 以下に降下し , Vreset1 以下に降下 |     |

|     |         |     |     | する前に Vint (U) 以上に上昇したとき              |     |

【注】 \* LVDRによるリセットで初期化されます。

#### LVDCNT 低電圧検出カウンタ アドレス:HTFC3

| ビット | ビット名 | 初期値 | R/W | 機能                                | 設定値 |

|-----|------|-----|-----|-----------------------------------|-----|

| 7   | CNT7 | 0   | R   | LVDCNT はリードのみ可能な 8 ビットのアップカウン     | _   |

| 6   | CNT6 | 0   | R   | タで , LVDE に 1 をライトするとカウントを開始しま    | _   |

| 5   | CNT5 | 0   | R   | す。 φ/4 をクロックソースとしてカウントアップし ,H'FF  | _   |

| 4   | CNT4 | 0   | R   | から H'00 にオーバフローすると,LVDSR の OVF ビッ | _   |

| 3   | CNT3 | 0   | R   | トが1にセットされ ,内部基準電圧生成回路が安定した        | _   |

| 2   | CNT2 | 0   | R   | ことを示します。LVD 機能を使用する場合 , 本カウンタ     | _   |

| 1   | CNT1 | 0   | R   | がオーバフローするまでの期間は待機する必要があり          | _   |

| 0   | CNT0 | 0   | R   | ます。                               | _   |

|     |      |     |     |                                   |     |

タイマコントロール / ステータスレジスタ W • TCSRW アドレス:H'FFB2

| TOSRW のピット6 へのデータの書き込みを制御                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ビット | ビット名   | 初期値 | R/W    | 機能                          | 設定値 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|-----|--------|-----------------------------|-----|

| 0:TCWEへの書き込みを禁止                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7   | B6WI   | 1   | R      | ビット6書き込み禁止                  | 1   |

| 1:TCWEへの書き込みを禁止                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |        |     |        | TCSRW のビット 6 へのデータの書き込みを制御  |     |

| 6         TCWE         0         R/(W)*         タイマカウンタW 書き込み終計可 TCW への書き込みを禁止 1: TCW への書き込みを禁止 1: TCW への書き込みを許可 1: TCSRW の書き込みを許可 1: TCSRW のピット 4 へのデータの書き込みを制御 0: TCSRWE への書き込みを禁止 1: TCSRW のピット 4 へのデータの書き込みを制御 0: TCSRWE への書き込みを禁止 1: TCSRW のピット 2 へのデータの書き込みを制御 0: WDON および WRST への書き込みを禁止 1: WDON および WRST への書き込みを許可 1: WDON および WRST への書き込みを許可 1: WDON への書き込みを許可 1: WDON への書き込みを許可 1: WDON への書き込みを許可 1: WDON への書き込みを計例 0: WDON への書き込みを計例 0: ヴォッチドッグタイマの動作の許可 / 禁止を制御 0: ヴォッチドッグタイマの動作を禁止 [クリア条件] リセット,または TCSRWE = 1 の状態で B2WI に 0をライトしたとき 1: ウォッチドッグタイマの動作を禁止 [クリア条件] TCSRWE = 1 の状態で B2WI に 0をライトしたとき 1: ウォッチドッグタイマの動作を許可 [セット条件] TCSRWE = 1 の状態で B2WI に 0をライトしたとき 1: ウォッチドッグタイマの動作を許可 [セット条件] TCSRWE = 1 の状態で B2WI に 0をライトしたとき 1: ウォッチドッグタイマの動作を許可 [セット条件] TCSRWE = 1 の状態で B2WI に 0をライトしながら WDON に 1をライトしたとき 1: ウォッチドッグタイマの動作を許可 [セットのの声き込みを制御 0: ピット 0 へのデータの書き込みを制御 1: ビット 0 への書き込みを禁止 1         1           0         WRST 0         RW*         ウォッチドッグタイマリセット 0         0 |     |        |     |        | 0 : TCWE への書き込みを許可          |     |

| TCW への書き込みを制御   0: TCW への書き込みを禁止   1: TCW への書き込みを禁止   1: TCW への書き込みを許可   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |        |     |        | 1 : TCWE への書き込みを禁止          |     |

| 0:TCW への書き込みを禁止                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6   | TCWE   | 0   | R/(W)* | タイマカウンタw 書き込み許可             | 0   |

| 1:TCW への書き込みを許可                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |        |     |        | TCW への書き込みを制御               |     |

| 5     B4WI     1     R     ビット4書き込み禁止<br>TCSRW のピット4へのデータの書き込みを制御<br>0: TCSRWE への書き込みを禁止     0       4     TCSRWE     0     R/(W)*     タイマコントロール / ステータスレジスタ W 書き込み<br>許可<br>TCSRW のピット 2 へのデータの書き込みを禁止<br>1: WDON および WRST への書き込みを禁止<br>1: WDON および WRST への書き込みを許可<br>0: WDON への書き込みを許可<br>1: WDON への書き込みを許可<br>1: WDON への書き込みを禁止     0       2     WDON     1     R/(W)*     ウォッチドッグタイマオン<br>ウォッチドッグタイマの動作を禁止<br>[クリア条件]<br>リセット,または TCSRWE = 1 の状態で B2WI に 0 をライトしたどき<br>1: ウォッチドッグタイマの動作を許可<br>[セット条件]<br>TCSRWE = 1 の状態で B2WI に 0 をライトしながら<br>WDON に 1 をライトしたどき       1     BOWI     1     R     ビット 0 書き込み禁止<br>TCSRW のピット 0 への書き込みを制御<br>0: ビット 0 への書き込みを禁止       0     WRST     0     RW*     ウォッチドッグタイマリセット     0                                                                                                                                                                                                                                                               |     |        |     |        | 0 : TCW への書き込みを禁止           |     |

| TCSRW のピット 4へのデータの書き込みを制御 0: TCSRWE への書き込みを禁止  4 TCSRWE 0 R/(W)* タイマコントロール / ステータスレジスタ W 書き込み 許可 TCSRW のピット 2 へのデータの書き込みを制御 0: WDON および WRST への書き込みを禁止 1: WDON および WRST への書き込みを許可  3 B2WI 1 R ピット 2 書き込み禁止 TCSRW のピット 2 へのデータの書き込みを制御 0: WDON への書き込みを許可 1: WDON への書き込みを許可 1: WDON への書き込みを許可 1: WDON への書き込みを許可 1: WDON への書き込みを禁止 [クリア条件] リセット , または TCSRWE = 1 の状態で B2WI に 0をライトしながら WDON に 0をライトしたとき 1: ウォッチドッグタイマの動作を禁止 [クリア条件] TCSRWE = 1 の状態で B2WI に 0をライトしながら WDON に 1をライトしたとき 1: ウォッチドッグタイマの動作を許可 [セット条件] TCSRWE = 1 の状態で B2WI に 0をライトしながら WDON に 1をライトしたとき 1 B0WI 1 R ピット 0 本のデータの書き込みを制御 0: ピット 0 への書き込みを禁止 0 WRST 0 RW* ウォッチドッグタイマリセット 0                                                                                                                                                                                                                                                                                                                                         |     |        |     |        | 1 : TCW への書き込みを許可           |     |

| 0:TCSRWEへの書き込みを禁止                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5   | B4WI   | 1   | R      |                             | 0   |

| 1: TCSRWE への書き込みを禁止                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |        |     |        | TCSRW のビット 4 へのデータの書き込みを制御  |     |

| 4     TCSRWE     0     R/(W)*     タイマコントロール / ステータスレジスタ W 書き込み 許可 TCSRW のピット 2 へのデータの書き込みを禁止 1: WDON および WRST への書き込みを許可 3     1     R     ビット 2 書き込み禁止 TCSRW のピット 2 へのデータの書き込みを計可 0: WDON への書き込みを計可 1: WDON への書き込みを計可 1: WDON への書き込みを禁止 つカッチドッグタイマオン ウオッチドッグタイマの動作の許可 / 禁止を制御 0: ウオッチドッグタイマの動作を禁止 [クリア条件] リセット , または TCSRWE = 1 の状態で B2WI に 0をライトしたとき 1: ウオッチドッグタイマの動作を許可 [セット条件] TCSRWE = 1 の状態で B2WI に 0をライトしたとき 1: ウオッチドッグタイマの動作を許可 [セット条件] TCSRWE = 1 の状態で B2WI に 0をライトしたとき 1: ウオッチドッグタイマの動作を許可 [セット条件] TCSRW のピット 0 へのデータの書き込みを制御 0: ピット 0 書き込みを計可 1: ピット 0 への書き込みを禁止 0 WRST 0 RW* ウオッチドッグタイマリセット 0     1                                                                                                                                                                                                                                                                                                                                                                           |     |        |     |        | 0 : TCSRWE への書き込みを許可        |     |

| 許可                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |        |     |        | 1 : TCSRWE への書き込みを禁止        |     |

| TCSRW のピット 2 へのデータの書き込みを制御 0: WDON および WRST への書き込みを禁止 1: WDON および WRST への書き込みを許可 3 B2WI 1 R ピット 2 書き込み禁止 TCSRW のピット 2 へのデータの書き込みを制御 0: WDON への書き込みを許可 1: WDON への書き込みを禁止 2 WDON 1 R/(W)* ウォッチドッグタイマオン ウォッチドッグタイマの動作の許可 / 禁止を制御 0: ウォッチドッグタイマの動作を禁止 [クリア条件] リセット , または TCSRWE = 1 の状態で B2WI に 0 をライトしたとき 1: ウォッチドッグタイマの動作を許可 [セット条件] TCSRWE = 1 の状態で B2WI に 0 をライトしたとき 1: ウォッチドッグタイマの動作を許可 [セット条件] TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 1 をライトしたとき 1 B0WI 1 R ピットの書き込み禁止 TCSRW のピット 0 へのデータの書き込みを制御 0: ピット 0 への書き込みを禁止 0 WRST 0 RW* ウォッチドッグタイマリセット 0                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4   | TCSRWE | 0   | R/(W)* |                             | 1   |

| 0:WDON および WRST への書き込みを禁止   1:WDON および WRST への書き込みを許可   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |        |     |        | ··· -                       |     |

| 1:WDON および WRST への書き込みを許可  R ビット 2書き込み禁止 TCSRW のビット 2へのデータの書き込みを制御 0:WDON への書き込みを許可 1:WDON への書き込みを禁止  2 WDON 1 R/(W)* ウォッチドッグタイマオン ウォッチドッグタイマの動作の許可 / 禁止を制御 0:ウォッチドッグタイマの動作を禁止 [クリア条件] リセット , または TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 0 をライトしたとき 1:ウォッチドッグタイマの動作を許可 [セット条件] TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 1 をライトしたとき  1 B0WI 1 R ビット 0 書き込み禁止 TCSRW のビット 0 へのデータの書き込みを制御 0:ビット 0 への書き込みを禁止 0 WRST 0 RW* ウォッチドッグタイマリセット 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |        |     |        |                             |     |

| 3   B2WI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |        |     |        |                             |     |

| TCSRW のピット 2 へのデータの書き込みを制御 0: WDON への書き込みを許可 1: WDON への書き込みを禁止  2 WDON 1 R/(W)* ウォッチドッグタイマオン ウォッチドッグタイマの動作の許可 / 禁止を制御 0: ウォッチドッグタイマの動作を禁止 [クリア条件] リセット,または TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 0 をライトしたとき 1: ウォッチドッグタイマの動作を許可 [セット条件] TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 1 をライトしたとき  1 B0WI 1 R ビット 0 書き込み禁止 TCSRW のピット 0 へのデータの書き込みを制御 0: ビット 0 への書き込みを禁止 0 WRST 0 RW* ウォッチドッグタイマリセット 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |        |     |        |                             |     |

| 0:WDONへの書き込みを禁止       2 WDON     1 R/(W)* ウォッチドッグタイマオン ウォッチドッグタイマの動作の許可 / 禁止を制御 の:ウォッチドッグタイマの動作を禁止 [クリア条件] リセット,または TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 0 をライトしたとき 1:ウォッチドッグタイマの動作を許可 [セット条件] TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 1 をライトしたとき       1 BOWI     1 R ビット 0 書き込み禁止 TCSRW のピット 0 へのデータの書き込みを制御 の:ビット 0 への書き込みを禁止 0 WRST 0 RW* ウォッチドッグタイマリセット     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3   | B2WI   | 1   | R      |                             | 0   |

| 1:WDON への書き込みを禁止                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |        |     |        |                             |     |

| 2       WDON       1       R/(W)*       ウォッチドッグタイマオン<br>ウォッチドッグタイマの動作の許可 / 禁止を制御<br>0: ウォッチドッグタイマの動作を禁止<br>[クリア条件]<br>リセット,または TCSRWE = 1 の状態で B2WI に 0 をライトしたとき<br>1: ウォッチドッグタイマの動作を許可<br>[セット条件]<br>TCSRWE = 1 の状態で B2WI に 0 をライトしながら<br>WDON に 1 をライトしたとき         1       BOWI       1       R       ビット 0 書き込み禁止<br>TCSRW のビット 0 へのデータの書き込みを制御<br>0: ビット 0 への書き込みを禁止       1         0       WRST       0       R/W*       ウォッチドッグタイマリセット       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |        |     |        |                             |     |

| ウォッチドッグタイマの動作の許可 / 禁止を制御         0: ウォッチドッグタイマの動作を禁止         [クリア条件]         リセット , または TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 0 をライトしたとき         1: ウォッチドッグタイマの動作を許可         [セット条件]         TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 1 をライトしたとき         1       B0WI         1       R         ビット 0 書き込み禁止       1         TCSRW のビット 0 へのデータの書き込みを制御 0: ビット 0 への書き込みを許可 1: ビット 0 への書き込みを禁止         0       WRST       0         RW*       ウォッチドッグタイマリセット 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |        |     |        |                             |     |

| 0: ウォッチドッグタイマの動作を禁止         [クリア条件]         リセット,または TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 0 をライトしたとき 1: ウォッチドッグタイマの動作を許可 [セット条件]         TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 1 をライトしたとき         1 B0WI       1 R ビット 0 書き込み禁止 TCSRW のビット 0 へのデータの書き込みを制御 0: ビット 0 への書き込みを許可 1: ビット 0 への書き込みを禁止         0 WRST       0 R/W* ウォッチドッグタイマリセット                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2   | WDON   | 1   | R/(W)* |                             | 0   |

| [クリア条件]       リセット,または TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 0 をライトしたとき 1:ウォッチドッグタイマの動作を許可 [セット条件]       1 ウォッチドッグタイマの動作を許可 [セット条件]         TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 1 をライトしたとき       1 をライトしたとき         1 B0WI       1 R ビット 0 書き込み禁止 TCSRW のビット 0 へのデータの書き込みを制御 0:ビット 0 への書き込みを許可 1:ビット 0 への書き込みを禁止         0 WRST       0 R/W* ウォッチドッグタイマリセット 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |        |     |        |                             |     |

| リセット , または TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 0 をライトしたとき 1: ウォッチドッグタイマの動作を許可 [セット条件] TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 1 をライトしたとき       1 B0WI 1 R ビット 0 書き込み禁止 TCSRW のビット 0 へのデータの書き込みを制御 0: ビット 0 への書き込みを許可 1: ビット 0 への書き込みを禁止       1 ビット 0 への書き込みを禁止                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |        |     |        |                             |     |

| をライトしながら WDON に 0 をライトしたとき 1: ウォッチドッグタイマの動作を許可 [セット条件] TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 1 をライトしたとき 1 B0WI 1 R ビット 0 書き込み禁止 1 TCSRW のビット 0 へのデータの書き込みを制御 0: ビット 0 への書き込みを許可 1: ビット 0 への書き込みを禁止 0 WRST 0 R/W* ウォッチドッグタイマリセット 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |        |     |        | -                           |     |

| 1: ウォッチドッグタイマの動作を許可 [セット条件]       TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 1 をライトしたとき         1 BOWI       1 R ビット 0 書き込み禁止 1 TCSRW のビット 0 へのデータの書き込みを制御 0: ビット 0 への書き込みを許可 1: ビット 0 への書き込みを禁止       0 WRST 0 R/W* ウォッチドッグタイマリセット 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |        |     |        | ,                           |     |

| [セット条件]   TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 1 をライトしたとき                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |        |     |        |                             |     |

| TCSRWE = 1 の状態で B2WI に 0 をライトしながら WDON に 1 をライトしたとき  1 B0WI 1 R ビット 0 書き込み禁止 1 TCSRW のビット 0 へのデータの書き込みを制御 0: ビット 0 への書き込みを許可 1: ビット 0 への書き込みを禁止  0 WRST 0 R/W* ウォッチドッグタイマリセット 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |        |     |        |                             |     |

| WDON に 1 をライトしたとき       1 BOWI     1 R ビット 0 書き込み禁止     1 TCSRW のビット 0 へのデータの書き込みを制御 0: ビット 0 への書き込みを許可 1: ビット 0 への書き込みを禁止       0 WRST 0 R/W* ウォッチドッグタイマリセット     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |        |     |        | •                           |     |

| 1     BOWI     1     R     ビット 0 書き込み禁止         TCSRW のビット 0 へのデータの書き込みを制御         0: ビット 0 への書き込みを許可         1: ビット 0 への書き込みを禁止         0     1     R     0     R/W*     ウォッチドッグタイマリセット     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |        |     |        |                             |     |

| TCSRW のビット 0 へのデータの書き込みを制御 0: ビット 0 への書き込みを許可 1: ビット 0 への書き込みを禁止 0 WRST 0 R/W* ウォッチドッグタイマリセット 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1   | BUWI   | 1   | R      |                             | 1   |

| 0: ビット 0 への書き込みを許可       1: ビット 0 への書き込みを禁止       0 WRST 0 R/W* ウォッチドッグタイマリセット 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | '   | BOWI   | '   |        |                             | '   |

| 1: ビット 0 への書き込みを禁止       0 WRST 0 R/W* ウォッチドッグタイマリセット 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |        |     |        |                             |     |

| 0         WRST         0         R/W*         ウォッチドッグタイマリセット         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |        |     |        |                             |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0   | WRST   | 0   | R/W*   |                             | 0   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | ****** |     | 1011   |                             |     |

| ことを示す                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |        |     |        |                             |     |

| [クリア条件]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |        |     |        | <br> 「クリア条件                 |     |

| (1) RES 信号によるリセット                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |        |     |        | -                           |     |

| (2) TCSRWE = 1 の状態で ,B0WI に 0 をライトしなが                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |        |     |        |                             |     |

| ら WRST に 0 をライトしたとき                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |        |     |        | • ,                         |     |

| [セット条件]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |        |     |        | [セット条件]                     |     |

| - TCW がオーバフローし ,内部リセット信号が発生した                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |        |     |        | TCW がオーバフローし ,内部リセット信号が発生した |     |

| とき                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |        |     |        | とき                          |     |

【注】 \* 書き込み条件が成立している場合にのみ,書き込み可能となります。

システムコントロールレジスタ1 アドレス:H'FFF0 • SYSCR1

| ビット | JRI システ<br>ビット名 | 初期値 | R/W | ンスタ 1 アトレス:HFFF0 機能                            | 設定値 |

|-----|-----------------|-----|-----|------------------------------------------------|-----|

| 7   | SSBY            | 0   | R/W | ソフトウェアスタンバイ                                    | 1   |

|     |                 |     |     | スタンバイモード,ウォッチモードへの遷移を指定                        |     |

|     |                 |     |     | 0: アクティブモードで SLEEP 命令実行後 , スリー                 |     |

|     |                 |     |     | プモードに遷移。サブアクティブモードで                            |     |

|     |                 |     |     | SLEEP 命令実行後,サブスリープモードに遷移                       |     |

|     |                 |     |     | 1:アクティブモードで SLEEP 命令実行後,スタン                    |     |

|     |                 |     |     | バイモードあるいはウォッチモードに遷移。 サブ                        |     |

|     |                 |     |     | アクティブモードで SLEEP 命令実行後 , ウォッ                    |     |

|     |                 |     |     | チモードに遷移                                        |     |

| 6   | STS2            | 0   | R/W | スタンバイタイマセレクト2~0                                | 0   |

| 5   | STS1            | 0   | R/W | 特定の割り込みにより,スタンバイモード,ウォッチ                       | 1   |

| 4   | STS0            | 0   | R/W | モードを解除し,アクティブモードに遷移する場合                        | 1   |

|     |                 |     |     | に ,クロックが安定するまで CPU と周辺機能が待機す                   |     |

|     |                 |     |     | る時間を指定。動作周波数に応じて待機時間が発振安                       |     |

|     |                 |     |     | 定時間以上になるように指定                                  |     |

|     |                 |     |     | 000: 待機時間 = 8,192 ステート                         |     |

|     |                 |     |     | 001:待機時間 = 16,384 ステート                         |     |

|     |                 |     |     | 010:待機時間 = 32,768 ステート                         |     |

|     |                 |     |     | 011:待機時間 = 65,536 ステート                         |     |

|     |                 |     |     | 100:待機時間 =131,072 ステート                         |     |

|     |                 |     |     | 101:待機時間 = 2 ステート                              |     |

|     |                 |     |     | 110:待機時間 = 8 ステート                              |     |

|     |                 |     |     | 111:待機時間 = 16 ステート                             |     |

|     |                 |     |     | 【注】 本タスク例では,システムクロックに                          |     |

|     |                 |     |     | 4.194304 MHz の水晶発振子を使用                         |     |

| 3   | LSON            | 0   | R/W | ロースピードオンフラグ                                    | 0   |

|     |                 |     |     | ウォッチモードを解除時に , CPU の動作クロックをシ                   |     |

|     |                 |     |     | ステムクロック (φ) にするか ,サブクロック (φ <sub>SUB</sub> ) に |     |

|     |                 |     |     | するかを選択。他の制御ビット,割り込み入力の組み                       |     |

|     |                 |     |     | 合わせで動作モードを決定                                   |     |

|     |                 |     |     | 0 : CPU の動作クロックはシステムクロック (φ)                   |     |

|     |                 |     |     | 1 : CPU の動作クロックはサブクロック(ф <sub>SUB</sub> )      |     |

| 1   | MA1             | 1   | R/W | アクティブ (中速) モードクロックセレクト                         | 1   |

| 0   | MA0             | 1   | R/W | アクティブ (中速) モードまたはスリープ (中速)                     | 1   |

|     |                 |     |     | モードの動作クロックを選択。MA1, MA0 書き込みは                   |     |

|     |                 |     |     | アクティブ (高速) モードまたはサブアクティブモー                     |     |

|     |                 |     |     | ドのときのみ可                                        |     |

|     |                 |     |     | 00 : \( \phi_{OSC} \setminus 16 \)             |     |

|     |                 |     |     | 01: \( \phi_{OSC} \scale 32 \)                 |     |

|     |                 |     |     | 10: \( \phi_{\text{OSC}} / 64 \)               |     |

|     |                 |     |     | 11 : φ <sub>OSC</sub> /128                     |     |

アドレス:H'FFF1 システムコントロールレジスタ 2 • SYSCR2

| ビット | ビット名  | 初期値 | R/W     | 機能                                                               | 設定値 |

|-----|-------|-----|---------|------------------------------------------------------------------|-----|

| 4   | NESEL | 1   | R/W     | ノイズ除去サンプリング周波数選択                                                 | 0   |

|     |       |     |         | サブクロック発振器より生成されたウォッチクロック                                         |     |

|     |       |     |         | (∮w) を ,システムクロック発振器より生成された OSC                                   |     |

|     |       |     |         | クロック (φ <sub>osc</sub> ) によりサンプリングする周波数を選                        |     |

|     |       |     |         | 択。 φ <sub>osc</sub> = 2 ~ 20 MHz のときは , 0 をセット                   |     |

|     |       |     |         | 0 : φ <sub>osc</sub> の 16 分周クロックでサンプリング                          |     |

|     |       |     |         | 1 : φ <sub>osc</sub> の 4 分周のクロックでサンプリング                          |     |

| 3   | DTON  | 0   | R/W     | ダイレクトトランスファオンフラグ                                                 | 0   |

|     |       |     |         | アクティブ (高速) モード , アクティブ (中速) モー                                   |     |

|     |       |     |         | ド,サブアクティブモードの各モード間を,SLEEP 命                                      |     |

|     |       |     |         | 令を実行することにより直接遷移するか否かを設定。                                         |     |

|     |       |     |         | SLEEP 命令実行後に遷移する動作モードは ,本ビット                                     |     |

|     |       |     |         | 以外の制御ビットの組み合わせで決定                                                |     |

|     |       |     |         | 0 : (1) アクティブモードで SLEEP 命令を実行したと<br>き , スタンバイモード , ウォッチモード , または |     |

|     |       |     |         | これ                                                               |     |

|     |       |     |         | (2) サブアクティブモードで SLEEP 命令を実行した                                    |     |

|     |       |     |         | とき,ウォッチモード,またはスリープモードに                                           |     |

|     |       |     |         | 置移                                                               |     |

|     |       |     |         |                                                                  |     |

|     |       |     |         | したとき ,アクティブ (中速) モード (SSBY = 0,                                  |     |

|     |       |     |         | MSON = 1, LSON = 0 のとき), またはサブアク                                 |     |

|     |       |     |         | ティブモード (SSBY = 1, TMA3 = 1, LSON = 1                             |     |

|     |       |     |         | のとき) に直接遷移                                                       |     |

|     |       |     |         | (2) アクティブ (中速) モードで SLEEP 命令を実行                                  |     |

|     |       |     |         | したとき ,アクティブ (高速) モード (SSBY = 0,                                  |     |

|     |       |     |         | MSON = 0, LSON = 0 のとき), またはサブアク                                 |     |

|     |       |     |         | ティブモード (SSBY = 1, TMA3 = 1, LSON = 1                             |     |

|     |       |     |         | のとき) に直接遷移                                                       |     |

|     |       |     |         | (3) サブアクティブモードで SLEEP 命令を実行した                                    |     |

|     |       |     |         | とき , アクティブ (高速) モード (SSBY = 1,                                   |     |

|     |       |     |         | TMA3 = 1, LSON = 0, MSON = 0 のとき), また                            |     |

|     |       |     |         | はアクティブ (中速) モード (SSBY = 1, TMA3                                  |     |

|     |       | _   |         | = 1, LSON = 0, MSON = 1 のとき) に直接遷移                               | _   |

| 2   | MSON  | 0   | R/W     | ミドルスピードオンフラグ~スタンバイモード,                                           | 0   |

|     |       |     |         | ウォッチモード,スリープモード解除後,アクティブ                                         |     |

|     |       |     |         | (高速) モードで動作させるか , アクティブ (中速)<br>モードで動作させるかを選択                    |     |

|     |       |     |         |                                                                  |     |

|     |       |     |         | 0:アクティブ (高速) モードで動作                                              |     |

|     | 0.44  | 0   | D / / / | 1: アクティブ (中速) モードで動作                                             | 0   |

| 1   | SA1   | 0   | R/W     | サブアクティブモードクロックセレクト                                               | 0   |

| 0   | SA0   | 0   | R/W     | サブアクティブモードの CPU 動作クロックを選択。                                       | 0   |

|     |       |     |         | SA1, SA0 はサブアクティブモードでライトしても値 は 東 キャャ                             |     |

|     |       |     |         | は更新されません                                                         |     |

|     |       |     |         | 00 : \$\phi_W/8                                                  |     |

|     |       |     |         | 01: \( \psi_W/4 \\  \text{1x: \( \phi_W/2 \)}                    |     |

|     |       |     |         | 1x : φ <sub>W</sub> /2<br>【注】x : Don't care                      |     |

|     |       |     |         | L/II A. DUIT Cale                                                |     |

CKSTPR1 クロック停止レジスタ 1 アドレス:H'FFFA

| ビット | ビット名     | 初期値 | R/W | 機能                             | 設定値 |

|-----|----------|-----|-----|--------------------------------|-----|

| 5   | S32CKSTP | 1   | R/W | SCI3 モジュールスタンバイモード制御           | 0   |

|     |          |     |     | 0 : SCl3 はモジュールスタンバイモードに設定     |     |

|     |          |     |     | 1 : SCl3 のモジュールスタンバイモードを解除     |     |

| 4   | ADCKSTP  | 1   | R/W | A/D コンバータモジュールスタンバイモード制御       | 0   |

|     |          |     |     | 0 : A/D コンバータはモジュールスタンバイモードに設定 |     |

|     |          |     |     | 1 : A/D コンバータのモジュールスタンバイモードを解除 |     |

| 3   | TGCKSTP  | 1   | R/W | タイマ G モジュールスタンバイモード制御          | 0   |

|     |          |     |     | 0:タイマ G はモジュールスタンバイモードに設定      |     |

|     |          |     |     | 1:タイマ G のモジュールスタンバイモードを解除      |     |

| 2   | TFCKSTP  | 1   | R/W | タイマF モジュールスタンバイモード制御           | 0   |

|     |          |     |     | 0:タイマFはモジュールスタンバイモードに設定        |     |

|     |          |     |     | 1:タイマFのモジュールスタンバイモードを解除        |     |

| 1   | TCCKSTP  | 1   | R/W | タイマ C モジュールスタンバイモード制御          | 0   |

|     |          |     |     | 0: タイマ C はモジュールスタンバイモードに設定     |     |

|     |          |     |     | 1:タイマC のモジュールスタンバイモードを解除       |     |

| 0   | TACKSTP  | 1   | R/W | タイマ A モジュールスタンバイモード制御          | 0   |

|     |          |     |     | 0:タイマ A はモジュールスタンバイモードに設定      |     |

|     |          |     |     | 1:タイマ A のモジュールスタンバイモードを解除      |     |

● CKSTPR2 クロック停止レジスタ 2 アドレス:H'FFFB

| ビット | ビット名     | 初期値 | R/W | 機能                         | 設定値 |

|-----|----------|-----|-----|----------------------------|-----|

| 7   | LVDCKSTP | 1   | R/W | LVD モジュールスタンバイモード制御        | 1   |

|     |          |     |     | 0 : LVD はモジュールスタンバイモードに設定  |     |

|     |          |     |     | 1 : LVD のモジュールスタンバイモードを解除  |     |

| 4   | PW2CKSTP | 1   | R/W | PWM2 モジュールスタンバイモード制御       | 0   |

|     |          |     |     | 0 : PWM2 はモジュールスタンバイモードに設定 |     |

|     |          |     |     | 1 : PWM2 のモジュールスタンバイモードを解除 |     |

| 3   | AECKSTP  | 1   | R/W | AEC モジュールスタンバイモード制御        | 0   |

|     |          |     |     | 0 : AEC はモジュールスタンバイモードに設定  |     |

|     |          |     |     | 1 : AEC のモジュールスタンバイモードを解除  |     |

| 2   | WDCKSTP  | 1   | R/W | WDT モジュールスタンバイモード制御        | 0   |

|     |          |     |     | 0 : WDT はモジュールスタンバイモードに設定  |     |

|     |          |     |     | 1 : WDT のモジュールスタンバイモードを解除  |     |

| 1   | PW1CKSTP | 1   | R/W | PWM1 モジュールスタンバイモード制御       | 0   |

|     |          |     |     | 0 : PWM1 はモジュールスタンバイモードに設定 |     |

|     |          |     |     | 1 : PWM1 のモジュールスタンバイモードを解除 |     |

| 0   | LDCKSTP  | 1   | R/W | LCD モジュールスタンバイモード制御        | 0   |

|     |          |     |     | 0 : LCD はモジュールスタンバイモードに設定  |     |

|     |          |     |     | 1 : LCD のモジュールスタンバイモードを解除  |     |

• PDR9 ポートデータレジスタ 9 アドレス: H'FFDC

| ビット | ビット名 | 初期値 | R/W | 機能             | 設定値 |

|-----|------|-----|-----|----------------|-----|

| 0   | P90  | 1   | R/W | P90 データレジスタ    | 0   |

|     |      |     |     | 0 : P90 は 0 出力 |     |

|     |      |     |     | 1 : P90 は 1 出力 |     |

#### 4.3 使用 RAM 説明

本タスク例の使用 RAM 説明を以下に示します。

## 表 3 使用 RAM 説明

| 変数名   | 説明     | メモリ消費量 | 使用関数名          |

|-------|--------|--------|----------------|

| flags | フラグを格納 | 1 バイト  | main, int_irq0 |

| • ] | flags | アドレス | : H'FB80 |

|-----|-------|------|----------|

|-----|-------|------|----------|

| ビット | ビット名    | 初期値 | 機能                      |

|-----|---------|-----|-------------------------|

| 7   | lvddonf | 0   | 電源電圧降下割り込みが発生したことを示すフラグ |

| 6   | _       | 0   | 未使用                     |

| 5   | _       | 0   |                         |

| 4   | _       | 0   |                         |

| 3   | _       | 0   |                         |

| 2   | _       | 0   |                         |

| 1   | _       | 0   |                         |

| 0   | _       | 0   |                         |

#### フローチャート 5.

#### 5.1 main

#### 5.2 int\_irq0

#### リンクアドレス指定 5.3

| セクション名 | アドレス   |

|--------|--------|

| CVECT  | H'0000 |

| Р      | H'0100 |

| В      | H'FB80 |

# 改訂記録

|      |            | 改訂内容 |      |

|------|------------|------|------|

| Rev. | 発行日        | ページ  | ポイント |

| 1.00 | 2005.09.14 | _    | 初版発行 |