# RA family, RX family

BGA 製品向けボードデザインガイド

# 要旨

本ガイドラインは、これまで QFP(Quad Flat Package)を使用されていたお客様向け、初めて BGA (Ball Grid Array) パッケージを使用されるお客様向けに、少しでも BGA が使い易くなるよう、特に BGA からの引き出し部に注目したボード設計の注意点をまとめたものである。

# 対象デバイス

RA ファミリ、RX ファミリ

# Contents

| 1.                     | BGA パッケージの特徴              | 3  |

|------------------------|---------------------------|----|

| 1.1                    | BGA パッケージとは               | 3  |

| 1.2                    | BGA のボール配置例               | 3  |

| 1.3                    | BGA,FBGA,LGA の定義          | 4  |

| 1.4                    | パッケージの名称およびコード(JEITA コード) | 4  |

| 1.4.1                  |                           |    |

| 1.4.2                  | パッケージ外観特徴コード: (2)         | 5  |

| 1.4.3                  | 基本パッケージ名称コード: (3)         | 5  |

| 1.4.4                  | パッケージ端子数コード: (4)          | 5  |

| 1.4.5                  | パッケージ呼び寸法コード: (5)         | 6  |

| 1.4.6                  | 端子直線間隔コード: (6)            | 6  |

|                        |                           |    |

| 2                      | BGA パッケージの特性              | 6  |

| 2.1                    | 熱抵抗(温度の伝えにくさを表す値)         | 6  |

| 2.2                    | 電気                        | 6  |

|                        |                           |    |

| 3                      | BGA パッケージの実装              |    |

| 3.1                    | RA/RX マイコンの BGA ラインナップ    | 7  |

| 3.2                    | ボードの推奨基板設計ルール(貫通基板)       | 8  |

| 3.3                    | 推奨層構成                     | 8  |

| 3.4                    | 基本的な基板設計の思想               | 9  |

| 3.5                    | 基板設計推奨ルール                 | 10 |

| 3.5.1                  | Power Supply, VCL         | 10 |

| 3.5.2                  | Reset                     | 11 |

| 3.5.3                  | Clock                     | 11 |

| 3.5.4                  | OSC                       | 11 |

| 3.5.5                  | USB                       | 13 |

| 3.5.6                  | Analog                    | 13 |

| 3.6                    | ボールからの配線引き出し例             | 14 |

|                        |                           |    |

| $\Box \land \forall i$ | pion history              | 15 |

# 1. BGA パッケージの特徴

# 1.1 BGA パッケージとは

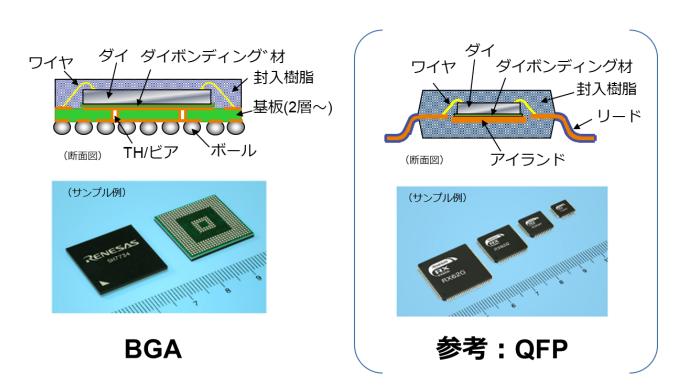

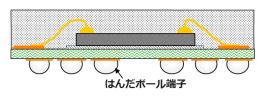

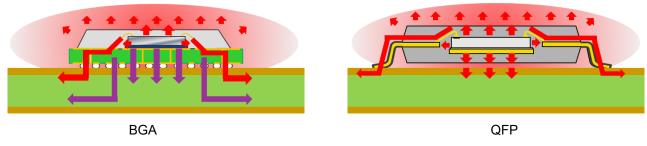

BGA パケージは、ボール状はんだがパッケージ裏面に配列されたパッケージのことを指す(図 1)。 BGA は、QFP に比べ次の特徴がある。

#### QFP と比べた BGA パッケージの特徴:

- ・BGA は、同じピン数であれば小型化に有利。

- ・BGA は、同じサイズであれば多ピン化に有利。

- ·BGAは、基板を通る放熱経路が増えるため、低熱抵抗化に有利。

- ・BGA は、小型化によりパッケージ長を短くでき、基板(インターポーザー)を多層にできるため、低インピーダンス化や伝送速度高速化などに有利。

- ・BGAは、電気特性の考慮が必要な場合、最適なボール配置あり。ただし電気特性が不問な場合、ボールはどこに配置しても良い。

- ※パッケージ材質がプラスチックの BGA を PBGA (Plastic BGA) という。弊社では、BGA は一般的に PBGA のことを指す。

図 1. BGA/QFP パッケージの断面図とサンプル例

## 1.2 BGA のボール配置例

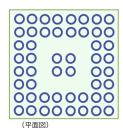

図 2 のように、パッケージサイズに対し接続できる信号数がほぼ決まっている QFP に対し(図 2. QFP)、BGA パッケージは大きく 3 つのボール配置に分けることができる。

・1 つ目はパッケージ外周にボールを配置する場合である(図 2. BGA①)。パッケージサイズに対し、信号数が比較的少ない場合に採用される。

- ・2 つ目はパッケージ外周に加え、チップ直下にサーマルボールを配置する場合である(図 2. BGA②)。 放熱性の考慮が必要な場合に採用される。

- ・3 つ目はパッケージ全面に隙間なくボールを配置する場合である(図 2. BGA③)。信号数が多い場合に採用される。一般的にパッケージやボードの設計が難しくなり、高コストになりやすい。

BGA①:外周

BGA2: サーマル有り

**BGA3**: Full Grid

QFP

図 2. BGA ボールの配置例

## 1.3BGA,FBGA,LGA の定義

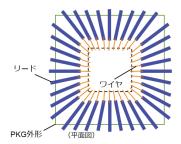

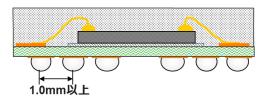

図 3 のように BGA と FBGA(Fine Pitch Ball Grid Array)は、端子ピッチ仕様が違う。端子ピッチが 1mm 以上のパッケージを BGA、端子ピッチが 0.8mm 以下のパッケージを FBGA という。

BGA: 1mm ボールピッチ以上

FBGA: 0.8mm ボールピッチ以下

図3. BGAとFBGAの定義

図4のようにBGAとLGA(Land Grid Array)は、はんだボール端子の有無が違う。はんだボール端子が有るパッケージをBGA、はんだボール端子が無いパッケージをLGAという。

BGA:ボール有り

LGA:ボール無し

図 4. BGA と LGA の定義

#### 1.4パッケージの名称およびコード(JEITA コード)

弊社 IC のパッケージは、JEITA 規格「EIAJ ED-7303C」に従い、JEITA パケージコードを一律に付与している。以下に、JEITA パッケージコードの構成について紹介する。

パッケージコードは以下に示す6項目で構成され、最大30桁で表示される。

| (1)        | (2) | (3) | (4) | (5)         | (6) |

|------------|-----|-----|-----|-------------|-----|

| $\Box$ $-$ |     |     |     | -0000×0000- |     |

#### 1.4.1 パッケージ本体材料コード: (1)

パッケージ本体材料コードは、表1の分類に従い、1字で表示される。

表 1. パッケージ本体材料コード

| 記号 | 材料      | 適用                 |

|----|---------|--------------------|

| С  | セラミックス  | 積層構造のセラミックパッケージ    |

| G  | セラミックス  | ガラス封止されたセラミックパッケージ |

| M  | 金属      | 金属材料で構成されたパッケージ    |

| Р  | プラスチックス | 樹脂で形成されたパッケージ      |

| S  | シリコン    | シリコンで構成されたパッケージ    |

| T  | テープ     | テープで構成されたパッケージ     |

## 1.4.2 パッケージ外観特徴コード: (2)

パッケージ外観特徴コードは、表2の機能分類に従い、必要に応じて最大3字までで表示される。

順位 機能分類 コード 意味 外観特徴 外形上の機能追加 Н Heat sink 放熱用ヒートシンク付き 1 パッケージ取付け高さ  $1.20 \text{mm} < L \le 1.70 \text{mm}$ L Low profile 1.00mm <T≦1.20mm Τ Thin V Very thin 0.80mm < V≤1.00mm 0.65mm <W ≤ 0.80mm W Very-very thin 0.50mm < U ≦ 0.65mm U Ultra thin Χ Extremely thin X≤0.50mm 端子直線間隔 Fine pitch 端子ピッチ 0.8mm以下(BGA、LGA)、0.5mm以下(QFP)

表 2. パッケージ外観特徴コード

#### 1.4.3 基本パッケージ名称コード: (3)

基本パッケージ名称コードは、基本パッケージ名称に従い、原則 3 字で表示する。なお、パッケージのフォーム分類は EIAJ ED-7300 に従う。例外として、基本パッケージ名称コード SOP、DTP に対応する、派生パッケージ名称コード TSOP(1)、TSOP(2)、DTP(1)、DTP(2)のみは基本パッケージ名称コードとして取り扱い、7 字又は 6 字を認める。この際に、TSOP(1)、TSOP(2)では、従来の TSOP(I)、TSOP(II)などを使用しない。さらに、TSOP(1)、TSOP(2)、DTP(1)、DTP(2)の場合には、パッケージコードの最大桁数が 30 桁を越える場合は、パッケージ端子数の中ヌケ表示を例のように省略する。

### 1.4.4 パッケージ端子数コード: (4)

パッケージ端子数コードは、最大 5 字で表示する。なお、端子とはリード、ピン、ランド、バンプ及びボールなど、外部接続方式が異なる電極の総称である。中ヌケ表示は 100 ピン未満に認め、5 字指定とする。例えば、28 ピンパッケージで中ヌケ 2 ピンの場合、28/26 と表記する。

## 1.4.5 パッケージ呼び寸法コード: (5)

パッケージ呼び寸法コードは、例に示すように「パッケージ本体幅(mm)」×「パッケージ本体長さ (mm)」で構成され、最大 11 字で表示する。ただし、小数点以下の数値が"x0"、"00"の場合は"0"、"00"を表記しない。

#### 1.4.6 端子直線間隔コード: (6)

端子直線間隔コードは、4字で表示する。インチ(inch)をミリ(mm)で表示している端子直線間隔は、ISO R370 に従い、丸めて表す。

### 2 BGA パッケージの特性

# 2.1 熱抵抗 (温度の伝えにくさを表す値)

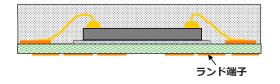

BGAはQFPに比べ、基板を通る放熱経路、特にチップ下の経路が増えるため、低熱抵抗化に有利となる。つまり、BGAはQFPより、放熱特性が良いということを示している(図5)。

図5に示すように、BGAはQFPに比べ、赤色の矢印で示されたリード部や樹脂からの放熱パスに加えて、紫色の矢印で示されたチップで発熱した熱が発熱元のチップ直下からパッケージの各部材を通じて放熱されるパスが加わるため、熱抵抗が低くなる。

図 5. BGA の放熱パス (QFP と比較)

#### 2.2 電気

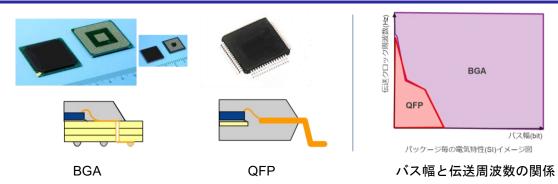

小型化が可能な BGA はパッケージ全長を短く出来るため、低インピーダンスや高速に有利となる(図6)。

- 特徴1: QFP と比較して BGA はパッケージ全長(ワイヤ+配線+スルーホール(TH)+ボール)を短くできるため、インダクタンス・抵抗成分を低くすることができる。

- ・特徴 2:BGA でもパッケージ小型化により、更にパッケージ全長が短くでき、インダクタンス・抵抗成分を低くすることができる。

- 例)電源インピーダンスを低くできるため、電源用バイパスコンデンサ(以降、パスコンと呼ぶ)数の低減(BOM コスト低減)に貢献が可能となる。

図 6. BGA パッケージ全長のイメージ(QFP と比較)および電気特性イメージ図

# 3 BGA パッケージの実装

# 3.1RA/RX マイコンの BGA ラインナップ

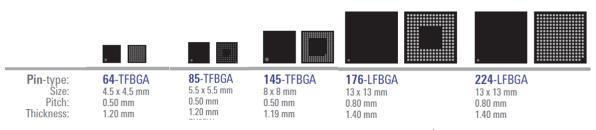

RA/RX マイコンは、主に民生用小型機器向けに、以下のようなパッケージを提供している(図7、表3)。

図 7. RA/RX マイコンの BGA ラインナップ

表 3. RA/RX マイコンの BGA ラインナップ一覧

| Target device                                   | Target package information |              |           |              |  |

|-------------------------------------------------|----------------------------|--------------|-----------|--------------|--|

| rarget device                                   | Package name               | Renesas code | Pin pitch | Size         |  |

| RA4L1                                           | BGA 64-pin                 | PLBG0064JD-A | 0.65 mm   | 5.5 x 5.5 mm |  |

| RA4L1, RA6M5                                    | BGA 100-pin                | PLBG0100KB-A | 0.5 mm    | 7 x 7 mm     |  |

| RA4E2, RA6E2                                    | LFBGA 36-pin               | PLBG0036KA-A | 0.5 mm    | 4 x 4 mm     |  |

| RA4E2, RA6E2                                    | LFBGA 64-pin               | PLBG0064KB-A | 0.5 mm    | 5 x 5 mm     |  |

| RA6M5                                           | LFBGA 144-pin              | PLBG0144KB-A | 0.5 mm    | 7 x 7 mm     |  |

| RA8P1, RA8T2, RA8M2, RA8D2                      | LFBGA 224-pin              | PLBG0224JA-A | 0.65 mm   | 11 x 11 mm   |  |

| RA8M1, RA8D1, RA8T1, RA8E2                      | LFBGA 224-pin              | PLBG0224GD-A | 0.8 mm    | 13 x 13 mm   |  |

| RA8P1, RA8T2, RA8M2, RA8D2                      | LFBGA 289-pin              | PLBG0289JA-A | 0.65 mm   | 12 x 12 mm   |  |

| RA8P1, RA8T2, RA8M2, RA8D2                      | LFBGA 303-pin              | PLBG0303GA-A | 0.8 mm    | 15 x 15 mm   |  |

| RX651, RX65N, RX66N, RX72N, RX72M               | LFBGA 176-pin              | PLBG0176GA-A | 0.8 mm    | 13 x 13 mm   |  |

| RX66N, RX72N, RX72M                             | LFBGA 224-pin              | PLBG0224GA-A | 0.8 mm    | 13 x 13 mm   |  |

| RX671, RX651                                    | TFBGA 64-pin               | PTBG0064KB-A | 0.5 mm    | 4.5 x 4.5 mm |  |

| RX23W                                           | TFBGA 85-pin               | PTBG0085KB-A | 0.5 mm    | 5.5 x 5.5 mm |  |

| RX23E-B                                         | TFBGA 100-pin              | PTBG0100KD-A | 0.5 mm    | 5.5 x 5.5 mm |  |

| RX65W-A                                         | TFBGA 145-pin              | PTBG0145KB-A | 0.5 mm    | 8 x 8 mm     |  |

| RA2E1                                           | WFLGA 36-pin               | PWLG0036KB-A | 0.5 mm    | 4 x 4 mm     |  |

| RX23W                                           | TFLGA 83-pin               | PTLG0083KA-A | 0.5 mm    | 6.1 x 9.5 mm |  |

| RX230, RX231                                    | TFLGA 100-pin              | PTLG0100KA-A | 0.5 mm    | 5.5 x 5.5 mm |  |

| RX113, RX651, RX65N, RX671, RA6M1, RA4M1        | TFLGA 100-pin              | PTLG0100JA-A | 0.65 mm   | 7 x 7 mm     |  |

| RX651, RX65N, RX66N, RX72N, RX671, RA6M2, RA6M3 | TFLGA 145-pin              | PTLG0145KA-A | 0.5 mm    | 7 x 7 mm     |  |

| RX671                                           | TFLGA 145-pin              | PTLG0145JC-A | 0.65 mm   | 9 x 9 mm     |  |

| RX651, RX65N                                    | TFLGA 177-pin              | PTLG0177KA-A | 0.5 mm    | 8 x 8 mm     |  |

# 3.2ボードの推奨基板設計ルール(貫通基板)

貫通 TH を用いたボード(貫通基板)における推奨基板設計ルールを以下に示す(図 8)。配線性や特性などの BGA パッケージの恩恵を最大限に受けるには、ボール間に配線を通すことが可能となる基板設計ルールの適用を推奨する。少なくとも BGA パッケージ搭載エリアの配線幅は 100um を推奨する。

※推奨ルールは、基板メーカーにより変わる可能性があり、詳細は基板メーカーに問い合わせが必要となる。

| F 列 平面図       |

|---------------|

| M N M         |

| D A D C       |

|               |

| A             |

| → ← B         |

| 断面図           |

| G L K         |

| / <del></del> |

|               |

|               |

|               |

| → <b>-</b> -  |

|               |

|               |

|               |

|               |

|               |

| < J →         |

|               |

|    |                         |                              |       |           |       |           | Unit : um |

|----|-------------------------|------------------------------|-------|-----------|-------|-----------|-----------|

| 記号 |                         | BGA Pitch別推奨値(板厚1.2~1.6mm想定) |       |           |       |           |           |

|    | 名称                      | 0.5mmピッチ                     |       | 0.65mmピッチ |       | 0.8mmピッチ  |           |

| 万  |                         | 外層                           | 内層    | 外層        | 内層    | 外層        | 内層        |

| Α  | パターン幅(BGA部以外)           | 100                          | 75    | 100       | 75    | 100       | 100       |

| A' | パターン幅(BGA部限定)           | 100                          | 60    | 100       | 60    | 100       | 100       |

| В  | パターン間隔 (MIN)            | 100                          | 75    | 100       | 75    | 100       | 100       |

| С  | パターンTHランド間隔(MIN)        | 100                          | 70    | 100       | 70    | 100       | 100       |

| D  | パターン - SR開口間隔(MIN)      | 50                           |       | 50        |       | 50        |           |

| Е  | BGAパッド径                 | φ 200-300                    |       | φ 300-400 |       | φ 350-450 |           |

| F  | BGAパッド SR開口径            | φ 300                        |       | φ 350     |       | φ 500     |           |

| G  | 貫通TH ドリル径               | φ 200                        |       | φ 200     |       | φ 250     |           |

| Н  | 貫通TH 穴径                 | φ 150                        |       | φ 150     |       | φ 200     |           |

| J  | TH Pitch(中心間)           | 650                          |       | 650       |       | 800       |           |

| K  | 貫通THランド径                | φ 450                        | φ 450 | φ 450     | φ 450 | φ 500     | φ 500     |

| L  | 貫通THランド間隔               | 200                          | 200   | 200       | 200   | 300       | 300       |

| М  | 貫通THランド - BGAパッド間隔(MIN) | 100                          |       | 100       |       | 100       |           |

図 8. 貫通基板における推奨基板設計ルール

## 3.3推奨層構成

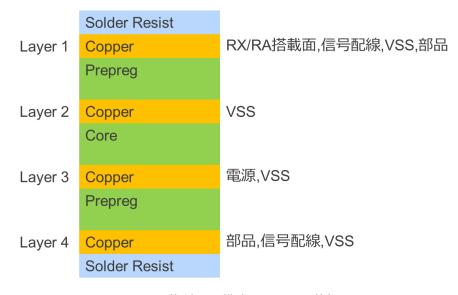

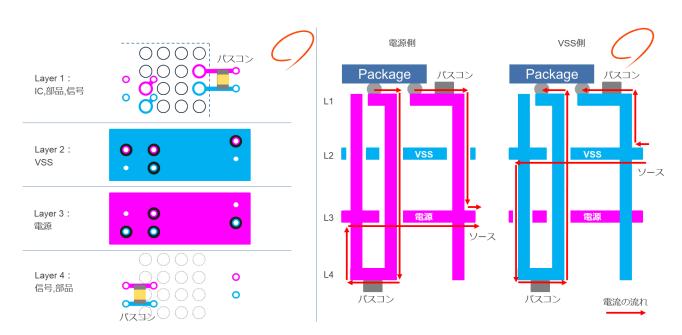

貫通 TH を用いたボードの層構成は、図9に示すような4層を推奨する。Layer 1 は、RA/RX 搭載,信号配線,VSS,部品搭載、Layer 2 は VSS プレーン、Layer 3 は必要最低限の電源プレーンと VSS プレーン、Layer 4 は部品搭載,信号配線,VSS の割り当てを推奨する。更に電気特性を向上する必要がある場合は、第2層(Layer 2)と第3層(Layer 3)の間に2層追加を推奨する。

図 9. 推奨の層構成:4層貫通基板

# 3.4基本的な基板設計の思想

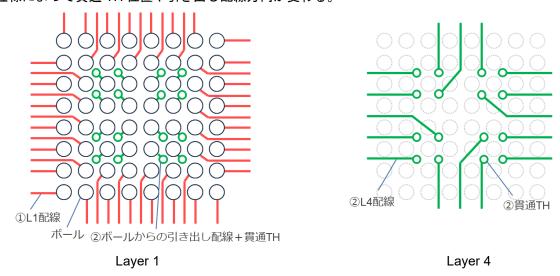

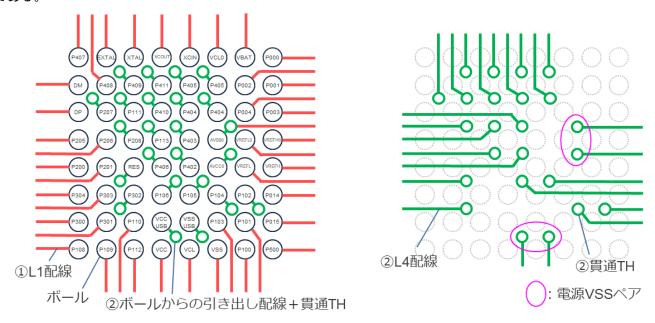

基本的な基板設計の思想は大きく 2 つのステップで示す。外周 2Row に対し RA/RX 搭載面となる表層 (Layer 1) で配線する  $1^{st}$ ステップ (①) と、内周 2Row に対し貫通 TH を介して RA/RX 搭載面と反対面となる裏面(Layer 4)もしくは内層(2 or 3 層)で配線する  $2^{nd}$  ステップ(②)である。

図 10 は 64BGA のフルグリッドの Layer 1 と Layer 4 の基本思想の配線例、図 11 は 144BGA 外周 4Row の Layer 1 と Layer 4 の基本思想の配線例である。赤色配線は Layer1 の配線、黒色丸はボール、緑色配線 と緑色丸はボールからの引き出し配線と貫通 TH を示す。本例は、ボール間に 1 本配線が通る場合を示している。ボール間に配線が通らない場合は、配線層が 1 層増え、他層の配線状況によっては、基板層数が 6 層以上必要になる場合がある。灰色の点線の丸は Layer 1 を透過したボール、緑色丸は貫通 TH と貫通 TH からの引き出し配線を示す。図示していないが、パスコンは貫通 TH の近くに配置する。なお、マイコン搭載回路の仕様によって貫通 TH 位置や引き出し配線方向が変わる。

図 10. 64 (8×8) BGA フルグリッドの Layer 1 と Layer 4 の基本的な引き出し配線例 (平面図)

図 11. 144 (13×13) BGA 外周 4Row の Layer 1 と Layer 4 の基本的な引き出し配線例 (平面図)

## 3.5基板設計推奨ルール

## 3.5.1 Power Supply, VCL

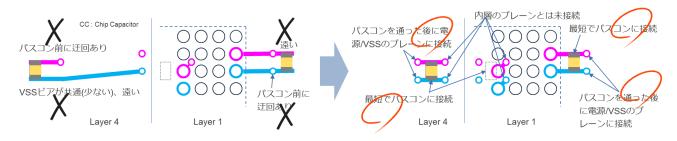

- ・電源端子は対(ペア)となる VSS との間に極力最短位置でパスコン(周波数特性の良いセラミックコンデンサを推奨)を接続する。IC/パッケージ近傍にパスコンを配置し、パスコン後に共通プレーンに接続する(図 12)。電流の流れが、IC/パッケージ→パスコン→共通電源 VSS プレーンとなるよう設計する(図 13)。

- ・電源端子が外周 2Row に配置される場合のパスコン搭載面は IC/パッケージ搭載面、電源端子が 3Row 目以降に配置される場合のパスコン搭載面は IC/パッケージ搭載面と反対面(裏面/Layer 4)を推奨する。

- ・IC/パッケージ〜パスコンまでの距離(配線や TH の抵抗/インダクタンス値)、パスコン容量,挿入位置、フェライトビーズ挿入位置、他電源とのマージ位置などの仕様がある場合は、各仕様に従う。

- ・パスコンを通った後の配線パターン幅や TH 数は、電流量を考慮し、太幅で配線および必要個数以上の TH を配置する。他電源とは極力隣接並走させない、隣接層間で重ねない。

- ・極力 VSS でシールドする。VSS シールド出来ない場合は間隔を広げる(>2×h(隣接層間厚))。

NG 例 OK 例(推奨)

図 12. Power Supply, VCL の推奨パスコン設計イメージ図(Layer 1/Layer 4、平面図)

各層のパスコン周辺のパターン(平面図)

パスコン周辺の電流の流れ(断面図)

図 13. Power Supply, VCL の推奨パスコン設計イメージ図(平面図/断面図)

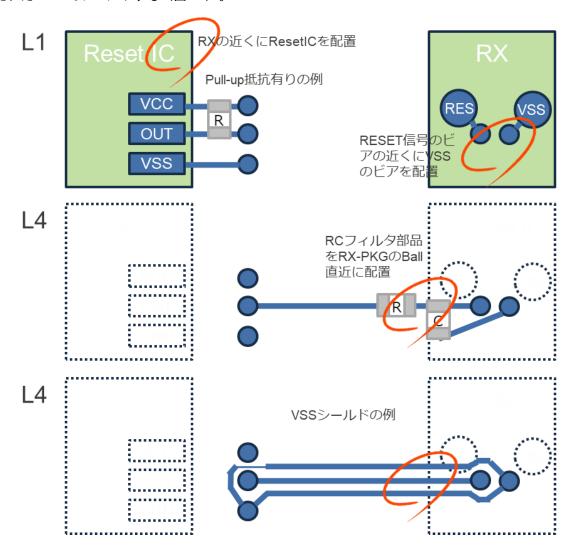

#### 3.5.2 Reset

- ・リセット IC と直接接続する場合、極力マイコンの近くにリセット IC を配置する(図 14)。

- ・ノイズを抑制する場合、ローパスフィルタの挿入を推奨する。(ローパスフィルタ挿入時は VSS シールド不要)(図 14)

- ・他信号(特に、大電流が流れるパターンや高速信号パターン)とは隣接並走させず、太く且つ複数の TH が打たれた VSS でシールドする(図 14)。

図 14. Reset の推奨設計イメージ図 (平面図)

# 3.5.3 Clock

- ・EXATL,XTAL,XCIN,XOUT,X1,X2 などのクロック入出力端子は、周辺回路を含め最短で配線する。

- ・他のパターン(特に、大電流が流れるパターンや高速信号パターン)とは隣接並走させず、VSS でシールドする。

- ・VSS シールド配線は、幅を 0.3 mm 以上、クロック配線との間隔を 0.3~2 mm、確保する。

- ・水晶振動子の周辺回路の下層は、信号,電源,VSS パターンを配線させない。(図 15)

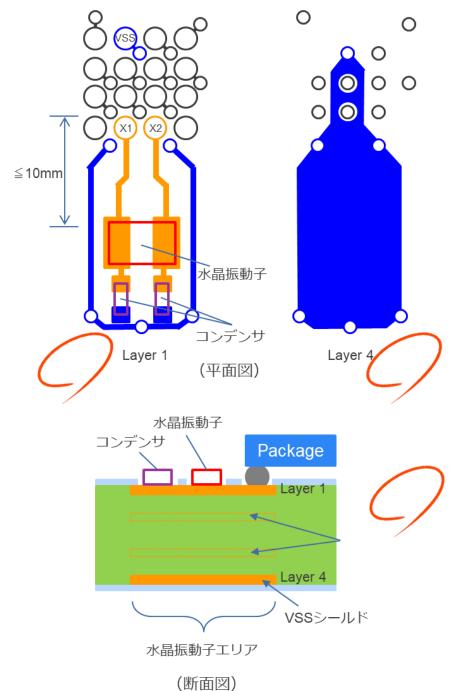

#### 3.5.4 OSC

・水晶振動子使用時の外付け部品(パスコンや抵抗)は、使用される振動子に最適な部品を選択する。

- 電源は3.5.1項の基板設計推奨ルールに従う。

- ・OSC 信号配線はマイコン実装面で 0.1 mm 配線幅にて配線し、同層および最下層で VSS シールドする。中間層には他信号も含め配線しない。同層の OSC 信号配線同士および他信号配線(特に、大電流が流れるパターンや高速信号パターン) と VSS シールドは 0.3mm の間隔を確保する。(図 15)

- ・水晶振動子は端子から極力近くに配置する(目安は 10mm 以内)。(図 15)

図 15. OSC の推奨設計イメージ図 (平面図/断面図)

#### 3.5.5 USB

- ・電源は3.5.1 項の基板設計推奨ルールに従う。但し、USBの VSS は他と分離し、1 点ショートとする。

- ・RREFの抵抗は、IC/パッケージ近傍に配置するが、パスコンとは並列に配置しない。

- ・RREFの抵抗含む配線は、同層/隣接層に渡り USBAVSS でシールドする。シールド出来ない場合、他信号と隣接並走させない。極力交差もさせない。極力間隔を離す。

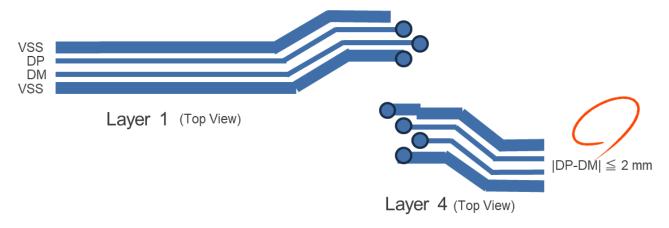

- ・差動信号(DP,DM)は、差動インピーダンス 90  $\Omega$  ±10 %でペア配線(等長,平行,等幅,同曲げ数,同 TH数)設計する。配線長差の目安は 2 mm 以内。USBVSS でシールドする(図 16)。シールド出来ない場合、他信号(特に、大電流が流れるパターンや高速信号パターン)と隣接並走させない。極力交差もさせない。隣接層のスロット/スリットも回避する。

図 16. USB/差動対の推奨設計イメージ図(平面図)

## 3.5.6 Analog

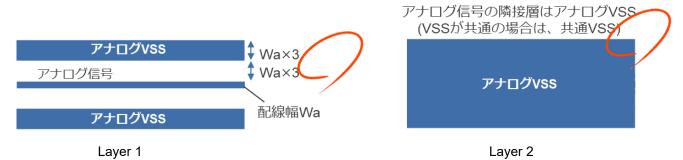

- ・アナログ端子の信号配線は Min 配線幅で且つ、電源/VSS/他信号(特に大電流が流れるパターンや高速信号パターン)と同層/隣接層含め隣接並走させず、アナログ VSS でシールドする。アナログ VSS シールド配線幅はアナログ信号配線幅の 3 倍以上、アナログ信号配線とアナログ VSS シールドの間隔は配線幅の 3 倍もしくは隣接層間との 3 倍を目安に確保する(図 17)。

- ・ローパスフィルタを挿入する場合は、搭載アナログ仕様に従う。

図 17. Analog の推奨設計イメージ図:シールド配線の例(平面図)

# 3.6ボールからの配線引き出し例

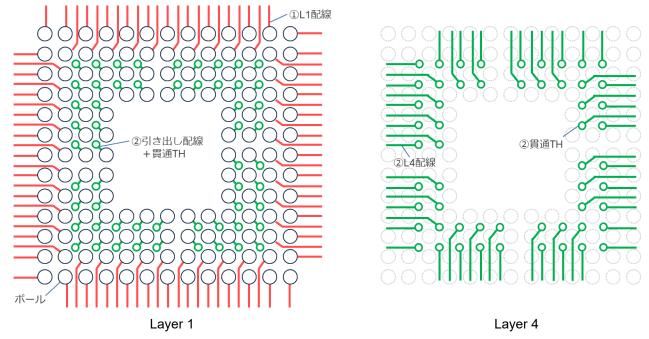

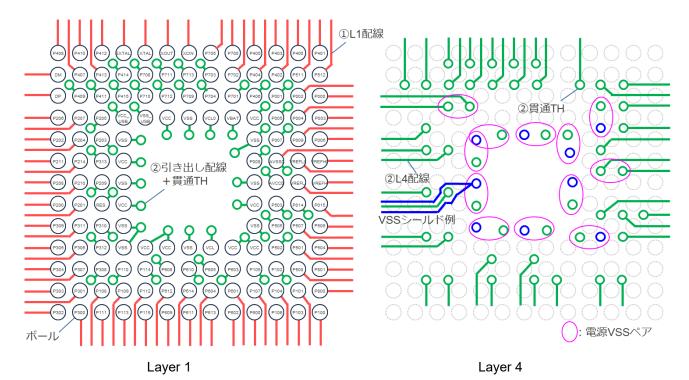

3.4 項の基本的な基板配線の思想と 3.5 項の基板設計推奨ルールに従い、部品配置(未図示)も考慮した 貫通 TH 位置と Layer 1, Layer 4 の配線引き出し例を図 18(RA6Mx/64BGA 例),図 19(RA6Mx/144BGA 例)に示す。電源は、必要数のパスコンをボール直近の Layer 4 に実装できるように VSS とペア隣接とな るよう貫通 TH 配置を検討することを推奨する。図中のマジェンダ色丸が電源と VSS の貫通 TH のペアの例 である。

Layer 1 Layer 4

図 18. 64 (8×8) BGA フルグリッドの Layer 1 と Layer 4 の引き出し配線例(平面図)

図 19. 144 (13×13) BGA 外周 4Row の Layer 1 と Layer 4 の引き出し配線例(平面図)

# Revision history

|      |               | Description |               |

|------|---------------|-------------|---------------|

| Rev. | Date          | Page        | Summary       |

| 1.00 | Apr. 23, 2024 | -           | First release |

| 2.00 | Sep. 17, 2025 | 7           | 表 3, 新製品を追加   |

#### 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意事項については、本ドキュメントおよびテクニカルアップデートを参照してください。

#### 1. 静電気対策

CMOS 製品の取り扱いの際は静電気防止を心がけてください。CMOS 製品は強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、当社が出荷梱包に使用している導電性のトレーやマガジンケース、導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。また、CMOS 製品を実装したボードについても同様の扱いをしてください。

#### 2. 電源投入時の処置

電源投入時は、製品の状態は不定です。電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。外部 リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の状態は保証できません。同様に、内蔵パワーオン リセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

#### 3. 電源オフ時における入力信号

当該製品の電源がオフ状態のときに、入力信号や入出力プルアップ電源を入れないでください。入力信号や入出力プルアップ電源からの電流注入により、誤動作を引き起こしたり、異常電流が流れ内部素子を劣化させたりする場合があります。資料中に「電源オフ時における入力信号」についての記載のある製品は、その内容を守ってください。

#### 4. 未使用端子の処理

未使用端子は、「未使用端子の処理」に従って処理してください。CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。

#### 5. クロックについて

リセット時は、クロックが安定した後、リセットを解除してください。プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子(または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

#### 6. 入力端子の印加波形

入力ノイズや反射波による波形歪みは誤動作の原因になりますので注意してください。CMOS 製品の入力がノイズなどに起因して、V<sub>IL</sub> (Max.) から V<sub>IH</sub> (Min.) までの領域にとどまるような場合は、誤動作を引き起こす恐れがあります。入力レベルが固定の場合はもちろん、V<sub>IL</sub> (Max.) から V<sub>IH</sub> (Min.) までの領域を通過する遷移期間中にチャタリングノイズなどが入らないように使用してください。

#### 7. リザーブアドレス (予約領域) のアクセス禁止

リザーブアドレス (予約領域) のアクセスを禁止します。アドレス領域には、将来の拡張機能用に割り付けられている リザーブアドレス (予約領域) があります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

#### 8. 製品間の相違について

型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。同じグループのマイコンでも型名が違うと、フラッシュメモリ、レイアウトパターンの相違などにより、電気的特性の範囲で、特性値、動作マージン、ノイズ耐量、ノイズ幅射量などが異なる場合があります。型名が違う製品に変更する場合は、個々の製品ごとにシステム評価試験を実施してください。

#### ご注意書き

- 1. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。回路、ソフトウェアおよびこれらに関連する情報を使用する場合、お客様の責任において、お客様の機器・システムを設計ください。これらの使用に起因して生じた損害(お客様または第三者いずれに生じた損害も含みます。以下同じです。)に関し、当社は、一切その責任を負いません。

- 2. 当社製品または本資料に記載された製品データ、図、表、プログラム、アルゴリズム、応用回路例等の情報の使用に起因して発生した第三者の特許 権、著作権その他の知的財産権に対する侵害またはこれらに関する紛争について、当社は、何らの保証を行うものではなく、また責任を負うもので はありません。

- 3. 当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 4. 当社製品を組み込んだ製品の輸出入、製造、販売、利用、配布その他の行為を行うにあたり、第三者保有の技術の利用に関するライセンスが必要となる場合、当該ライセンス取得の判断および取得はお客様の責任において行ってください。

- 5. 当社製品を、全部または一部を問わず、改造、改変、複製、リバースエンジニアリング、その他、不適切に使用しないでください。かかる改造、改変、複製、リバースエンジニアリング等により生じた損害に関し、当社は、一切その責任を負いません。

- 6. 当社は、当社製品の品質水準を「標準水準」および「高品質水準」に分類しており、各品質水準は、以下に示す用途に製品が使用されることを意図 しております。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット等

高品質水準:輸送機器(自動車、電車、船舶等)、交通制御(信号)、大規模通信機器、金融端末基幹システム、各種安全制御装置等 当社製品は、データシート等により高信頼性、Harsh environment 向け製品と定義しているものを除き、直接生命・身体に危害を及ぼす可能性のある機器・システム(生命維持装置、人体に埋め込み使用するもの等)、もしくは多大な物的損害を発生させるおそれのある機器・システム(宇宙機器と、海底中継器、原子力制御システム、航空機制御システム、プラント基幹システム、軍事機器等)に使用されることを意図しておらず、これらの用途に使用することは想定していません。たとえ、当社が想定していない用途に当社製品を使用したことにより損害が生じても、当社は一切その青年を負いません。

- 7. あらゆる半導体製品は、外部攻撃からの安全性を 100%保証されているわけではありません。当社ハードウェア/ソフトウェア製品にはセキュリティ対策が組み込まれているものもありますが、これによって、当社は、セキュリティ脆弱性または侵害(当社製品または当社製品が使用されているシステムに対する不正アクセス・不正使用を含みますが、これに限りません。) から生じる責任を負うものではありません。当社は、当社製品または当社製品が使用されたあらゆるシステムが、不正な改変、攻撃、ウイルス、干渉、ハッキング、データの破壊または窃盗その他の不正な侵入行為(「脆弱性問題」といいます。) によって影響を受けないことを保証しません。当社は、脆弱性問題に起因しまたはこれに関連して生じた損害について、一切責任を負いません。また、法令において認められる限りにおいて、本資料および当社ハードウェア/ソフトウェア製品について、商品性および特定目的との合致に関する保証ならびに第三者の権利を侵害しないことの保証を含め、明示または黙示のいかなる保証も行いません。

- 8. 当社製品をご使用の際は、最新の製品情報(データシート、ユーザーズマニュアル、アプリケーションノート、信頼性ハンドブックに記載の「半導体デバイスの使用上の一般的な注意事項」等)をご確認の上、当社が指定する最大定格、動作電源電圧範囲、放熱特性、実装条件その他指定条件の範囲内でご使用ください。指定条件の範囲を超えて当社製品をご使用された場合の故障、誤動作の不具合および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めていますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は、データシート等において高信頼性、Harsh environment 向け製品と定義しているものを除き、耐放射線設計を行っておりません。仮に当社製品の故障または誤動作が生じた場合であっても、人身事故、火災事故その他社会的損害等を生じさせないよう、お客様の責任において、冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、お客様の機器・システムとしての出荷保証を行ってください。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様の機器・システムとしての安全検証をお客様の責任で行ってください。

- 10. 当社製品の環境適合性等の詳細につきましては、製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。かかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器・システムに使用することはできません。当社製品および技術を輸出、販売または移転等する場合は、「外国為替及び外国貿易法」その他日本国および適用される外国の輸出管理関連法規を遵守し、それらの定めるところに従い必要な手続きを行ってください。

- 12. お客様が当社製品を第三者に転売等される場合には、事前に当該第三者に対して、本ご注意書き記載の諸条件を通知する責任を負うものといたします

- 13. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを禁じます。

- 14. 本資料に記載されている内容または当社製品についてご不明な点がございましたら、当社の営業担当者までお問合せください。

- 注 1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社が直接的、間接的 に支配する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

(Rev.5.0-1 2020.10)

#### 本社所在地

〒135-0061 東京都江東区豊洲 3-2-24 (豊洲フォレシア)

www.renesas.com

# 商標について

ルネサスおよびルネサスロゴはルネサス エレクトロニクス株式会社の 商標です。すべての商標および登録商標は、それぞれの所有者に帰属 します。

#### お問合せ窓口

弊社の製品や技術、ドキュメントの最新情報、最寄の営業お問合せ窓口に関する情報などは、弊社ウェブサイトをご覧ください。

www.renesas.com/contact/