# RENESAS

# USER MANUAL

Operation of the HC5503C, HC5503T Family of SLICs Evaluation Board (HC5503XEVAL1)

## Features

- One Evaluation Board for Performance Testing of the HC5503C, HC5503J and HC5503T Family of SLICs

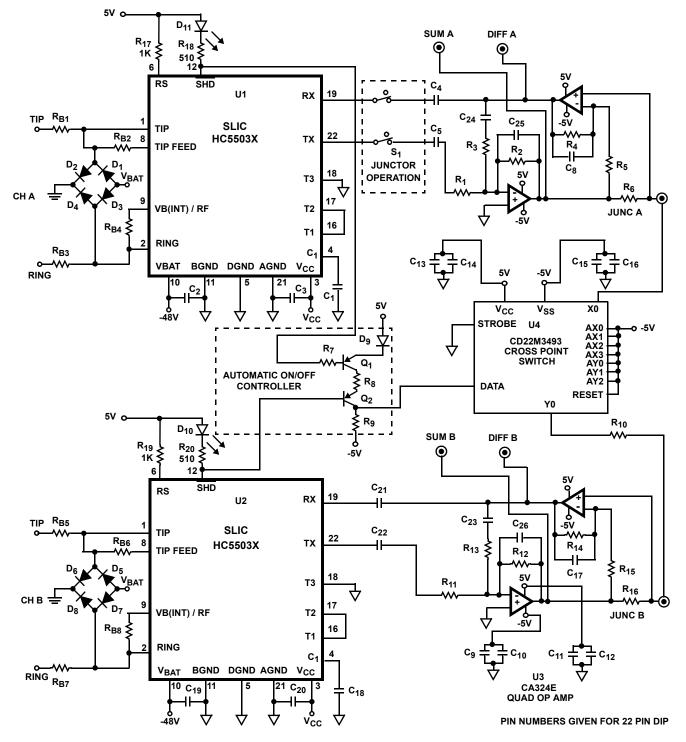

- Includes On-Board Op Amp and Cross Point Switch for Evaluation of "Junctor" Applications

- Monitoring of Switch Hook Detect (SHD) via On Board LED

- Automatic On/Off Controller for Cross Point Switch Connection

# Functional Description

#### **Evaluation Board**

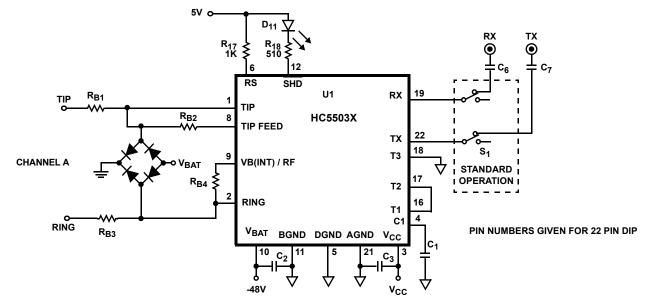

To facilitate testing of all 3 parts on one evaluation board, the board is equipped with one Double Pole Double Throw (DPDT) toggle switch  $S_1$ . The DPDT switch determines the connection of the SLIC's Transmit (TX) and Receive (RX) outputs. The outputs are either connected to banana jacks TX or RX for full evaluation of the voice and DC feeding characteristics (reference Figure 4) or the Onboard Op Amp and Cross Point Switch for evaluation of the end-to-end application (reference Figure 6).

The HC5503C/J/T evaluation board is configured to match a 600 $\Omega$  line impedance via the tip and ring feed resistors  $R_{B1},$   $R_{B2},$   $R_{B3}$  and  $R_{B4}.$  Provided with the evaluation board are two generic HC5503X samples.

## HC5503C

The HC5503C is a low cost Subscriber Line Interface Circuit (SLIC), that replaces the components of an **unbalanced** discrete Analog circuit design.

## HC5503J

The HC5503J is a low cost Subscriber Line Interface Circuit (SLIC), that replaces discrete or thick film hybrid "Junctor" unbalanced design solutions [1].

## HC5503T

The HC5503T is a low cost Subscriber Line Interface Circuit (SLIC), that replaces the components of a discrete Transformer Analog circuit design.

# Power Requirements for the HC5503C/J/T

## **Power Supply Connections**

The HC5503C/J/T Evaluation Board requires three external power supplies. The SLIC is powered by two supplies  $V_{BAT} = -48V$  (Typ) and  $V_{CC} = +5V$ . The third supply ( $V_{EE} = -5V$ ) powers the external Op Amps and Cross Point Switch for the Junctor application.

## **Ground Connections**

The HC5503C/J/T evaluation board has tied the analog, digital and battery grounds to a common ground plane

designated GND. It is recommended that the analog, digital and battery grounds of the SLIC be tied together as close to the device pins as possible. The three external power supplies should each be grounded to the evaluation board.

# **Getting Started**

Verify that the sample is oriented in its socket correctly. Correct orientation is with pin 1 pointing towards the onboard pin 1 designator located in the upper left hand corner of the sockets. (Reference the data sheet for location of device pin 1.)

# Verifying Basic SLIC Operation

The operation of the sample parts can be verified by performing 4 tests:

- 1. Power Supply Current Verification.

- 2. Normal Loop Feed Verification.

- 3. Tip and Ring Voltage Verification.

- 4. Gain Verification (4-wire to 2-wire).

The above 4 tests require the following equipment: a  $600\Omega$  load, a sine wave generator, an AC volt meter and two external supplies (V<sub>BAT</sub>, V<sub>CC</sub>).

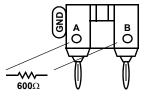

Application Tip: When terminating tip and ring, it is handy to assemble terminators using a Pomona MDP dual banana plug connector as the terminating resistor receptacle. Refer to Figure 1 for details.

FIGURE 1. TERMINATION ADAPTER

Using the termination shown in Figure 1 provides an unobtrusive technique for terminating tip and ring while still providing access to both signals using the banana jack feature of the MDP connector. Posts are also available that fit into holes A and B, providing a solderable connection for the terminating resistor.

# Test #1 Power Supply Current Verification

A quick check of evaluation board and the sample is to measure the supply currents. The readings should be similar to the values listed in Table 1. The measurements can be made using a series ammeter on each supply, or power supplies with current displays.

AN9813 Rev 1.00 November 1998

## Discussion

The currents measured include those of the SLIC and supporting circuitry (i.e., 2nd HC5503X SLIC, Op Amp, Channel A's LED, the Cross Point Switch and Transistors  $Q_1$  and  $Q_2$ ). For SLIC supply currents consult the applicable data sheet.

#### Setup

- 1. Connect the power supplies to the Evaluation board.

- 2. Set V<sub>BAT</sub> to -48V, V<sub>CC</sub> to +5V and Ground the V<sub>EE</sub> pin (V<sub>EE</sub> supply not required for this test).

- 3. Set the DPDT switch (S1) to standard operation. This connects the Transmit and Receive outputs to banana jacks TX and RX.

- 4. Terminate tip and ring Channel A with a 600Ω load (Channel B is disconnected during standard operation).

- 5. Measure the supply currents and compare to those in Table 1.

#### TABLE 1.

| HC5503C, HC5503J, HC5503T |                |          |

|---------------------------|----------------|----------|

| SUPPLY                    | <b>RL (</b> Ω) | TYP (mA) |

| V <sub>CC</sub> = +5V     | 600            | 10.9     |

| V <sub>BAT</sub> = -48V   | 600            | 33.5     |

# Test #2 Normal Loop Feed Verification

This test verifies loop current operation and loop current detection via the onboard LED.

#### Discussion

When power is applied to the SLIC a loop current will flow from tip to ring through the  $600\Omega$  load. Loop current detection occurs when this loop current triggers an internal detector that pulls the output of SHD low, illuminating the LED through the +5V supply.

#### Setup

- 1. Connect the power supplies to the Evaluation board.

- 2. Set V<sub>BAT</sub> to -48V, V<sub>CC</sub> to +5V and Ground the V<sub>EE</sub> pin (V<sub>EE</sub> supply not required for this test).

- 3. Set the DPDT switch (S1) to standard operation. This connects the Transmit and Receive outputs to banana jacks TX and RX.

- 4. Terminate tip and ring Channel A with a  $600\Omega$  load (Channel B is disconnected during standard operation).

#### Verification:

- 1. The  $\overline{\text{SHD}}$  LED is on when tip and ring are terminated with 600 $\Omega$ .

- 2. The SHD LED is off when tip and ring are an open circuit.

## Test #3 Tip and Ring Voltage Verification

This test verifies the tip and ring voltages.

## Setup

- 1. Connect the power supplies to the Evaluation board.

- 2. Set  $V_{BAT}$  to -48V,  $V_{CC}$  to +5V and Ground the  $V_{EE}$  pin ( $V_{EE}$  supply not required for this test).

- Set the DPDT switch (S1) to standard operation. This connects the Transmit and Receive outputs to banana jacks TX and RX.

- 4. Terminate tip and ring Channel A with a 600Ω load (Channel B is disconnected during standard operation).

- 5. Measure tip and ring voltages with respect to ground and compare to those in Table 2.

| BATTERY                 | TIP TYP (V) | RING TYP (V) |

|-------------------------|-------------|--------------|

| V <sub>BAT</sub> = -48V | -12.8       | -30.6        |

# Test #4 Gain Verification (4-Wire to 2-Wire)

This test will verify the SLIC is operating properly and that the 4-wire to 2-wire gain is 1.0 or 0.0dB.

#### Discussion

When terminated with  $600\Omega$  load, the SLIC will exhibit unity gain from the RX input pin to across tip and ring (VTR). When an open circuit exists, a mismatch occurs and the tip to ring voltage doubles. The dB gain is calculated in Equation 1.

$$dB = 20 \log \frac{V_{TR}}{V_{RX}}$$

(EQ. 1)

#### Setup

- 1. Connect the power supplies to the Evaluation board.

- 2. Set  $V_{BAT}$  to -48V,  $V_{CC}$  to +5V and Ground the  $V_{EE}$  pin ( $V_{EE}$  supply not required for this test).

- 3. Set the DPDT switch (S1) to standard operation. This connects the Transmit and Receive outputs to banana jacks TX and RX.

- 4. Terminate tip and ring Channel A with a 600Ω load (Channel B is disconnected during standard operation).

- 5. Connect a sine wave generator, referenced to ground, to the RX input.

- 6. Set the generator for  $1V_{RMS}$  at 1kHz.

- 7. Connect an AC voltmeter across tip and ring.

## Verification

- 1. Tip to ring AC voltage of  $1V_{\mbox{RMS}}$  when terminated.

- 2. Tip to ring AC voltage of  $2V_{RMS}$  when not terminated.

# Verifying Junctor Operation

The operation of the Junctor application circuit using the 2 HC5503X samples provided can be verified by performing 4 tests:

- 1. Channel to Channel Transhybrid Balance.

- 2. Inter-Channel Transhybrid Balance.

- 3. Channel to Channel Gain.

- 4. Intra-Channel Transhybrid Balance with different loads.

The above 4 tests require the following equipment: Two  $600\Omega$  loads, a sine wave generator, an AC volt meter and three external supplies (V<sub>BAT</sub>, V<sub>CC</sub>, V<sub>EE</sub>).

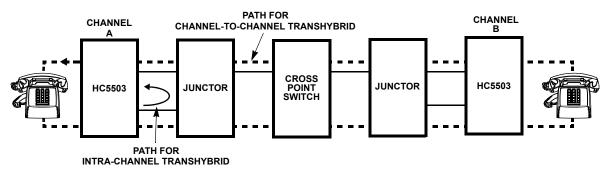

## **Definition of Junctor Circuit**

The function of the Junctor application circuit is to convert a two port network with a Transmit Output (TX) and a Receive Input

(RX) into a one-port network. The conversion to a one-port network now makes it easy to connect phone lines in a small PBX or Key System through a single Cross Point. This conversion is accomplished by the connection of a Differential Amplifier and a Summing Amplifier. The Differential Amplifier and Summing Amplifier are used to cancel the return signal and prevent echo (reference Figure 6). In this one-port network, echo can occur in two ways: Channel to Channel and Intra-Channel. Reference Figure 5 for signal path for both channelto-channel and intra-channel signals.

# Test #5 Channel to Channel Transhybrid

## Definition

The removal of the receive signal from the transmit signal, to prevent an echo on the transmit side is defined as Channel to Channel Transhybrid Balance. In other words, Channel to Channel Transhybrid signals occur when the receive signal (from Channel B) is retransmitted along with the transmit signal of Channel A back to Channel B.

Channel to Channel Transhybrid Balance is performed by the Summing Amplifier (the output of this amplifier is SUM A and SUM B in Figure 6).

## Setup

- 1. Connect the power supplies to the Evaluation board.

- 2. Set  $V_{BAT}$  to -48V,  $V_{CC}$  to +5V and  $V_{EE}$  to -5V.

- 3. Set the DPDT switch (S1) to Junctor operation. This connects the Onboard Op Amp, Cross Point Switch and the second HC5503X SLIC to the Transmit and Receive outputs of Channel A.

- 4. Terminate tip and ring of **both** Channel A and Channel B with a  $600\Omega$  load.

- 5. Connect a sine wave generator in parallel with the  $600\Omega$  load across tip and ring of Channel A. The output of this generator needs to be floating.

- 6. Set the generator for  $1V_{RMS}$  at 1kHz.

- 7. Connect an AC volt meter between test point DIFF B and ground. This will measure the AC voltage at the output to the Differential Amplifier (DIFF B).

- 8. Connect an AC volt meter between test point SUM B and ground. This will measure the AC voltage at the output of the Summing Amplifier (SUM B).

- 9. The Channel to Channel Transhybrid Balance is calculated using the following formula in Equation 2.

$$dB = 20 \log \frac{SUMB}{DIFFB}$$

(EQ. 2)

- 10. To measure Channel to Channel Transhybrid Balance on Channel A, connect the sine wave generator in parallel with the  $600\Omega$  load across tip and ring of Channel B and repeating steps 7 through 9 in a similar fashion. Voltage measurements taken at DIFF A and SUM A. Results for both Channels should be the same.

- 11. Compare results to that listed in Table 3.

# Test #6 Intra-Channel Transhybrid

## Definition

Intra-Channel Transhybrid Balance is defined as the removal of the transmit signal from the receive signal, and thereby cancellation of echo, within a channel. In other words, Intra-Channel Transhybrid Balance is when the transmit signal from Channel A is feed back into the input of Channel A.

Intra-Channel Transhybrid Balance is performed by the Differential Amplifier (the output of this amplifier is DIFF A and DIFF B in Figure 6).

Calculation of resistor value (R<sub>4</sub>) for optimum Intra-Channel Transhybrid Balance is discussed in Test #8.

## Setup

- 1. Connect the power supplies to the Evaluation board.

- 2. Set V<sub>BAT</sub> to -48V, V<sub>CC</sub> to +5V and V<sub>EE</sub> to -5V.

- 3. Set the DPDT switch (S1) to Junctor operation. This connects the Onboard Op Amp, Cross Point Switch and the second HC5503X SLIC to the Transmit and Receive outputs of Channel A.

- 4. Terminate tip and ring of **both** Channel A and Channel B with a  $600\Omega$  load.

- 5. Connect a sine wave generator in parallel with the  $600\Omega$  load across tip and ring of Channel A. The output of this generator needs to be floating.

- 6. Set the generator for  $1V_{RMS}$  and 1kHz.

- 7. Connect an AC volt meter between test point SUM A and ground. This will measure the AC voltage at the input to the Differential Amplifier (SUM A).

- 8. Connect an AC volt meter between test point DIFF A and ground. This will measure the AC voltage at the output of the Differential Amplifier (DIFF A).

- 9. The Inter-Channel Transhybrid Balance is calculated using the following formula in Equation 3.

$$dB = 20 \log \frac{DIFFA}{SUMA}$$

(EQ. 3)

- 10. To measure Inter-Channel Transhybrid Balance on Channel B, connect the sine wave generator in parallel with the  $600\Omega$  load across tip and ring of Channel B and repeating steps 7 through 9 in a similar fashion. Voltage measurements taken at SUM B and DIFF B. Results for both Channels should be the same.

- 11. Compare results to that listed in Table 3.

TABLE 3.

| TEST                                                                          | SUM TYP<br>(V <sub>RMS</sub> ) | DIFF TYP<br>(V <sub>RMS</sub> ) | TRANSHYBRID<br>BALANCE (dB) |

|-------------------------------------------------------------------------------|--------------------------------|---------------------------------|-----------------------------|

| Channel to Channel<br>Transhybrid Balance<br>Channel A to B<br>Channel B to A | 18.45m<br>20.79m               | 1.009<br>1.007                  | -34.7<br>-33.7              |

| Intra-Channel<br>Transhybrid Balance<br>Channel A<br>Channel B                | 0.986<br>0.990                 | 64.9m<br>67.0m                  | -23.6<br>-23.4              |

# Test #7 Channel A to Channel B Gain

This demo board is configured to have a Channel to Channel gain of 1 or 0dB. This test will illustrate a procedure for calculating the proper  $R_4$  resistor value to achieve a Channel to Channel gain of 1 with any Cross Point or network used to connect the two line cards. Also included is an easy procedure to verify the calculations.

#### Discussion

Channel to Channel gain is dependent upon: the 2-wire to 4-wire and the 4-wire to 2-wire gains of the HC5503X being one, the gain setting resistors of the differential amplifier (R<sub>4</sub>, R<sub>5</sub>, R<sub>14</sub>, and R<sub>15</sub>), the resistance of the Cross Point Switch (Rx) and resistors R<sub>6</sub> and R<sub>16</sub> (Reference Figure 5). The resistance values of R<sub>6</sub> and R<sub>16</sub> are generally set to 604 $\Omega$  for impedance matching to a transformer line card. If impedance matching to a 600 $\Omega$  transformer is not a design requirement, then the values of R<sub>6</sub> and R<sub>16</sub> are not critical and can be set to match various impedances. It is important however, that R<sub>6</sub> equal R<sub>16</sub>.

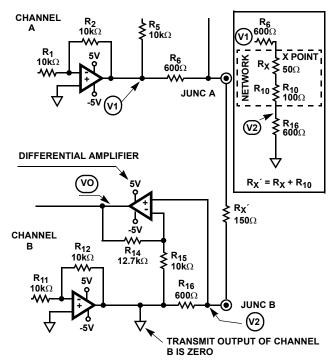

Figure 2 is a simplified version of the Junctor circuit and shows the critical components required to calculate the optimum  $R_{14}$ value to obtain a Channel A to Channel B gain of one. Because the 2-wire to 4-wire gain of the HC5503X is one, the voltage appearing at V1 is the tip to ring voltage of Channel A (Summing amplifier configured for a gain of one). The tip to ring voltage of Channel B is equal to the voltage at VO, because the 4-wire to 2-wire gain of the HC5503X is also one. Writing an equation for VO in terms of V1 will enable the gain to be set to one and the corresponding resistor values determined.

Equation 4 can be used to determine the output voltage of the differential amplifier, and therefore the tip to ring voltage of Channel B, in terms of the voltage at V2.

$$VO = V2 \left( 1 + \frac{R_{14}}{R_{15}} \right)$$

(EQ. 4)

The voltage at V2, with respect to V1, is:

$$V2 = \left(\frac{R_{16}}{R_6 + R_X + R_{10} + R_{16}}\right) V1$$

(EQ. 5)

Substituting Equation 5 into Equation 4 and defining  $R_X' = R_X + R_{10}$ . Where  $R_X'$  is the total network resistance connecting Junctor A and Junctor B input/outputs.

$$VO = V1 \left( \frac{R_{16}}{R_6 + R_X' + R_{16}} \right) \left( 1 + \frac{R_{14}}{R_{15}} \right)$$

(EQ. 6)

Dividing both sides by V1 yields an equation for Channel A to Channel B gain.

$$\frac{\text{VO}}{\text{V1}} = \frac{\text{ChannelB}}{\text{ChannelA}} = \left(\frac{\text{R}_{16}}{\text{R}_6 + \text{R}_X' + \text{R}_{16}}\right) \left(1 + \frac{\text{R}_{14}}{\text{R}_{15}}\right)$$

(EQ. 7)

Setting V0/V1 equal to one and rearranging to solve for  $R_{14}$  , assuming  $R_6$  =  $R_{16},$  yields Equation 8.

$$R_{14} = R_{15} \left( 1 + \frac{R_X}{R_6} \right)$$

(EQ. 8)

Equation 8 can be used for the calculation of  $R_{14}$  to achieve a Channel A to Channel B Gain of one. A similar analysis for the calculation of  $R_4$  to achieve a Channel B to Channel A gain of one is given in Equation 9.

$$R_4 = R_5 \left( 1 + \frac{R_X'}{R_6} \right)$$

(EQ. 9)

The value of R<sub>14</sub> and R<sub>4</sub> can now be determined for any network resistance. The network resistance is defined as the total resistance between the Junctor inputs/outputs. In the case of the demo board the network resistance is the resistance of the Cross Point Switch (50 $\Omega$ ) and R<sub>10</sub> (100 $\Omega$ ). If R<sub>1</sub> = R<sub>11</sub> = R<sub>2</sub> = R<sub>12</sub> = R<sub>5</sub> = R<sub>15</sub> = 10k $\Omega$ , R<sub>6</sub> = R<sub>16</sub> = 604 $\Omega$  and the Network = 150 $\Omega$  then R<sub>4</sub> = 12.48k $\Omega$ . Closest standard value is 12.7k $\Omega$ . If the Network resistance is equal to 50 $\Omega$  (Single CD22M3493 Cross Point), then R<sub>4</sub> = 10.83k $\Omega$ . Closest standard value is 10.7k $\Omega$ .

FIGURE 2. CHANNEL TO CHANNEL TRANSHYBRID BALANCE

#### Verification

The following procedure can be used to verify the above calculations.

#### Setup

- 1. Connect the power supplies to the Evaluation board.

- 2. Set V<sub>BAT</sub> to -48V, V<sub>CC</sub> to +5V and V<sub>EE</sub> to -5V.

- 3. Set the DPDT switch (S1) to Junctor operation. This connects the Onboard Op Amp, Cross Point Switch and the second HC5503X SLIC to the Transmit and Receive outputs of Channel A.

- 4. Terminate tip and ring of both Channel A and Channel B with a  $600\Omega$  load.

- 5. Connect a sine wave generator in parallel with the  $600\Omega$  load across tip and ring of Channel A. The output of this generator needs to be floating.

- 6. Set the generator for  $1V_{RMS}$  and 1kHz.

- 7. Measure the AC voltage across tip and ring (VTR) of both Channels A and B.

- 8. The Channel A to Channel B Gain is calculated using the following formula in Equation 10.

- $dB = 20 \log \frac{VTR(channelB)}{VTR(channelA)}$ (EQ. 10)

- 9. To measure Channel B to Channel A Gain connect the sine wave generator in parallel with the  $600\Omega$  load across tip and ring of Channel B and repeating steps 7 and 8 in a similar fashion. Results for both Channels should be about the same.

- 10. Compare results to that listed in Table 4.

TES

Channel A to Channel B

Channel B to Channel A

Gain

|    | IADLE 4.            |                     |

|----|---------------------|---------------------|

|    | TIP TO RING         | TIP TO RING         |

|    | CHANNEL A           | CHANNEL B           |

| ST | (V <sub>RMS</sub> ) | (V <sub>RMS</sub> ) |

1.0074

| Gain                              | 1.0035 | 1.0068 |  |

|-----------------------------------|--------|--------|--|

| Test #8 Intra-Channel Transhybrid |        |        |  |

| Balance with Different Loads      |        |        |  |

This evaluation board is configured to give the optimum Intra-Channel Transhybrid Balance for an impedance of  $150\Omega$  between the two Junctor inputs/outputs. This test will illustrate a procedure for calculating the proper R<sub>4</sub> and R<sub>14</sub> resistor values to optimize the Intra-Channel Transhybrid Balance when a different Cross Point or network is used. Also included is an easy procedure to verify the calculations.

#### Discussion

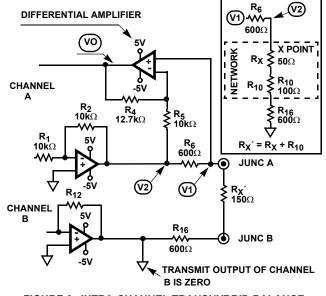

Intra-Channel Transhybrid Balance is performed by the Differential Amplifier (Reference Figure 3). The goal is to cancel all of the transmit signal of Channel A by the Differential Amplifier, so that none of the transmit signal is feed back into the receive terminal of channel A. The transmit signal can be cancelled by the differential amplifier by adjusting the value of resistor  $R_4$ . The value of  $R_4$  is dependent upon: the resistance value of  $R_6$ , the resistance of the network that connects the two Junctor inputs/outputs together (Cross Point +  $R_{10}$ ) and resistor  $R_{16}$ . Figure 3 is a simplified version of the Junctor circuit and shows the critical components required to calculate the optimum  $R_4$  value for Intra-Channel Transhybrid Balance.

Equation 11 is the characteristic equation for the output voltage of the Differential Amplifier.

$$VO = V1 \left(1 + \frac{R_4}{R_5}\right) - V2 \frac{R_4}{R_5}$$

(EQ. 11)

GAIN

(dB)

-0.01

-0.03

1.0063

The voltage at V2, with respect to V1, where  $R_X$  = resistance of Cross Point Switch is:

$$V2 = \left(\frac{R_X + R_{10} + R_{16}}{R_X + R_{10} + R_{16} + R_6}\right) V1$$

(EQ. 12)

Substituting Equation 12 into Equation 11, setting V0 equal to Zero, defining  $R_X' = R_X + R_{10}$  and rearranging to solve for R4:

$$R_4 = \frac{R_5(R_X' + R_{16})}{R_{16}}$$

(EQ. 13)

Equation 13 can be used for the calculation of  $R_4$  to achieve a good Intra-Channel Transhybrid Balance in Channel A. A similar analysis for Channel B is given in Equation 14.

$$R_{14} = \frac{R_{15}(R_X' + R_6)}{R_6}$$

(EQ. 14)

The value of R<sub>4</sub> and R<sub>14</sub> can now be determined for any network resistance. In the case of the demo board, the network resistance (R<sub>X</sub><sup>'</sup>) is the resistance of the Cross Point Switch (50 $\Omega$ ) and R10 (100 $\Omega$ ). If R<sub>1</sub> = R<sub>11</sub> = R<sub>2</sub> = R<sub>12</sub> = R<sub>5</sub> = R<sub>15</sub> = 10k $\Omega$ , R<sub>6</sub> = R<sub>16</sub> = 604 $\Omega$  and the Network = 150 $\Omega$  then R<sub>4</sub> = 12.48k $\Omega$ . Closest standard value is 12.7k $\Omega$ . If the Network resistance is equal to 50 $\Omega$  (Single CD22M3493 Cross Point), then R<sub>4</sub> = 10.83k $\Omega$ . Closest standard value is 10.7k $\Omega$ .

Notice that the calculated value of  $R_4$  and  $R_{14}$  for both Channel to Channel and Intra-channel are the same. This is because the gain from Channel to Channel is set for one. If the Channel to Channel gain was set to anything other than one, the Intra-channel Transhybrid Balance would become unacceptable. Proper operation of this circuit requires that the Channel to Channel gain be set to one.

FIGURE 3. INTRA-CHANNEL TRANSHYBRID BALANCE

**TABLE 6. JUNCTOR CIRCUIT**

#### Verification

The following procedure can be used to verify the above calculations.

#### Setup

- 1. Replace resistors R<sub>4</sub> and R<sub>14</sub> with a 10.7k $\Omega$  resistor as calculated above. Note, R<sub>14</sub> is Channel B's equivalent of Channel A's R<sub>4</sub>.

- 2. Connect the power supplies to the Evaluation board.

- 3. Set V<sub>BAT</sub> to -48V, V<sub>CC</sub> to +5V and V<sub>EE</sub> to -5V.

- Set the DPDT switch (S<sub>1</sub>) to Junctor operation. This connects the Onboard Op Amp, Cross Point Switch and the second HC5503J SLIC to the Transmit and Receive outputs of Channel A.

- 5. Replace resistor  $R_{10}$  with a short. This will result in a network resistance of  $50\Omega$  total.

- 6. Terminate tip and ring of **both** Channel A and Channel B with a  $600\Omega$  load.

- 7. Connect a sine wave generator in parallel with the  $600\Omega$  load across tip and ring of Channel A. The output of this generator needs to be floating.

- 8. Set the generator for 1V<sub>RMS</sub> and 1kHz.

- 9. Connect an AC volt meter between test point SUM A and ground. This will measure the AC voltage at the input to the Differential Amplifier (SUM A).

- 10. Connect an AC volt meter between test point DIFF A and ground. This will measure the AC voltage at the output of the Differential Amplifier (DIFF A).

- 11. The Intra-Channel Transhybrid Balance is calculated using the following formula in Equation 15.

$$dB = 20 \log \frac{DIFFA}{SUMA}$$

(EQ. 15)

- 12. To measure Intra-Channel Transhybrid Balance on Channel B, connect the sine wave generator in parallel with the  $600\Omega$  load across tip and ring of Channel B and repeating steps 8 through 11 in a similar fashion. Voltage measurements taken at SUM B and DIFF B. Results for both Channels should be the same.

- 13. Compare results to that listed in Table 3 section "Intra-Channel Transhybrid Balance."

## Functional Circuit Component Descriptions

A brief description of each component is provided below. The components will be grouped by function to provide further insight into the operation of the HC5503C/J/T board.

#### TABLE 5. TWO WIRE SIDE, TIP AND RING

| $\begin{array}{c} R_{B1}, R_{B2}, \\ R_{B3}, R_{B4}, \\ R_{B5}, R_{B6}, \\ R_{B7}, R_{B8} \end{array}$ | Feed resistors (R <sub>B1</sub> , R <sub>B2</sub> , R <sub>B3</sub> , R <sub>B4</sub> , R <sub>B5</sub> , R <sub>B6</sub> , R <sub>B7</sub> and R <sub>B8</sub> ) that set the 2-wire impedance to $600\Omega$ . R <sub>B2</sub> , R <sub>B4</sub> , R <sub>B6</sub> and R <sub>B8</sub> are used for loop current detection. R <sub>B1</sub> , R <sub>B3</sub> , R <sub>B5</sub> and R <sub>B7</sub> are used for current limiting during a surge event. |

|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $D_1, D_2, D_3, D_4, D_5, D_6, D_7, D_8$                                                               | Secondary surge protection.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CA324E                                                                                                 | Intersil Quad Op Amp.                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $R_1, R_2, R_3, R_{11}, R_{12}, R_{13}$                                                                | Transhybrid Balance and Gain setting resistors for the Summing Amplifiers.                                                                                                                                                                                                                                                                                                                                           |

| $R_4, R_5, R_{14}, R_{15}$                                                                             | Transhybrid Balance and Gain setting resistors for the Differential Amplifiers.                                                                                                                                                                                                                                                                                                                                      |

| $\begin{array}{c} C_8, C_{17}, C_{25}, \\ C_{26}, C_{23}, C_{24} \end{array}$                          | Compensation Capacitors to roll of the high frequency gain of the Summing and Differential Amplifier. $C_{23}$ and $C_{24}$ prevent a DC loop.                                                                                                                                                                                                                                                                       |

| R <sub>6</sub> , R <sub>16</sub>                                                                       | Provides a $600\Omega$ termination looking into the Junctor input.                                                                                                                                                                                                                                                                                                                                                   |

| R <sub>10</sub>                                                                                        | Series resistor to bring the total resistance of the "Network" to $150\Omega$ . The "Network" is defined as the total resistance that connects Junctor A to Junctor B.                                                                                                                                                                                                                                               |

| $C_4, C_5, C_6, C_7, C_{21}, C_{22}$                                                                   | AC decoupling capacitors for the HC5503X<br>Transmit (TX) and Receive (RX) outputs.                                                                                                                                                                                                                                                                                                                                  |

| CDM22M3493                                                                                             | Cross Point Switch. The resistance of the switch (X0 to Y0) is approximately $50\Omega$ .                                                                                                                                                                                                                                                                                                                            |

| S <sub>1</sub>                                                                                         | DPDT Switch used to connect the SLIC's Transmit<br>and Receive outputs of Channel A to either banana<br>jacks TX and RX or the onboard Op Amp and<br>Cross Point for evaluation of the Junctor circuit.                                                                                                                                                                                                              |

| Q <sub>1</sub> , Q <sub>2</sub> , R <sub>7</sub> ,<br>R <sub>8</sub> , R <sub>9</sub> , D <sub>9</sub> | Automatic on/off controller of the Cross Point<br>Switch. This circuit senses the SHD outputs of both<br>SLICs. If both SLICs are in the off-hook condition,<br>then the Cross Point Switch is activated and the<br>Junctor A and Junctor B outputs are connected<br>together. If either SLIC is in the On-hook condition,<br>the Cross Point Switch is off and Junctor A and<br>Junctor B outputs are disconnected. |

#### TABLE 7. FILTER CAPACITOR

| C <sub>1</sub> , C <sub>18</sub> | $C_1$ and $C_{18}$ are required for proper operation of the |

|----------------------------------|-------------------------------------------------------------|

|                                  | SLIC's loop current limit function.                         |

#### TABLE 8. SUPPLY DECOUPLING CAPACITORS

| C <sub>2</sub> , C <sub>3</sub> , | Supply decoupling capacitors. |

|-----------------------------------|-------------------------------|

| C <sub>9</sub> -C <sub>16</sub> , |                               |

| C <sub>19</sub> , C <sub>20</sub> |                               |

#### TABLE 9. SHD LEDs

| $R_9, R_{20}, D_9,$ | $R_9 a$ nd $R_{20}$ are the Current limiting resistors for the |

|---------------------|----------------------------------------------------------------|

| D <sub>10</sub>     | SHD LEDs (D <sub>9</sub> and D <sub>10</sub> ).                |

#### TABLE 10. PULLUP RESISTORS

|  | Pull up resistors ( $R_{17}$ , $R_{19}$ ). Required for proper operation of the SLIC. |  |

|--|---------------------------------------------------------------------------------------|--|

|--|---------------------------------------------------------------------------------------|--|

#### Reference

[1] HC5503J - Future Product. For more information call Don LaFontaine at (321) 729-5604.

Schematic Diagram for Standard Operation

FIGURE 5. INTRA-CHANNEL AND CHANNEL-TO-CHANNEL PATHS THROUGH THE SYSTEM

| HC5503C/J/T E | Evaluation l | Board Parts | List | _ |

|---------------|--------------|-------------|------|---|

|               |              |             |      |   |

| COMPONENT                                                                                                                                        | VALUE         | TOLERANCE          | RATING | COMPONENT                                                                                  | VALUE                   | TOLERANCE | RATING   |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------|--------|--------------------------------------------------------------------------------------------|-------------------------|-----------|----------|

| SLIC                                                                                                                                             | U1<br>U2      | HC5503X<br>HC5503X |        | C <sub>2</sub> , C <sub>19</sub>                                                           | 0.01µF                  | 20%       | 100V     |

| Quad Op Amp                                                                                                                                      | U3            | CA324E             |        | C <sub>3</sub> , C <sub>20</sub>                                                           | 0.01µF                  | 20%       | 50V      |

| Cross Point Switch                                                                                                                               | U4            | CD22M3493          |        | $C_4, C_5, C_6, C_7, C_{21}, C_{22}$                                                       | 0.47μF                  | 20%       | 50V      |

| $R_1, R_2, R_3, R_5, R_9, R_{11}, R_{12}, R_{13}, R_{15}$                                                                                        | 10kΩ          | 1%                 | 1/4W   | C <sub>8</sub> , C <sub>17</sub> , C <sub>25</sub> , C <sub>26</sub>                       | .001µF                  | 10%       | 50V      |

| R <sub>B1</sub> , R <sub>B2</sub> , R <sub>B3</sub> , R <sub>B4</sub> ,<br>R <sub>B5</sub> , R <sub>B6</sub> , R <sub>B7</sub> , R <sub>B8</sub> | 150Ω          | 1%                 | 2W     | C <sub>23</sub> , C <sub>24</sub>                                                          | 0.82µF                  | 20%       | 50V      |

| R <sub>8</sub>                                                                                                                                   | 5.62kΩ        | 1%                 | 1/4W   | C <sub>9</sub> , C <sub>11</sub> , C <sub>13</sub> , C <sub>15</sub><br>Supply Decoupling  | 0.1µf                   | 10%       | 50V      |

| R <sub>4</sub> , R <sub>14</sub>                                                                                                                 | 12.7kΩ        | 1%                 | 1/4W   | C <sub>10</sub> , C <sub>12</sub> , C <sub>14</sub> , C <sub>16</sub><br>Supply Decoupling | 0.01µF                  | 10%       | 50V      |

| R <sub>6</sub> , R <sub>16</sub>                                                                                                                 | 604Ω          | 1%                 | 1/4W   | $D_1, D_2, D_3, D_4, D_5, D_6, D_7, D_8, D_{11}$                                           | 1N40007                 | n/a       | 100V, 1A |

| R <sub>18</sub> , R <sub>20</sub>                                                                                                                | 510Ω          | 5%                 | 1/4W   | D <sub>9</sub> , D <sub>10</sub>                                                           | LED, RED                |           |          |

| R <sub>7</sub> , R <sub>17</sub> , R <sub>19</sub>                                                                                               | $1.0 k\Omega$ | 5%                 | 1/4W   | S <sub>1</sub>                                                                             | SPDT CO PC Mount Switch |           | vitch    |

| C <sub>1</sub> , C <sub>18</sub>                                                                                                                 | 0.33µF        | 10%                | 50V    | R10                                                                                        | 100Ω                    | 1%        | 1/4W     |

AN9813 Rev 1.00 November 1998

Schematic Diagram for Junctor

FIGURE 6. APPLICATION SCHEMATIC FOR JUNCTOR OPERATION

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard" Computers: office equipment: communications equipment: test and measurement equipment: audio and visual equipment: home electronic appliances; machine tools; personal electronic equipment: industrial robots: etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc. Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics oroducts outside of such specified ranges

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Plea e contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

#### SALES OFFICES

#### **Renesas Electronics Corporation**

http://www.renesas.com

Refer to "http://www.renesas.com/" for the latest and detailed information Renesas Electronics America Inc. 1001 Murphy Ranch Road, Milpitas, CA 95035, U.S.A. Tel: +1-408-432-8888, Fax: +1-408-434-5351 Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004 Renesas Electronics Europe Limited Dukes Meadow, Miliboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tei: +44-1628-651-700, Fax: +44-1628-651-804 Renesas Electronics Europe GmbH Arcadiastrasse 10, 40472 Düsseldorf, Germar Tel: +49-211-6503-0, Fax: +49-211-6503-1327 Renesas Electronics (China) Co., Ltd. Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679 Renesas Electronics (Shanghai) Co., Ltd. Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0888, Fax: +86-21-2226-0999 Renesas Electronics Hong Kong Limited Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +852-2265-6688, Fax: +852 2886-9022 Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670 Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300 Renesas Electronics Malaysia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amco Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Unit 1207, Block B, Menara Amcorp, Amcorp Tel: +60-3-7955-9390, Fax: +60-3-7955-9510 Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777 Renesas Electronics Korea Co., Ltd. 17F, KAMCO Yangjae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tei: +822-558-3737, Fax: +822-558-5338