Development of a Voltage Feedback Spice Op-Amp Macromodel

AN1685 Rev.0.00 Feb 20, 2012

# Introduction

A voltage-feedback amplifier macromodel has been developed that simulates the most common effects, such as transient response, frequency response, voltage noise and input/output slew rate limiting. Detailed descriptions of each stage in the model will be presented with examples of model performance and correlation to actual device behavior.

Macromodels are developed for the customer instead of releasing full transistor schematics. Of course, the most accurate simulations are conducted from fully-extracted 3-D device models. Not only would it be impractical to share these models because of the need to accommodate the numerous simulation platforms, but also because of proprietary reasons.

One of the first op-amp macromodel techniques was developed by Boyle in 1974 and used only two transistors, a few diodes and linear elements [1]. Linear elements like resistors, capacitors, inductor and voltage/current control sources simulate much faster than active elements and are used to provide poles, zeros and any gain. For a DC model, a voltage-controlled voltage source can represent the amplifier while resistances can be added to better represent the input and output impedance. Capacitors, inductors, diodes and transistors can then provide the proper AC response. If you want more information on the development of simulation models, see Alexander and Bowers [2] and [3]. We will follow their model here.

#### **The ISL28133**

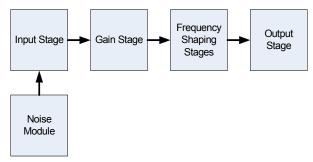

As an example, we are going to investigate the ISL28133. The ISL28133 is a zero-drift operational amplifier with voltage feedback topology. Intended for low frequency and power precision applications, the gain bandwidth product is 400kHz, the slew rate is  $0.1V/\mu s$ , and the supply current is  $18\mu A$ . A five-stage model represents the actual circuit, the block diagram for which is shown in Figure 1. The five stages are the input stage, the gain stage, the frequency-shaping stage, the output stage, and the noise module.

FIGURE 1. ISL28133 MACROMODEL BLOCK DIAGRAM

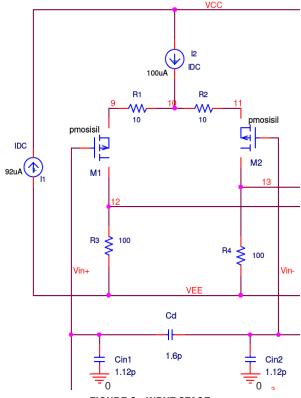

## The Input Stage

The input stage of the zero-drift amplifier is shown in Figure 2. The 100 $\mu$ A current source 'I2' feeds the PMOS input pair. Normally, I2 should be chosen less than the quiescent current. Remember, the ISL28133's typical supply current (RL = open) is only 18 $\mu$ A. However, a small I2 (~10 $\mu$ A) would make the input voltage noise too large to emulate. This will be discussed later in the noise analysis section of this document. Choose I2 = 100 $\mu$ A and use I1 to compensate back to the total quiescent current. Cin1 and Cin2 are the input common mode capacitance and Cdiff is the input differential mode capacitance.

FIGURE 2. INPUT STAGE

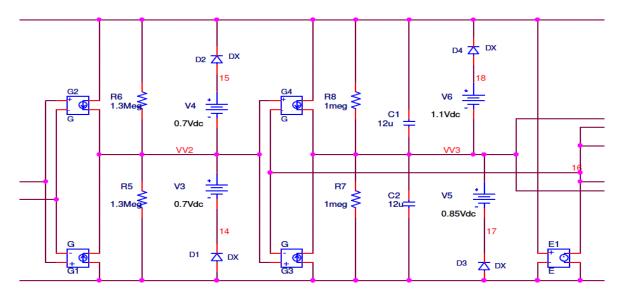

### The Gain Stage (Figure 3)

This stage performs several important functions in the model:

- This stage sets the DC gain of the part. All the subsequent stages provide unity DC gain.

- 2. It provides slew rate limiting.

- 3. It adds the dominant pole to the AC characteristic.

- It level shifts the signal from two voltages referred to the supplies to a single voltage referred to the mid-point.

- 5. It limits the full scale output swing.

FIGURE 3. GAIN STAGE

Referring to Figure 3, Ga is the gain of block G1 and G2. Gb is the gain of block G3 and G4.

$$SlewRate = \frac{I2 \bullet R3 \bullet Ga \bullet R5 \bullet Gb}{C1}$$

(EQ. 1)

Changing the value of V3 and V4 limits the slew rate. Also, R8/C1 and R7/C2 decide the dominant pole of this model. E1 is used to set the reference level at the middle of Vcc and Vee.

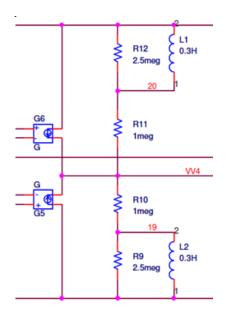

### **Frequency-Shaping Stages**

The "telescopic" frequency shaping techniques used here are very common in op-amp modeling. It is easy to add more poles and zeros. Each frequency-shaping block provides unity gain. A zero-pole pair is included in this model and shown in Figure 4.

$$R10 = R11 = 1M\Omega \tag{EQ. 2}$$

$$R9 = R12 = R10 \cdot (\frac{f_p}{f_z} - 1)$$

(EQ. 3)

$$L1 = L2 = \frac{R9}{2\pi f_p} \tag{EQ. 4}$$

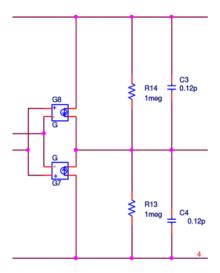

A higher order pole stage is shown in Figure 5, G7/8, R13/14 and C3/4.

FIGURE 4. ZERO-POLE PAIR STAGE

FIGURE 5. HIGHER ORDER POLE STAGE

## **Noise Simulation**

The ISL28133 input current noise is very small (~70fA), so it is neglected in this model. The voltage noise of the MOSFET can be modeled using the following equations.

$$V_i^2(f) = 4kT(\frac{2}{3})\frac{1}{g_{in}} + \frac{K}{WLC_{on}f}$$

(EQ. 5)

$$g_{\scriptscriptstyle m} \propto \sqrt{I_{\scriptscriptstyle D}}$$

(EQ. 6)

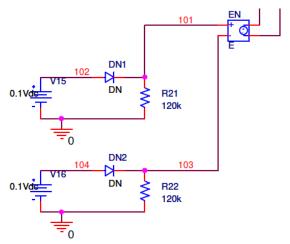

I<sub>D</sub> is the drain current. High bias current in the model is needed to emulate the low voltage noise. At the input stage, the tail current is set high enough to generate the low input voltage noise. Before the noise sources are added, the model has to be rendered lower noise than the spec or typical performance noise curve in the <a href="ISL28133">ISL28133</a> datasheet. The noise-voltage module of Figure 6 generates 1/f and white noise by using a 0.1V voltage source biasing a diode-resistor series combination. White noise is generated by the thermal noise-current.

$$i_n^2 = \frac{4kT}{R} \tag{EQ. 7}$$

where k is the Boltzmann's constant. So, the required value of the resistor for a given noise-voltage spectral density is:

$$R = \frac{e_n^2}{2 \times 4kT} \tag{EQ. 8}$$

where  $\mathbf{e}_n$  is the spectral density of the white noise voltage. The design of the chopper stabilized amplifier greatly reduces  $\mathbf{1}/f$  noise.  $\mathbf{1}/f$  noise (flicker noise) refers to the noise exhibiting power spectral density inversely proportional to the frequency.

More generally, the noise with the spectral density

$$S_N \propto \frac{1}{\left|f\right|^{\beta}} \quad \beta > 0$$

(EQ. 9)

is also called 1/f noise. Normally, the frequency where the flicker noise curve crosses the white noise curve is defined as the corner frequency. The small amount of flicker noise that remains is modeled within the SPICE diode model. Referring to Figure 6,

$$i_n^2 = 2qI_d + KF \bullet \frac{I_d^{AF}}{frequency}$$

(EQ. 10)

Id is the DC diode current. AF and KF are the model parameters of the SPICE diode and q is the charge of the electron. The flicker noise exponent (AF) is set to 1 and the flicker noise coefficient (KF) is set

$$KF = \frac{E_a^2}{2R^2 \bullet I_d} \tag{EQ. 11}$$

where Ea is the noise-voltage spectral density at 1Hz. The simulated voltage noise will show the 1/f noise-voltage spectral density with the correct corner frequency.

FIGURE 6. NOISE VOLTAGE MODULE

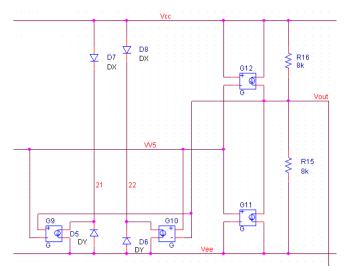

## **Output Stage**

After the frequency shaping-stages, the signal appears at Node VV5, which is referenced to the midpoint of two supply rails. Each controlled source can generate enough current to support the desired voltage drop across its paralleled resistor. R15 and R16 are equal to twice of the open loop output resistance, so their parallel combination gives the correct Zout. D5-D8 and G9/10 are used to force a current from the positive rail to the negative rail to correct the real current sink or source in the supply pins.

$$G9 = G10 = G11 = G12 = \frac{1}{2Z_{out}}$$

(EQ. 12)

$$R15 = R16 = 2Z_{out}$$

(EQ. 13)

FIGURE 7. OUTPUT STAGE

#### **Simulation Results**

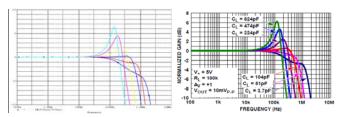

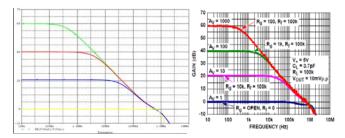

Some SPICE simulation results are compared with the typical performance curve from the <u>ISL28133 datasheet</u> in the following. (Figure 8b is from the datasheet).

FIGURE 8. GAIN vs FREQUENCY vs LOAD CAPACITANCE. IT CANNOT BE VERY ACCURATE BECAUSE THE PARASITIC CAPACITANCE ON THE BOARD WASN'T INCLUDED IN THE MODEL. THE ERROR IS LESS THAN 5%

FIGURE 9. FREQUENCY RESPONSE OF CLOSED LOOP GAIN WITH DIFFERENT GAIN. AT GAIN = 100, THE BANDWIDTH IS 3.94kHz AND THE ERROR IS LESS THAN 5%. AT LOW GAIN, THE BANDWIDTH IS EXPANDED BECAUSE OF THE ZERO POLE PAIR

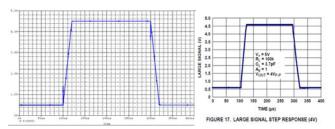

FIGURE 10. LARGE SIGNAL STEP RESPONSE. THE SLEW RATE SIMULATED IS 0.198V/µs AND THE ERROR IS 1%

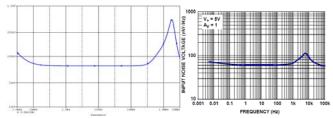

FIGURE 11. INPUT NOISE VOLTAGE VS FREQUENCY. AT 1kHz, THE SIMULATED INPUT NOISE VOLTAGE IS 64.9 nV/Hz, VERY CLOSE TO THE VALUE IN THE DATASHEET 65nV/Hz. THE SIMULATED CURVE CANNOT CATCH THE PEAK NEAR 10kHz

# **Conclusion**

A truly comprehensive SPICE macromodel for a voltage feedback amplifier is developed. This macromodel includes effects such as transfer response, accurate AC response, DC offset and voltage noise. It is easy to add more features like CMRR, PSRR, input current-noise, etc. Also it is convenient to change the parameters of the model to fit other voltage feedback amplifiers. Actually, several of Intersil's voltage feedback amplifiers use the same model topology.

# **ISL28133 Macromodel Netlist**

- \* ISL28133 Macromodel

- \* Revision B, July 2009 by Jian Wang

- \* This model simulates AC characteristics, Voltage Noise, Transient Response

- \* Connections: +input -input +Vupply -Vsupply Vout

.subckt ISL28133 3 2 7 4 6

\*Input Stage

C\_Cin1 80 1.12p C\_Cin2 20 1.12p C\_Cd 8 2 1.6p R\_R1 9 10 10 R\_R2 10 11 10 R R3 4 12 100 4 13 100 R\_R4  $M_M1$ 12899 pmosisil

+ L=50u

| + W=50u          |                       |                                                                                                                                                                                                  |  |

|------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| M_M2             | 13 2 11 11 pmosisil   | R_R13 4 W5 1meg                                                                                                                                                                                  |  |

| + L=50u          |                       | R_R14 VV5 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                    |  |

| + W=50u          |                       | *Output Stage                                                                                                                                                                                    |  |

| I_I1 4 7 DC 92uA |                       | G_G9 21 4 6 VV5 0.0000125                                                                                                                                                                        |  |

| I_I2             | 7 10 DC 100uA         | G_G10 22 4 VV5 6 0.0000125                                                                                                                                                                       |  |

| *Gain st         |                       | D_D5 4 21 DY                                                                                                                                                                                     |  |

| G_G1             | 4 VV2 13 12 0.0002    | D_D6 4 22 DY                                                                                                                                                                                     |  |

| G_G2             | 7 VV2 13 12 0.0002    | D_D7 7 21 DX                                                                                                                                                                                     |  |

| R_R5             | 4 VV2 1.3Meg          | D_D8 7 22 DX                                                                                                                                                                                     |  |

| R_R6             | VV2 1.3Meg            | R_R15                                                                                                                                                                                            |  |

| D_D1             | 4 14 DX               | R_R16 67 8k                                                                                                                                                                                      |  |

| D_D1<br>D_D2     | 15 7 DX               | G_G11 6 4 VV5 4 -0.000125                                                                                                                                                                        |  |

| V_V3             | VV2 14 0.7Vdc         | G_G12 7 6 7 VV5 -0.000125                                                                                                                                                                        |  |

| V_V3<br>V_V4     | 15 VV2 0.7Vdc         | *Voltage Noise                                                                                                                                                                                   |  |

|                  | it first pole         | D_DN1 102 101 DN                                                                                                                                                                                 |  |

| G_G3             | 4 VV3 VV2 16 1        | D_DN2 104 103 DN                                                                                                                                                                                 |  |

| G_G4             | 7 VV3 VV2 16 1        | R_R21 0 101 120k                                                                                                                                                                                 |  |

| R_R7             | 4 VV3 1meg            | R_R22                                                                                                                                                                                            |  |

| R_R8             | W3 7 1meg             | E_EN 8 3 101 103 1                                                                                                                                                                               |  |

| C_C1             | VV3 7 12u             | V_V15 102 0 0.1Vdc                                                                                                                                                                               |  |

| C_C2             | 4 VV3 12u             | V_V16 104 0 0.1Vdc                                                                                                                                                                               |  |

| D_D3             | 4 17 DX               | .model pmosisil pmos (kp=16e-3 vto=10m)                                                                                                                                                          |  |

| D_D4             | 18 7 DX               | .model DN D(KF=6.4E-16 AF=1)                                                                                                                                                                     |  |

| V_V5             | VV3 17 0.7Vdc         | .MODEL DX D(IS=1E-18 Rs=1)                                                                                                                                                                       |  |

| _<br>V_V6        | 18 VV3 0.7Vdc         | .MODEL DY D(IS=1E-15 BV=50 Rs=1)                                                                                                                                                                 |  |

| -<br>*Zero/Pole  |                       | ends ISL28133                                                                                                                                                                                    |  |

| E_E1             | 16 4 7 4 0.5          |                                                                                                                                                                                                  |  |

| _<br>G_G5        | 4 VV4 VV3 16 0.000001 | References [1] BOYLE, G.R., "Macromodeling of integrated circuit operational amplifiers", IEEE J. 1974, SC-9.                                                                                    |  |

| _<br>G_G6        | 7 VV4 VV3 16 0.000001 |                                                                                                                                                                                                  |  |

| _<br>L_L1        | 20 7 0.3H             | [2] Derek Bowers, Mark Alexander, Joe Buxton, "A<br>Comprehensive Simulation Macromodels for 'Current<br>Feedback' Operational Amplifiers," IEEE Proceedings, Vol.<br>137, April 1990 pp.137-145 |  |

| R_R12            | 20 7 2.5meg           |                                                                                                                                                                                                  |  |

| R_R11            | VV4 20 1meg           |                                                                                                                                                                                                  |  |

| L_L2             | 4 19 0.3H             | [3] Mark Alexander, Derek Bowers, "AN-138 SPICE-Compatible                                                                                                                                       |  |

| R_R9             | 4 19 2.5meg           | Op Amp Macro-Models", Analog Devices Inc., Application Note 138.                                                                                                                                 |  |

| R_R10            | 19 VV4 1meg           | [4] "AN-840 Development of an Extensive SPICE Macromodel                                                                                                                                         |  |

| *Pole            |                       | for 'Current-Feedback' Amplifiers", National Semiconductor                                                                                                                                       |  |

| G_G7             | 4 VV5 VV4 16 0.000001 | Corp., Application Note 840.                                                                                                                                                                     |  |

| G_G8             | 7 VV5 VV4 16 0.000001 |                                                                                                                                                                                                  |  |

| C_C3             | VV5 7 0.12p           |                                                                                                                                                                                                  |  |

|                  |                       |                                                                                                                                                                                                  |  |

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system, Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc. Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- e contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

#### SALES OFFICES

## Renesas Electronics Corporation

http://www.renesas.com

Refer to "http://www.renesas.com/" for the latest and detailed information

Renesas Electronics America Inc. 1001 Murphy Ranch Road, Milpitas, CA 95035, U.S.A. Tel: +1-408-432-8888, Fax: +1-408-434-5351

Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004

Renesas Electronics Europe Limited Dukes Meadow, Milliboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tel: +44-1628-651-700, Fax: +44-1628-651-804

Renesas Electronics Europe GmbH

Arcadiastrasse 10, 40472 Düsseldorf, German Tel: +49-211-6503-0, Fax: +49-211-6503-1327

Renesas Electronics (China) Co., Ltd.

Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679

Renesas Electronics (Shanghai) Co., Ltd.

Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0898, Fax: +86-21-2226-0999

Renesas Electronics Hong Kong Limited

Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +852-2265-6688, Fax: +852 2886-9022

Renesas Electronics Taiwan Co., Ltd.

13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670

Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300

Renesas Electronics Malaysia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amco Amcorp Trade Centre, No. 18, Jin Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia

Unit 1207, Block B, Menara Amcorp, Amcorp Tel: +60-3-7955-9390, Fax: +60-3-7955-9510

Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777

Renesas Electronics Korea Co., Ltd. 17F, KAMCO Yangiae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tel: +82-2-558-3737, Fax: +82-2-558-5338