# SH7730 グループ

# BSC バイト選択付き SRAM 設定例

RJJ06B1099-0001 Rev.0.01 2010.09.15

# 要旨

この資料はバスステートコントローラ (BSC) のバイト選択付き SRAM 空間インタフェースの機能を紹介し、バイト選択付き SRAM との接続例を掲載しています。

# 動作確認デバイス

SH7730

# 目次

| 1. | はじめに             | 2  |

|----|------------------|----|

|    |                  |    |

| 2. | 応用例の説明           | 3  |

|    |                  |    |

| 3  | <b>参</b> 老ドキュメント | 20 |

#### 1. はじめに

# 1.1 仕様

- SH7730 とルネサス製 64M ビット バイト選択付き SRAM (8M × 8 / 4M × 16 ビット) を 16 ビットバス幅で接続します。

- SH7730 のバスステートコントローラ (BSC) を使用し,外部のバイト選択付き SRAM に対するリード/ライトを行います。

## 1.2 使用機能

• バスステートコントローラ (BSC)

### 1.3 適用条件

• マイコン: SH7730 (R8A77301)

● SRAM: ルネサス エレクトロニクス製 64M ビット品:

R1WV6416R (8M×8/4M×16 ビット)

● 動作周波数 CPU クロック: 266.66 MHz

SuperHyway バスクロック: 133.33 MHzバスクロック:66.66 MHz周辺クロック:33.33 MHz

● エリア 5B バス幅: 16 ビット固定 (MD3 端子 = Low レベル)

● クロック動作モード: モード 2 (MD0 端子 = Low レベル、MD1 端子 = High レベル)

● エンディアン: ビッグエンディアン (MD5 端子 = Low レベル)

• ツールチェーン: ルネサス エレクトロニクス製 SuperH RISC engine Standard Toolchain Ver.9.3.0.0

• コンパイルオプション: High-performance Embedded Workshop でのデフォルト設定

(-cpu=sh4a -include="\$(PROJDIR)\footnote{Y}inc"

-object="\$(CONFIGDIR)\forall \\$(FILELEAF).obj" -debug -optimize=0

-gbr=auto -chgincpath -errorpath -global\_volatile=0

-opt range=all-infinite loop=0 -del vacant loop=0 -struct alloc=1 -nologo)

## 1.4 関連するアプリケーションノート

本資料の参考プログラムは,「SH7730 グループ アプリケーションノート SH7730 初期設定例(RJJ06B0864)」の設定条件で動作確認しています。そちらもあわせて参照ください。

# 2. 応用例の説明

### 2.1 使用機能の概要

SH7730 のバスステートコントローラ (BSC) を使用し , 外部に接続されたバイト選択付き SRAM の制御を行います。表 1 に本応用例で使用するバイト選択付き SRAM R1WV6416R (以下 , 単にバイト選択付き SRAM と表記します) の仕様を示します。

| 項目      | バイト選択付き SRAM 仕様          |

|---------|--------------------------|

| 型名      | ルネサス エレクトロニクス製 R1WV6416R |

| 容量 (構成) | 64M ビット (8M×8/4M×16 ビット) |

| 使用個数    | 1個                       |

| アクセス時間  | ランダムアクセス時: 70ns (最大)     |

| データバス幅  | 8 ビット/16 ビット切り替え         |

表 1 本応用例で使用するバイト選択付き SRAM 仕様

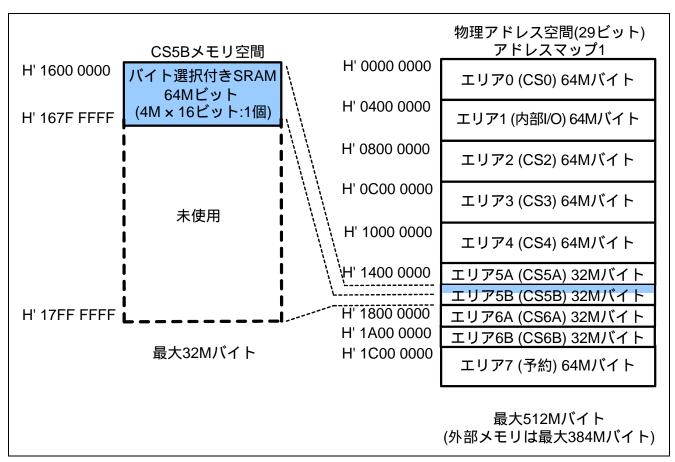

図 1 に  $4M \times 16$  ビット構成でのメモリマップを示します。接続するメモリの種類およびデータバス幅は, CS 空間ごとに指定します。本応用例では,CS5B 空間にバイト選択付き SRAM を接続します。

CS5B 空間は最大 32 M バイトの領域を使用できます。

本応用例のバイト選択付き SRAM は物理アドレス空間の H'1600 0000~H'167F FFFF に配置されます。

図 1 メモリマップ (4Mx16 ビット構成)

物理アドレス空間はさらに,ソフトウェアから見た仮想アドレス空間上にマッピングされます。仮想アドレス空間から物理アドレス空間へのアドレス変換は,メモリマネジメントユニット (MMU) の使用の有無により異なります。

詳細については ,「SH7730 グループ ハードウェアマニュアル (RJJ09B0339)」の「バスステートコントローラ (BSC)」および「メモリマネジメントユニット (MMU)」の項を参照ください。

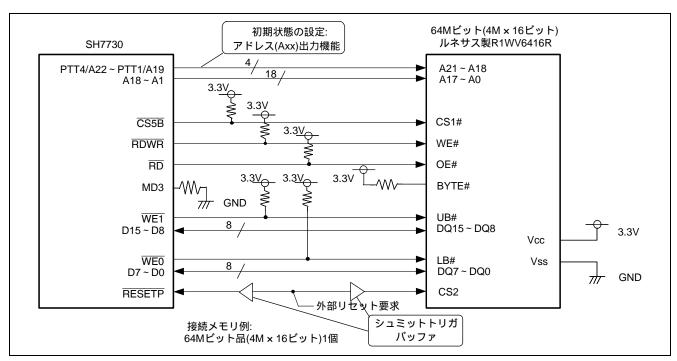

図2にバイト選択付き SRAM 接続回路例を示します。

SH7730 とバイト選択付き SRAM は 16 ビットバス幅で接続します。バイト選択付き SRAM のデータバス幅 を 16 ビット固定とするため , SRAM の BYTE#端子は High レベルに固定します。また , SH7730 の CS5B 空間のデータバス幅を 16 ビットとするため , CS5BBCR レジスタの BSZ[1:0] = "B'10"に設定します。

電源投入時の SH7730 の端子状態不安定期間でのバイト選択付き SRAM への誤アクセスを防ぐために,外部リセット IC 等を使用して,リセット信号を SH7730 の  $\overline{\text{RESETP}}$  端子とバイト選択付き SRAM の CS2 端子に入力してください。バイト選択付き SRAM の CS2 端子は High アクティブのチップセレクト端子です。バイト選択付き SRAM は CS2 端子にリセット信号(Low レベル信号)が入力するとスタンバイ状態になり,リセット信号が解除(High レベル信号)されるまで他の端子は外部からの信号を受け付けませんので誤アクセスが防げます。

図 2 SRAM 接続回路例

表 2 に SH7730 の端子機能を示します。A19~A22 端子は初期端子機能がアドレス端子になっていますので、ピンファンクションコントローラ (PFC) による端子機能の切り替えは不要です。

| SH7730 端子           | 入出力 | 初期端子機能    | 機能       |

|---------------------|-----|-----------|----------|

| PTT4/A22 ~ PTT1/A19 | 出力  | A22 ~ A19 | アドレスバス   |

| A18 ~ A1            | 出力  | A18 ~ A1  | アドレスバス   |

| D15 ~ D8            | 入出力 | D15 ~ D8  | データバス    |

| D7 ~ D0             | 入出力 | D7 ~ D0   | データバス    |

| RD                  | 出力  | RD        | リードイネーブル |

| RDWR                | 出力  | RDWR      | リード/ライト  |

| WE0                 | 出力  | WE0       | ライトイネーブル |

| WE1                 | 出力  | WE1       | ライトイネーブル |

| CS5B                | 出力  | CS5B      | チップセレクト  |

表 2 SH7730 端子機能

## 2.2 使用機能の設定手順

## 2.2.1 バイト選択付き SRAM の書き込み方式について

ここでバイト選択付き SRAM の書き込み方式について述べます。バイト選択付き SRAM の書き込みはバイト選択付き SRAM の CS1#端子が Low, CS2 端子が High, WE#端子が Low, LB#端子または UB#端子が Low のオーバラップ中に行われます (バイト選択付き SRAM の規格: tWP に相当)。

書き込み開始は ,バイト選択付き SRAM の CS1#端子の Low 遷移 , CS2 端子の High 遷移 ,WE#端子の Low 遷移 , LB#端子または UB#端子の Low 遷移のうち最も遅い遷移点で始まります。

書き込み終了は ,バイト選択付き SRAM の CS1#端子の High 遷移 , CS2 端子の Low 遷移 ,WE#端子の High 遷移 , LB#端子または UB#端子の High 遷移のうち , 最も早い遷移点で終わります。

tWP は書き込み開始から書き込み終了までの時間で測定され,tWP の規格値を満たせない場合には書き込みは保証されません。

また,バイト選択付き SRAMには3種の書き込みタイミングを制御するモードがあります。

(1) WE# CLOCK: バイト選択付き SRAM の WE#端子に入力する信号により書き込みタイミングを主体

的に制御するモード

(2) LB#,UB# CLOCK: バイト選択付き SRAM の LB#端子,UB#端子に入力する信号により書き込みタイミン

グを主体的に制御するモード

(3) CS1#,CS2 CLOCK: バイト選択付き SRAM の CS1#端子,CS2 端子に入力する信号により書き込みタイミ

ングを主体的に制御するモード

表 3 SH7730 とバイト選択 SRAM の接続端子一覧

| SH7730 端子           | バイト選択付き<br>SRAM 端子 | CS5BWCR<br>レジスタ設定 | 備考                          |  |

|---------------------|--------------------|-------------------|-----------------------------|--|

| RDWR                | WE#                | BAS = 1           | WE# CLOCK 対応                |  |

| WE0                 | LB#                | BAS = 0           | LB#, UB# CLOCK 対応           |  |

| WE1                 | UB#                | DA3 = 0           |                             |  |

| CS5B                | CS1#               | _                 | CS5B 空間選択時に Low レベル         |  |

| RESETP              | CS2                | _                 | バッファ IC を介してリセット信号を入力       |  |

| PTT4/A22 ~ PTT1/A19 | A21 ~ A18          | _                 | SH7730(A22) SRAM(A21) · · · |  |

| A18 ~ A1            | A17 ~ A0           | _                 | SH7730(A1) SRAM(A0) · · ·   |  |

| D15 ~ D8            | DQ15 ~ DQ8         | _                 | SH7730(D8) SRAM(DQ8) · · ·  |  |

| D7 ~ D0             | DQ7 ~ DQ0          | _                 | SH7730(D0) SRAM(DQ0) · · ·  |  |

| RD                  | OE#                | _                 |                             |  |

SH7730 は CS5B 空間バスコントロールレジスタ (CS5BBCR) で TYPE[3:0] = B'0011 (バイト選択付き SRAM) を設定し, CS5B 空間ウェイトコントロールレジスタ (CS5BWCR) で BAS = 1 を設定することで, SH7730 の RDWR 信号により WE# CLOCK に対応します。

また CS5B 空間バスコントロールレジスタ(CS5BBCR)で TYPE[3:0] = B'0011(バイト選択付き SRAM)を設定し, CS5B 空間ウェイトコントロールレジスタ (CS5BWCR) で BAS = 0 を設定することで, SH7730 の WEn信号により LB#,UB# CLOCK に対応します。

SH7730 は CS1#,CS2 CLOCK には対応していません。

## 2.2.2 バスステートコントローラの設定例

表 3 に WE# CLOCK 時 (BAS = 1) のバスステートコントローラの設定例を , 表 4 に LB#,UB# CLOCK 時 (BAS = 0) のバスステートコントローラの設定例を示します。

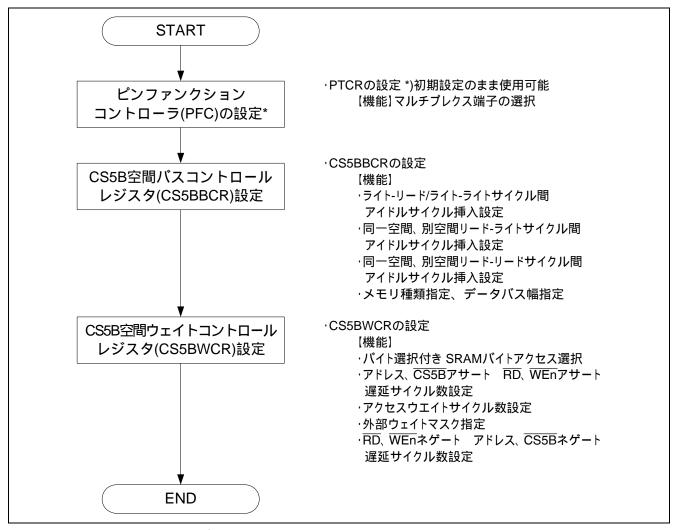

各レジスタの詳細については ,「SH7730 グループ ハードウェアマニュアル (RJJ09B0339)」の「バスステートコントローラ (BSC)」の章を参照ください。図 3 にバスステートコントローラの設定手順例を示します。

なお,表3,表4に示した設定例については,使用するメモリの規格値に合わせて設定してください。

表 4 バスステートコントローラの設定例 1 (WE# CLOCK BAS = 1)

| レジスタ名                                      | アドレス        | 設定値         | 機能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------|-------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS5B 空間バス<br>コントロール<br>レジスタ<br>(CS5BBCR)   | H'FEC1 0018 | H'2492 3400 | <ul> <li>ライト-リード/ライト-ライトサイクル間アイドル指定 IWW[2:0] = "B'010": 2 アイドルサイクル挿入</li> <li>別空間リード-ライトサイクル間アイドル指定 IWRWD[2:0] = "B'010": 2 アイドルサイクル挿入</li> <li>同一空間リード-ライトサイクル間アイドル指定 IWRWS[2:0] = "B'010": 2 アイドルサイクル挿入</li> <li>別空間リード-リードサイクル間アイドル指定 IWRRD[2:0] = "B'010": 2 アイドルサイクル挿入</li> <li>同一空間リード-リードサイクル間アイドル指定 IWRRS[2:0] = "B'010": 2 アイドルサイクル挿入</li> <li>ラー空間リード-リードサイクル間アイドル指定 IWRRS[2:0] = "B'010": 2 アイドルサイクル挿入</li> <li>メモリ種類指定 TYPE[3:0] = "B'0011": バイト選択付き SRAM</li> <li>データバス幅指定 BSZ[1:0] = "B'10": 16 ビット</li> </ul> |

| CS5B 空間ウェイト<br>コントロール<br>レジスタ<br>(CS5BWCR) | H'FEC1 0038 | H'0010 0AC1 | <ul> <li>バイト選択付き SRAM バイトアクセス選択 BAS = 1: WEn はリードライトアクセスサイクル中アサート ,RDWR はライトタイミングでアサート</li> <li>ライトアクセスウェイトサイクル数 WW[2:0] = "B'000": WR[3:0]と同じサイクル</li> <li>アドレス , CS5B アサート→RD , WEn アサート遅延サイクル数 SW[1:0] = "B'01": 1.5 サイクル</li> <li>アクセスウェイトサイクル数 WR[3:0] = "B'0101": 5 サイクル</li> <li>外部ウェイトマスク指定 WM = 1: 外部ウェイト入力無視</li> <li>RD , WEn ネゲート→アドレス , CS5B ネゲート遅延サイクル数 HW[1:0] = "B'01": 1.5 サイクル</li> </ul>                                                                                                                  |

# 表 5 バスステートコントローラの設定例 2 (LB#,UB# CLOCK BAS = 0)

| レジスタ名                                      | アドレス        | 設定値         | 機能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------|-------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS5B 空間バス<br>コントロール<br>レジスタ<br>(CS5BBCR)   | H'FEC1 0018 | H'2492 3400 | <ul> <li>ライト-リード/ライト-ライトサイクル間アイドル指定 IWW[2:0] = "B'010": 2 アイドルサイクル挿入</li> <li>別空間リード-ライトサイクル間アイドル指定 IWRWD[2:0] = "B'010": 2 アイドルサイクル挿入</li> <li>同一空間リード-ライトサイクル間アイドル指定 IWRWS[2:0] = "B'010": 2 アイドルサイクル挿入</li> <li>別空間リード-リードサイクル間アイドル指定 IWRRD[2:0] = "B'010": 2 アイドルサイクル挿入</li> <li>同一空間リード-リードサイクル間アイドル指定 IWRRS[2:0] = "B'010": 2 アイドルサイクル挿入</li> <li>ラー空間リード-リードサイクル間アイドル指定 IWRRS[2:0] = "B'010": 2 アイドルサイクル挿入</li> <li>メモリ種類指定 TYPE[3:0] = "B'0011": バイト選択付き SRAM</li> <li>データバス幅指定 BSZ[1:0] = "B'10": 16 ビット</li> </ul> |

| CS5B 空間ウェイト<br>コントロール<br>レジスタ<br>(CS5BWCR) | H'FEC1 0038 | H'0000 0AC1 | <ul> <li>バイト選択付き SRAM バイトアクセス選択 BAS = 0: WEn はリードライトタイミングでアサート ,RDWR はライトアクセスサイクル中アサート</li> <li>ライトアクセスウェイトサイクル数 WW[2:0] = "B'000": WR[3:0]と同じサイクル</li> <li>アドレス , CS5B アサート→RD , WEn アサート遅延サイクル数 SW[1:0] = "B'01": 1.5 サイクル</li> <li>アクセスウェイトサイクル数 WR[3:0] = "B'0101": 5 サイクル</li> <li>外部ウェイトマスク指定 WM = 1: 外部ウェイト入力無視</li> <li>RD , WEn ネゲート→アドレス , CS5B ネゲート遅延サイクル数 HW[1:0] = "B'01": 1.5 サイクル</li> </ul>                                                                                                                  |

図3 バスステートコントローラの設定手順例 (CS5B 空間)

# 2.3 バイト選択付き SRAM のタイミング設定参考例

参考プログラムでは,接続するメモリ (R1WV6416R) のアクセススピードに応じたウェイトサイクルを設定しています。SH7730の動作条件は,バスクロック 66.66 MHz (tcyc = 15 ns) です。SH7730 およびR1WV6416Rの AC 特性に関しては,各デバイスのデータシートを参照ください。

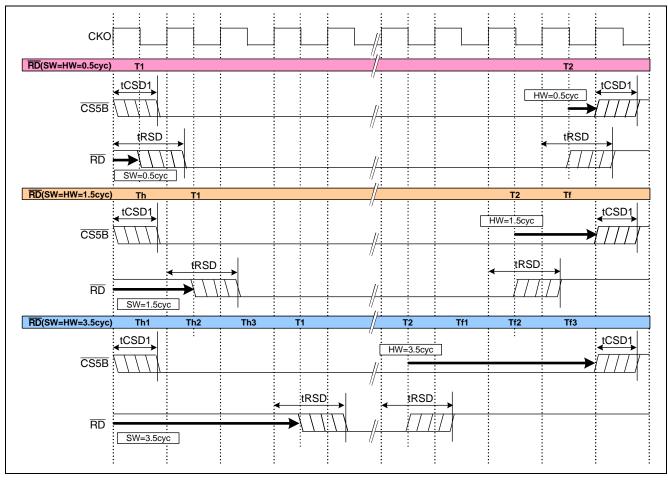

## 【補足】遅延サイクル Th , Tf について

CS5B 空間ウェイトコントロールレジスタ (CS5BWCR) において設定される,

- ・ SW[1:0]: アドレス ,  $\overline{\text{CS5B}}$  アサート $\rightarrow \overline{\text{RD}}$  ,  $\overline{\text{WEn}}$  アサート遅延サイクル (Th) のサイクル数

- ・ HW[1:0]:  $\overline{\text{RD}}$  ,  $\overline{\text{WEn}}$  ネゲート $\rightarrow$ アドレス ,  $\overline{\text{CS5B}}$  ネゲート遅延サイクル (Tf) のサイクル数 はそれぞれ , 0.5 サイクル , 1.5 サイクル , 2.5 サイクル , 3.5 サイクルの設定が可能です。一方 , SH7730 の AC 特性において , 各信号の遅延時間はすべて , CKO の立ち上がりからの時間として規定されています。

図 4 に Th , Tf と遅延時間の関係を示します。SW ビット , HW ビットで設定した遅延サイクル数から 0.5を引いたサイクル数の後に , 各信号の遅延を加算してタイミング設計を行います。

本アプリケーションノートでは , タイミングの計算式における遅延サイクル Th , Tf をそれぞれ , (SW ビット or HW ビットの設定値 -0.5) サイクル数 と規定しています。

図 4 遅延サイクルと遅延時間の関係

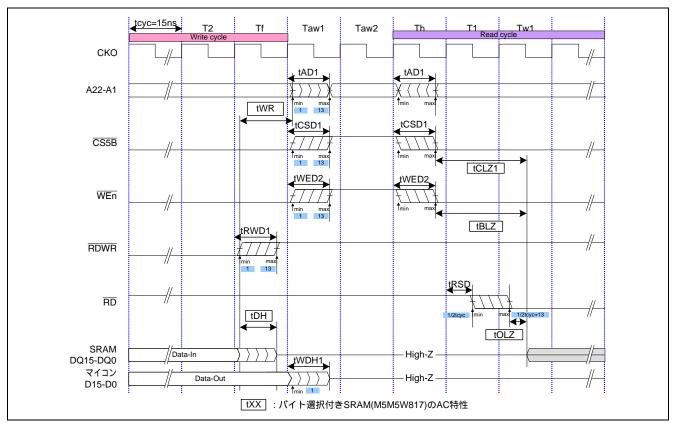

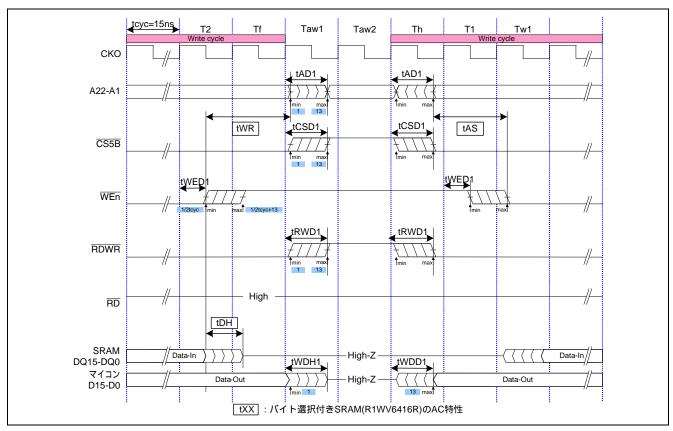

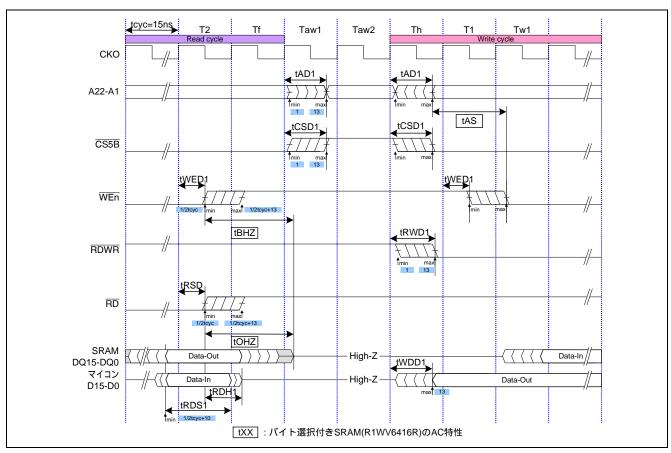

# 2.3.1 タイミング設定例 1 (WE# CLOCK BAS = 1)

SH7730 ではバイト選択付き SRAM の WE#端子による書き込み制御 (WE# CLOCK) と, LB#端子,UB#端子による書き込み制御 (LB#,UB# CLOCK) に対応しています。

ここでは ,バイト選択付き SRAM の WE#端子による書き込み制御 (WE# CLOCK) での設定例を示します。なお , バイト選択付き SRAM の WE#端子による書き込み制御 (WE# CLOCK) を使用する場合には CS5BWCR レジスタ/BAS = 1 に設定します。

# 1. アクセスウェイトサイクル

T1 サイクルと T2 サイクル間にウェイトサイクル (Tw) を設定します。

本設定において, SH7730 とバイト選択付き SRAM のバスタイミングを満たしていることを確認します。 (参考例では 5 ウェイトサイクル (Tw=5) を設定しています。) ( T1=T2=1)

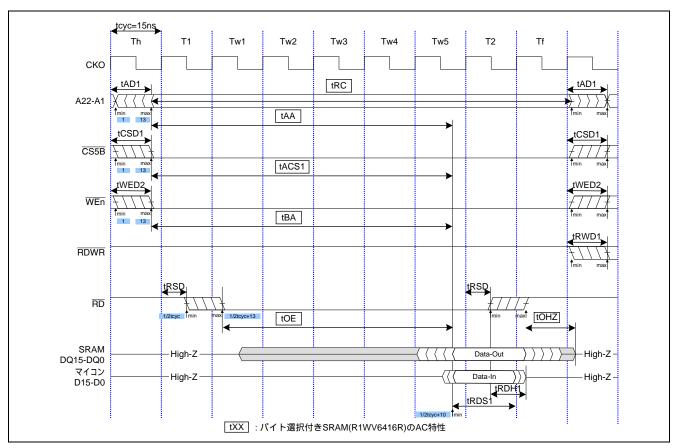

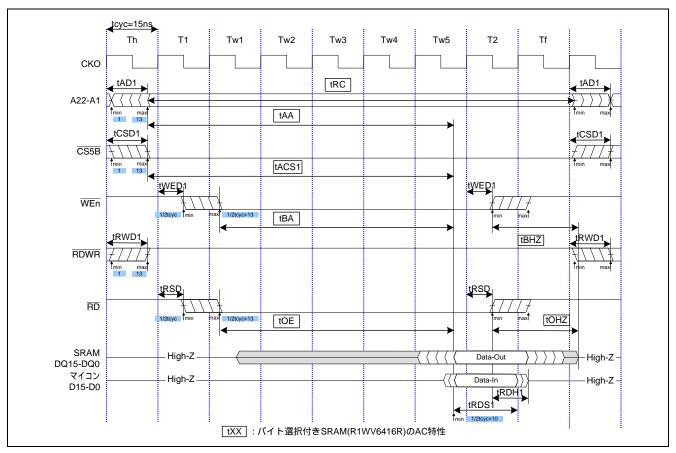

# A. リードサイクルタイミング

- バイト選択付き SRAM の tRC (リードサイクル時間)

tRC(min) ≤ (Th + T1 + Tw + T2 + Tf) × tcyc − tAD1(max)\*¹ + tAD1(min)\*² ......(図 5)

- バイト選択付き SRAM の tAA (アドレスアクセス時間) tAA(max) ≤ (Th + T1 + Tw + T2) × tcyc – tAD1(max) – tRDS1(min) ......(図 5)

- バイト選択付き SRAM の tACS1 (チップセレクト 1 アクセス時間) tACS1(max) ≤ (Th + T1 + Tw + T2) × tcyc – tCSD1(max) – tRDS1(min) .......(図 5)

- バイト選択付き SRAM の tBA (LB#,UB#アクセス時間) tBA(max) ≤ (Th + T1 + Tw + T2) × tcyc – tWED2(max) – tRDS1(min) ......(図 5)

- バイト選択付き SRAM の tOE (出力イネーブルアクセス時間)

tOE(max) ≤ (T1 + Tw + T2) × tcyc − tRSD(max) − tRDS1(min) .......(図 5)

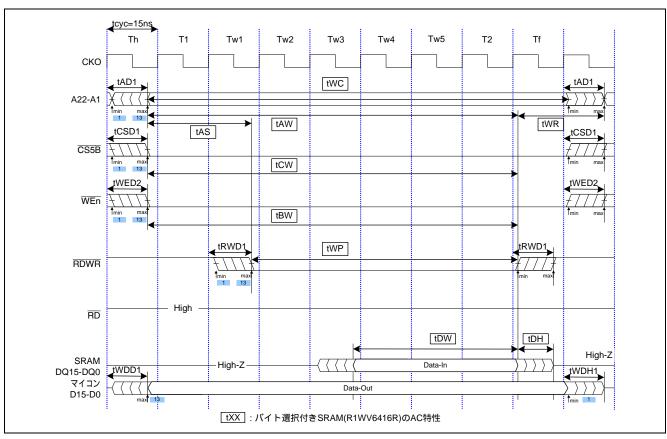

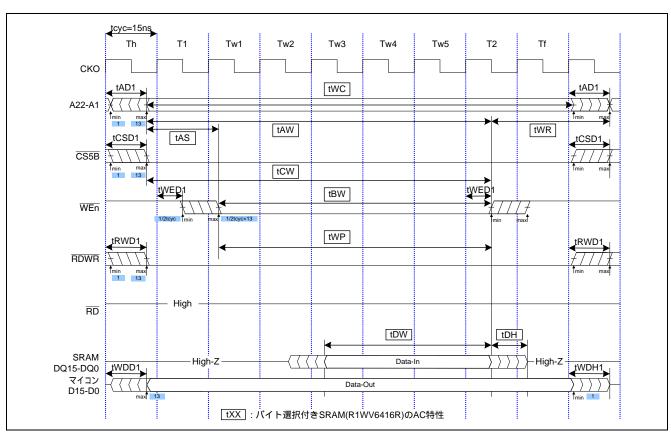

### B. ライトサイクルタイミング

- バイト選択付き SRAM の tWC (ライトサイクル時間) tWC(min) ≤ (Th + T1 + Tw + T2 + Tf) × tcyc − tAD1(max)\*<sup>1</sup> + tAD1(min)\*<sup>2</sup> ......(図 6)

- バイト選択付き SRAM の tCW (チップセレクト 1 セットアップ時間) tCW(min) ≤ (Th + T1 + Tw + T2 ) × tcyc − tCSD1(max) + tRWD1 (min) ......(図 6)

- バイト選択付き SRAM の tBW (LB#,UB#セットアップ時間) tBW(min) ≤ (Th + T1 + Tw + T2 ) × tcyc – tWED2(max) + tRWD1 (min) ......(図 6)

- バイト選択付き SRAM の tWP (ライトパルス幅) tWP(min) ≤ (Tw + T2) × tcyc − tRWD1(max) + tRWD1(min) ......(図 6)

- バイト選択付き SRAM の tDW (データセットアップ時間)

tDW(min) ≤ (Th + T1 + Tw + T2) × tcyc tWDD1(max) + tRWD1(min) ......(図 6)

- バイト選択付き SRAM の tDH (データホールド時間) tDH (min) ≤ Tf × tcyc – tRWD1(max) + tWDH1(min) ......(図 6)

- 2. CS アサート期間拡張

- A. アドレス, CS5B アサート→RD, WEn アサートまでの遅延サイクル (Th) 使用するバイト選択付き SRAM の tAS (アドレスセットアップ時間) を満足していることを確認します。 参考例では Th = 1.0 に設定しています。

- バイト選択付き SRAM の tAS (アドレスセットアップ時間)

tAS(min) ≤ (Th + T1) × tcyc tAD1(max) + tRWD1(min) ......(図 6)

- B. RD , WEn ネゲート→アドレス , CS5B ネゲートまでの遅延サイクル (Tf) 使用するバイト選択付き SRAM の tWR (ライトリカバリ時間) を満足していることを確認します。 参考例では Tf = 1.0 に設定しています。

- バイト選択付き SRAM の tWR (ライトリカバリ時間)

tWR(min) ≤ Tf × tcyc − tRWD1(max) + tAD1(min) ......(図 6)

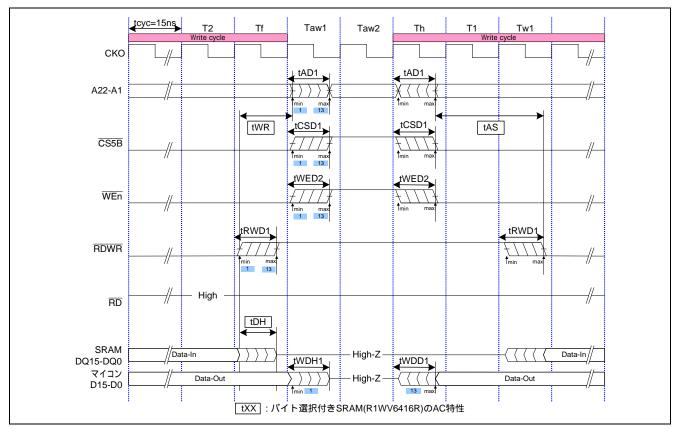

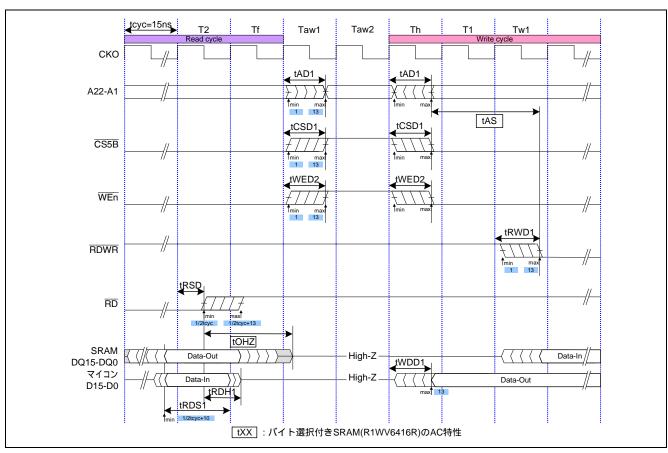

- 3. アクセスサイクル間ウェイト

連続するアクセス間にアクセスサイクル間ウェイトの挿入を設定します。

本設定において,対象のバイト選択付き SRAM の tOHZ (出力イネーブルアクセス時間)を満たしていることを確認します。(参考例ではライト-リード/ライト-ライトサイクル間,同一空間リード-ライトサイクル間,別空間,別空間リード-ライトサイクル間のウェイトサイクル,同一空間リード-リードサイクル間,別空間リード-リードサイクル間のウェイトサイクルを2サイクル (Taw=2)に設定しています。)  $*^3$

- バイト選択付き SRAM の tOHZ (出力イネーブルアクセス時間)

tOHZ(max) ≤ (T2 + Tf + Taw) × tcyc tRSD(max)\*<sup>4</sup> ......(図 8)

- 【注】 1. tAD1(max)かtCSD1(max)の長いほうが適用されます。

- 2. tAD1(min)か tCSD1(min)の短いほうが適用されます。

- 3. 参考例では一例として各サイクル間ウェイトを一律に2サイクルに設定していますが,各タイミングを精査することで,ウェイトサイクル数を短縮できる可能性があります。

- 4. リードサイクル後,次の同一空間サイクル/別空間サイクル開始までに D15-D0 が High Z になっている必要があります。そのためには $(T2+Tf+Taw) \times tcyc-tRSD(max)$ の合計が tOHZ(max)以上であれば良いことになります。

図 5 バイト選択付き SRAM リードタイミング (BAS = 1)

図 6 バイト選択付き SRAM ライトタイミング (BAS = 1)

図7 バイト選択付き SRAM ライト-ライトサイクル間タイミング (BAS = 1)

図 8 バイト選択付き SRAM リード-ライトサイクル間タイミング (BAS = 1)

図 9 バイト選択付き SRAM ライト-リードサイクル間タイミング (BAS = 1)

図 10 バイト選択付き SRAM リード-リードサイクル間タイミング (BAS = 1)

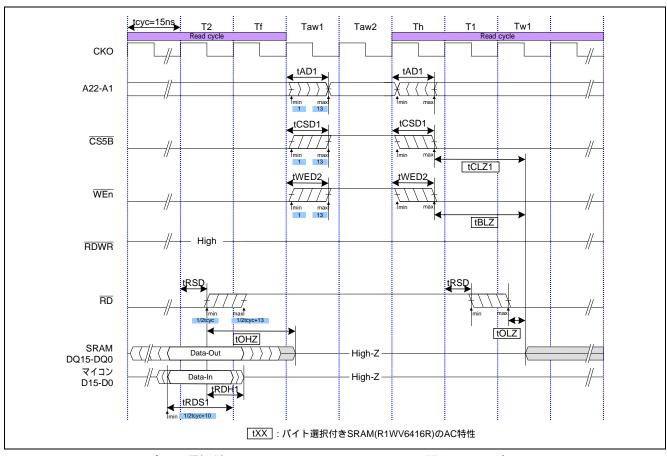

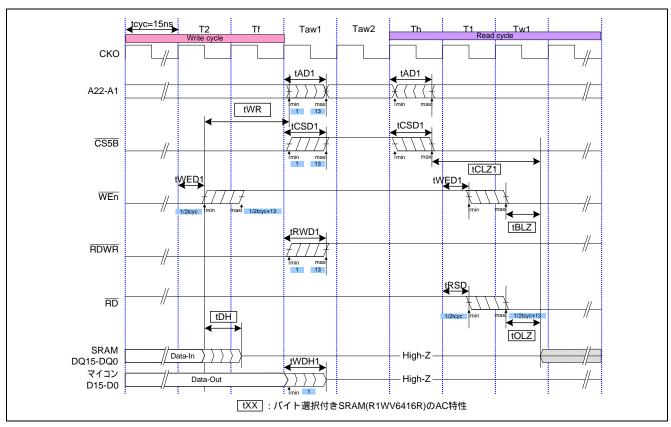

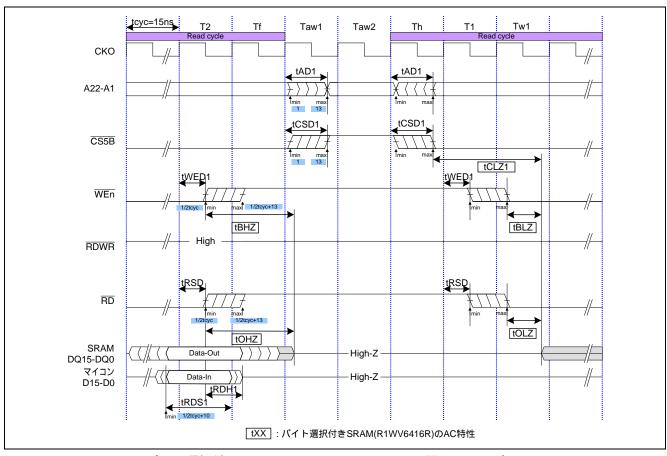

# 2.3.2 タイミング設定例 2 (LB#,UB# CLOCK BAS = 0)

ここでは ,バイト選択付き SRAM の LB#端子,UB#端子による書き込み制御モード (LB#,UB# CLOCK) での設定例を示します。なお , バイト選択付き SRAM の LB#端子,UB#端子による書き込み制御 (LB#,UB# CLOCK) を使用する場合には CS5BWCR レジスタ/BAS = 0 に設定します。

#### 1. アクセスウェイトサイクル

T1 サイクルと T2 サイクル間にウェイトサイクル (Tw) を設定します。

本設定において, SH7730 とバイト選択付き SRAM のバスタイミングを満たしていることを確認します。 (参考例では 5 ウェイトサイクル (Tw=5) を設定しています。) ( T1=T2=1)

#### A. リードサイクルタイミング

- バイト選択付き SRAM の tRC (リードサイクル時間) tRC(min) ≤ (Th + T1 + Tw + T2 + Tf) × tcyc – tAD1(max)\*<sup>1</sup> + tAD1(min)\*<sup>2</sup> ......(図 11)

- バイト選択付き SRAM の tAA (アドレスアクセス時間) tAA (max) ≤ (Th + T1 + Tw + T2) × tcyc – tAD1(max) – tRDS1(min) ......(図 11)

- バイト選択付き SRAM の tACS1 (チップセレクト 1 アクセス時間) tACS1(max) ≤ (Th + T1 + Tw + T2) × tcyc – tCSD1(max) – tRDS1(min) ......(図 11)

- バイト選択付き SRAM の tBA (LB#,UB#アクセス時間) tBA(max) ≤ (T1 + Tw + T2) × tcyc – tWED1(max) – tRDS1(min) ......(図 11)

#### B. ライトサイクルタイミング

- バイト選択付き SRAM の tWC (ライトサイクル時間)

tWC(min) ≤ (Th + T1 + Tw + T2 + Tf) × tcyc tAD1(max)\*<sup>1</sup> + tAD1(min)\*<sup>2</sup> ......(図 12)

- バイト選択付き SRAM の tAW (WE#の立ち上がりに対するアドレスセットアップ時間) tAW(min) ≤ (Th + T1 + Tw ) × tcyc tAD1(max) + tWED1 (min) .......(図 12)

- バイト選択付き SRAM の tCW (チップセレクト 1 セットアップ時間) tCW(min) ≤ (Th + T1 + Tw ) × tcyc − tCSD1(max) + tWED1 (min) ......(図 12)

- バイト選択付き SRAM の tBW (LB#,UB#セットアップ時間) tBW(min) ≤ (T1 + Tw ) × tcyc – tWED1(max) + tWED1 (min) ......(図 12)

- バイト選択付き SRAM の tWP (ライトパルス幅) tWP(min) ≤ (T1 + Tw ) × tcyc tWED1(max) + tWED1 (min) ......(図 12)

- バイト選択付き SRAM の tDW (データセットアップ時間) tDW(min) ≤ (Th + T1 + Tw ) × tcyc – tWDD1(max) + tWED1(min) ......(図 12)

- バイト選択付き SRAM の tDH (データホールド時間)

tDH (min) ≤ (T2 + Tf) × tcyc tWED1(max) + tWDH1(min) ......(図 12)

- 2. CS アサート期間拡張

- A. アドレス, CS5B アサート→RD, WEn アサートまでの遅延サイクル (Th) 使用するバイト選択付き SRAM の tAS (アドレスセットアップ時間) を満足していることを確認します。 参考例では Th = 1.0 に設定しています。

- バイト選択付き SRAM の tAS (アドレスセットアップ時間) tAS(min) ≤ Th × tcyc – tAD1(max) + tWED1(min) ......(図 12)

- B. RD , WEn ネゲート→アドレス , CS5B ネゲートまでの遅延サイクル (Tf) 使用するバイト選択付き SRAM の tWR (ライトリカバリ時間) を満足していることを確認します。 参考例では Tf = 1.0 に設定しています。

- バイト選択付き SRAM の tWR (ライトリカバリ時間)

tWR(min) ≤ (T2 + Tf) × tcyc tWED1(max) + tAD1(min) ......(図 12)

- 3. アクセスサイクル間ウェイト

連続するアクセス間にアクセスサイクル間ウェイトの挿入を設定します。

本設定において,対象のバイト選択付き SRAM の tOHZ (出力イネーブルアクセス時間)  $*^3$  または tBHZ (LB#,UB#イネーブルアクセス時間)  $*^3$  を満たしていることを確認します。(参考例ではライト-リード/ライト-ライトサイクル間,同一空間リード-ライトサイクル間,別空間リード-ライトサイクル間のウェイトサイクル (Taw=2) に設定しています。)  $*^4$

- バイト選択付き SRAM の tOHZ (出力イネーブルアクセス時間) tOHZ(max) ≤ (T2 + Tf + Taw) × tcyc – tRSD(max)\*<sup>5</sup> ......(図 14)

- バイト選択付き SRAM の tBHZ (LB#,UB#イネーブルアクセス時間)

tBHZ(max) ≤ (T2 + Tf + Taw) × tcyc tWED1(max)\*<sup>5</sup> .......(図 14)

- 【注】 1. tAD1(max)かtCSD1(max)の長いほうが適用されます。

- 2. tAD1(min)か tCSD1(min)の短いほうが適用されます。

- 3. 出力イネーブルアクセス時間, LB#,UB#イネーブルアクセス時間共に満足させる必要があります。

- 4. 参考例では一例として各サイクル間ウェイトを一律に2サイクルに設定していますが,各タイミングを精査することで,ウェイトサイクル数を短縮できる可能性があります。

- 5. リードサイクル後,次の同一空間サイクル/別空間サイクル開始までに D15-D0 が High Z になっている必要があります。そのためには(T2 + Tf + Taw) × tcyc tRSD(max)の合計が tOHZ(max)以上,または(T2 + Tf + Taw) × tcyc tWED1(max)の合計が tBHZ(max) 以上であれば良いことになります。

図 11 バイト選択付き SRAM リードタイミング (BAS = 0)

図 12 バイト選択付き SRAM ライトタイミング (BAS = 0)

図 13 バイト選択付き SRAM ライト-ライトサイクル間タイミング (BAS = 0)

図 14 バイト選択付き SRAM リード-ライトサイクル間タイミング (BAS = 0)

図 15 バイト選択付き SRAM ライト-リードサイクル間タイミング (BAS = 0)

図 16 バイト選択付き SRAM リード-リードサイクル間タイミング (BAS = 0)

# 3. 参考ドキュメント

- ソフトウェアマニュアル SH-4A ソフトウェアマニュアル (RJJ09B0090) (最新版をルネサス エレクトロニクスホームページから入手してください。)

- ハードウェアマニュアル SH7730 グループ ハードウェアマニュアル (RJJ09B0339) (最新版をルネサス エレクトロニクスホームページから入手してください。)

# ホームページとサポート窓口

ルネサス エレクトロニクスホームページ

http://japan.renesas.com/

お問合せ先

http://japan.renesas.com/inquiry

すべての商標および登録商標は,それぞれの所有者に帰属します。

# 改訂記録

|      |            | 改訂内容 |      |  |

|------|------------|------|------|--|

| Rev. | 発行日        | ページ  | ポイント |  |

| 1.00 | 2010.09.15 | _    | 初版発行 |  |

|      |            |      |      |  |

|      |            |      |      |  |

|      |            |      |      |  |

|      |            |      |      |  |

|      |            |      |      |  |

|      |            |      |      |  |

|      |            |      |      |  |

|      |            |      |      |  |

# 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意 事項については、本文を参照してください。なお、本マニュアルの本文と異なる記載がある場合は、本文の 記載が優先するものとします。

#### 1. 未使用端子の処理

【注意】未使用端子は、本文の「未使用端子の処理」に従って処理してください。

CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。未使用端子は、本文「未使用端子の処理」で説明する指示に従い処理してください。

#### 2. 電源投入時の処置

【注意】電源投入時は,製品の状態は不定です。

電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。 外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の 状態は保証できません。

同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

3. リザーブアドレスのアクセス禁止

【注意】リザーブアドレスのアクセスを禁止します。

アドレス領域には、将来の機能拡張用に割り付けられているリザーブアドレスがあります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

#### 4. クロックについて

【注意】リセット時は、クロックが安定した後、リセットを解除してください。

プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。 リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子(または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

#### 5. 製品間の相違について

【注意】型名の異なる製品に変更する場合は、事前に問題ないことをご確認下さい。

同じグループのマイコンでも型名が違うと、内部メモリ、レイアウトパターンの相違などにより、特性が異なる場合があります。型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。

# ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営 業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報 の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA機器、通信機器、計測機器、AV機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命維持を目的として設計されていない医療機器

(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療

行為 (患部切り出し等) を行うもの、その他直接人命に影響を与えるもの) (厚生労働省定義の高度管理医療機器に相当) またはシステム等

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制するRoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関し て、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社がその総株主の議決権の過半数を 直接または間接に保有する会社をいいます。

- 注2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

ルネサスエレクトロニクス株式会社

■営業お問合せ窓口

http://www.renesas.com

※営業お問合せ窓口の住所・電話番号は変更になることがあります。最新情報につきましては、弊社ホームページをご覧ください。

ルネサス エレクトロニクス販売株式会社 〒100-0004 千代田区大手町2-6-2(日本ビル)

(03)5201-5307

| ■技術的なお問合せおよび資料のご請求は下記へどうぞ                  |  |

|--------------------------------------------|--|

| 総合お問合せ窓口: http://japan.renesas.com/inquiry |  |