## Introduction

It is often necessary to divide a signal frequency by a fixed coefficient, which is simple if this coefficient is an even number equal to 2, 4, 8 and so on. However, dividing by odd or fractional coefficients is a more complicated task. Using the LUTs and DFFs resources in GreenPAK, one can efficiently divide a given frequency by 1.5, 2.5, 3, 3.5, 4.5, 5, and many other coefficients.

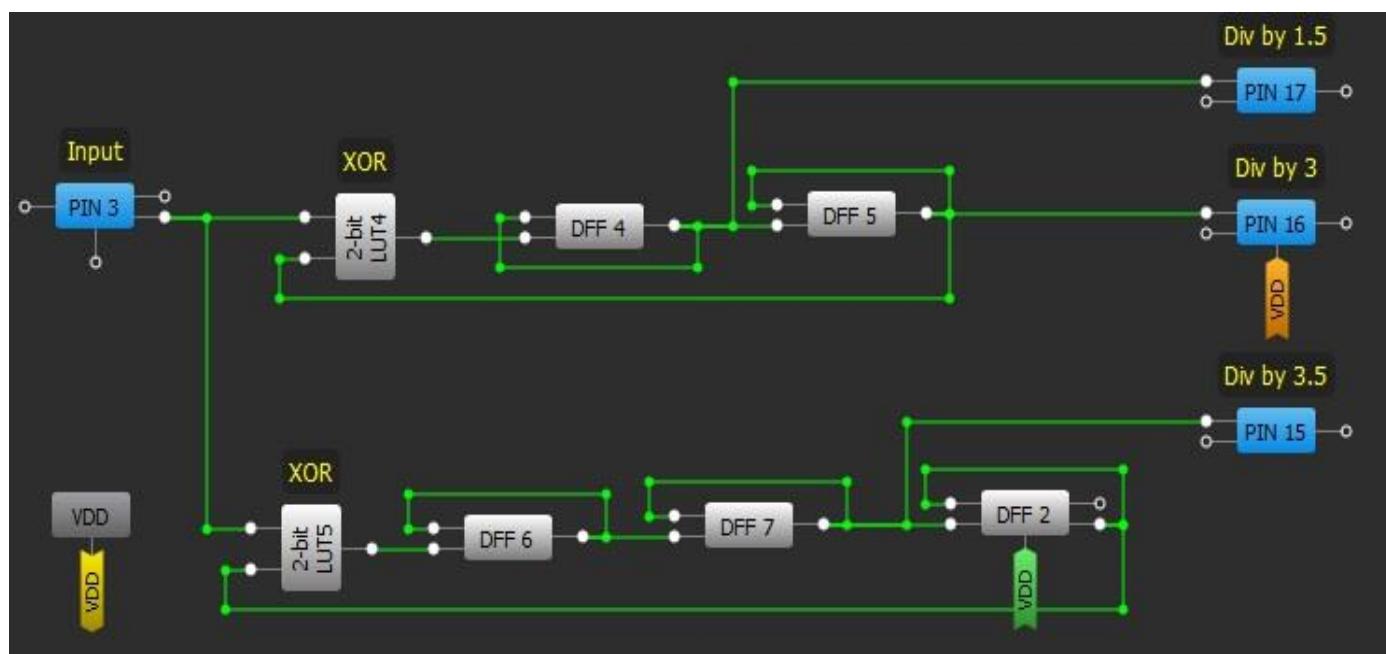

## Frequency divide by 1.5, 3, 3.5

Here DFFs each provide frequency division by 2, while XOR LUTs are used to eliminate the odd half input clock which comes to the first DFF. This makes it possible to get coefficients  $2-0.5=1.5$ ;  $1.5*2=3$ ;  $4-0.5=3.5$ .

Blocks configurations are shown in figures 1-5 below.

| 2-bit LUT4 |     |     |     |     |

|------------|-----|-----|-----|-----|

| IN3        | IN2 | IN1 | IN0 | OUT |

| 0          | 0   | 0   | 0   | 0   |

| 0          | 0   | 0   | 1   | 1   |

| 0          | 0   | 1   | 0   | 1   |

| 0          | 0   | 1   | 1   | 0   |

| 2-bit LUT5 |     |     |     |     |

|------------|-----|-----|-----|-----|

| IN3        | IN2 | IN1 | IN0 | OUT |

| 0          | 0   | 0   | 0   | 0   |

| 0          | 0   | 0   | 1   | 1   |

| 0          | 0   | 1   | 0   | 1   |

| 0          | 0   | 1   | 1   | 0   |

Figure 2. LUTs properties

Figure 1. Frequency divide by 1.5, 3, 3.5 circuit design

| PIN 3                         |                       |

|-------------------------------|-----------------------|

| <b>I/O selection:</b>         | Digital input         |

| <b>Input mode:</b><br>OE = 0  | Digital in without Sc |

| <b>Output mode:</b><br>OE = 1 | None                  |

| <b>Resistor:</b>              | Floating              |

| <b>Resistor value:</b>        | Floating              |

| PIN 15                        |                       |

| <b>I/O selection:</b>         | Digital output        |

| <b>Input mode:</b><br>OE = 0  | None                  |

| <b>Output mode:</b><br>OE = 1 | 1x push pull          |

| <b>Resistor:</b>              | Floating              |

| <b>Resistor value:</b>        | Floating              |

| PIN 16                        |                       |

| <b>I/O selection:</b>         | Digital output        |

| <b>Input mode:</b><br>OE = 0  | None                  |

| <b>Output mode:</b><br>OE = 1 | 1x push pull          |

| <b>Resistor:</b>              | Floating              |

| <b>Resistor value:</b>        | Floating              |

| PIN 17                        |                       |

| <b>I/O selection:</b>         | Digital output        |

| <b>Input mode:</b><br>OE = 0  | None                  |

| <b>Output mode:</b><br>OE = 1 | 1x push pull          |

| <b>Resistor:</b>              | Floating              |

| <b>Resistor value:</b>        | Floating              |

Figure 3. Pins properties

| 2-bit LUT0/DFF/LATCH4      |                  |

|----------------------------|------------------|

| <b>Type:</b>               | DFF / LATCH      |

| <b>Mode:</b>               | DFF              |

| <b>nSET/nRESET option:</b> | None             |

| <b>Initial polarity:</b>   | Low              |

| <b>Q output polarity:</b>  | Inverted (nQ)    |

| 2-bit LUT1/DFF/LATCH5      |                  |

| <b>Type:</b>               | DFF / LATCH      |

| <b>Mode:</b>               | DFF              |

| <b>nSET/nRESET option:</b> | None             |

| <b>Initial polarity:</b>   | Low              |

| <b>Q output polarity:</b>  | Inverted (nQ)    |

| 2-bit LUT2/DFF/LATCH6      |                  |

| <b>Type:</b>               | DFF / LATCH      |

| <b>Mode:</b>               | DFF              |

| <b>nSET/nRESET option:</b> | None             |

| <b>Initial polarity:</b>   | Low              |

| <b>Q output polarity:</b>  | Inverted (nQ)    |

| 2-bit LUT3/DFF/LATCH7      |                  |

| <b>Type:</b>               | DFF / LATCH      |

| <b>Mode:</b>               | DFF              |

| <b>nSET/nRESET option:</b> | None             |

| <b>Initial polarity:</b>   | Low              |

| <b>Q output polarity:</b>  | Inverted (nQ)    |

| 3-bit LUT2/DFF/LATCH2      |                  |

| <b>Type:</b>               | DFF / LATCH      |

| <b>Mode:</b>               | DFF              |

| <b>nSET/nRESET option:</b> | nRESET           |

| <b>Initial polarity:</b>   | Low              |

| <b>Q output polarity:</b>  | Non-inverted (Q) |

Figure 4. DFFs properties

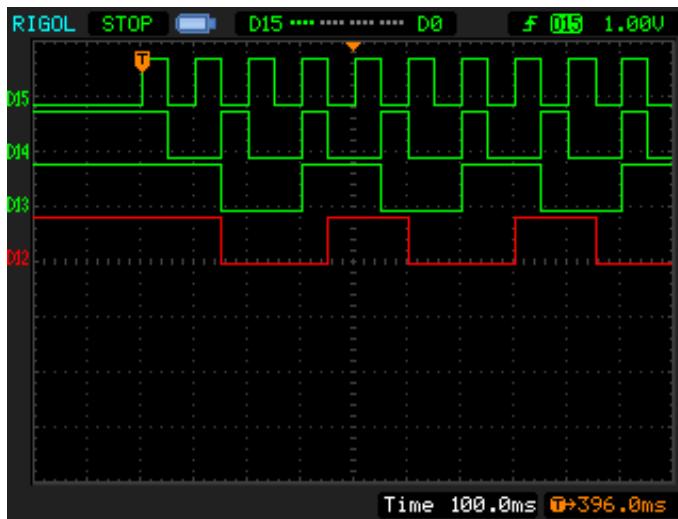

Figure 5. Frequency divider functional diagram

(D15 – Input signal; D14 – F/1.5;

D13 – F/3; D12 – F/3.5)

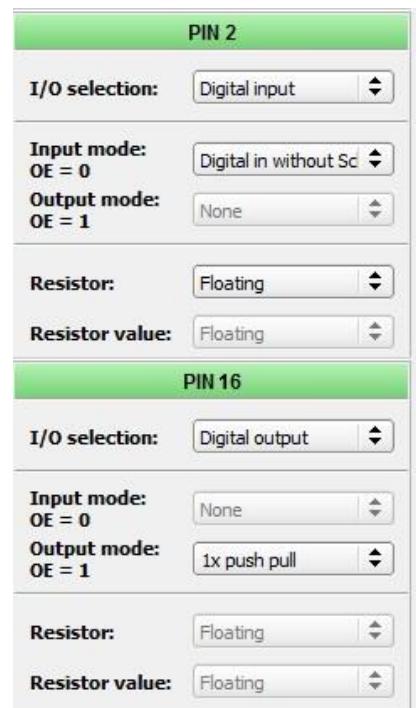

| PIN 2                  |                       |

|------------------------|-----------------------|

| I/O selection:         | Digital input         |

| Input mode:<br>OE = 0  | Digital in without Sc |

| Output mode:<br>OE = 1 | None                  |

| Resistor:              | Floating              |

| Resistor value:        | Floating              |

| PIN 14                 |                       |

| I/O selection:         | Digital output        |

| Input mode:<br>OE = 0  | None                  |

| Output mode:<br>OE = 1 | 1x push pull          |

| Resistor:              | Floating              |

| Resistor value:        | Floating              |

| PIN 16                 |                       |

| I/O selection:         | Digital output        |

| Input mode:<br>OE = 0  | None                  |

| Output mode:<br>OE = 1 | 1x push pull          |

| Resistor:              | Floating              |

| Resistor value:        | Floating              |

Figure 7. Pins properties

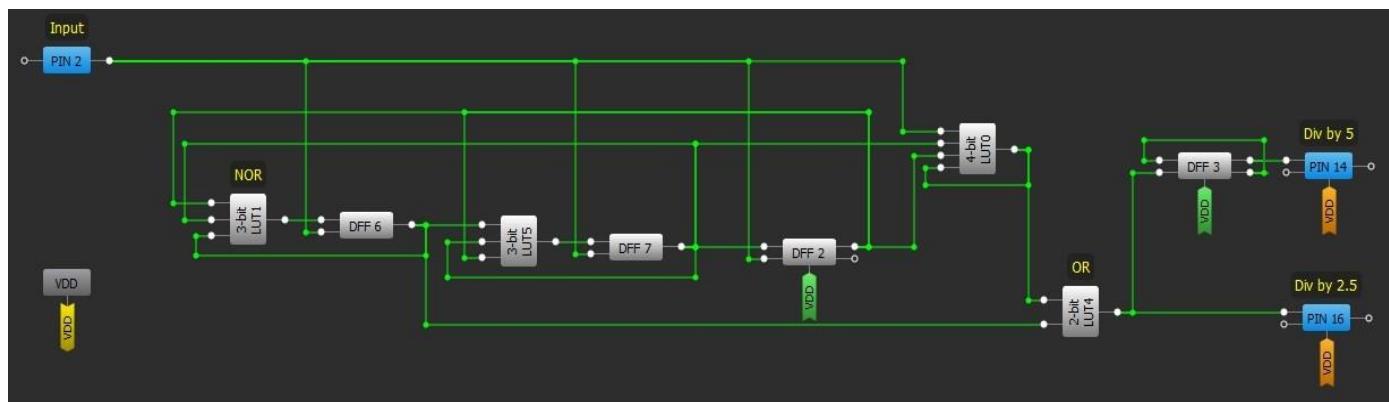

## Frequency divide by 2.5, 5

This case operates differently than the previous 1.5, 3, 3.5 example. Here, the same CLK signal is supplied to a string of DFF CK inputs, but LUTs and feedback reconfigure their D inputs. In this way frequency division by 2.5 can be designed. DFF3 is used to divide by 2 a previously divided by 2.5 frequency and output the divide by 5 signal.

Blocks configurations are shown in figures 6-9.

Figure 6. Frequency divider by 2.5; 5 circuit design

|                             |     |     |     |     |                              |                  |  |  |  |

|-----------------------------|-----|-----|-----|-----|------------------------------|------------------|--|--|--|

| <b>3-bit LUT1</b>           |     |     |     |     | <b>2-bit LUT2/DFF/LATCH6</b> |                  |  |  |  |

| IN3                         | IN2 | IN1 | IN0 | OUT | Type:                        | DFF / LATCH      |  |  |  |

| 0                           | 0   | 0   | 0   | 1   | Mode:                        | DFF              |  |  |  |

| 0                           | 0   | 0   | 1   | 0   | nSET/nRESET option:          | None             |  |  |  |

| 0                           | 0   | 1   | 0   | 0   | Initial polarity:            | Low              |  |  |  |

| 0                           | 0   | 1   | 1   | 0   | Q output polarity:           | Non-inverted (Q) |  |  |  |

| 0                           | 1   | 0   | 0   | 0   |                              |                  |  |  |  |

| 0                           | 1   | 0   | 1   | 0   |                              |                  |  |  |  |

| 0                           | 1   | 1   | 0   | 0   |                              |                  |  |  |  |

| 0                           | 1   | 1   | 1   | 0   |                              |                  |  |  |  |

| <b>3-bit LUT5</b>           |     |     |     |     | <b>2-bit LUT3/DFF/LATCH7</b> |                  |  |  |  |

| IN3                         | IN2 | IN1 | IN0 | OUT | Type:                        | DFF / LATCH      |  |  |  |

| 0                           | 0   | 0   | 0   | 0   | Mode:                        | DFF              |  |  |  |

| 0                           | 0   | 0   | 1   | 0   | nSET/nRESET option:          | None             |  |  |  |

| 0                           | 0   | 1   | 0   | 1   | Initial polarity:            | Low              |  |  |  |

| 0                           | 0   | 1   | 1   | 0   | Q output polarity:           | Non-inverted (Q) |  |  |  |

| 0                           | 1   | 0   | 0   | 1   |                              |                  |  |  |  |

| 0                           | 1   | 0   | 1   | 0   |                              |                  |  |  |  |

| 0                           | 1   | 1   | 0   | 1   |                              |                  |  |  |  |

| 0                           | 1   | 1   | 1   | 0   |                              |                  |  |  |  |

| <b>2-bit LUT4</b>           |     |     |     |     | <b>3-bit LUT2/DFF/LATCH2</b> |                  |  |  |  |

| IN3                         | IN2 | IN1 | IN0 | OUT | Type:                        | DFF / LATCH      |  |  |  |

| 0                           | 0   | 0   | 0   | 0   | Mode:                        | DFF              |  |  |  |

| 0                           | 0   | 0   | 1   | 1   | nSET/nRESET option:          | nRESET           |  |  |  |

| 0                           | 0   | 1   | 0   | 1   | Initial polarity:            | Low              |  |  |  |

| 0                           | 0   | 1   | 1   | 1   | Q output polarity:           | Non-inverted (Q) |  |  |  |

| <b>4-bit LUT0/CNT2/DLY2</b> |     |     |     |     | <b>3-bit LUT3/DFF/LATCH3</b> |                  |  |  |  |

| Type:                       | LUT |     |     |     | Type:                        | DFF / LATCH      |  |  |  |

| IN3                         | IN2 | IN1 | IN0 | OUT | Mode:                        | DFF              |  |  |  |

| 0                           | 0   | 0   | 0   | 0   | nSET/nRESET option:          | nRESET           |  |  |  |

| 0                           | 0   | 0   | 1   | 0   | Initial polarity:            | Low              |  |  |  |

| 0                           | 0   | 1   | 0   | 0   | Q output polarity:           | Non-inverted (Q) |  |  |  |

| 0                           | 0   | 1   | 1   | 0   |                              |                  |  |  |  |

| 0                           | 1   | 0   | 0   | 0   |                              |                  |  |  |  |

| 0                           | 1   | 0   | 1   | 0   |                              |                  |  |  |  |

| 0                           | 1   | 1   | 0   | 1   |                              |                  |  |  |  |

| 0                           | 1   | 1   | 1   | 1   |                              |                  |  |  |  |

| 1                           | 0   | 0   | 0   | 0   |                              |                  |  |  |  |

| 1                           | 0   | 0   | 1   | 1   |                              |                  |  |  |  |

| 1                           | 0   | 1   | 0   | 0   |                              |                  |  |  |  |

| 1                           | 0   | 1   | 1   | 1   |                              |                  |  |  |  |

| 1                           | 1   | 0   | 0   | 0   |                              |                  |  |  |  |

| 1                           | 1   | 0   | 1   | 1   |                              |                  |  |  |  |

| 1                           | 1   | 1   | 0   | 0   |                              |                  |  |  |  |

| 1                           | 1   | 1   | 1   | 1   |                              |                  |  |  |  |

Figure 8. LUTs properties

Figure 9. DFFs properties

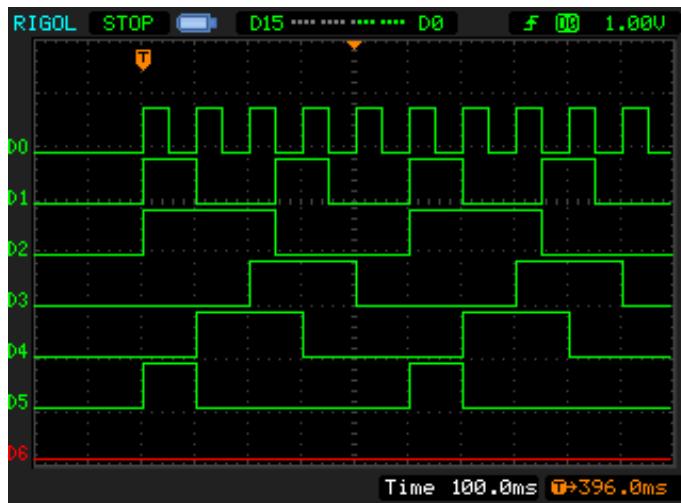

By taking a signal from the other DFFs outputs it is possible to get a divide by 5 signal as well, but with different duty cycle (not 50%, as previously) and phase shift (see figure 10): D3 – DFF2, D4 – DFF7, D5 – DFF6.

**Figure 10. Frequency divider functional diagram**

**(D0 – Input signal; D1 – F/2.5; D2, D3, D4, D5 – F/5)**

### Frequency divide by 4.5

Frequency division by 4.5 circuit is based on the previous circuit (divider by 5).

**Figure 12. Pins properties**

There are some additional blocks (DFF4 and 2-bit LUT5) which provide elimination of half clock period for DFFs (as in the divide by 1.5, 3, 3.5 circuit). This allows us to get divide by 4.5.

Blocks configurations are shown in figures 11-14.

**Figure 11. Frequency divide by 4.5 circuit design**

| 2-bit LUT5           |     |     |     |     |  | 2-bit LUT2/DFF/LATCH6 |                  |  |  |  |  |  |  |

|----------------------|-----|-----|-----|-----|--|-----------------------|------------------|--|--|--|--|--|--|

| IN3                  | IN2 | IN1 | IN0 | OUT |  | Type:                 | DFF / LATCH      |  |  |  |  |  |  |

| 0                    | 0   | 0   | 0   | 0   |  | Mode:                 | DFF              |  |  |  |  |  |  |

| 0                    | 0   | 0   | 1   | 1   |  | nSET/nRESET option:   | None             |  |  |  |  |  |  |

| 0                    | 0   | 1   | 0   | 1   |  | Initial polarity:     | Low              |  |  |  |  |  |  |

| 0                    | 0   | 1   | 1   | 0   |  | Q output polarity:    | Non-inverted (Q) |  |  |  |  |  |  |

| 3-bit LUT1           |     |     |     |     |  | 2-bit LUT3/DFF/LATCH7 |                  |  |  |  |  |  |  |

| IN3                  | IN2 | IN1 | IN0 | OUT |  | Type:                 | DFF / LATCH      |  |  |  |  |  |  |

| 0                    | 0   | 0   | 0   | 1   |  | Mode:                 | DFF              |  |  |  |  |  |  |

| 0                    | 0   | 0   | 1   | 0   |  | nSET/nRESET option:   | None             |  |  |  |  |  |  |

| 0                    | 0   | 1   | 0   | 0   |  | Initial polarity:     | Low              |  |  |  |  |  |  |

| 0                    | 0   | 1   | 1   | 0   |  | Q output polarity:    | Non-inverted (Q) |  |  |  |  |  |  |

| 3-bit LUT5           |     |     |     |     |  | 3-bit LUT2/DFF/LATCH2 |                  |  |  |  |  |  |  |

| IN3                  | IN2 | IN1 | IN0 | OUT |  | Type:                 | DFF / LATCH      |  |  |  |  |  |  |

| 0                    | 0   | 0   | 0   | 0   |  | Mode:                 | DFF              |  |  |  |  |  |  |

| 0                    | 0   | 0   | 1   | 0   |  | nSET/nRESET option:   | nRESET           |  |  |  |  |  |  |

| 0                    | 0   | 1   | 0   | 1   |  | Initial polarity:     | Low              |  |  |  |  |  |  |

| 0                    | 0   | 1   | 1   | 0   |  | Q output polarity:    | Non-inverted (Q) |  |  |  |  |  |  |

| 4-bit LUT0/CNT2/DLY2 |     |     |     |     |  | 3-bit LUT3/DFF/LATCH3 |                  |  |  |  |  |  |  |

| Type:                | LUT |     |     |     |  | Type:                 | DFF / LATCH      |  |  |  |  |  |  |

| IN3                  | IN2 | IN1 | IN0 | OUT |  | Mode:                 | DFF              |  |  |  |  |  |  |

| 0                    | 0   | 0   | 0   | 0   |  | nSET/nRESET option:   | nRESET           |  |  |  |  |  |  |

| 0                    | 0   | 0   | 1   | 0   |  | Initial polarity:     | Low              |  |  |  |  |  |  |

| 0                    | 0   | 1   | 0   | 0   |  | Q output polarity:    | Non-inverted (Q) |  |  |  |  |  |  |

| 0                    | 0   | 1   | 1   | 0   |  |                       |                  |  |  |  |  |  |  |

| 0                    | 1   | 0   | 0   | 1   |  |                       |                  |  |  |  |  |  |  |

| 0                    | 1   | 0   | 1   | 0   |  |                       |                  |  |  |  |  |  |  |

| 0                    | 1   | 1   | 0   | 0   |  |                       |                  |  |  |  |  |  |  |

| 0                    | 1   | 1   | 1   | 1   |  |                       |                  |  |  |  |  |  |  |

| 1                    | 0   | 0   | 0   | 0   |  |                       |                  |  |  |  |  |  |  |

| 1                    | 0   | 0   | 1   | 1   |  |                       |                  |  |  |  |  |  |  |

| 1                    | 0   | 1   | 0   | 0   |  |                       |                  |  |  |  |  |  |  |

| 1                    | 0   | 1   | 1   | 1   |  |                       |                  |  |  |  |  |  |  |

| 1                    | 1   | 0   | 0   | 0   |  |                       |                  |  |  |  |  |  |  |

| 1                    | 1   | 0   | 1   | 1   |  |                       |                  |  |  |  |  |  |  |

| 1                    | 1   | 1   | 0   | 0   |  |                       |                  |  |  |  |  |  |  |

| 1                    | 1   | 1   | 1   | 1   |  |                       |                  |  |  |  |  |  |  |

| 2-bit LUT4           |     |     |     |     |  | 2-bit LUT0/DFF/LATCH4 |                  |  |  |  |  |  |  |

| IN3                  | IN2 | IN1 | IN0 | OUT |  | Type:                 | DFF / LATCH      |  |  |  |  |  |  |

| 0                    | 0   | 0   | 0   | 0   |  | Mode:                 | DFF              |  |  |  |  |  |  |

| 0                    | 0   | 0   | 1   | 1   |  | nSET/nRESET option:   | None             |  |  |  |  |  |  |

| 0                    | 0   | 1   | 0   | 1   |  | Initial polarity:     | Low              |  |  |  |  |  |  |

| 0                    | 0   | 1   | 1   | 1   |  | Q output polarity:    | Inverted (nQ)    |  |  |  |  |  |  |

| 0                    | 1   | 0   | 0   | 0   |  |                       |                  |  |  |  |  |  |  |

| 0                    | 1   | 0   | 1   | 0   |  |                       |                  |  |  |  |  |  |  |

| 0                    | 1   | 1   | 0   | 0   |  |                       |                  |  |  |  |  |  |  |

Figure 13. LUTs properties

Figure 14. DFFs properties

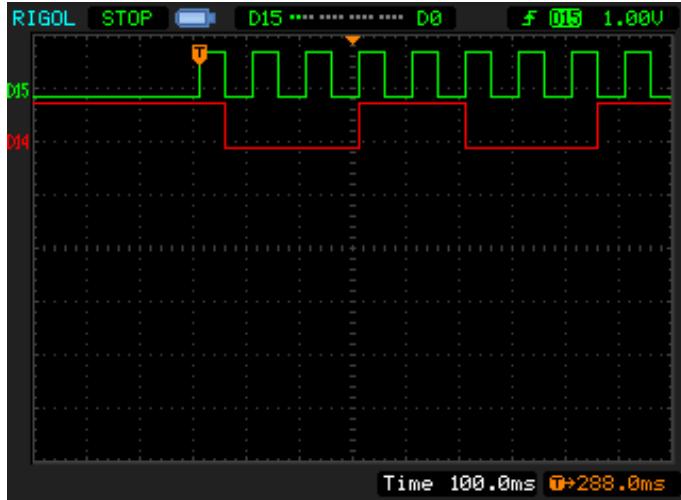

**Figure 15. Frequency divider functional waveforms**

(D15 – Input signal; D14 – F/4.5)

## Conclusion

Frequency dividers which are typically not simple to realize can be constructed using LUTS and DFFs.

As was shown, it is possible to divide a frequency by 1.5, 2.5, 3, 3.5, 4.5, 5. Such circuits may be used as a single device or as a part of a larger circuit.

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit [www.renesas.com/contact-us/](http://www.renesas.com/contact-us/).