-

-

设计资源

- 设计和开发

- 特色设计工具

- 合作伙伴

- 内容和培训

通用频率转换器 (UFT™)

瑞萨电子 FemtoClock® NG 通用频率转换器™ (UFT™) 可满足您所有的频率合成、频率转换和抖动衰减需求。 可从单个产品包中寻找支持 1、2、3 或 4 个 PLL 的系列产品。

作为频率合成器,可使用现成的基频模式晶体来生成 1MHz 到 1.3GHz 的输出频率。 通用频率转换器的内部架构允许使用 16MHz 到 40MHz 之间的任何晶体频率,无论所需频率如何。

作为频率转换器,该系列设备在 8 kHz 到 710MHz 的频率范围内接受为每个 PLL 配置一到两个输入参考时钟,以在需要时相互切换,同时在大多数情况下能生成 1MHz 到 1.3GHz 范围内的任何输出频率,而不发生频率转换错误。

通用频率转换器系列产品支持为预装入内部一次性可编程 (OTP) 非易失性存储器的每个 PLL 提供一到两个不同的引脚可选配置,以便在通电时能自动运行,或者可使用一个 I2C 串行接口来设置所需的频率转换配置。

除了晶体输入外,通用频率转换器 (UFT) 还为每个 PLL 配置两个时钟输入和两个输出。 每个输出可独立编程为 LVPECL 或 LVDS。 也可使用带单端输出的通用频率转换器版本。 可通过引脚或寄存器在各 PLL 配置的两个输入参考之间进行手动选择,或通过可恢复或不可恢复式还原自动选择。

这些设备可用于下列工作模式:

- 频率合成器模式允许从基频模式晶体输入中生成任意输出频率。 PLL 反馈环路支持分数反馈分频器。 它允许 VCO 工作频率变成晶体频率的非整数倍数。

- 高带宽频率转换器模式用于将一到两个具有相同标称频率的输入时钟转换成不相关的输出频率,从而削弱周期间抖动。 只使用高带宽 PLL 环路。 可使用预分频器级来支持高达 710MHz 的频率。

- 低带宽频率转换器模式(抖动衰减器模式)涉及两个 PLL 环路,通常用于实现输出到输入的频率转换率。 低带宽 PLL 环路可通过模数转换器驱动数控晶体振荡器 (DCXO)。 相位检测器经过优化后,可在最低 8 kHz 的频率下开始工作。 可使用外部低通滤波器。

关于频率转换器

频率转换器用于将输入信号的频率转换成输出信号所需的频率。 这些器件通常由振荡器或 PLL 和混频器组成。 在某些器件中,抖动衰减器电路可集成到频率转换器,以简化电路并减少物料清单 (BOM)。 瑞萨电子的丰富抖动衰减和频率转换器产品组合可以满足几乎任何应用的需求。

产品选型表

Outputs (#) |

Output Type |

Output Freq Range (MHz) |

Inputs (#) |

Input Freq (MHz) |

Input Type |

Output Banks (#) |

Core Voltage (V) |

Output Voltage (V) |

Output Skew (ps) |

Phase Jitter Typ RMS (ps) |

Phase Jitter Max RMS (ps) |

C-C Jitter Typ P-P (ps) |

C-C Jitter Max P-P (ps) |

Period Jitter Typ P-P (ps) |

Period Jitter Max P-P (ps) |

App Jitter Compliance |

Prog. Clock |

Prog. Interface |

Reference Output |

Abs. Pull Range Min. (± PPM) |

Price (USD) | 1ku |

|

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 器件号 | ||||||||||||||||||||||

| FemtoClock™ NG Universal Frequency Translator | 4 | HCSL, LVCMOS, LVDS, LVPECL | 0.008 - 1000 | 2 | 0.008 - 875 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 4 | 2.5, 3.3 | 2.5, 3.3, 1.8 | 50 | 0.2 | Yes | I2C | Yes | 9.55 | |||||||

| FemtoClock™ NG Universal Frequency Translator | 4 | HCSL, LVCMOS, LVDS, LVPECL | 0.008 - 1000 | 2 | 0.008 - 875 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 4 | 2.5, 3.3 | 2.5, 3.3, 1.8 | 50 | 0.35 | Yes | I2C | Yes | 6.081 | |||||||

| FemtoClock™ NG Universal Frequency Translator | 4 | HCSL, LVCMOS, LVDS, LVPECL | 0.008 - 1000 | 2 | 0.008 - 875 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 4 | 2.5, 3.3 | 2.5, 3.3, 1.8 | 50 | 0.276 | Yes | I2C | Yes | 5.794 | |||||||

| FemtoClock NG Universal Frequency Translator (2-in/1-PLL/8-out) | 8 | LVCMOS, LVDS, LVPECL | 0.008 - 1000 | 2 | 0.008 - 875 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 4 | 2.5, 3.3 | 2.5, 3.3 | 45 | 0.27, 0.28 | 0.3 | Yes | I2C | No, Yes | 14.19 | ||||||

| FemtoClock NG Dual Universal Frequency Translator (4-in/2-PLL/8-out) | 8 | LVCMOS, LVDS, LVPECL | 0.008 - 1000 | 4 | 0.008 - 875 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 4 | 2.5, 3.3 | 2.5, 3.3 | 45 | 0.26, 0.28 | 0.3 | Yes | I2C, SPI | No, Yes | 29.22 | ||||||

| FemtoClock NG Dual Universal Frequency Translator (2-in/2-PLL/8-out) | 8 | LVCMOS, LVDS, LVPECL | 0.008 - 1000 | 2 | 0.008 - 875 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 4 | 2.5, 3.3 | 2.5, 3.3 | 45 | 0.24, 0.28 | 0.3 | Yes | I2C | No, Yes | 23.46 | ||||||

| FemtoClock NG Universal Frequency Translator (2-in/1-PLL/8-out) | 8 | HCSL, LVCMOS, LVDS, LVPECL | 0.008 - 1000 | 2 | 0.008 - 875 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL | 4 | 2.5, 3.3 | 1.8, 2.5, 3.3 | 45 | 0.28 | Yes | I2C, SPI | Yes | 9.973 | |||||||

| FemtoClock NG Universal Frequency Translator (4-in/2-PLL/8-out) | 8 | HCSL, LVCMOS, LVDS, LVPECL | 0.008 - 1000 | 4 | 0.008 - 875 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 4 | 2.5, 3.3 | 2.5, 3.3 | 45 | 0.28 | Yes | I2C, SPI | Yes | 12.72 | |||||||

| FemtoClock NG Universal Frequency Translator (2-in/2-PLL/8-out) | 8 | HCSL, LVCMOS, LVDS, LVPECL | 0.008 - 1000 | 2 | 0.008 - 875 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 4 | 2.5, 3.3 | 2.5, 3.3 | 45 | 0.28 | Yes | I2C | Yes | 12.99 | |||||||

| FemtoClock NG Triple Universal Frequency Translator | 6 | LVDS, LVPECL | 0.98 - 1300 | 7 | 0.008 - 710 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 3 | 2.5 | 2.5 | 0.333 | 0.465 | 40 | Yes | I2C | No | 72.42 |

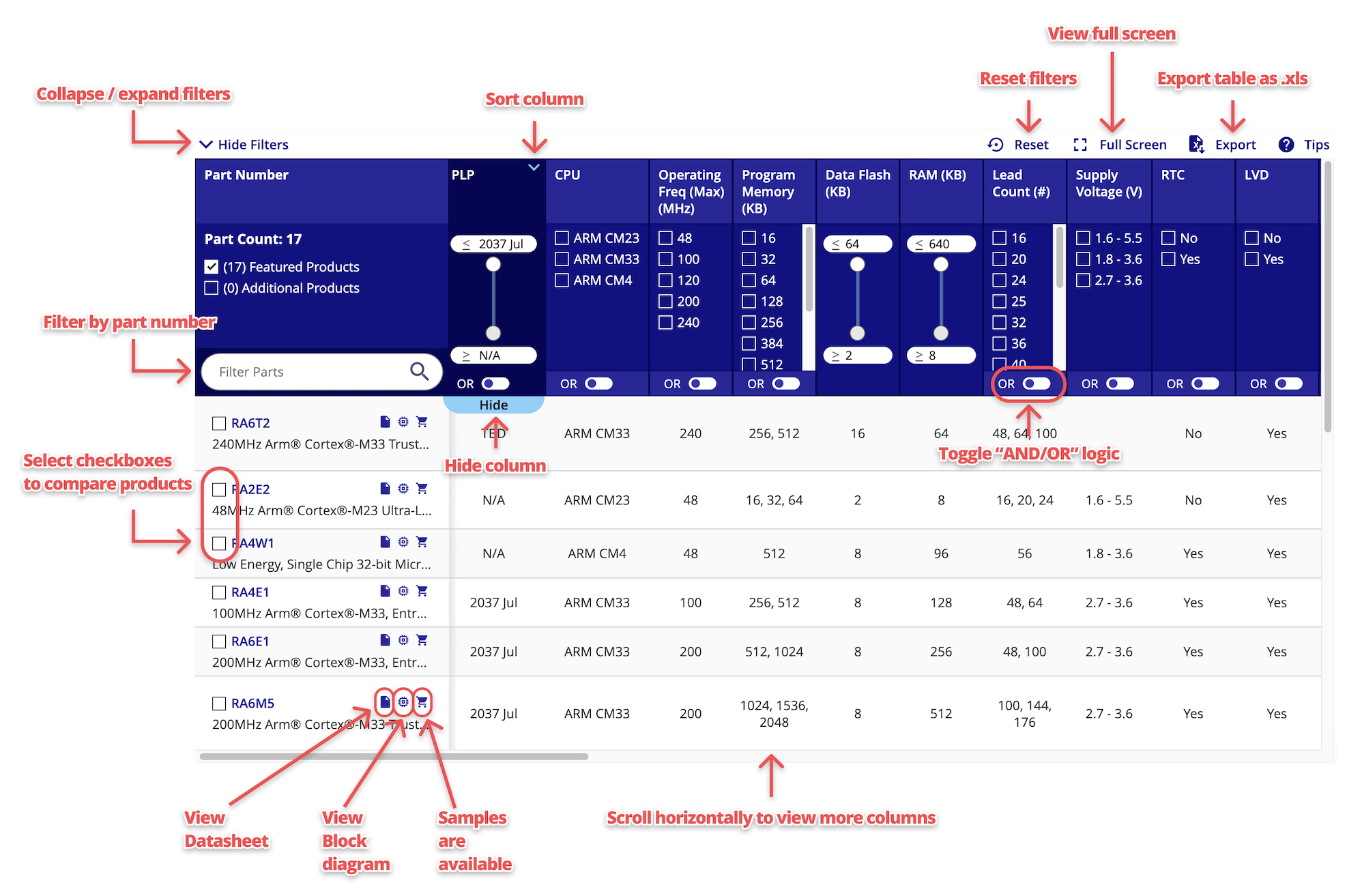

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product

视频和培训

An overview of IDT's 8T49N240 programmable clock generator and jitter attenuator IC, featuring sub-200fs phase noise, helping to ease design constraints and lower total system costs 10Gbps and 40/100Gbps multi-lane systems.

The IDT® 8T49N240 is the latest member of IDT's third-generation Universal Frequency Translator (UFT™) family. It features the ability to produce virtually any common output frequency from virtually any input frequency. The highly-flexible, high-performance clock generator and jitter attenuator is ideal for 10Gbps or multi-lane 40Gpbs / 100Gbps timing applications where 300fs of phase noise is typically the maximum acceptable amount allowed at the physical ports. The 200fs phase noise specification of the 8T49N240 provides ample noise margin, enabling engineers to simplify their clock tree designs and utilize lower cost PCBs.

The 8T49N240 features a 6 x 6 mm package footprint, requiring considerably less PCB area than most other solutions with this level of performance and flexibility. The device is also suitable for 25/28Gbps interfaces.

Visit https://www.IDT.com/8T49N240 to learn more and request samples.