-

-

设计资源

- 设计和开发

- 特色设计工具

- 合作伙伴

- 内容和培训

8V79S680

circle有效可提供样片符合 JESD204B 标准的扇出缓冲器和分频器

概览

简介

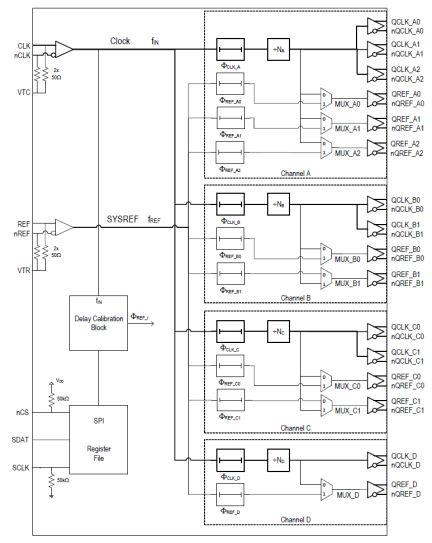

8V79S680 是一款完全集成的时钟和 SYSREF 信号扇出缓冲器,适用于 JESD204B 应用。 该器件是专为无线基站无线电设备电路板设计的高性能时钟和转换器同步解决方案,符合 JESD204B 子类 0、1 和 2 标准。 该器件的主要功能是分配和扇出由 JESB204B 时钟发生器(如 8V19N480)生成的高频时钟和低频系统参考信号,从而扩展其扇出功能并提供额外的相位延迟。 8V79S680 经过优化,可提供相位噪声极低的时钟和精确、相位可调的 SYSREF 同步信号,满足 GSM、WCDMA、LTE、LTE-A 无线电板实施的要求。低偏移输出、低器件间偏移特性和快速输出上升/下降时间有助于系统设计实现跨器件的确定性时钟和 SYSREF 相位关系。

该器件将输入时钟和 JESD204B SYSREF 信号分配到四个扇出通道。 在每个通道中,输入时钟和 SYSREF 信号均扇出到多个时钟(QCLK)和 SYSREF(QREF)输出。 时钟信号可以在每个通道中进行分频。 可配置的相位延迟电路可用于时钟和 SYSREF 信号。 所有信号路径中的传播延迟都是完全确定的,以支持一个器件内时钟和 SYSREF 信号之间的固定相位关系。 时钟分频器可以旁路,以实现低延迟时钟路径。 该器件可辅助实现器件内部分频器之间以及多个器件之间的同步,消除分频器在电源和配置周期之间引入的相位模糊性。

每个通道支持高达 3GHz 的时钟频率。 在另一种配置中,例如 JESD204B 子类 0 和 2,SYSREF(QREF)输出可配置为常规时钟输出,从而为器件添加额外的时钟扇出。

所有输出在幅度配置、输出信号端接方面都非常灵活,并允许直流和交流耦合。 不使用时可禁用输出并关断电源。 SYSREF 输出预偏置功能可防止开机故障,并实现系统同步信号的交流耦合。

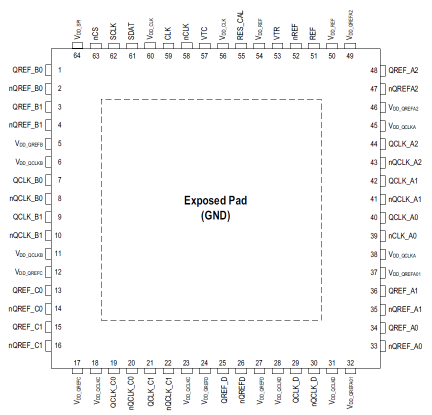

该器件通过一个三线 SPI 串行接口进行配置。 该器件采用无铅(RoHS 6)64 引脚 VFQFN 封装。扩展的温度范围支持无线基础设施、电信和网络终端设备的要求。 该器件属于 IDT 高性能时钟系列。

特性

- 支持高速、低相位噪声转换器时钟

- 时钟和 SYSREF 信号的分配、扇出、相位延迟

- 极低的输出本底噪声:-158.8dBc/Hz 本底噪声(245.76MHz)

- 支持高达 3GHz 的时钟频率,包括 983.04MHz、491.52MHz、245.76MHz 和 122.88MHz 的时钟输出频率

- 4 个输出通道,共 16 个差分输出:

— 8 个专用时钟输出

— 8 个输出可配置为带有独立相位延迟级的 SYSREF 输出,或配置为附加时钟输出 - 每个通道包含:

— 分频器:÷1、÷2、÷4、÷6、÷8、÷12、÷16

— 时钟相位延迟电路 - 时钟相位延迟电路

— 时钟:延迟单位为时钟周期;256 步

— SYSREF:可配置的精密相位延迟电路:8 级 131ps、262ps、393ps 或 524ps - 灵活的差分输出:

— LVDS/LVPECL 可配置

— 振幅可配置

— 未使用输出的省电模式

— 支持直流和交流耦合

— QREF(SYSREF)输出预偏置功能,可防止在打开或关闭输出时出现故障 - 电源电压:

— 3.3V 内核和信号 I/O

— 1.8V 数字控制 SPI I/O(3.3V 容限输入) - 64 VFQFN-P 封装(9mm x 9mm x 0.85mm)

- 环境温度范围:-40°C 至 +85°C

产品对比

应用

文档

|

|

|

|

|---|---|---|

| 类型 | 文档标题 | 日期 |

| 数据手册 | PDF 940 KB | |

| 产品变更通告 | PDF 1.26 MB | |

| 概览 | PDF 331 KB | |

| 应用文档 | PDF 601 KB | |

| 应用文档 | PDF 586 KB | |

| 产品变更通告 | PDF 983 KB | |

6 items

|

||

设计和开发

模型

ECAD 模块

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

产品选择

Pkg. Type |

Lead Count (#) |

Temp. Grade |

Pb (Lead) Free |

Carrier Type |

Moisture Sensitivity Level (MSL) |

Price (USD) | 1ku |

购买 / 样片 |

|

|---|---|---|---|---|---|---|---|---|

| 器件号 | ||||||||

| VFQFPN | 64 | I | Yes | Tray | 3 | 12.58 | 获取样片, | |

| VFQFPN | 64 | I | Yes | Reel | 3 |

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product

视频和培训

新闻和博客

|

瑞萨电子拓展5G毫米波产品阵容,推出具有卓越发射器输出功率性能的波束成形器 | 新闻 | 2021年11月10日 |