Evaluation Board 8EBV89317 for Industrial Automation and Power Systems - 10G Ethernet PLL and IEEE 1588 Synthesizer

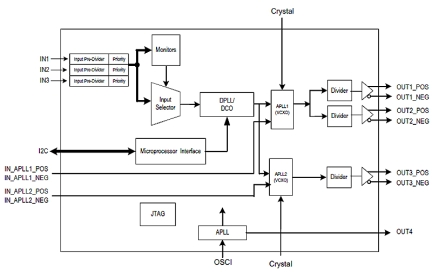

The 8EBV89317 10G Ethernet PLL Evaluation board for Industrial Automation and Power Systems allows the user to connect up to three single ended reference inputs via SMA...