# Testing Power-up Conditions on GreenPAK Evaluation Board

Author: Luke Thomas Date: Oct 22, 2014

### Introduction

Testing each combination of input logic at power-up is important in ensuring correctness in all cases for a given design. The GreenPAK evaluation board is designed for testing power-up conditions in GreenPAK hardware.

This application note will cover a simple example where the designer must test power-up conditions and determine an appropriate solution.

## **A Simple Delayed Output**

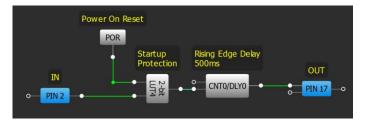

The example circuit is a rising edge delay with one input and one output. The output copies the input; however, the input must be held HIGH for 500ms before the output will be HIGH. The design of this circuit is only one delay block in the GreenPAK software. The design is shown in Figure 1.

# **Testing the Power-Up Response**

To test the device's power-up response, you must program the design into the NVM (Non-Volatile Memory). Since GreenPAK is a one-time programmable device, make sure the design does as you intend it in normal operation before testing the power-up conditions.

Figure 1. GreenPAK Delay Circuit

# **Programming the Chip**

From the GreenPAK designer software, start the

Emulation Tool by pressing the Emulator button on the ribbon.

From the Emulator Window, program the device by pressing the "Program" button found in the top right of the window.

The software will notify you that the chip can be programmed only once, continue by clicking the "Yes" button. After a few moments, the software will notify you if the programming was a success.<sup>1</sup>

### **Test Mode**

Once the chip has been programmed in NVM, you can enter Test Mode without performing Emulation. Emulation drives the register bits on power-up, so you cannot get a true startup response in Emulator mode. Enter Test Mode by pressing the Test Mode button found in the top right of the Emulation Window. The Test Mode button will highlight orange to show the board is in Test Mode.<sup>2</sup>

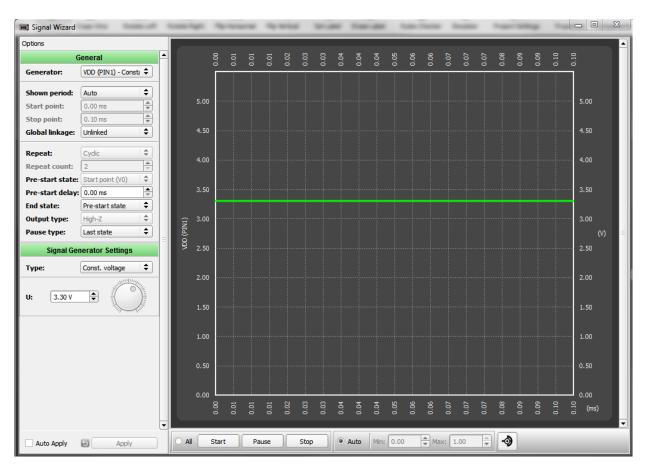

## Configuring the Signal Generator

Click the Edit button next to the VDD Signal Generator PIN1 (Figure 2) in the Emulation Window. You will see the signal wizard appear, it will be similar to Figure 3.

Figure 2. Signals' Interface from Emulation

On the left hand side of the signal wizard (Figure 3), you may choose to Globally Link the signal.

<sup>&</sup>lt;sup>1</sup> Note: If the chip has already been programmed, you must replace the chip on the evaluation board with a chip that has never been programmed.

<sup>&</sup>lt;sup>2</sup> Note: The Emulation button should not be highlighted.

Figure 3. Signal Wizard

Global linkage causes all linked signals to start, pause and stop together when using Start Gens, Pause Gens, and Stop Gens buttons at the bottom of the emulator window.

By default, all generators except for VDD are globally linked.<sup>3</sup>

For this example, we will Globally Link VDD. In order to simulate power-up conditions, we will be pausing and starting VDD, thus in the signal wizard window select the Pause Type to be "0.00 V" from the drop down menu.

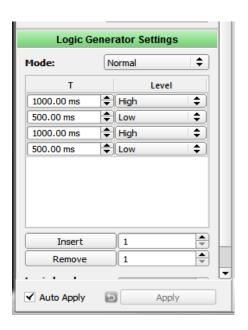

In order to simulate the input being HIGH while the VDD is powered up, we will create a logic generator

on the input and have it start HIGH at the same time as VDD. This is done by right-clicking on PIN2 in the emulator window and selecting "Logic Generator".

Choose Edit by PIN2 to bring up the Signal Wizard. Insert two more logic levels and configure the settings like those shown in Figure 4.4

Since the two signals are linked, you can power down the device by pressing the button "Pause Gens" and repower the device be pressing "Start Gens".

This also starts the Logic Generator on PIN2, which will simulate the case in which the input is engaged as VDD powers on.

<sup>&</sup>lt;sup>3</sup> Note: any Signal or Logic Generator can be Globally Linked/Unlinked by pressing the "G" in the signals' interface, Figure 2.

<sup>&</sup>lt;sup>4</sup> Note: Don't forget to hit Apply

Figure 4. Logic Generator Settings

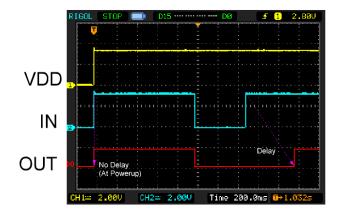

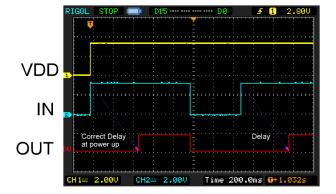

The waveform in Figure 6 shows both VDD and IN simultaneously rising.

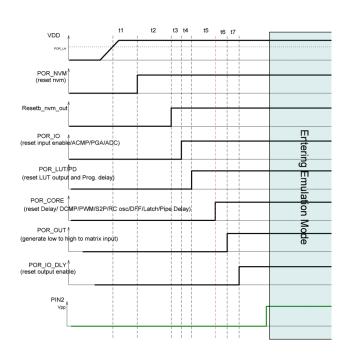

## Power-up Sequence on GreenPAK

The GreenPAK has a specific power-up sequence for powering each block. The startup sequence is shown in Figure 5. POR\_IO, POR\_LUT/PD and POR\_CORE show the order in which blocks are powered up and enabled. The POR\_IO is the first power signal applied to blocks and it enables the IO inputs, ACMP, PGA, and ADC. After those have been powered on, POR\_LUT/PD is applied. LUTs will produce their outputs and the Prog delay is powered up. POR\_CORE is powered last and includes all other blocks. On power-up, delay blocks pass the input to the output without enforcing any delay. Thus, when a logical HIGH is applied at startup, the delay will not force a delayed signal, but the delay block will immediately output HIGH (Figure 6).

Figure 5. GreenPAK2 Startup

Figure 6. No Startup Logic

Figure 7. With Startup Logic

## **Solving the Problem**

If the design needed the delay to occur even if IN is HIGH when VDD goes HIGH, you can add a LUT with the POR block to solve the problem. As referenced in Figure 5, the POR signal stays LOW until all other blocks have been powered up.

A LUT added to the input of the Delay block can enforce a LOW signal until the POR signal has been set. Figure 8 contains the new design. 2-bit LUT4 will be configured as an AND gate, which will keep the input to the delay block LOW until POR has been set. Once POR is set, the delay block will enforce delays and work as expected. The waveform of the new design is shown in Figure 7.

Figure 8. Circuit with Startup Logic

### Conclusion

The GreenPAK Evaluation Board is an effective tool for testing and designing GreenPAK chips. The Test Mode is an essential feature to testing power-up conditions and can be combined with global linkage to see a design's response to different inputs when power is applied.

### **Related Files**

Programming code for GreenPAK Designer.

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.