-

-

-

設計リソース

- 設計・開発

- 注目の設計ツール

- パートナー

- コンテンツ&トレーニング

-

サポート

-

サンプル&ご購入

-

ルネサスサイトからの直接購入

便利なルネサスからの直接購入を選択できるようになりました。

- 購入関連情報

-

ルネサスサイトからの直接購入

8430S10I-02

circle廃止品Clock Generator For Cavium Processors

概要

説明

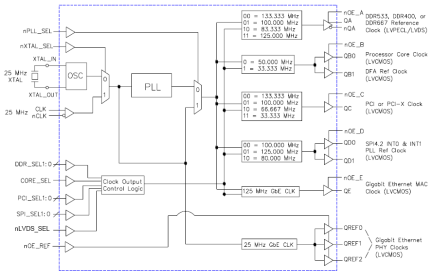

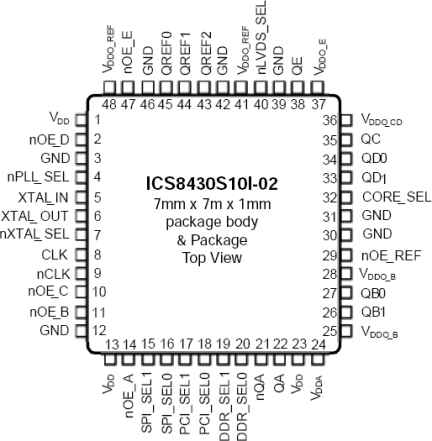

The 8430S10I-02 is a PLL-based clock generator specifically designed for Cavium Networks SoC processors. This high performance device is optimized to generate the processor core reference clock, the DDR reference clocks, the PCI/PCI-X bus clocks, and the clocks for both the Gigabit Ethernet MAC and PHY. The clock generator offers ultra low-jitter, low-skew clock outputs, and edge rates that easily meet the input requirements for the CN30XX/CN31XX/CN38XX/CN58XX processors. The output frequencies are generated from a 25MHz external input source or an external 25MHz parallel resonant crystal. The extended temperature range of the 8430S10I-02 supports telecommunication, networking, and storage requirements.

特長

- One selectable differential output pair for DDR 533/400/667, LVPECL, LVDS interface levels

- Nine LVCMOS/ LVTTL outputs, 20Ω typical output impedance

- Selectable external crystal or differential (single-ended) input source

- Crystal oscillator interface designed for 25MHz, parallel resonant crystal

- Differential input pair (CLK, nCLK) accepts LVPECL, LVDS, SSTL input levels

- Internal resistor bias on nCLK pin allows the user to drive CLK input with external single-ended (LVCMOS/ LVTTL) input levels

- Power output supply modes LVDS and LVPECL - full 3.3V LVCMOS - full 3.3V or mixed 3.3V core/2.5V output

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

製品選択

Pkg. Type |

Lead Count (#) |

Temp. Grade |

Pb (Lead) Free |

Carrier Type |

ご購入 / サンプル |

|

|---|---|---|---|---|---|---|

| 型名 | ||||||

| PTQFP | 48 | I | Yes | Tray | ||

| PTQFP | 48 | I | Yes | Reel |

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product