発行日:2017年10月19日

# **RENESAS TECHNICAL UPDATE**

〒135-0061 東京都江東区豊洲 3-2-24 豊洲フォレシアルネサス エレクトロニクス株式会社

問合せ窓口 http://japan.renesas.com/contact/

E-mail: csc@renesas.com

| 製   | 品分類   | 品分類 MPU & MCU 発行番号 TN-RX*-A164B/J |        | 164B/J | Rev.                                            | 第2版  |  |

|-----|-------|-----------------------------------|--------|--------|-------------------------------------------------|------|--|

| 題名  |       |                                   |        |        | 技術情報                                            |      |  |

| 適   |       |                                   | 対象ロット等 |        |                                                 |      |  |

| 用製品 | RX65N | グループ、RX651 グループ                   | 全ロット   | 関連資料   | RX65N グループ、I<br>ユーザーズマニュフ<br>Rev.1.00 (R01UH059 | アルハー |  |

RX65N グループ、RX651 グループ ユーザーズマニュアル ハードウェア編 Rev.1.00 において、誤記がありましたので、以下のとおり訂正いたします。

TN-RX\*-A164A/J に No.8 を追加し、No.11 の内容を変更しました。また、No.9、No.10 の変更後の用語を一部見直しました。変更箇所を赤字で示します。

| No. | 章番号                         | 訂正内容                                       |

|-----|-----------------------------|--------------------------------------------|

| 1   | 1章 概要                       | 表1.1 仕様概要(5/8) リアルタイムクロック機能に注記を追加          |

| 2   | 23章 マルチファンクションピンコントローラ(MPC) | 23.2.24 外部バス制御レジスタ0 (PFBCR0)のビット名誤記を訂正     |

| 3   | 41章 クワッドシリアルペリフェラルインタフェース   | 41.4.3 シリアルフラッシュメモリを使用する場合の注意事項に変更         |

|     | (QSPI)                      |                                            |

| 4   | 44章 SDスレーブインタフェース(SDSI)     | 44.1 概要 本文内誤記を訂正                           |

| 5   | 50章 12ビットA/Dコンバータ(S12ADFa)  | 50.1 仕様概要 表50.1 動作モードの誤記を訂正                |

| 6   | 51章 12ビットD/Aコンバータ(R12DA)    | 51.3 動作説明 本文(3)                            |

|     |                             | ADCLKが周辺モジュールクロックよりも速い場合の動作条件を削除           |

| 7   | 51章 12ビットD/Aコンバータ(R12DA)    | 51.3.1 D/A変換とA/D変換の干渉対策 本文(4)および図51.4      |

|     |                             | ADCLKが周辺モジュールクロックよりも速い場合の動作条件を削除           |

| 8   | 57章 電気的特性                   | 57.1 絶対最大定格 ジャンクション温度を追加                   |

| 9   | 57章 電気的特性                   | 57.2 DC特性 ディープスタンバイ電流値の誤記訂正                |

| 10  | 57章 電気的特性                   | 57.2 DC特性 表57.6 リファレンス電源電流 12ビットA/D変換中(ユニッ |

|     |                             | ト0)の電気的特性値の誤記を訂正                           |

| 11  | 57章 電気的特性                   | 57.2 DC特性 熱抵抗を追加                           |

# No.1 1.1 仕様概要

表 1.1 のリアルタイムクロックの機能欄、および表末に以下のとおり注 4 を追加いたします。

# Page 66 of 2491

表1.1 仕様概要 (5/8)

| 分類  | モジュール/機能               | 説明                                                                                              |

|-----|------------------------|-------------------------------------------------------------------------------------------------|

| タイマ | プログラマブルパルス             | • (4ビット× 4グループ) × 2ユニット                                                                         |

|     | ジェネレータ(PPG)            | • MTU3、またはTPUからの出力をトリガとしてパルスを出力                                                                 |

|     |                        | • 最大32本のパルス出力                                                                                   |

|     | 8ビットタイマ(TMRb)          | • (8ビット× 2チャネル) × 2ユニット                                                                         |

|     |                        | • 7種類の内部クロック(PCLKB/1, PCLKB/2, PCLKB/8, PCLKB/32, PCLKB/64, PCLKB/1024, PCLKB/8192)と外部クロックを選択可能 |

|     |                        | • 任意のデューティ比のパルス出力やPWM出力が可能                                                                      |

|     |                        | • 2チャネルをカスケード接続し16ビットタイマとして使用可能                                                                 |

|     |                        | • A/Dコンバータの変換開始トリガを生成可能                                                                         |

|     |                        | • SCI5, SCI6, SCI12のボーレートクロック生成可能                                                               |

|     |                        | • ELCによるイベントリンク機能をサポート                                                                          |

|     | コンペアマッチタイマ             | • (16ビット× 2チャネル) × 2ユニット                                                                        |

|     | (CMT)                  | • 4種類のクロック(PCLKB/8, PCLKB/32, PCLKB/128, PCLKB/512)を選択可能                                        |

|     |                        | • ELCによるイベントリンク機能をサポート                                                                          |

|     | コンペアマッチタイマW            | • (32ビット× 1チャネル) × 2ユニット                                                                        |

|     | (CMTW)                 | <ul><li>コンペアマッチ、インプットキャプチャ入力およびアウトプットコンペア出力が可能</li></ul>                                        |

|     |                        | • 4種類のクロック(PCLKB/8, PCLKB/32, PCLKB/128, PCLKB/512)を選択可能                                        |

|     |                        | • コンペアマッチ、インプットキャプチャ、およびアウトプットコンペア発生時、割り                                                        |

|     |                        | 込み要求の発生を選択可能                                                                                    |

|     |                        | • ELCによるイベントリンク機能をサポート                                                                          |

|     | リアルタイムクロック             | • クロックソース:メインクロック、サブクロック                                                                        |

|     | (RTCd) <sup>(注4)</sup> | • 時計カウント/秒単位の32ビットバイナリカウントを選択可能                                                                 |

|     |                        | <ul><li>時計/カレンダ機能</li></ul>                                                                     |

|     |                        | • 割り込み要因:アラーム割り込み、周期割り込み、桁上げ割り込み                                                                |

|     |                        | • バッテリバックアップ動作                                                                                  |

|     |                        | • 3値タイムキャプチャ機能                                                                                  |

|     |                        | • ELCによるイベントリンク機能をサポート                                                                          |

|     |                        | 省略                                                                                              |

# Page 69 of 2491

| I               | 省略                                                          |  |  |  |  |  |  |

|-----------------|-------------------------------------------------------------|--|--|--|--|--|--|

| 動作周波数           | 120MHz max                                                  |  |  |  |  |  |  |

| 電源電圧            | VCC = AVCC0 = AVCC1 = VCC_USB = 2.7~3.6V, 2.7≦VREFH0≦AVCC0, |  |  |  |  |  |  |

|                 | V <sub>BATT</sub> = 2.0∼3.6V                                |  |  |  |  |  |  |

| 動作周囲温度          | Dバージョン: -40~+85°C                                           |  |  |  |  |  |  |

|                 | Gバージョン: −40~+105°C (計画中)                                    |  |  |  |  |  |  |

| パッケージ           | 145ピンTFLGA (PTLG0145KA-A)                                   |  |  |  |  |  |  |

|                 | 144ピンLFQFP (PLQP0144KA-B)                                   |  |  |  |  |  |  |

|                 | 100ピンTFLGA (PTLG0100JA-A)                                   |  |  |  |  |  |  |

|                 | 100ピンLFQFP (PLQP0100KB-B)                                   |  |  |  |  |  |  |

| オンチップデバッギングシステム | • E1エミュレータ(JTAGおよびFINEインタフェース)                              |  |  |  |  |  |  |

|                 | • E20エミュレータ(JTAGインタフェース)                                    |  |  |  |  |  |  |

- 注 1. Magic Packet™は、Advanced Micro Devices, Inc.の登録商標です。 注 2. 暗号機能の有無で型名が異なります。

- 注 3. SDHI/SDSI の有無で型名が異なります。(コードフラッシュメモリ容量が 1M バイト以下の製品)

- リアルタイムクロックを使用しない場合、「31.6.7 リアルタイムクロックを使用しない場合の初期化手順」に従ってリアル 注 4. タイムクロック内のレジスタを初期化してください。

# No.2 23.2.24 外部バス制御レジスタ 0 (PFBCR0) (Page 808 of 2491)

以下のとおり ADRHMS2 ビットのビット名を訂正いたします。

#### 【変更前】

| ビット | シンボル    | ビット名               | 機能                | R/W |  |  |  |  |  |  |

|-----|---------|--------------------|-------------------|-----|--|--|--|--|--|--|

| Ī   | 省略      |                    |                   |     |  |  |  |  |  |  |

| b1  | ADRHMS  | A16~A23 出力許可ビット    | 表 23.20 を参照してください | R/W |  |  |  |  |  |  |

| b2  | ADRHMS2 | A18~A20 出力許可 2 ビット |                   | R/W |  |  |  |  |  |  |

| 省略  |         |                    |                   |     |  |  |  |  |  |  |

#### 【変更後】

| ビット | シンボル    | ビット名               | 機能                | R/W |  |  |  |  |  |  |

|-----|---------|--------------------|-------------------|-----|--|--|--|--|--|--|

|     | 省略      |                    |                   |     |  |  |  |  |  |  |

| b1  | ADRHMS  | A16~A23 出力許可ビット    | 表 23.20 を参照してください | R/W |  |  |  |  |  |  |

| b2  | ADRHMS2 | A16~A23 出力許可 2 ビット |                   | R/W |  |  |  |  |  |  |

|     | 省略      |                    |                   |     |  |  |  |  |  |  |

# No.3 41.4 使用時の注意事項(Page 1972 of 2491)

QSPI 章の「41.4 使用時の注意事項」において、41.4.3 の見出し、および記載内容を以下のとおり変更いたします。

# 【変更前】

# 41.4.3 Single/Dual/Quad-SPI 動作で SPI モード 3 を使用する場合

Single/Dual/Quad-SPI 動作でシリアルフラッシュメモリを使用する場合は、SPCMDn.CPOL ビット  $(n=0\sim3)$ を"1"、SPCMDn.CPHA ビット $(n=0\sim3)$ を"1"に設定し、SPI モード 3 を使用してください。

#### 【変更後】

# 41.4.3 シリアルフラッシュメモリを使用する場合の注意事項

SPI動作モードを Dual-SPI または Quad-SPI にしてシリアルフラッシュメモリを使用する場合、SPCMDn.CPOL、 CPHA ビット $(n=0\sim3)$ を両方とも"1"にし、SPI モード 3 に設定してください。モード  $0\sim$ モード 2 は使用できません。また、SPCMDn.SPNDEN、SLNDEN、SCKDEN ビットをすべて"1"にして遅延期間を設けてください。

# No.4 44.1 概要(Page 2040 of 2491)

SDSI 章の「44.1 概要」本文3行目を以下のとおり訂正いたします。

#### 【変更前】

20M バイト/秒以上の最高スループットを実現することが可能です。

#### 【変更後】

25M バイト/秒の最高スループットを実現することが可能です。

#### No.5 50.1 概要(Page 2168 of 2491)

S12ADFa 章の「50.1 概要」において、「表 50.1 12 ビット A/D コンバータの仕様(1/2)」の動作モードの内容欄 1 行目を以下のとおり訂正いたします。

#### 【変更前】

動作モードは3ユニット個別で設定可能です。

# 【変更後】

動作モードは2ユニット個別で設定可能です。

# No.6 51.3 動作説明(Page 2313 of 2491)

R12DA 章の「51.3 動作説明」において、(3)の本文を以下のとおり訂正いたします。

#### 【変更前】

(3) DADRO レジスタを書き換えると変換を開始します。tDCONV 時間経過後、変換結果が出力されます。 DAADSCR.DAADST ビットが"1" (D/A 変換と A/D 変換の干渉対策が有効)の場合、D/A 変換開始まで最大 A/D 変換1回分待たされます(ADCLK が周辺モジュールクロックよりも速い場合は、A/D 変換1回分以上待たされる場合があります)。

#### 【変更後】

(3) DADR0 レジスタを書き換えると変換を開始します。tDCONV 時間経過後、変換結果が出力されます。 DAADSCR.DAADST ビットが"1" (D/A 変換と A/D 変換の干渉対策が有効)の場合、D/A 変換開始まで最大 A/D 変換 1 回分待たされます。

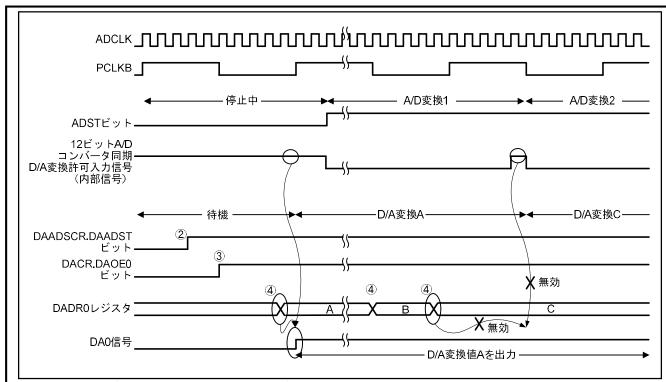

### No.7 51.3.1 D/A 変換と A/D 変換の干渉対策

R12AD 章の「51.3.1 D/A 変換と A/D 変換の干渉対策」において、ADCLK が周辺モジュールクロックよりも速い場合に関する記述を削除いたします。

#### Page 2314 of 2491

(4)の本文を以下のとおり訂正いたします。

#### 【変更前】

(4) DADR0 レジスタを設定する(ADCLK が周辺モジュールクロックよりも速い場合は、A/D 変換 1 回分以上待たされる場合があります)。

#### 【変更後】

(4) DADR0 レジスタを設定する。

#### Page 2315 of 2491

図 51.3 下の本文、および図 51.4 を削除いたします。

ADCLK が PCLK よりも速い場合、A/D 変換 1 と A/D 変換 2 の間に出力される ADCLK 1 周期分の 12 ビット A/D コンバータ同期 D/A 変換許可入力信号を 12 ビット D/A コンバータが取り込めない可能性があります。図 51.4 に 12 ビット D/A コンバータが 12 ビット A/D コンバータ同期 D/A 変換許可入力信号を取り込めない例を示します。この場合、DAO 信号は D/A 変換値 A の出力を継続します。

図 51.4 12 ビット D/A コンバータが 12 ビット A/D コンバータ同期 D/A 変換許可入力信号を取り込めない例

# No.8 57.1 絶対最大定格(Page 2407 of 2491)

電気的特性章の「57.1 絶対最大定格」において、以下のとおり「表 57.1 絶対最大定格」にジャンクション温度の特性値を追加いたします。

# 【変更前】

| 項目                                  | 記号                | 定格値                        | 単位 |

|-------------------------------------|-------------------|----------------------------|----|

| 電源電圧                                | VCC, VCC_USB      | −0.3 ~ +4.0                | V  |

| V <sub>BATT</sub> 電源電圧              | $V_{BATT}$        | −0.3 ~ +4.0                | V  |

| 入力電圧 (5Vトレラント対応ポート(注1)以外)           | V <sub>in</sub>   | -0.3 ~ VCC + 0.3 (最大4.0)   | V  |

| 入力電圧(5Vトレラント対応ポート <sup>(注1)</sup> ) | V <sub>in</sub>   | -0.3 ~ VCC + 4.0 (最大5.8)   | V  |

| リファレンス電源電圧                          | VREFH0            | -0.3 ~ AVCC0 + 0.3 (最大4.0) | V  |

| アナログ電源電圧                            | AVCC0, AVCC1 (注2) | −0.3 ~ +4.0                | V  |

| アナログ入力電圧                            | V <sub>AN</sub>   | -0.3 ~ AVCC + 0.3 (最大4.0)  | V  |

| 保存温度                                | $T_{stg}$         | −55 <b>~</b> +125          | °C |

# 【変更後】

| 項                      | i 🗏                       | 記号                | 定格値                        | 単位 |

|------------------------|---------------------------|-------------------|----------------------------|----|

| 電源電圧                   |                           | VCC, VCC_USB      | −0.3 ~ +4.0                | V  |

| V <sub>BATT</sub> 電源電圧 |                           | V <sub>BATT</sub> | −0.3 ~ +4.0                | ٧  |

| 入力電圧 (5Vトレラント対         | 対応ポート <sup>(注1)</sup> 以外) | V <sub>in</sub>   | -0.3 ~ VCC + 0.3 (最大4.0)   | V  |

| 入力電圧(5Vトレラント対          | 応ポート <sup>(注1)</sup> )    | V <sub>in</sub>   | -0.3 ~ VCC + 4.0 (最大5.8)   | ٧  |

| リファレンス電源電圧             |                           | VREFH0            | -0.3 ~ AVCC0 + 0.3 (最大4.0) | V  |

| アナログ電源電圧               |                           | AVCC0, AVCC1 (注2) | −0.3 ~ +4.0                | ٧  |

| アナログ入力電圧               |                           | V <sub>AN</sub>   | -0.3 ~ AVCC + 0.3 (最大4.0)  | V  |

| ジャンクション温度 Dバージョン       |                           | T <sub>j</sub>    | −40 <b>~</b> +105          | °C |

| 保存温度                   |                           | T <sub>stg</sub>  | −55 <b>~</b> +125          | °C |

# No.9 57.2 DC 特性(Page 2410 of 2491)

電気的特性章の「57.2 DC 特性」において、「表 57.5 DC 特性 (3)」のディープソフトウェアスタンバイモードでの特性値を以下のとおり訂正いたします。

# 【変更前】

|           | 項目                                                                                          |                                    |                                          |      |   | typ  | max | 単位 | 測定条件 |

|-----------|---------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------|------|---|------|-----|----|------|

| 消費電流 (注1) |                                                                                             | <u>.</u> 1                         | <b>省略</b>                                | Icc  |   | _    | 省略  | 3  |      |

|           |                                                                                             | スタンバイRA<br>(USB0のみ)電               | M, USBレジューム検出部<br>原供給あり                  | (注3) | _ | 15.5 | 51  | μА |      |

|           | \<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\ | スタンバイ<br>RAM, USB                  | パワーオンリセット回路<br>低消費電力機能無効 <sup>(注5)</sup> |      | _ | 11.5 | 29  |    |      |

|           | ボイー<br>ンロトウン<br>スタンズイ=                                                                      | レジューム<br>検出部<br>(USB0のみ)<br>電源供給なし | パワーオンリセット回路<br>低消費電力機能有効 <sup>(注6)</sup> |      | _ | 4.9  | 20  |    |      |

|           | ,                                                                                           | RTC動作時<br>の増分                      | 低CL水晶 <mark>発振</mark> 子使用時               |      | _ | 1    | _   |    |      |

|           |                                                                                             |                                    | 標準CL水晶 <mark>発振</mark> 子使用時              |      | _ | 2    | _   |    |      |

|           |                                                                                             |                                    | <b>省略</b>                                |      |   | •    | 省略  | 3  |      |

# 【変更後】

|      | 項目                      |                                    |                                                         |                 |    | typ  | max | 単位 | 測定条件 |

|------|-------------------------|------------------------------------|---------------------------------------------------------|-----------------|----|------|-----|----|------|

| 消費電流 |                         | =                                  | 省略                                                      | I <sub>cc</sub> | 省略 |      |     |    |      |

| (注1) |                         | スタンバイRA<br>(USB0のみ)電               | M、USBレジューム検出部<br>源供給あり                                  | (注3)            | _  | 15.5 | 61  | μΑ |      |

|      | ν μ μ<br>Γ   γ<br>Γ   Σ | スタンバイ<br>RAM、USB                   | パワーオンリセット回路 <mark>の</mark><br>低消費電力機能無効 <sup>(注5)</sup> |                 | _  | 11.5 | 38  |    |      |

|      | ゲイーン<br>ソロトウ<br>スタンズイ=  | レジューム<br>検出部<br>(USB0のみ)<br>電源供給なし | パワーオンリセット回路の<br>低消費電力機能有効 <sup>(注6)</sup>               |                 | _  | 4.9  | 29  |    |      |

|      |                         | RTC動作時                             | 低CL水晶振動子使用時                                             |                 | _  | 1    | _   |    |      |

|      |                         | の増分                                | 標準CL水晶 <mark>振動</mark> 子使用時                             |                 | _  | 2    | _   |    |      |

|      | 省略                      |                                    |                                                         |                 |    | •    | 省略  | 3  |      |

# No.10 57.2 DC 特性(Page 2411 of 2491)

電気的特性章の「57.2 DC 特性」において、「表 57.6 DC 特性 (4)」のリファレンス電源電流-12 ビット A/D 変換中(ユニット 0)の特性値を以下のとおり訂正いたします。

# 【変更前】

|        | 項目                        | 記号                 | min | typ  | max | 単位 | 測定条件    |  |  |

|--------|---------------------------|--------------------|-----|------|-----|----|---------|--|--|

|        | 省略                        |                    |     |      |     |    |         |  |  |

| リファレンス | 12 ビット A/D 変換中(ユニット 0)    | Al <sub>REFH</sub> | _   | 25   | 40  | μΑ | IVREFH0 |  |  |

| 電源電流   | 12 ビット A/D 変換待機時(ユニット 0)  |                    | _   | 0.07 | 0.4 | μΑ | IVREFH0 |  |  |

|        | 12 ビット A/D スタンバイ時(ユニット 0) |                    | _   | 0.07 | 0.2 | μΑ | IVREFH0 |  |  |

| 省略     |                           |                    |     |      |     |    |         |  |  |

# 【変更後】

|      | 記号                            | min                | typ | max  | 単位  | 測定条件 |         |  |  |

|------|-------------------------------|--------------------|-----|------|-----|------|---------|--|--|

|      | 省略                            |                    |     |      |     |      |         |  |  |

|      | 12 ビット A/D 変換中(ユニット 0)        | Al <sub>REFH</sub> | _   | 38   | 60  | μΑ   | IVREFH0 |  |  |

| 電源電流 | 12 ビット A/D 変換待機時(ユニット 0)      |                    | _   | 0.07 | 0.4 | μA   | IVREFH0 |  |  |

|      | 12 ビット A/D モジュールストップ時(ユニット 0) |                    | _   | 0.07 | 0.2 | μΑ   | IVREFH0 |  |  |

|      | 省略                            |                    |     |      |     |      |         |  |  |

# No.11 57.2 DC 特性

電気的特性章の「57.2 DC 特性」に以下の電気的特性を追加いたします。

# 【変更後】

表57.x 熱抵抗値(参考値)

| 項目  | パッケージ                     | 記号            | max  | 単位   | 測定条件                      |

|-----|---------------------------|---------------|------|------|---------------------------|

| 熱抵抗 | 144ピンLFQFP (PLQP0144KA-B) | $\theta_{ja}$ | 50.9 | °C/W | JESD51-2および<br>JESD51-7準拠 |

|     | 100ピンLFQFP (PLQP0100KB-B) |               | 52.5 |      |                           |

|     | 145ピンTFLGA (PTLG0145KA-A) |               | 34.6 |      | JESD51-2および<br>JESD51-9準拠 |

|     | 100ピンTFLGA (PTLG0100JA-A) |               | 34.1 |      |                           |

|     | 144ピンLFQFP (PLQP0144KA-B) | $\Psi_{jt}$   | 1.5  | °C/W | JESD51-2および<br>JESD51-7準拠 |

|     | 100ピンLFQFP (PLQP0100KB-B) |               | 1.5  |      |                           |

|     | 145ピンTFLGA (PTLG0145KA-A) |               | 0.4  |      | JESD51-2および<br>JESD51-9準拠 |

|     | 100ピンTFLGA (PTLG0100JA-A) |               | 0.4  |      |                           |

注. 数値は 4 層の実装ボードを想定した参考値です。熱抵抗は実装ボードの層数やサイズなどの環境に依存しますので、環境の詳細については、JEDEC 規格を参照してください。

以上