# **BROADEST CLOCK BUFFER, DIVIDER AND MULTIPLEXER PORTFOLIO**

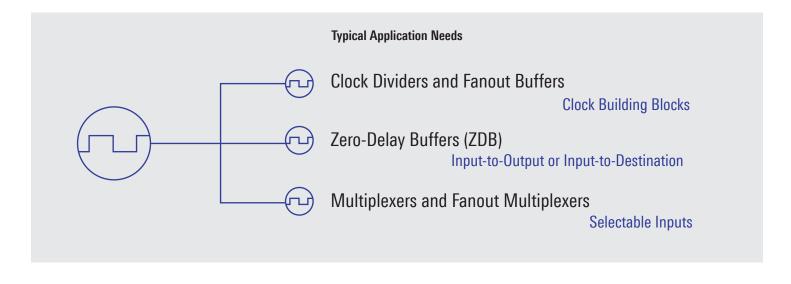

Renesas clock distribution products are used to condition, manipulate and distribute clock signals within a system, with or without the use of a phase-locked loop (PLL). These devices are well-suited for most applications where the input signal is of good quality, and the goal is to buffer, fan-out, divide, or multiplex the input signal. A single-output clock buffer is also useful for translating a clock from one signaling standard to another, such as LVCMOS-in to LVPECL-out.

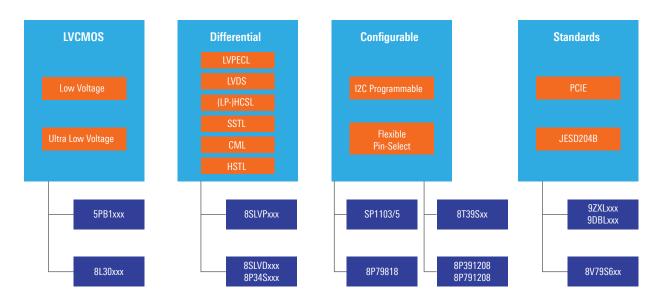

As the industry leader in timing solutions, Renesas offers a rich portfolio of clock buffer, clock distribution and multiplexer solutions to meet the needs of virtually any application. Renesas has the largest portfolio of clock distribution devices that support differential signals. LVDS, LVPECL, HCSL, LVCMOS, CML, HSTL, SSTL are some of the most common I/O levels supported by these devices.

### Product categories

- Fanout Buffers

- Zero-Delay Buffers

- Multiplexers

#### Benefits

- Low additive jitter/skew that lower system noise floor

- Programmable output clock type for design flexibility

- Wide operation voltage for design compatibility

- High integration reduces BOM cost, saves board space

- Re-use in different design base on built-in multiple OTP configuration

#### Features

- High-performance 2-20 output clock buffers

- Individually selectable output voltage 1.8V-2.5V-3.3V

- PCI Express buffers with Gen5 performance

- Programmable crystal load capacitance achieve high accuracy

## **BROADEST CLOCK BUFFER, DIVIDER AND MULTIPLEXER PORFOLIO**

**Buffer Summary by Functionality**

#### **Buffer Family Selection Guide**

|                 | 5PB                 | 9DB/9ZXL         | 8SLVP                                     | 8SLVD | 8P34S       | 8T39S                      | 8V79S6       |

|-----------------|---------------------|------------------|-------------------------------------------|-------|-------------|----------------------------|--------------|

| Characteristics | Low Additive Jitter | PCIe Gen5        | Simple and Low Noise                      |       | Low Power   | Flexible                   | JESD204B     |

| I/0             | LVCMOS              | LPHCSL           | LVPECL                                    | LVDS  | LVDS        | Universal                  | LVDS, LVPECL |

| Features        | 1~10 outputs,       | 2~20 outputs, OE | Single, dual functions and matched pinout |       |             | S/E, OE, 2 banks, XTAL I/F | Dual, Delay  |

| fmax            | 200 MHz             | 100 MHz, 125 MHz | 2 GHz                                     | 2 GHz | 1.3-2.0 GHz | 2 GHz                      | 3 GHz        |

| Supply          | 1.8V - 3.3V         | 1.8V - 3.3V      | 2.5V - 3.3V                               | 2.5V  | 1.8V        | 2.5V, 3.3V, Mixed          | 3.3V         |

To request samples, download documentation or learn more visit: renesas.com/buffers

Renesas Electronics America Inc. | renesas.com 1001 Murphy Ranch Road, Milpitas, CA 95035 | Phone: 1-888-468-3774

© 2020 Renesas Electronics America Inc. (REA). All rights reserved. All trademarks are the property of their respective owners. REA believes the information herein was accurate when given but assumes no risk as to its quality or use. All information is provided as-is without warranties of any kind, whether express, implied, statutory, or arising from course of dealing, usage, or trade practice, including without limitation as to merchantability, fitness for a particular purpose, or non-infringement. REA shall not be liable for any direct, indicet, special, or other information herein, all contents are protected by U.S. and international copyright laws. Except as specifically permitted herein, no portion of this material may be reproduced in any form, or by any means, without primission from Renesas Electronics America laury. Visions or users are not permitted to modify, distribute, publish, transmit or create derivative works of any of this material for any public or commercial purposes.

Document No.: R31DS0002EU0000