# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

## ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# R32C/100シリーズ

ソフトウェアマニュアル ルネサスマイクロコンピュータ M16Cファミリ/R32C/100シリーズ

本資料に記載の全ての情報は本資料発行時点のものであり、ルネサスエレクトロニクスは、 予告なしに、本資料に記載した製品または仕様を変更することがあります。 ルネサスエレクトロニクスのホームページなどにより公開される最新情報をご確認ください。

#### 本資料ご利用に際しての留意事項

- 1. 本資料は、お客様に用途に応じた適切な弊社製品をご購入いただくための参考資料であり、本資料中に記載の技術情報について弊社または第三者の知的財産権その他の権利の実施、使用を許諾または保証するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例など全ての情報 の使用に起因する損害、第三者の知的財産権その他の権利に対する侵害に関し、弊社は責任を負い ません。

- 3. 本資料に記載の製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他 軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替および外国貿易法」 その他輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。

- 4. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例などの全ての情報は本資料発行時点のものであり、弊社は本資料に記載した製品または仕様等を予告なしに変更することがあります。弊社の半導体製品のご購入およびご使用に当たりましては、事前に弊社営業窓口で最新の情報をご確認いただきますとともに、弊社ホームページ(http://www.renesas.com)などを通じて公開される情報に常にご注意ください。

- 5. 本資料に記載した情報は、正確を期すため慎重に制作したものですが、万一本資料の記述の誤りに 起因する損害がお客様に生じた場合においても、弊社はその責任を負いません。

- 6. 本資料に記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他 応用回路例などの情報を流用する場合は、流用する情報を単独で評価するだけでなく、システム 全体で十分に評価し、お客様の責任において適用可否を判断してください。弊社は、適用可否に 対する責任は負いません。

- 7. 本資料に記載された製品は、各種安全装置や運輸・交通用、医療用、燃焼制御用、航空宇宙用、原子力、海底中継用の機器・システムなど、その故障や誤動作が直接人命を脅かしあるいは人体に危害を及ぼすおそれのあるような機器・システムや特に高度な品質・信頼性が要求される機器・システムでの使用を意図して設計、製造されたものではありません(弊社が自動車用と指定する製品を自動車に使用する場合を除きます)。これらの用途に利用されることをご検討の際には、必ず事前に弊社営業窓口へご照会ください。なお、上記用途に使用されたことにより発生した損害等について弊社はその責任を負いかねますのでご了承願います。

- 8. 第7項にかかわらず、本資料に記載された製品は、下記の用途には使用しないでください。これらの用途に使用されたことにより発生した損害等につきましては、弊社は一切の責任を負いません。

- 1)生命維持装置。

- 2)人体に埋め込み使用するもの。

- 3)治療行為(患部切り出し、薬剤投与等)を行うもの。

- 4)その他、直接人命に影響を与えるもの。

- 9. 本資料に記載された製品のご使用につき、特に最大定格、動作電源電圧範囲、放熱特性、実装条件 およびその他諸条件につきましては、弊社保証範囲内でご使用ください。弊社保証値を越えて製品 をご使用された場合の故障および事故につきましては、弊社はその責任を負いません。

- 10. 弊社は製品の品質および信頼性の向上に努めておりますが、特に半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。弊社製品の故障または誤動作が生じた場合も人身事故、火災事故、社会的損害などを生じさせないよう、お客様の責任において冗長設計、延焼対策設計、誤動作防止設計などの安全設計(含むハードウェアおよびソフトウェア)およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特にマイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 1 1 . 本資料に記載の製品は、これを搭載した製品から剥がれた場合、幼児が口に入れて誤飲する等の 事故の危険性があります。お客様の製品への実装後に容易に本製品が剥がれることがなきよう、 お客様の責任において十分な安全設計をお願いします。お客様の製品から剥がれた場合の事故に つきましては、弊社はその責任を負いません。

- 12.本資料の全部または一部を弊社の文書による事前の承諾なしに転載または複製することを固くお断りいたします。

- 13.本資料に関する詳細についてのお問い合わせ、その他お気付きの点等がございましたら弊社営業窓口までご照会ください。

# 本書の表記について

本書では、マイクロコンピュータの動作を詳細に説明するために、一定のルールに基づいて記載しています。

本書では、以下のような表記を用いています。

| 分類       | 記述                | 内容                                |  |

|----------|-------------------|-----------------------------------|--|

| 記号       | IMM               | 即値(Immediate)を表します。               |  |

|          | IMMEX             | 演算時に符号拡張(Extension)される即値を表します。    |  |

|          | abs               | 絶対アドレッシングの絶対(Absolute)値を表します。     |  |

|          | dsp               | 相対アドレッシングの変位(Displacement)を表します。  |  |

|          | []                | 間接アドレッシングを表します。                   |  |

|          | label             | プログラムカウンタ相対で使用されるラベル(Label)を表し    |  |

|          |                   | ます。                               |  |

|          | bit               | ビット番号を表します。                       |  |

|          | R0LB、R0B、         | 下線部のように "B" を付加したレジスタシンボルは、バンク    |  |

|          | R2R0 <u>B</u> など  | 1レジスタを表します。                       |  |

| 数值       | 000 <u>b</u>      | 最後に "b" を付加した数値は2進数を表します。         |  |

|          | 0000 <u>h</u>     | 最後に "h" を付加した数値は16進数を表します。        |  |

|          | 100               | 数字のみの場合は10進数(BCD)を表します。           |  |

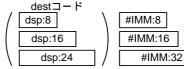

| ビット長指定   | #IMM <u>:8</u> など | 下線部はオペランド記号の有効ビット数を表します。          |  |

|          | :3                | 有効ビット長が3ビットであることを表します。            |  |

|          | :4                | 有効ビット長が4ビットであることを表します。            |  |

|          | :8                | 有効ビット長が8ビットであることを表します。            |  |

|          | :16               | 有効ビット長が16ビットであることを表します。           |  |

|          | :24               | 有効ビット長が24ビットであることを表します。           |  |

|          | :32               | 有効ビット長が32ビットであることを表します。           |  |

| 命令フォーマット | MOV <u>:S</u> など  | 下線部は命令フォーマットを指定する記号です。            |  |

|          | :G                | ジェネリック形式を表します。                    |  |

|          | :Q                | クイック形式を表します。                      |  |

|          | :S                | ショート形式を表します。                      |  |

|          | :Z                | ゼロ形式を表します。                        |  |

| 演算サイズ    | MOV <u>.W</u> など  | 下線部は命令の演算サイズを指定する記号です。            |  |

|          | .В                | バイト(8bit)演算を指定します。                |  |

|          | .W                | ワード(16bit)演算を指定します。               |  |

|          | .L                | ロングワード(32bit)演算を指定します。            |  |

|          | .BW               | バイトからワードへの変換を指定します。               |  |

|          | .BL               | バイトからロングワードへの変換を指定します。            |  |

|          | .WL               | ワードからロングワードへの変換を指定します。            |  |

| 分岐距離指定   | JMP <u>.A</u> など  | 下線部は分岐の相対距離の有効ビット数を指定する記号で<br> す。 |  |

|          | .S                | 3ビットのPC前方相対を表します。有効値は1~8です。       |  |

|          | .В                | 8ビットのPC相対を表します。有効値は-128~+127です。   |  |

|          | .W                | 16ビットのPC相対を表します。                  |  |

|          |                   | 有効値は-32768~+32767です。              |  |

|          | .А                | 24ビットのPC相対を表します。                  |  |

|          |                   | 有効値は-8388608~+8388607です。          |  |

| 分類        | 記述                | 内容                                  |

|-----------|-------------------|-------------------------------------|

| オペレーション   |                   | 原則としてC言語の文法規則に則っています。以下、本書で         |

|           |                   | 使用している記述について説明します。                  |

|           | =                 | 代入演算子です。右辺の値を左辺に代入します。              |

|           | -                 | 単項演算子の負号、または二項演算子の「差」を表します。         |

|           | +                 | 二項演算子の「和」を表します。                     |

|           | *                 | ポインタ演算子、または二項演算子の「積」を表します。          |

|           | /                 | 二項演算子の「商」を表します。                     |

|           | %                 | 二項演算子の「剰余」を表します。                    |

|           | ~                 | 単項ビット演算子の「NOT」を表します。                |

|           | &                 | 二項ビット演算子の「AND」を表します。                |

|           |                   | 二項ビット演算子の「OR」を表します。                 |

|           | ٨                 | 二項ビット演算子の「Exclusive OR」を表します。       |

|           | (float)           | キャスト演算子です。                          |

|           | ÷                 | 文の終了を表します。                          |

|           | {}                | 複文の開始と終了を表します。{}内には複数の文が記述でき        |

|           |                   | ます。                                 |

|           | if (式) 文1 else 文2 | if文を表します。式を評価して、真であれば文1を、偽であ        |

|           |                   | れば文2を実行します。                         |

|           | for (文1;式;文2) 文3  | for文を表します。文1を実行した後、式を評価して、真であ       |

|           |                   | れば文3を実行します。文3の実行後は、文2を実行した後、        |

|           |                   | 式を評価します。                            |

|           | do 文 while (式);   | do文を表します。式が真の間、文を実行します。式の真偽         |

|           |                   | にかかわらず、文は最低1回実行されます。                |

|           | while (式) 文       | while文を表します。式が真の間、文を実行します。          |

|           | ==、!=             | 比較演算子です。順に「等しい」、「等しくない」を表しま         |

|           |                   | す。                                  |

|           | >, <              | 比較演算子です。順に「大なり」「小なり」を表します。          |

|           | >=、<=             | 比較演算子です。'>'、'<' に '=='の条件が加わります。    |

|           | &&、               | 論理演算子です。左側の条件と、右側の条件のそれぞれ           |

|           |                   | 「AND」と「OR」を表します。                    |

|           | true              | C言語にはありません。 Cndで指定した条件が成立したとき       |

|           |                   | に "1" になります。                        |

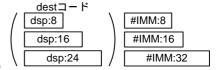

| 選択可能なsrc/ | #IMMEX            | #IMMEX:8または#IMMEX:16が指定できます。        |

| dest      | #IMM              | 演算サイズに応じて、#IMM:8、#IMM:16、または#IMM:32 |

|           |                   | が指定できます。                            |

|           |                   | #IMM:3や#IMM:4は含みません。                |

# 目次

| 1. | 概   | 要           |                                       |    |

|----|-----|-------------|---------------------------------------|----|

|    | 1.1 | R32         | :C/100シリーズの特長                         | 2  |

|    | 1.2 | アド          | ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 3  |

|    | 1.3 | レジ          | デスタ構成                                 | 4  |

|    |     | 1.3.1       | 基本レジスタ                                | 5  |

|    |     | 1.3.2       | 高速割り込みレジスタ                            | 6  |

|    |     | 1.3.3       | DMAC関連レジスタ                            | 6  |

|    |     | 1.3.4       | フラグレジスタ (FLG)                         | 7  |

|    |     | 1.3.5       | レジスタバンク                               | 10 |

|    |     | 1.3.6       | リセット解除後の内部レジスタ値                       | 11 |

|    | 1.4 | デー          | ・タタイプ                                 | 12 |

|    |     | 1.4.1       | 整数型                                   | 12 |

|    |     | 1.4.2       | 10進数型                                 | 12 |

|    |     | 1.4.3       | 固定小数点型                                | 13 |

|    |     | 1.4.4       | 浮動小数点型                                | 13 |

|    |     | 1.4.5       | ビット型                                  | 14 |

|    |     | 1.4.6       | ストリング型                                | 14 |

|    | 1.5 | デー          | - 夕配置                                 | 15 |

|    |     | 1.5.1       | レジスタ上のデータ配置                           | 15 |

|    |     | 1.5.2       | メモリ上のデータ配置                            | 15 |

|    | 1.6 | 命令          | >フォーマット                               | 16 |

|    |     | 1.6.1       | オペコード                                 | 17 |

|    |     | 1.6.2       | オペランド                                 |    |

|    | 1.7 | ベク          | 'タテーブル                                |    |

|    |     | 1.7.1       | 固定ベクタテーブル                             |    |

|    |     | 1.7.2       | 可変ベクタテーブル                             | 19 |

| 2. | ア   | ドレッ         | シングモード                                |    |

|    | 2.1 | アド          | ・<br>・<br>・レッシングモード                   | 22 |

|    | 2.2 | 本章          | で見方                                   | 23 |

|    | 2.3 | <b>一</b> 舟殳 | と命令アドレッシング                            | 24 |

|    | 2.4 | 間接          | ま命令アドレッシング                            | 27 |

|    | 2.5 | 拡張          | 命令アドレッシング                             | 30 |

|    | 2.6 | 特定          | 『命令アドレッシング                            | 32 |

|    | 2.7 | ビッ          | ト命令アドレッシング                            | 34 |

| 3. | 命   | 令           |                                       |    |

|    | 3.1 | 本章          | :の見方                                  | 38 |

|    | 32  | 命今          | · 詳細説明                                | 43 |

| 索引 | 3         |             |                               | 277 |

|----|-----------|-------------|-------------------------------|-----|

|    | 5.7       | 割り          | 込みの注意事項                       | 275 |

|    | 5.6       | 多重          | 割り込み                          | 273 |

|    | 5.5       | 割り          | 込み優先順位                        | 273 |

|    | 5.4       | 割り          | 込みルーチンからの復帰                   | 273 |

|    |           | 5.3.3       | レジスタ退避                        | 272 |

|    |           | 5.3.2       | プロセッサ割り込み優先レベル(IPL)の変化        | 272 |

|    |           | 5.3.1       | 割り込み応答時間                      | 271 |

|    | 5.3       | 割り          | 込みシーケンス                       | 270 |

|    |           | 5.2.4       | 割り込み制御レジスタの変更                 | 269 |

|    |           | 5.2.3       | 割り込み要求レベルとプロセッサ割り込み優先レベル(IPL) | 268 |

|    |           | 5.2.2       | 割り込み要求ビット                     |     |

|    |           | 5.2.1       | ョリ込み許可フラグ(Iフラグ)               |     |

|    | 5.2       |             | 込み制御                          |     |

|    |           | 5.1.3       | ハードウェア割り込み                    |     |

|    |           | 5.1.2       | ソフトウェア割り込み                    |     |

|    | 0.1       | 5.1.1       | 割り込みの分類                       |     |

| 5. | 古)<br>5.1 |             |                               | 264 |

| 5. |           | り込み         |                               |     |

|    | 4.3       | 命令          | ·コード/サイクル数                    |     |

|    |           | 4.2.3       | 条件の指定                         |     |

|    |           | 4.2.2       | オペランドの指定                      |     |

|    | 7.2       | 4.2.1       | 演算長の指定                        |     |

|    | 4.2       |             | レッシング                         |     |

| 4. | 哼<br>4.1  | •           | ド/サイクル数<br>:の見方               | 172 |

| 4  | <u>~</u>  |             |                               |     |

|    |           | 3.3.6       | アドレッシングモード                    |     |

|    |           | 3.3.5       | インデックス命令の次に実行できる命令            |     |

|    |           | 3.3.4       | BITINDEX.size src             |     |

|    |           | 3.3.3       | INDEX1.size src               |     |

|    |           | 3.3.2       | INDEX1.size src               |     |

|    | 3.3       | イン<br>3.3.1 | デックス命令INDEXB.size src         |     |

|    | $\sim$    | <b>/</b>    |                               | 400 |

# R32C/100シリーズ命令一覧

表 C.1 アルファベット別ページ早見表 (1/5)

| ニーモニック   | 内容             | 機能記載ページ | 命令コード/サイクル数<br>記載ページ |

|----------|----------------|---------|----------------------|

| ABS      | 絶対値            | 44      | 180                  |

| ADC      | キャリー付き加算       | 45      | 180                  |

| ADCF     | キャリーフラグの加算     | 46      | 181                  |

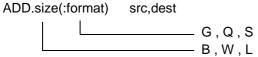

| ADD      | キャリーなし加算       | 47      | 182                  |

| ADDF     | 浮動小数点加算        | 49      | 184                  |

| ADSF     | サインフラグの加算      | 50      | 185                  |

| AND      | 論理積            | 51      | 186                  |

| BCLR     | ビットクリア         | 53      | 187                  |

| BITINDEX | ビットインデックス      | 54      | 188                  |

| BMCnd    | 条件ビット転送        | 55      | 188                  |

| BMC      | C フラグが "1" の場合 | 55      | 188                  |

| BMEQ     | 等しい場合          | 55      | 188                  |

| BMGE     | 等しいか符号付きで大きい場合 | 55      | 188                  |

| BMGEU    | 等しいか大きい場合      | 55      | 188                  |

| BMGT     | 符号付きで大きい場合     | 55      | 188                  |

| BMGTU    | 大きい            | 55      | 188                  |

| BMLE     | 等しいか符号付きで小さい場合 | 55      | 188                  |

| BMLEU    | 等しいか小さい場合      | 55      | 188                  |

| BMLT     | 符号付きで小さい場合     | 55      | 188                  |

| BMLTU    | 小さい場合          | 55      | 188                  |

| BMN      | 負の場合           | 55      | 188                  |

| BMNC     | Cフラグが "0" の場合  | 55      | 188                  |

| BMNE     | 等しくない場合        | 55      | 188                  |

| BMNO     | Oフラグが "0" の場合  | 55      | 188                  |

| BMNZ     | Zフラグが "0" の場合  | 55      | 188                  |

| вмо      | Oフラグが "1" の場合  | 55      | 188                  |

| BMPZ     | 正またはゼロの場合      | 55      | 188                  |

| BMZ      | Zフラグが "1" の場合  | 55      | 188                  |

| BNOT     | ビット反転          | 56      | 189                  |

| BRK      | デバッグ割り込み       | 57      | 189                  |

| BRK2     | デバッグ割り込み2      | 58      | 189                  |

| BSET     | ビットセット         | 59      | 190                  |

| BTST     | ビットテスト         | 60      | 190                  |

| BTSTC    | ビットテスト&クリア     | 61      | 191                  |

| BTSTS    | ビットテスト&セット     | 62      | 191                  |

| CLIP     | クリップ           | 63      | 192                  |

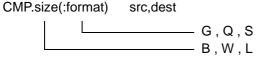

| CMP      | 比較             | 64      | 192                  |

| CMPF     | 浮動小数点比較        | 66      | 194                  |

表 C.1 アルファベット別ページ早見表 (続き) (2 / 5)

| ニーモニック            | 内容             | 機能記載ページ | 命令コード/サイクル数<br>記載ページ |

|-------------------|----------------|---------|----------------------|

| CNVIF             | 整数 浮動小数点数变换    | 67      | 195                  |

| DADC              | キャリー付き10進加算    | 68      | 196                  |

| DADD              | 10進加算          | 69      | 197                  |

| DEC               | デクリメント         | 70      | 198                  |

| DIV               | 符号付き除算         | 71      | 199                  |

| DIVF              | 浮動小数点除算        | 72      | 200                  |

| DIVU              | 符号なし除算         | 73      | 201                  |

| DIVX              | 符号付き除算         | 74      | 202                  |

| DSBB              | ボロー付き 10進減算    | 75      | 203                  |

| DSUB              | 10進減算          | 76      | 204                  |

| EDIV              | 符号付き除算         | 77      | 205                  |

| EDIVU             | 符号なし除算         | 78      | 206                  |

| EDIVX             | 符号付き除算         | 79      | 207                  |

| EMUL              | 符号付き乗算         | 80      | 208                  |

| EMULU             | 符号なし乗算         | 81      | 209                  |

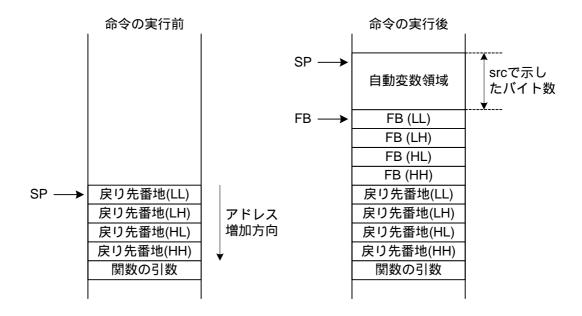

| ENTER             | スタックフレーム生成     | 82      | 209                  |

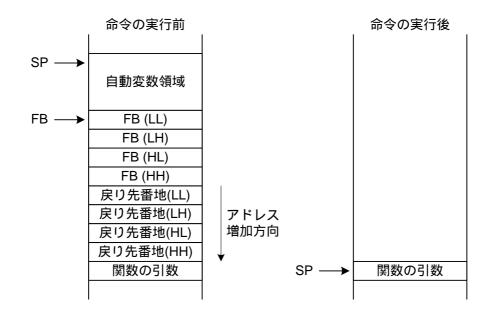

| EXITD             | スタックフレーム解放     | 83      | 210                  |

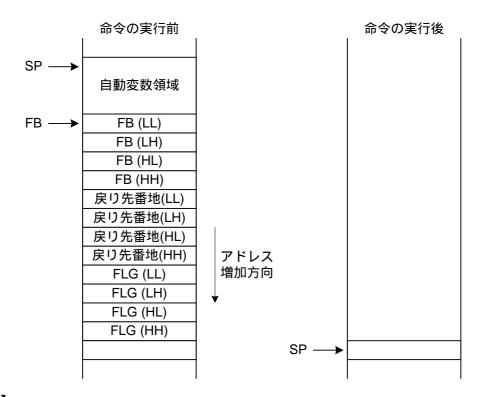

| EXITI             | 割り込みスタックフレーム解放 | 84      | 210                  |

| EXTS              | 符号拡張           | 85      | 210                  |

| EXTZ              | ゼロ拡張           | 86      | 212                  |

| FCLR              | フラグのクリア        | 88      | 214                  |

| FREIT             | 高速割り込みからの復帰    | 89      | 214                  |

| FSET              | フラグのセット        | 90      | 214                  |

| INC               | インクリメント        | 91      | 215                  |

| INDEX <i>Type</i> | インデックス         | 92      | 216                  |

| INDEXB            | 第1、第2オペランドに加算  | 92      | 216                  |

| INDEX1            | 第1オペランドに加算     | 92      | 215                  |

| INDEX2            | 第2オペランドに加算     | 92      | 216                  |

| INT               | INT命令割り込み      | 93      | 217                  |

| INTO              | オーバフロー割り込み     | 94      | 217                  |

| JCnd              | 条件分岐           | 95      | 217                  |

| JC                | フラグが "1" の場合   | 95      | 217                  |

| JEQ               | 等しい場合          | 95      | 217                  |

| JGE               | 等しいか符号付きで大きい場合 | 95      | 217                  |

| JGEU              | 等しいか大きい場合      | 95      | 217                  |

| JGT               | 符号付きで大きい場合     | 95      | 217                  |

| JGTU              | 大きい            | 95      | 217                  |

| JLE               | 等しいか符号付きで小さい場合 | 95      | 217                  |

| JLEU              | 等しいか小さい場合      | 95      | 217                  |

| JLT               | 符号付きで小さい場合     | 95      | 217                  |

表 C.1 アルファベット別ページ早見表 (続き) (3 / 5)

| ニーモニック         | 内容                                | 機能記載ページ | 命令コード/サイクル数<br>記載ページ |

|----------------|-----------------------------------|---------|----------------------|

| JLTU           |                                   | 95      | 217                  |

| JN             | り                                 | 95      | 217                  |

| JNC            |                                   | 95      | 217                  |

| JNE            | 等しくない場合                           | 95      | 217                  |

| JNO            | <del>すりくない場合 </del> Oフラグが "0" の場合 | 95      | 217                  |

| JNZ            |                                   | 95      | 217                  |

| JO             | Oフラグが "1" の場合                     | 95      | 217                  |

| JPZ            | <br>正またはゼロの場合                     | 95      | 217                  |

| JZ             | Zフラグが "1" の場合                     | 95      | 217                  |

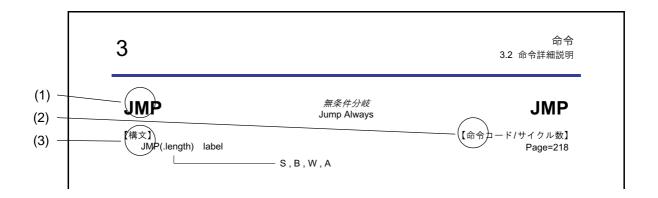

| JMP            | 無条件分岐                             | 96      | 218                  |

| JMPI           | 間接分岐                              | 97      | 219                  |

| JSR            | サブルーチン分岐                          | 98      | 220                  |

| JSRI           | ファルー・ファス                          | 99      | 220                  |

| LDC            | 専用レジスタへの転送                        | 100     | 221                  |

| LDCTX          | コンテキストの復帰                         | 101     | 222                  |

| LDIPL          | 割り込み優先レベル設定                       | 103     | 223                  |

| MAX            | 最大值選択                             | 104     | 223                  |

| MIN            | 最小值選択                             | 105     | 225                  |

| MOV            | 転送                                | 106     | 226                  |

| MOVA           | 実効アドレス転送                          | 108     | 231                  |

| MOV <i>Dir</i> | 4ビットデータ転送                         | 109     | 231                  |

| MOVHH          | src上位から dest 上位へ転送                | 109     | 231                  |

| MOVHL          | src上位からdest下位へ転送                  | 109     | 231                  |

| MOVLH          | src下位からdest上位へ転送                  | 109     | 231                  |

| MOVLL          | src下位から dest 下位へ転送                | 109     | 231                  |

| MUL            | 符号付き乗算                            | 110     | 232                  |

| MULF           | 浮動小数点乗算                           | 111     | 233                  |

| MULU           | 符号なし乗算                            | 112     | 234                  |

| MULX           | 丸め付き乗算                            | 113     | 236                  |

| NEG            | 符号反転                              | 115     | 236                  |

| NOP            | ノーオペレーション                         | 116     | 237                  |

| NOT            | 論理反転                              | 117     | 237                  |

| OR             | 論理和                               | 118     | 237                  |

| POP            | レジスタ/メモリの復帰                       | 119     | 238                  |

| POPC           | 専用レジスタの復帰                         | 120     | 239                  |

| POPM           | 複数レジスタの復帰                         | 121     | 239                  |

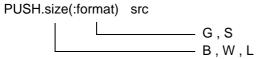

| PUSH           | レジスタ/メモリ/即値の退避                    | 122     | 239                  |

| PUSHA          | 実効アドレスの退避                         | 124     | 241                  |

| PUSHC          | 専用レジスタの退避                         | 125     | 242                  |

表 C.1 アルファベット別ページ早見表 (続き) (4 / 5)

| ニーモニック | 内容                      | 機能記載ページ | 命令コード/サイクル数<br>記載ページ |

|--------|-------------------------|---------|----------------------|

| PUSHM  | 複数レジスタの退避               | 126     | 242                  |

| REIT   | 割り込みからの復帰               | 127     | 242                  |

| RMPA   | 利り込みからの後帰  <br>  積和演算   | 128     | 243                  |

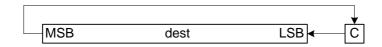

| ROLC   | 神仙原弁   キャリー付き左回転        | 129     | 243                  |

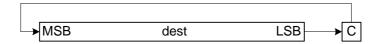

| RORC   | キャリー付き右回転               | 130     | 243                  |

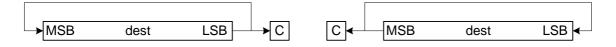

| ROT    |                         | 131     | 244                  |

| ROUND  | □型   □型                 | 132     | 245                  |

| RTS    | サブルーチンからの復帰             | 133     | 246                  |

| SBB    | ボロー付き減算                 | 134     | 246                  |

| SCCnd  | 条件設定                    | 135     | 247                  |

| SCC    | Cフラグが "1" の場合           | 135     | 247                  |

| SCEQ   | 等しい場合                   | 135     | 247                  |

| SCGE   | 等しいが符号付きで大きい場合          | 135     | 247                  |

| SCGEU  | 等しいか大きい場合               | 135     | 247                  |

| SCGT   | 符号付きで大きい場合              | 135     | 247                  |

| SCGTU  | 大きい                     | 135     | 247                  |

| SCLE   | 等しいか符号付きで小さい場合          | 135     | 247                  |

| SCLEU  | 等しいか小さい場合               | 135     | 247                  |

| SCLT   | 符号付きで小さい場合              | 135     | 247                  |

| SCLTU  | 小さい場合                   | 135     | 247                  |

| SCN    | 負の場合                    | 135     | 247                  |

| SCNC   | Cフラグが "0" の場合           | 135     | 247                  |

| SCNE   | 等しくない場合                 | 135     | 247                  |

| SCNO   | 〇フラグが "0" の場合           | 135     | 247                  |

| SCNZ   | フフラグが "0" の場合           | 135     | 247                  |

| SCO    | Oフラグが "1" の場合           | 135     | 247                  |

| SCPZ   | 正またはゼロの場合               | 135     | 247                  |

| SCZ    | Zフラグが "1" の場合           | 135     | 247                  |

| SCMPU  | ストリング比較                 | 136     | 248                  |

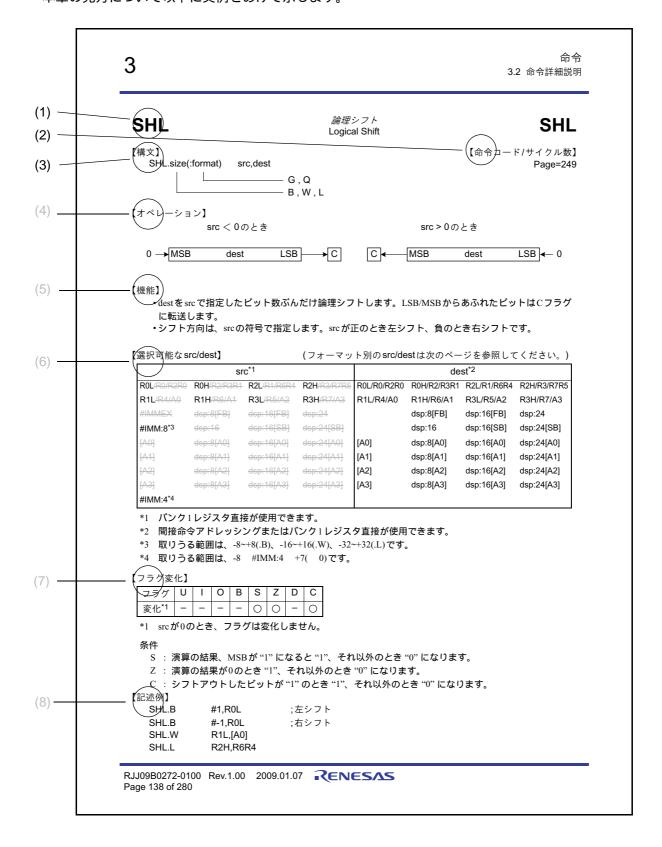

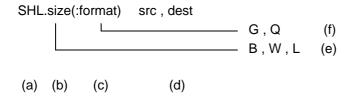

| SHA    | 算術シフト                   | 137     | 248                  |

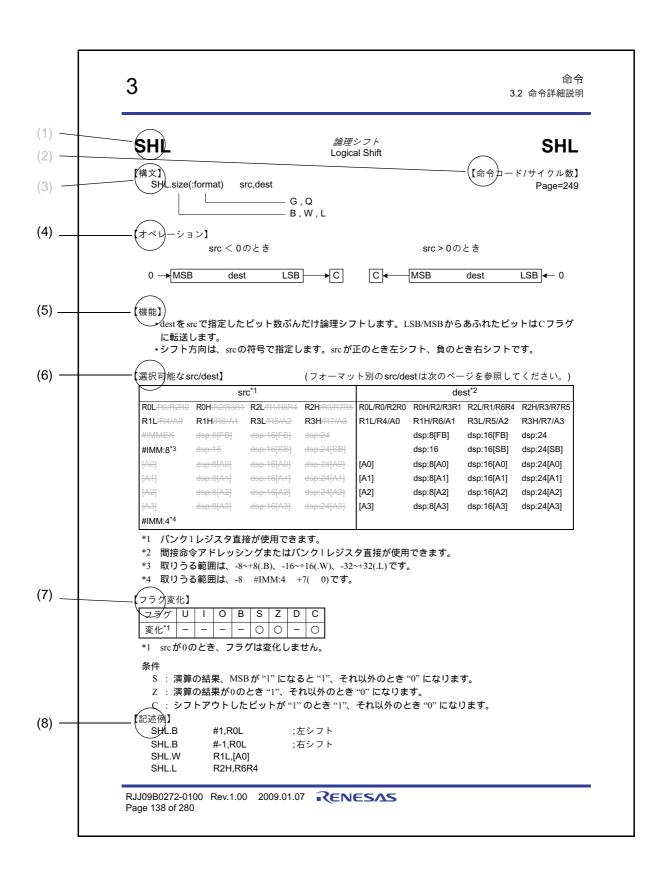

| SHL    | 論理シフト                   | 138     | 249                  |

| SIN    | ストリング入力                 | 140     | 251                  |

| SMOVB  | グーックッパパ<br>  逆方向ストリング転送 | 141     | 251                  |

| SMOVF  | 順方向ストリング転送              | 142     | 251                  |

| SMOVU  | ストリング転送                 | 143     | 252                  |

| SOUT   | ストリング出力                 | 144     | 252                  |

| SSTR   | ストリングストア                | 145     | 252                  |

| STC    | カーッン・ハーッ                | 146     | 253                  |

| STCTX  | コンテキストの退避               | 147     | 254                  |

| STNZ   | 条件付き転送                  | 149     | 254                  |

表 C.1 アルファベット別ページ早見表 (続き) (5 / 5)

| ニーモニック | 内容        | 機能記載 ページ | 命令コード/サイクル数<br>記載ページ |

|--------|-----------|----------|----------------------|

| STOP   | ストップ      | 150      | 254                  |

| STZ    | 条件付き転送    | 151      | 255                  |

| STZX   | 条件付き転送    | 152      | 255                  |

| SUB    | ボローなし減算   | 153      | 256                  |

| SUBF   | 浮動小数点減算   | 154      | 257                  |

| SUNTIL | ストリングサーチ  | 155      | 258                  |

| SWHILE | ストリングサーチ  | 156      | 258                  |

| TST    | テスト       | 157      | 258                  |

| UND    | 未定義命令割り込み | 158      | 259                  |

| WAIT   | ウェイト      | 159      | 259                  |

| XCHG   | 交換        | 160      | 260                  |

| XOR    | 排他的論理和    | 161      | 260                  |

表 C.2 機能別ページ早見表 (1/3)

| 機能     | ニーモニック   | 内容             | 機能記載ページ | 命令コード/サイクル数<br>記載ページ |

|--------|----------|----------------|---------|----------------------|

| <br>転送 | MOV      | 転送             | 106     | 226                  |

|        | MOVA     | 実効アドレス転送       | 108     | 231                  |

|        | MOVDir   | 4ビットデータ転送      | 109     | 231                  |

|        | POP      | レジスタ/メモリの復帰    | 119     | 238                  |

|        | POPM     | 複数レジスタの復帰      | 121     | 239                  |

|        | PUSH     | レジスタ/メモリ/即値の退避 | 122     | 239                  |

|        | PUSHA    | 実効アドレスの退避      | 124     | 241                  |

|        | PUSHM    | 複数レジスタの退避      | 126     | 242                  |

|        | STNZ     | 条件付き転送         | 149     | 254                  |

|        | STZ      | 条件付き転送         | 151     | 255                  |

|        | STZX     | 条件付き転送         | 152     | 255                  |

|        | XCHG     | 交換             | 160     | 260                  |

| ビット処理  | BCLR     | ビットクリア         | 53      | 187                  |

|        | BITINDEX | ビットインデックス      | 54      | 188                  |

|        | BMCnd    | 条件ビット転送        | 55      | 188                  |

|        | BNOT     | ビット反転          | 56      | 189                  |

|        | BSET     | ビットセット         | 59      | 190                  |

|        | BTST     | ビットテスト         | 60      | 190                  |

|        | BTSTC    | ビットテスト&クリア     | 61      | 191                  |

|        | BTSTS    | ビットテスト&セット     | 62      | 191                  |

| シフト    | ROLC     | キャリー付き左回転      | 129     | 243                  |

|        | RORC     | キャリー付き右回転      | 130     | 243                  |

|        | ROT      | 回転             | 131     | 244                  |

|        | SHA      | 算術シフト          | 137     | 248                  |

|        | SHL      | 論理シフト          | 138     | 249                  |

| 算術演算   | ABS      | 絶対値            | 44      | 180                  |

|        | ADC      | キャリー付き加算       | 45      | 180                  |

|        | ADCF     | キャリーフラグの加算     | 46      | 181                  |

|        | ADD      | キャリーなし加算       | 47      | 182                  |

|        | ADSF     | サインフラグの加算      | 50      | 185                  |

|        | CLIP     | クリップ           | 63      | 192                  |

|        | CMP      | 比較             | 64      | 192                  |

|        | DEC      | デクリメント         | 70      | 198                  |

|        | DIV      | 符号付き除算         | 71      | 199                  |

|        | DIVU     | 符号なし除算         | 73      | 201                  |

|        | DIVX     | 符号付き除算         | 74      | 202                  |

|        | EDIV     | 符号付き除算         | 77      | 205                  |

|        | EDIVU    | 符号なし除算         | 78      | 206                  |

|        | EDIVX    | 符号付き除算         | 79      | 207                  |

表 C.2 機能別ページ早見表 (続き) (2 / 3)

| 機能         | ニーモニック | 内容           | 機能記載ページ | 命令コード/サイクル数<br>記載ページ |

|------------|--------|--------------|---------|----------------------|

| <br>算術演算   | EMUL   | <br>  符号付き乗算 | 80      | 208                  |

| 3F113/3C3F | EMULU  | 符号なし乗算       | 81      | 209                  |

|            | EXTS   | 符号拡張         | 85      | 210                  |

|            | EXTZ   | ゼロ拡張         | 86      | 212                  |

|            | INC    | インクリメント      | 91      | 215                  |

|            | MAX    | 最大值選択        | 104     | 223                  |

|            | MIN    | 最小值選択        | 105     | 225                  |

|            | MUL    | 符号付き乗算       | 110     | 232                  |

|            | MULU   | 符号なし乗算       | 112     | 234                  |

|            | MULX   | 丸め付き乗算       | 113     | 236                  |

|            | NEG    | 符号反転         | 115     | 236                  |

|            | SBB    | ボロー付き減算      | 134     | 246                  |

|            | SUB    | ボローなし減算      | 153     | 256                  |

| 10進演算      | DADC   | キャリー付き10進加算  | 68      | 196                  |

|            | DADD   | 10進加算        | 69      | 197                  |

|            | DSBB   | ボロー付き10進減算   | 75      | 203                  |

|            | DSUB   | 10進減算        | 76      | 204                  |

| 浮動小数点      | ADDF   | 浮動小数点加算      | 49      | 184                  |

| 演算         | CMPF   | 浮動小数点比較      | 66      | 194                  |

|            | CNVIF  | 整数 浮動小数点数变换  | 67      | 195                  |

|            | DIVF   | 浮動小数点除算      | 72      | 200                  |

|            | MULF   | 浮動小数点乗算      | 111     | 233                  |

|            | ROUND  | 浮動小数点数 整数変換  | 132     | 245                  |

|            | SUBF   | 浮動小数点減算      | 154     | 257                  |

| 積和演算       | RMPA   | 積和演算         | 128     | 243                  |

| 論理演算       | AND    | 論理積          | 51      | 186                  |

|            | NOT    | 論理反転         | 117     | 237                  |

|            | OR     | 論理和          | 118     | 237                  |

|            | TST    | テスト          | 157     | 258                  |

|            | XOR    | 排他的論理和       | 161     | 260                  |

| 分岐         | JCnd   | 条件分岐         | 95      | 217                  |

|            | JMP    | 無条件分岐        | 96      | 218                  |

|            | JMPI   | 間接分岐         | 97      | 219                  |

|            | JSR    | サブルーチン分岐     | 98      | 220                  |

|            | JSRI   | 間接サブルーチン分岐   | 99      | 220                  |

|            | RTS    | サブルーチンからの復帰  | 133     | 246                  |

表 C.2 機能別ページ早見表 (続き) (3 / 3)

| 機能     | ニーモニック    | 内容             | 機能記載ページ | 命令コード/サイクル数<br>記載ページ |

|--------|-----------|----------------|---------|----------------------|

| ストリング  | SCMPU     | ストリング比較        | 136     | 248                  |

|        | SIN       | ストリング入力        | 140     | 251                  |

|        | SMOVB     | 逆方向ストリング転送     | 141     | 251                  |

|        | SMOVF     | 順方向ストリング転送     | 142     | 251                  |

|        | SMOVU     | ストリング転送        | 143     | 252                  |

|        | SOUT      | ストリング出力        | 144     | 252                  |

|        | SSTR      | ストリングストア       | 145     | 252                  |

|        | SUNTIL    | ストリングサーチ       | 155     | 258                  |

|        | SWHILE    | ストリングサーチ       | 156     | 258                  |

| 専用レジス  | FCLR      | フラグのクリア        | 88      | 214                  |

| 夕操作    | FSET      | フラグのセット        | 90      | 214                  |

|        | LDC       | 専用レジスタへの転送     | 100     | 221                  |

|        | POPC      | 専用レジスタの復帰      | 120     | 239                  |

|        | PUSHC     | 専用レジスタの退避      | 125     | 242                  |

|        | STC       | 専用レジスタから転送     | 146     | 253                  |

| 割り込み   | BRK       | デバッグ割り込み       | 57      | 189                  |

|        | BRK2      | デバッグ割り込み2      | 58      | 189                  |

|        | FREIT     | 高速割り込みからの復帰    | 89      | 214                  |

|        | INT       | INT命令割り込み      | 93      | 217                  |

|        | INTO      | オーバフロー割り込み     | 94      | 217                  |

|        | LDIPL     | 割り込み優先レベル設定    | 103     | 223                  |

|        | REIT      | 割り込みからの復帰      | 127     | 242                  |

|        | UND       | 未定義命令割り込み      | 158     | 259                  |

| 高級言語   | ENTER     | スタックフレーム生成     | 82      | 209                  |

| サポート   | EXITD     | スタックフレーム解放     | 83      | 210                  |

|        | EXITI     | 割り込みスタックフレーム解放 | 84      | 210                  |

| OSサポート | LDCTX     | コンテキストの復帰      | 101     | 222                  |

|        | STCTX     | コンテキストの退避      | 147     | 254                  |

| その他    | INDEXType | インデックス         | 92      | 216                  |

|        | NOP       | ノーオペレーション      | 116     | 237                  |

|        | SCCnd     | 条件設定           | 135     | 247                  |

|        | STOP      | ストップ           | 150     | 254                  |

|        | WAIT      | ウェイト           | 159     | 259                  |

# 1. 概要

- 1.1 R32C/100シリーズの特長

- 1.2 アドレス空間

- 1.3 レジスタ構成

- 1.4 データタイプ

- 1.5 データ配置

- 1.6 命令フォーマット

- 1.7 ベクタテーブル

#### R32C/100シリーズの特長 1.1

R32C/100シリーズは、組み込み機器を対象として開発されたシングルチップマイクロコンピュータです。 C言語に適した命令を持ち、使用頻度の高い命令を1バイトオペコードに配置していますので、アセンブ リ言語を使用しても、C言語を使用しても、より少ないメモリ容量で効率の良いプログラムを開発できま す。また、1クロックで実行する命令を多数持たせ、より高速な演算処理を実現しました。

豊富なアドレッシングモードに対応した108種類の命令セットを持ち、レジスタ-レジスタ、レジスタ-メ モリ、メモリ-メモリ間の演算やビットおよび4ビットデータを対象とする演算ができます。

また、乗算器、浮動小数点演算器を内蔵していますので、高速な演算ができます。

### (1) 特長

(a) レジスタ構成

データレジスタ 32ビット×4本(16ビットレジスタとしても使用可能。また、内2本は8ビッ

トレジスタとしても使用可能)

アドレスレジスタ 32ビット×4本 ベースレジスタ 32ビット×2本

(b) 特長ある命令セット

C言語に適した命令(スタックフレーム操作) : ENTER、EXITD、など

レジスタ、メモリを区別しない命令 : MOV、ADD、SUB、など 強力なビット処理命令 : BCLR、BTST、BSET、など 4ビット転送命令 : MOVLL、MOVHL、など

使用頻度の高い1バイト命令 : MOV、ADD、SUB、JMP、など

高速な1サイクル命令 : MOV、ADD、SUB、など

固定小数点乗算命令 : MULX

浮動小数点演算命令 : ADDF、SUBF、MULF、DIVF、など

(c) 4Gバイトのリニアなアドレス空間 分岐距離に応じた相対ジャンプ命令

(d) 高速な命令実行時間

最短1サイクル命令 : 108命令中36命令が1サイクル命令

### (2) 性能 (動作周波数 100MHz時)

| レジスタ間転送                | 10ns  |

|------------------------|-------|

| レジスタ–メモリ間転送            | 20ns  |

| レジスタ間加減算               | 10ns  |

| 8ビット×8ビットレジスタ間演算       | 20ns  |

| 16ビット×16ビットレジスタ間演算     | 20ns  |

| 32ビット×32ビットレジスタ間演算     | 20ns  |

| 16ビット ÷ 16ビットレジスタ間演算   | 150ns |

| 32 ビット ÷ 32 ビットレジスタ間演算 | 220ns |

|                        |       |

#### アドレス空間 1.2

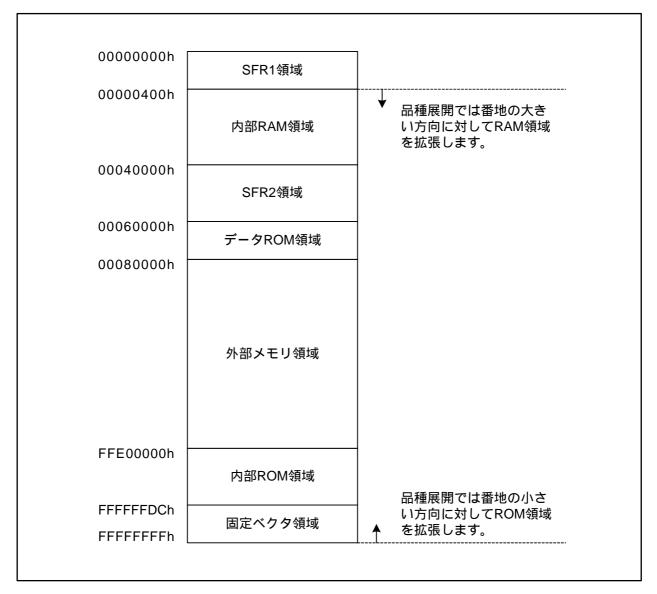

アドレス空間を図 1.1 に示します。

00000000h 番地~000003FFh 番地と00040000h 番地~0004FFFFh 番地は、SFR(スペシャルファンクションレ ジスタ)領域です。

00000400h番地~0003FFFFh番地、00060000h番地~0007FFFFh番地、およびFFE00000h番地~FFFFFFFh番 地はメモリ領域です。品種展開では00000400h番地から番地の大きい方向に対してRAM領域を、FFFFFFFh 番地から番地の小さい方向にROM領域を拡張します。ただし、FFFFFFDCh番地~FFFFFFFh番地は固定べ クタ領域です。

アドレス空間 図 1.1

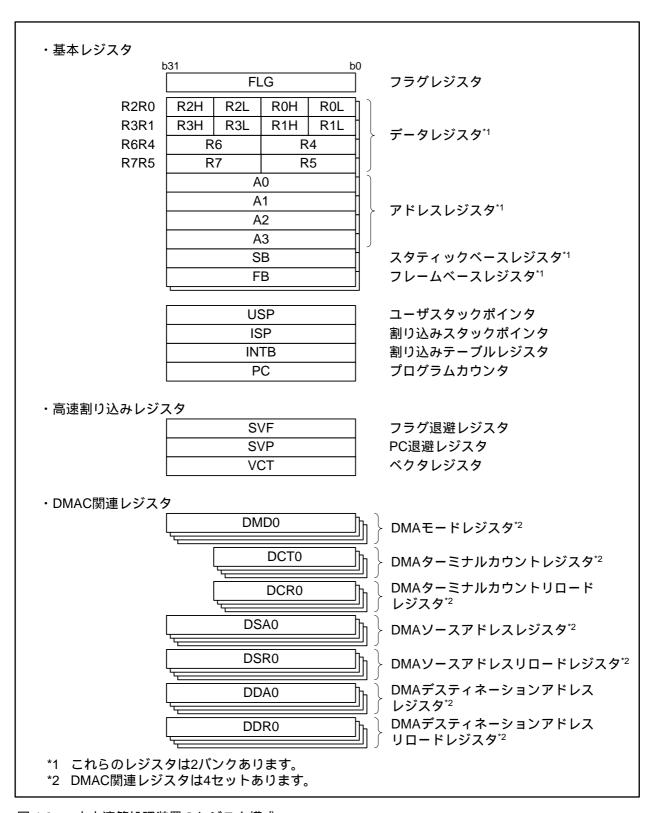

## 1.3 レジスタ構成

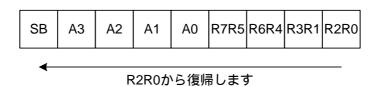

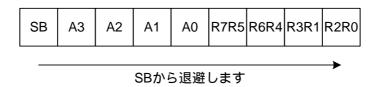

中央演算処理装置には図 1.2 に示すレジスタがあります。これらのうち、R2R0、R3R1、R6R4、R7R5、A0、A1、A2、A3、SB、FBの10個のレジスタは2バンクあります。レジスタバンクの切り替えはレジスタバンク指定フラグ(フラグレジスタのBフラグ)で行います。

図 1.2 中央演算処理装置のレジスタ構成

#### 1.3.1 基本レジスタ

基本レジスタには以下の9種類があります。

(1) データレジスタ(R2R0/R3R1/R6R4/R7R5/R0/R0H/R0L/R1/R1H/R1L/R2/R2H/R2L/R3/R3H/R3L/R4/ R5/R6/R7)

データレジスタ(R2R0/R3R1/R6R4/R7R5)は32ビットで構成されており、主に転送や算術、論理演算に使用します。

R2R0/R3R1/R6R4/R7R5は、上位(R2/R3/R6/R7)と下位(R0/R1/R4/R5)を別々に16ビットのデータレジスタとして使用できます。

また、R2R0/R3R1は、上位(R2H/R3H)、中上位(R2L/R3L)、中下位(R0H/R1H)、下位(R0L/R1L)を別々に8ビットのデータレジスタとしても使用できます。

## (2) アドレスレジスタ(A0/A1/A2/A3)

アドレスレジスタ(A0/A1/A2/A3)は32ビットで構成されており、データレジスタと同等の機能をもちます。また、アドレスレジスタ間接アドレッシングおよびアドレスレジスタ相対アドレッシングに使用します。

(3) スタティックベースレジスタ(SB)

スタティックベースレジスタ(SB)は32ビットで構成されており、SB相対アドレッシングに使用します。

(4) フレームベースレジスタ(FB)

フレームベースレジスタ(FB)は32ビットで構成されており、FB相対アドレッシングに使用します。

(5) プログラムカウンタ(PC)

プログラムカウンタ(PC)は32ビットで構成されており、次に実行する命令の番地を示します。

(6) 割り込みテーブルレジスタ(INTB)

割り込みテーブルレジスタ(INTB)は32ビットで構成されており、割り込みベクタテーブルの先頭番地を示します。

(7) ユーザスタックポインタ(USP) / 割り込みスタックポインタ(ISP)

スタックポインタは、ユーザスタックポインタ(USP)と割り込みスタックポインタ(ISP)の2種類があり、共に32ビットで構成されています。

使用するスタックポインタ(USP/ISP)は、スタックポインタ指定フラグ(Uフラグ)によって切り替えられます。

スタックポインタ指定フラグ(Uフラグ)は、フラグレジスタ(FLG)のビット7です。

USP, ISPには4の倍数を設定してください。4の倍数を設定したほうが実行効率がよくなります。

(8) フラグレジスタ(FLG)

フラグレジスタ(FLG)は16ビットの予約ビットを含む32ビットのレジスタで構成されており、1ビット単位でフラグとして使用します。各フラグの機能は、「1.3.4 フラグレジスタ (FLG)」を参照してください。

#### 高速割り込みレジスタ 1.3.2

高速割り込みレジスタは割り込み応答を高速化するために設けられたレジスタで、以下の3個のレジス タがあります。割り込みシーケンスでのレジスタ退避に、スタック領域の代わりにこれらのレジスタを 使用することで割り込み応答の高速化を図っています。

#### (1) フラグ退避レジスタ(SVF)

フラグ退避レジスタ (SVF) は 16 ビットで構成されており、高速割り込み発生時にフラグレジスタ (FLG)を退避させるために使用します。

## (2) PC退避レジスタ(SVP)

PC退避レジスタ(SVP)は32ビットで構成されており、高速割り込み発生時プログラムカウンタを退 避させるために使用します。

## (3) ベクタレジスタ(VCT)

ベクタレジスタ(VCT)は32ビットで構成されており、高速割り込み発生時の分岐先番地を示します。

#### 1.3.3 DMAC関連レジスタ

DMAC関連のレジスタには以下の7種類あります。

(1) DMAモードレジスタ(DMD0/DMD1/DMD2/DMD3)

DMA モードレジスタ (DMD0/DMD1/DMD2/DMD3) は32 ビットで構成されており、DMA の転送モー ドなどを設定するレジスタです。

(2) DMA ターミナルカウントレジスタ(DCT0/DCT1/DCT2/DCT3)

DMA ターミナルカウントレジスタ(DCT0/DCT1/DCT2/DCT3)は24ビットで構成されており、DMAの 転送回数をカウントするレジスタです。

(3) DMA ターミナルカウントリロードレジスタ (DCR0/DCR1/DCR2/DCR3)

DMA ターミナルカウントリロードレジスタ (DCR0/DCR1/DCR2/DCR3) は 24 ビットで構成されてお り、DMA ターミナルカウントレジスタの初期値を設定するレジスタです。

(4) DMAソースアドレスレジスタ(DSA0/DSA1/DSA2/DSA3)

DMAソースアドレスレジスタ(DSA0/DSA1/DSA2/DSA3)は32ビットで構成されており、DMAの転送 元のアドレスを保持するレジスタです。

(5) DMAソースアドレスリロードレジスタ(DSR0/DSR1/DSR2/DSR3)

DMA ソースアドレスリロードレジスタ (DSR0/DSR1/DSR2/DSR3) は 32 ビットで構成されており、 DMAソースアドレスレジスタの初期値を設定するレジスタです。

- (6) DMA デスティネーションアドレスレジスタ(DDA0/DDA1/DDA2/DDA3) DMA デスティネーションアドレスレジスタ (DDA0/DDA1/DDA2/DDA3) は 32 ビットで構成されてお り、DMAの転送先のアドレスを保持するレジスタです。

- (7) DMAデスティネーションアドレスリロードレジスタ(DDR0/DDR1/DDR2/DDR3) DMAデスティネーションアドレスリロードレジスタ(DDR0/DDR1/DDR2/DDR3)は32ビットで構成さ れており、DMAデスティネーションアドレスレジスタの初期値を設定するレジスタです。

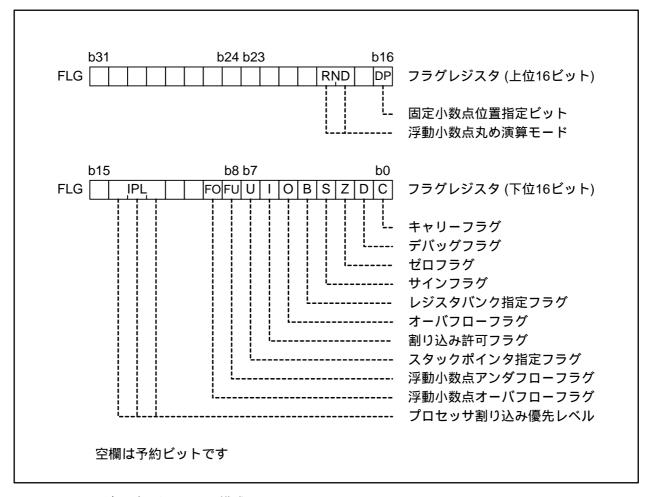

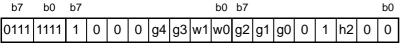

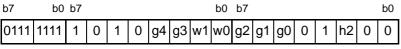

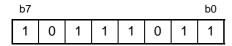

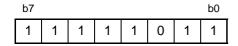

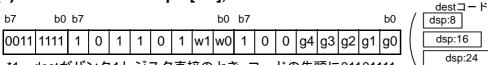

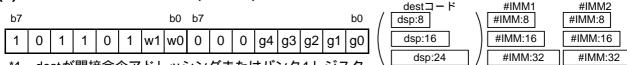

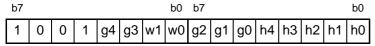

## 1.3.4 フラグレジスタ (FLG)

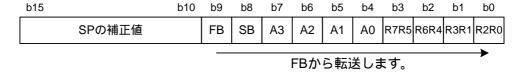

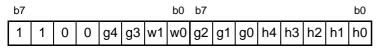

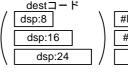

フラグレジスタ(FLG)の構成を図 1.3に示します。

図 1.3 フラグレジスタ(FLG)の構成

各フラグの機能を以下に示します。

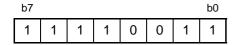

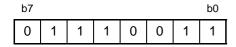

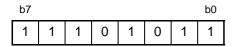

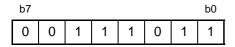

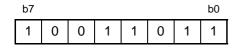

(1) ビット0: キャリーフラグ (Cフラグ) 算術論理ユニットで発生したキャリー、ボロー、シフトアウトしたビット等を保持します。 (2) ビット1: デバッグフラグ (Dフラグ)

シングルステップ割り込みを許可するフラグです。

このフラグを"1"にすると、命令実行後シングルステップ割り込みが発生します。割り込みを受け 付けると、このフラグは"0"になります。

(3) ビット2:ゼロフラグ(Zフラグ)

演算の結果が0のとき "1" になり、それ以外のとき "0" になります。

(4) ビット3: サインフラグ (Sフラグ)

演算の結果が負のとき"1"になり、それ以外のとき"0"になります。

(5) ビット4: レジスタバンク指定フラグ (Bフラグ)

レジスタバンクの選択を行います。このフラグが "0" のときレジスタバンク 0 が指定され、"1" のと きレジスタバンク1が指定されます。

(6) ビット5: オーバフローフラグ (Oフラグ)

演算の結果がオーバフローしたとき "1" になり、それ以外のとき "0" になります。

(7) ビット6:割り込み許可フラグ(Iフラグ)

マスカブル割り込みを許可するフラグです。

このフラグが"0"のとき割り込みは禁止され、"1"のとき許可されます。

割り込みを受け付けると、このフラグは"0"になります。

(8) ビット7: スタックポインタ指定フラグ (Uフラグ)

このフラグが "0" のとき割り込みスタックポインタ(ISP)が指定され、"1" のときユーザスタックポイ ンタ(USP)が指定されます。

ハードウェア割り込みを受け付けたとき、またはソフトウェア割り込み番号0~127のINT命令を実行 したとき、このフラグは"0"になります。

(9) ビット8: 浮動小数点アンダフローフラグ(FUフラグ)

浮動小数点演算の結果が、最小の正規化数を下回った場合(アンダフロー)、"1"になり、それ以外の とき "0" になります。

また、オペランドのデータが正規化数でも0でもない(不正入力値)場合にも、"1"になります。

(10)ビット9: 浮動小数点オーバフローフラグ(FOフラグ)

浮動小数点演算の結果が、最大の正規化数を上回った場合(オーバフロー)、"1"になり、それ以外の とき "0" になります。

また、オペランドのデータが正規化数でも0でもない(不正入力値)場合にも、"1"になります。

#### (11) ビット10~ビット11: 予約領域

### (12)ビット12~ビット14: プロセッサ割り込み優先レベル (IPL)

プロセッサ割り込み優先レベル(IPL)は3ビットで構成されており、レベル0からレベル7までの8段 階のプロセッサ割り込み優先レベルを指定します。

要求があった割り込みの割り込み要求レベルが、プロセッサ割り込み優先レベル(IPL)より大きい場 合、その割り込みが許可されます。

プロセッサ割り込み優先レベル (IPL) をレベル 7 (111b) に設定した場合、すべての割り込みが禁止さ れます。

## (13)ビット15:予約領域

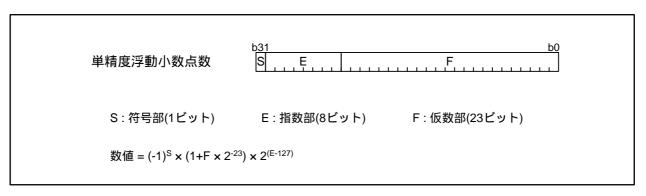

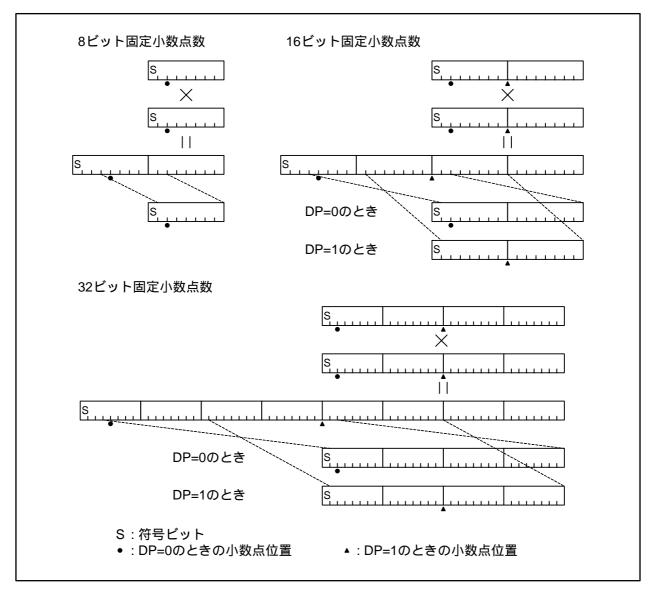

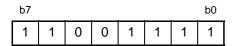

## (14)ビット16: 固定小数点位置指定ビット(DPビット)

固定小数点数の小数点位置を指定するビットです。また、固定小数点乗算の結果から、どの部分を 最終演算結果として抜き出すかを指定するビットでもあります。

MULX命令で使用します。

## (15)ビット17:予約領域

## (16)ビット18~ビット19: 浮動小数点丸め演算モード(RND)

浮動小数点丸め演算モード(RND)は2ビットで構成されており、浮動小数点演算の結果を丸める方式 を指定します。

| RND | 丸めモード | 説明                             |

|-----|-------|--------------------------------|

| 00b | 最近値   | 表現可能な最も近い値に丸めます。元の値が表現可能な2値    |

|     |       | の中間値の場合は、ビット0が "0" になるように丸めます。 |

| 01b | 予約    | 設定しないでください。                    |

| 10b | - 方向  | 演算結果が- に近づくように丸めます。            |

| 11b | ゼロ方向  | 演算結果が0に近づくように丸めます。             |

(17)ビット20~ビット31:予約領域

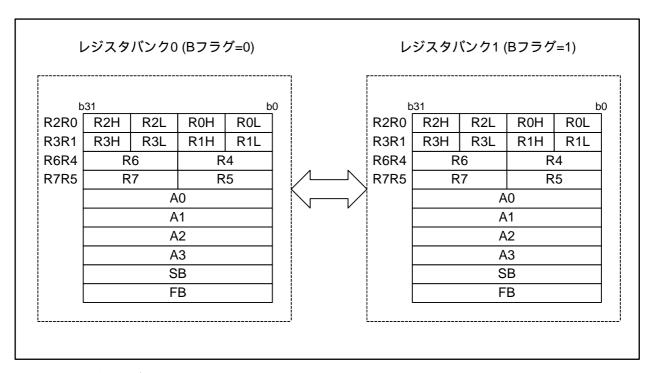

#### レジスタバンク 1.3.5

データレジスタ(R2R0/R3R1/R6R4/R7R5)、アドレスレジスタ(A0/A1/A2/A3)、フレームベースレジスタ (FB)、およびスタティックベースレジスタ(SB)で構成されたレジスタバンクが2セットあります。レジス タバンクは、フラグレジスタ(FLG)のレジスタバンク指定フラグ(Bフラグ)で切り替えます。 レジスタバンクの構成を図1.4に示します。

図 1.4 レジスタバンクの構成

R32C/100シリーズでは、レジスタバンク指定フラグを0にしたままで、レジスタバンク1をアクセスで きるアドレッシングモードを用意しています。

#### リセット解除後の内部レジスタ値 1.3.6

リセット解除後の各レジスタの値を以下に示します。

| • データレジスタ(R2R0/R3R1/R6R4/R7R5)                  | : 00000000h |

|-------------------------------------------------|-------------|

| •アドレスレジスタ(A0/A1/A2/A3)                          | : 00000000h |

| •スタティックベースレジスタ(SB)                              | : 00000000h |

| •フレームベースレジスタ(FB)                                | : 00000000h |

| •割り込みテーブルレジスタ(INTB)                             | : 00000000h |

| ・ユーザスタックポインタ(USP)                               | : 00000000h |

| •割り込みスタックポインタ(ISP)                              | : 00000000h |

| •フラグレジスタ(FLG)                                   | : 00000000h |

| ・DMAモードレジスタ(DMD0/DMD1/DMD2/DMD3)                | : 00000000h |

| ・DMA ターミナルカウントレジスタ(DCT0/DCT1/DCT2/DCT3)         | : 不定        |

| ・DMA ターミナルカウントリロードレジスタ(DCR0/DCR1/DCR2/DCR3)     | : 不定        |

| ・DMAソースアドレスレジスタ(DSA0/DSA1/DSA2/DSA3)            | : 不定        |

| ・DMAソースアドレスリロードレジスタ(DSR0/DSR1/DSR2/DSR3)        | : 不定        |

| • DMA デスティネーションアドレスレジスタ(DDA0/DDA1/DDA2/DDA3)    | : 不定        |

| ・DMA デスティネーションアドレスリロードレジスタ(DDR0/DDR1/DDR2/DDR3) | : 不定        |

| ・フラグ退避レジスタ(SVF)                                 | : 不定        |

| • PC 退避レジスタ(SVP)                                | : 不定        |

| •ベクタレジスタ(VCT)                                   | : 不定        |

## 1.4 データタイプ

データタイプは整数型、10進数型、固定小数点型、浮動小数点型、ビット型、ストリング型の6種類です。

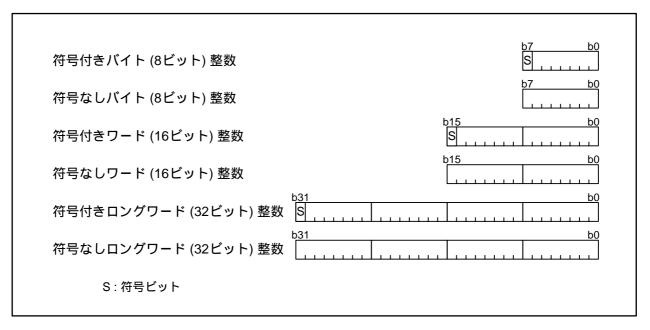

### 1.4.1 整数型

整数には符号付きと符号なしがあります。符号付き整数の負の値は2の補数で表現します。

図 1.5 整数型

## 1.4.2 10進数型

2進化10進数(BCD)を扱うことができます。10進数は、DADC、DADD、DSBB、DSUBの4種類の命令で使用できます。

図 1.6 10進数型

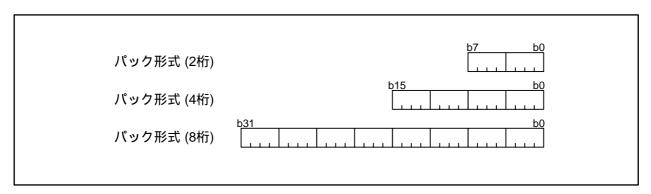

#### 固定小数点型 1.4.3

一般に固定小数点数の乗算は整数乗算命令とシフト命令で行いますが、R32C/100シリーズでは、固定 少数点専用の乗算命令 MULX を搭載しています。 MULX 命令でサポートする固定小数点数のフォーマッ トは図 1.7のとおりです。なお、DP=1のときは8ビット固定小数点数はありません。

図 1.7 固定小数点型

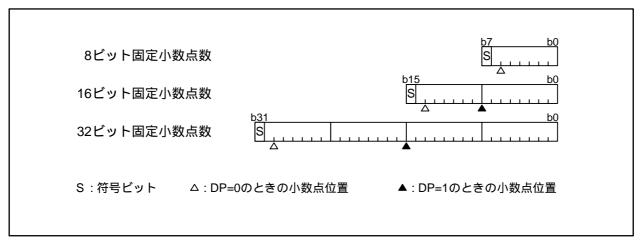

#### 1.4.4 浮動小数点型

R32C/100シリーズでは、IEEE754で規定されている単精度の浮動小数点型をサポートしています。 浮動小数点型は浮動小数点演算命令ADDF、CMPF、CNVIF、DIVF、MULF、ROUND、SUBFの7種類 の命令で使用できます。

#### 図 1.8 浮動小数点型

浮動小数点型は以下の数値をサポートしています。

- 0<E<255 (正規化数—Normal Numbers)

- E=0かつF=0 (ゼロ—Signed Zero)

以下の数値はサポートしていません。

- •E=0かつF>0 (非正規化数—Subnormal Numbers)

- E=255かつF=0 (無限大—Infinity)

- E=255かつF>0 (非数—NaN: Not-a-Number)

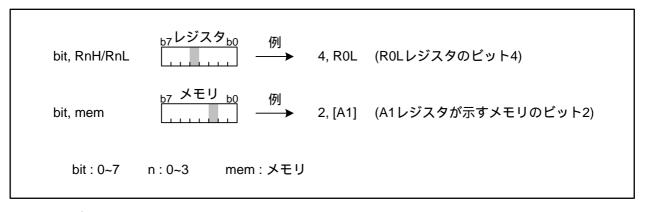

#### 1.4.5 ビット型

ビット型はBCLR、BSET、BNOT、BTST、BMCnd、BTSTS、BTSTCの7種類の命令で使用できます。 レジスタのビットは、レジスタ名と0~7のビット番号で指定します。指定できるレジスタは8ビット長 のレジスタ(R0L/R0H/R1L/R1H/R2L/R2H/R3L/R3H)だけです。

メモリのビットも同様に対象とするアドレスと0~7のビット番号で指定します。アドレス指定に使用で きるアドレッシングモードは、絶対(BTST:Sのみ)、0番地相対、アドレスレジスタ間接、アドレスレジス タ相対、SB相対、FB相対の6種類です。

図 1.9 ビット型

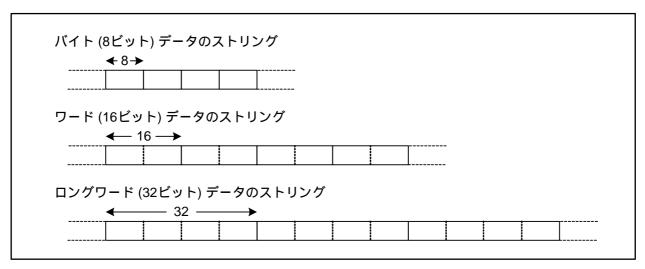

## 1.4.6 ストリング型

ストリング型はバイト(8ビット)、ワード(16ビット)、ロングワード(32ビット)のうち、同じ種類の データを任意の数だけ連続して並べたデータタイプです。

ストリング命令SMOVB、SMOVF、SMOVU、SCMPU、SIN、SOUT、SSTR、SUNTIL、SWHILEの9種 類の命令で使用できます。

図 1.10 ストリング型

# 1.5 データ配置

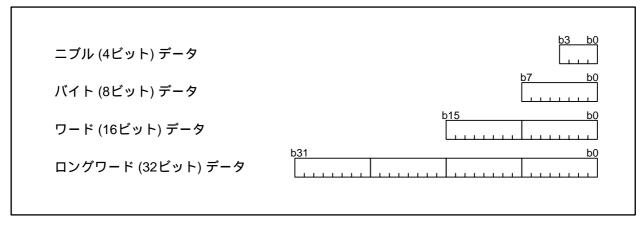

## 1.5.1 レジスタ上のデータ配置

レジスタのデータサイズとビット番号の関係を図 1.11に示します。

図 1.11 レジスタ上のデータ配置

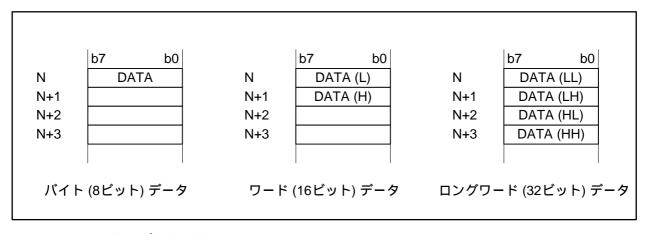

## 1.5.2 メモリ上のデータ配置

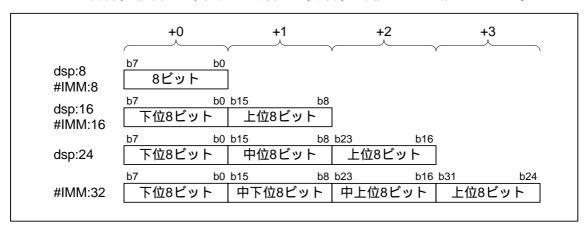

メモリ上のデータ配置を図 1.12に示します。

図 1.12 メモリ上のデータ配置

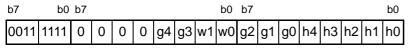

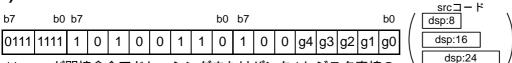

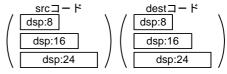

#### 1.6 命令フォーマット

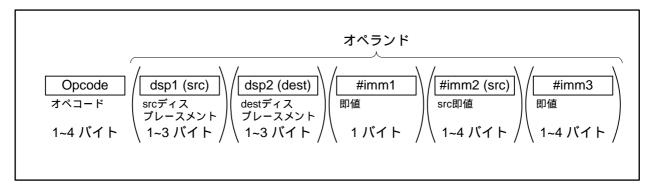

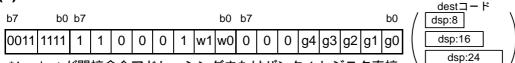

R32C/100シリーズの命令は図 1.13のように構成され、1命令あたり最短で1バイト、最長で14バイトにな ります。命令の動作、オペランドの種類と数、命令の長さはオペコードの部分で決定されます。

図 1.13 命令フォーマット

R32C/100 シリーズでは、使用頻度が高いと思われる命令がより少ないバイト数になるように命令コード を定義しています。また一部の命令では、使用できるアドレッシングモードを限定することでさらに命令 バイト数を少なくしたフォーマットが選択できます。

命令のフォーマットには、ジェネリック、クイック、ショート、ゼロの4つの形式があります。 各フォーマットの特徴を以下に示します。

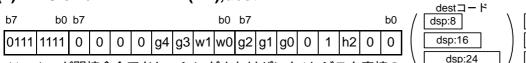

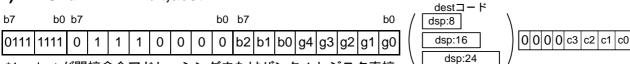

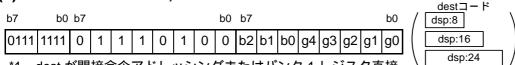

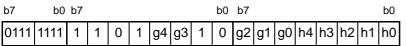

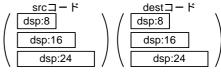

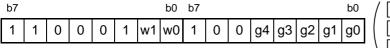

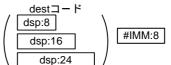

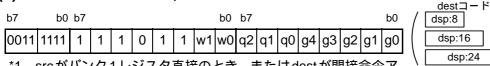

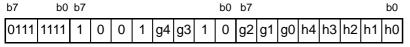

#### (1) ジェネリック形式(:G)

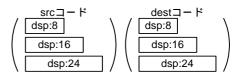

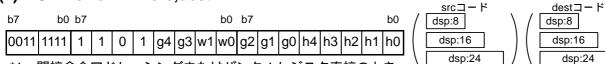

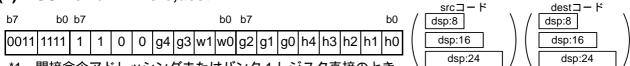

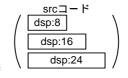

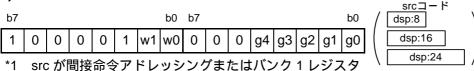

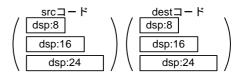

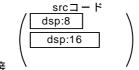

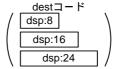

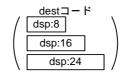

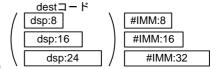

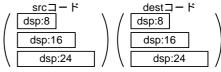

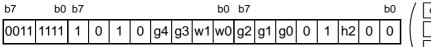

ジェネリック形式のオペコードは2~3バイトです。このオペコードには、動作およびsource (以下src と省略)とdestination(以下destと省略)のアドレッシングモードの情報が含まれます。

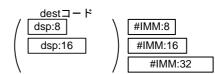

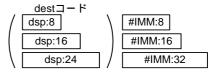

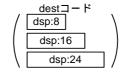

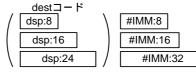

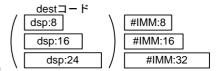

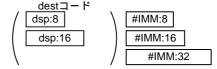

命令コードはオペコード(2~3バイト)とsrc コード(0~4バイト)およびdest コード(0~3バイト)で構成 されます。

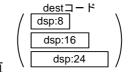

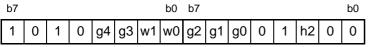

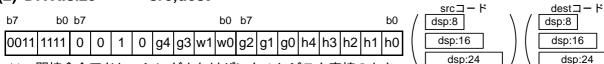

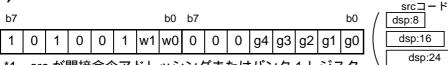

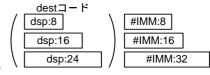

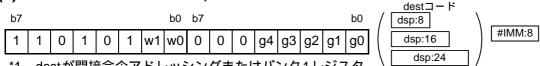

#### (2) クイック形式(:Q)

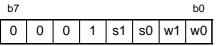

クイック形式のオペコードは1~2バイトです。このオペコードには、動作および即値データとdestの アドレッシングモードの情報が含まれます。ただしオペコードに含まれる即値データは3ビットもしく は4ビットで表現できる数値に制限されます。

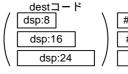

命令コードは即値データを含むオペコード(1~2バイト)とdestコード(0~3バイト)で構成されます。

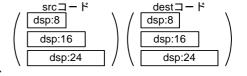

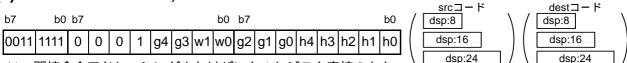

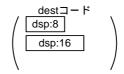

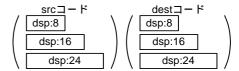

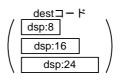

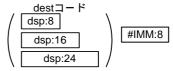

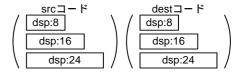

#### (3) ショート形式(:S)

ショート形式のオペコードは1~2バイトです。このオペコードには、動作およびsrc とdestのアドレッ シングモードの情報が含まれます。ただし、使用できるアドレッシングモードは制限されます。 命令コードはオペコード(1~2バイト)とsrc コード(0~4バイト)およびdest コード(0~2バイト)で構成

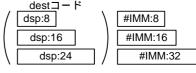

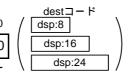

#### (4) ゼロ形式(:Z)

されます。

ゼロ形式のオペコードは1バイトです。このオペコードには、動作(および即値データ)とdestのアド レッシングモードの情報が含まれます。ただし、即値データは0固定です。また、使用できるアドレッ シングモードも制限されます。

命令コードはオペコード(1バイト)とdest コード $(0\sim2$ バイト)で構成されます。

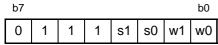

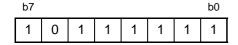

#### オペコード 1.6.1

オペコードは1~3バイト長のビット列で構成されます。オペランドのアドレッシングモードが「間接命 令アドレッシング」または「バンク1レジスタ直接」のときは、オペコードの先頭に8ビットのビット列 が付き、2~4バイトの長さになります。

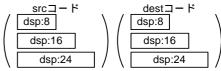

#### 1.6.2 オペランド

オペランドはdsp1、dsp2、#imm1、#imm2、#imm3の各フィールドで構成されます。各フィールドは命 令や選択するアドレッシングモードによって省略されます。

src コードはdsp1 フィールドまたは#imm2 フィールドに配置され、dest コードはdsp2 フィールドに配置 されます。#imm1 フィールドはオペコードを拡張するときに用いられます。ただし、src コードを2つ持 つ命令(CLIP、STZX)では、src1を#imm2フィールドに、src2を#imm3フィールドに配置します。

#### (1) dsp1フィールド

dsp1 フィールドは 1~3 バイトで構成されます。src のアドレッシングモードが絶対もしくは相対 (ス タックポインタ相対を除く)のときのみこのフィールドが存在します。

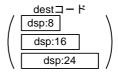

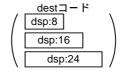

### (2) dsp2フィールド

dsp2 フィールドは 1~3 バイトで構成されます。dest のアドレッシングモードが相対(プログラムカウ ンタ相対を除く)のときのみこのフィールドが存在します。

#### (3) #imm1フィールド

#imm1フィールドは1バイトで構成されます。一部の命令にのみこのフィールドが存在します。

BMCnd命令 #imm1フィールドに8ビットの即値を配置し、下位4ビットで条件コードを

指定します。

LDC/STC命令 #imm1フィールドに配置された8ビットの即値でDMAC関連レジスタおよび

VCTレジスタを指定します。SB、FB、FLG、SP、ISP、SVF、SVP、INTB

をアクセスするときは、このフィールドは存在しません。

MOV dsp:8[SP] #imm1フィールドに配置された8ビットの即値がスタックポインタに対する

ディスプレースメントdsp:8を表します。

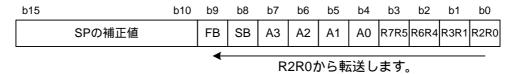

PUSHM/POPM命令 #imm1フィールドに8ビットの即値を配置し、"1"になっているビットの位

置で退避/復帰するレジスタを指定します。

ROT/SHA/SHL命令 #imm1フィールドに配置された8ビットの即値がシフト数を表します。

#### (4) #imm2フィールド

#imm2フィールドは1/2/4バイトで構成されます。srcのアドレッシングモードが即値、符号拡張即値 のときのみこのフィールドが存在します。

#### (5) #imm3フィールド

#imm3フィールドは1/2/4バイトで構成されます。一部の命令にのみこのフィールドが存在します。

CLIP/STZX命令 srcオペランドに2つの即値を指定します。第1の即値を#imm2フィールド に、第2の即値を#imm3フィールドに設定します。

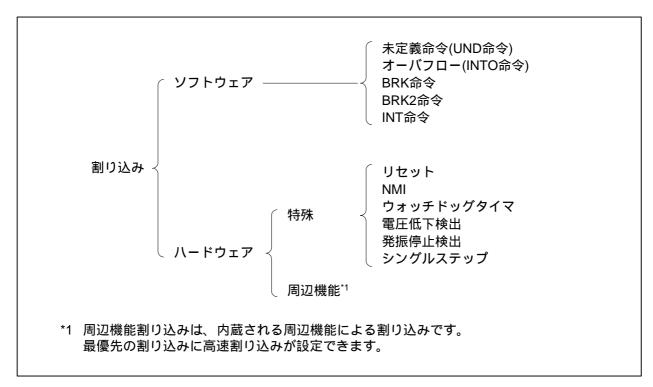

## 1.7 ベクタテーブル

ベクタテーブルには、割り込みベクタテーブルがあり、割り込みベクタテーブルには、固定ベクタテー ブルと可変ベクタテーブルがあります。

#### 1.7.1 固定ベクタテーブル

固定ベクタテーブルは、固定アドレス(FFFFFFDCh~FFFFFFFh番地)に配置された割り込みベクタテー ブルです。図 1.14に固定ベクタテーブルを示します。

割り込みベクタテーブルは、1本あたり4バイトからなる9本の割り込みベクタで構成されています。各 ベクタには、割り込みルーチンの先頭アドレスを設定します。

|           | ブル                       |

|-----------|--------------------------|

|           | 3 2 1 1 0                |

| FFFFFDCh  | 未定義命令                    |

| FFFFFE0h  | オーバフロー                   |

| FFFFFE4h  | BRK命令                    |

| FFFFFE8h  | 予約領域                     |

| FFFFFECh  | 予約領域                     |

| FFFFFF0h  | ウォッチドッグタイマ、電圧低下検出、発振停止検出 |

| FFFFFFF4h | 予約領域                     |

| FFFFFFF8h | NMI                      |

| FFFFFFCh  | リセット                     |

図 1.14 固定ベクタテーブル

#### 可変ベクタテーブル 1.7.2

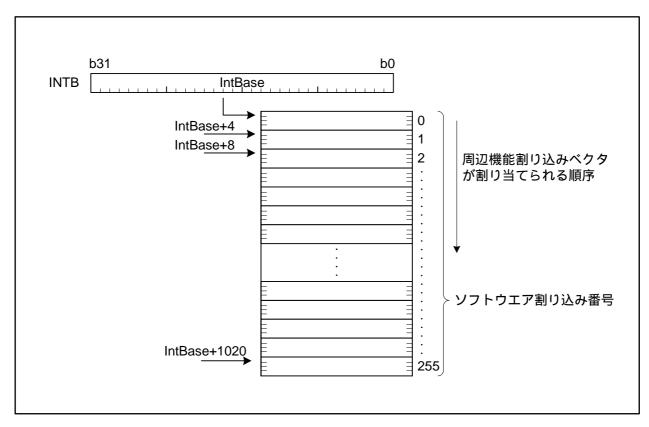

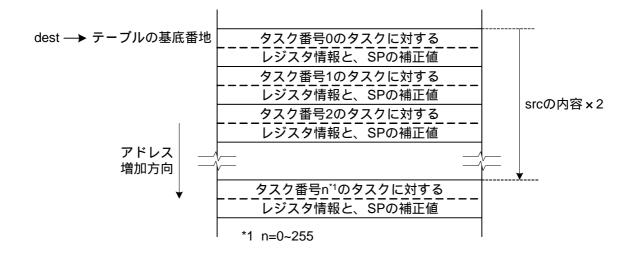

可変ベクタテーブルは、テーブルの配置アドレスを変えることができるベクタテーブルです。可変ベ クタテーブルは、割り込みテーブルレジスタ (INTB) の内容で示された値を先頭アドレス (IntBase) とする 1Kバイトの割り込みベクタテーブルです。図 1.15に可変ベクタテーブルを示します。

可変ベクタテーブルは、1本あたり4バイトからなる256本の割り込みベクタで構成されています。各 ベクタ領域には、割り込み処理ルーチンの先頭アドレスを設定します。また、ベクタごとにソフトウェ ア割り込み番号(0~255)があり、INT命令では、このソフトウェア割り込み番号を使用します。

内蔵周辺機能の割り込み(周辺機能割り込み)も可変ベクタテーブルに割り当てられます。周辺機能割 り込みの割り込みベクタは、ソフトウェア割り込み番号の0番側から割り当てられますが、品種によって 数が異なることがあります。よって、INT命令割り込みを使用する場合、ソフトウェア番号割り込み番号 255から使用することを推奨します。

INT 命令割り込みに使用するスタックポインタ (SP) は、ソフトウェア割り込み番号によって異なりま す。

ソフトウェア割り込み番号 0~127 では、割り込み要求受け付け時にスタックポインタ指定フラグ (Uフ ラグ)を退避し、Uフラグを "0" にして割り込みスタックポインタ(ISP)を選択した後、割り込みシーケン スを実行します。割り込み処理ルーチンから復帰するときに割り込み要求受け付け前の U フラグが復帰 されます。

ソフトウェア割り込み番号128~255では、スタックポインタは切り替わりません。

周辺機能割り込みでは、ソフトウェア割り込み番号に関係なく、割り込み要求受け付け時に割り込み スタックポインタ(ISP)を選択します。

図 1.15 可変ベクタテーブル

1.7 ベクタテーブル

# 2. アドレッシングモード

- 2.1 アドレッシングモード

- 2.2 本章の見方

- 2.3 一般命令アドレッシング

- 2.4 間接命令アドレッシング

- 2.6 特定命令アドレッシング

- 2.7 ビット命令アドレッシング

#### アドレッシングモード 2.1

本章ではアドレッシングモードを示す記号、動作についてアドレッシングモードごとに説明しています。 アドレッシングモードは、以下に示す5つのタイプがあります。

### (1) 一般命令アドレッシング

汎用レジスタやメモリをアクセスする最も一般的なアドレッシングです。

- レジスタ直接

- 即値

- •符号拡張即値

- •0番地相対

- アドレスレジスタ間接

- アドレスレジスタ相対

- SB 相対

- FB 相対

#### (2) 間接命令アドレッシング

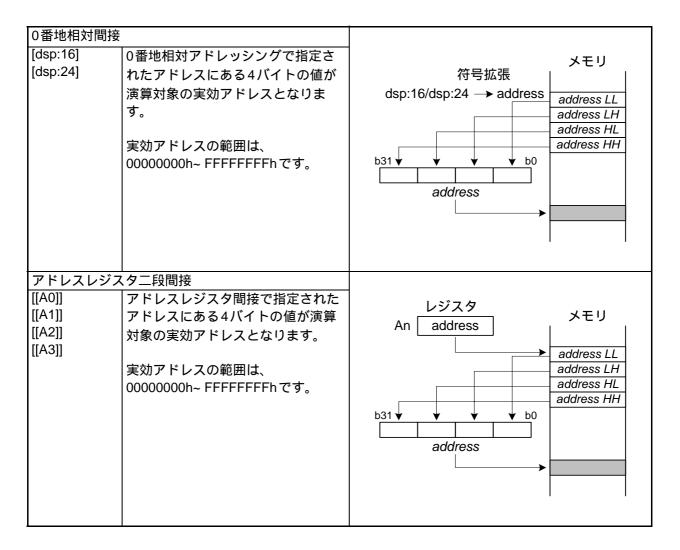

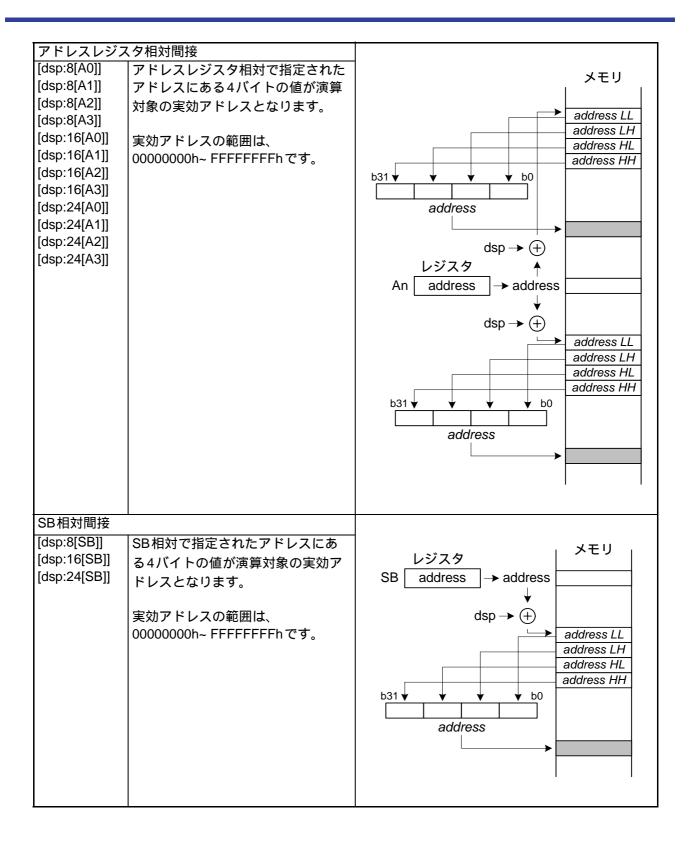

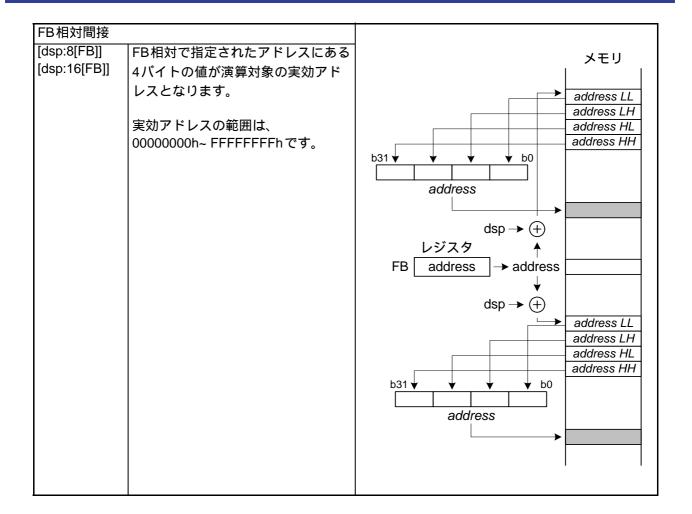

メモリに書かれた情報を元にメモリをアクセスするアドレッシングです。一般命令アドレッシングを サポートするほぼすべての命令で使用できます。

- •0番地相対間接

- アドレスレジスタ二段間接

- •アドレスレジスタ相対間接

- •SB相対間接

- •FB相対間接

# (3) 拡張命令アドレッシング

一般命令アドレッシングでは直接アクセスできないレジスタやメモリをアクセスしたり、コードサイ ズを削減するために拡張されたアドレッシングです。

- •バンク1レジスタ直接

- 短縮即値

- スタックポインタ相対

#### (4) 特定命令アドレッシング

専用レジスタやフラグ、メモリをアクセスするアドレッシング、および分岐に使用するアドレッシン グです。一部の命令でのみサポートしています。

- •専用レジスタ直接

- FLG直接

- 絶対

- プログラムカウンタ相対

### (5) ビット命令アドレッシング

汎用レジスタやメモリをビット単位でアクセスするアドレッシングです。

- レジスタ直接

- 絶対

- •0番地相対

- アドレスレジスタ間接

- アドレスレジスタ相対

- SB 相対

- FB 相対

#### 本章の見方 2.2

本章の見方を以下に実例をあげて示します。

# (1) 名称

アドレッシングの名称です。

# (2) 記号

アドレッシングモードを示す記号です。

":3"、":4"、":8"、":16"、":24"、":32" は、直前の値の有効ビット数を示します。マニュアルの記載 上、有効ビット数を明記する必要があるために記載していますが、通常は記述する必要はありません。 "dsp"などの記号は数値やシンボルに置き換えて記述してください。

# (3) 解説

動作、実効アドレスの範囲を説明します。

# (4) 動作図

動作を図で説明します。

# 2.3 一般命令アドレッシング

汎用レジスタやメモリをアクセスする最も一般的なアドレッシングです。ほとんどの命令で使用できま す。

| レジスタ直接   |                   |                                             |

|----------|-------------------|---------------------------------------------|

| R0L      | 指定したレジスタが演算の対象とな  |                                             |

| R0H      | ります。              |                                             |

| R1L      |                   | 1 > 2 7 7                                   |

| R1H      |                   | レジスタ                                        |

| R2L      |                   | b7 b0                                       |

| R2H      |                   | R0L/R1L                                     |

| R3L      |                   | b15 b8                                      |

| R3H      |                   | R0H/R1H                                     |

| R0       |                   | b23 b16                                     |

| R1       |                   | R2L/R3L                                     |

| R2       |                   | b31 b24                                     |

| R3       |                   | R2H/R3H  !                                  |

| R4       |                   | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\      |

| R5       |                   | R0/R1/ [b15 b8 b7 b0                        |

| R6       |                   | R4/R5                                       |

| R7       |                   | R2/R3/ b31 b24 b23 b16                      |

| R2R0     |                   | R6/R7 L                                     |

| R3R1     |                   |                                             |

| R6R4     |                   | R2R0/R3R1/ b31 b24 b23 b16 b15 b8 b7 b0     |

| R7R5     |                   | R6R4/R7R5/                                  |

| A0       |                   | A0/A1/A2/A3                                 |

| A1       |                   | R3R1R2R0/ b63 b56 b48 b40 b32 b24 b16 b8 b0 |

| A2       |                   | R7R5R6R4/                                   |

| A3       |                   | A1A0/A3A2                                   |

| R3R1R2R0 |                   |                                             |

| R7R5R6R4 |                   |                                             |

| A1A0     |                   |                                             |

| A3A2     |                   |                                             |

| 即值       |                   |                                             |

| #IMM     | #IMMで示した即値が演算の対象と | <u>b7 b0</u>                                |

| #IMM:8   | なります。             | #IMM:8                                      |

| #IMM:16  |                   | b15 b8 b7 b0                                |

| #IMM:32  |                   | #IMM:16                                     |

|          |                   | b31 b24 b23 b16 b15 b8 b7 b0                |

|          |                   | #IMM:32                                     |

|          |                   | <u> </u>                                    |

|          |                   |                                             |

| 符号扩張即值                                                                                                                                                                      |                                                                                                                                                |                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 符号拡張即值<br>#IMMEX:<br>#IMMEX:16<br>#IMMEX:16                                                                                                                                 | #IMMEXで示した即値をサイズ指定子で指定されたビット長に符号拡張した結果が演算の対象となります。  ディスプレースメント(dsp)で示した値を符号拡張した結果が演算対象                                                         | サイズ指定子に.Wを指定 #IMMEX:8                                                     |

| アドレスレジス                                                                                                                                                                     | の実効アドレスとなります。<br>実効アドレスの範囲は、dsp:16では<br>00000000h~00007FFFhと、<br>FFFF8000h~FFFFFFFhで、dsp:24<br>では00000000h~007FFFFhと、<br>FF800000h~FFFFFFFhです。 | 符号拡張 dsp:16/dsp:24 → address                                              |

| [A0]<br>[A1]<br>[A2]<br>[A3]                                                                                                                                                | アドレスレジスタ(A0/A1/A2/A3)の<br>値が演算対象の実効アドレスとなり<br>ます。<br>実効アドレスの範囲は、<br>00000000h~ FFFFFFFhです。                                                     | メモリ<br>An address                                                         |

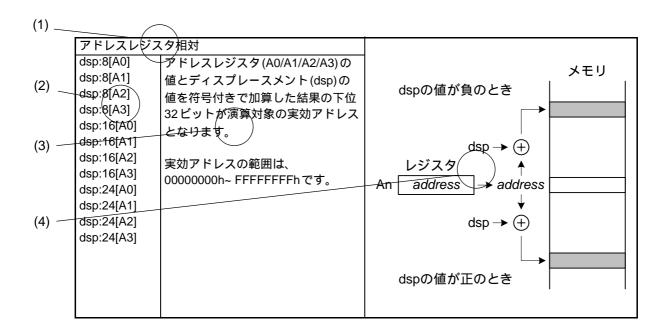

| マドレスレジス<br>dsp:8[A0]<br>dsp:8[A1]<br>dsp:8[A2]<br>dsp:8[A3]<br>dsp:16[A0]<br>dsp:16[A1]<br>dsp:16[A2]<br>dsp:16[A3]<br>dsp:24[A0]<br>dsp:24[A1]<br>dsp:24[A2]<br>dsp:24[A3] | スタ相対 アドレスレジスタ(A0/A1/A2/A3)の値とディスプレースメント(dsp)の値を符号付きで加算した結果の下位32ビットが演算対象の実効アドレスとなります。 実効アドレスの範囲は、00000000h~ FFFFFFFF です。                        | メモリ dspの値が負のとき  dsp → +  レジスタ ↑ An address → address  dsp → +  dspの値が正のとき |

| SB相対                                  |                                                                                                                                    |                                                                |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| dsp:8[SB]<br>dsp:16[SB]<br>dsp:24[SB] | スタティックベースレジスタ(SB)の値とディスプレースメント(dsp)の値を符号なしで加算した結果の下位32ビットが演算対象の実効アドレスとなります。  実効アドレスの範囲は、00000000h~ FFFFFFFF です。                    | レジスタ SB address → address   dsp → +                            |

| FB相対                                  | '                                                                                                                                  |                                                                |

| dsp:8[FB]<br>dsp:16[FB]               | フレームベースレジスタ(FB)の値と<br>ディスプレースメント(dsp)の値を<br>符号付きで加算した結果の下位32<br>ビットが演算対象の実効アドレスと<br>なります。<br>実効アドレスの範囲は、<br>00000000h~ FFFFFFFhです。 | メモリ dspの値が負のとき dsp → (+) レジスタ ↑ FB address → address dsp → (+) |

|                                       |                                                                                                                                    | dspの値が正のとき                                                     |

#### 間接命令アドレッシング 2.4

#### 拡張命令アドレッシング 2.5

| バンク1レジス        | 夕直接               |                                                           |

|----------------|-------------------|-----------------------------------------------------------|

| R0LB           | 指定したバンク1レジスタが演算の  |                                                           |

| R0HB           | 対象となります。          |                                                           |

| R1LB           |                   | レジスタ                                                      |

| R1HB           | Bフラグの値に関わらず、常にバン  |                                                           |

| R2LB           | ク1レジスタ直接が指定できます。  | R0LB/R1LB : b7 b0                                         |

| R2HB           |                   |                                                           |

| R3LB           |                   | b15 b8                                                    |

| R3HB           |                   | R0HB/R1HB                                                 |

| R0B            |                   | b23 b16                                                   |

| R1B            |                   | R2LB/R3LB                                                 |

| R2B            |                   | b31 b24                                                   |

| R3B            |                   | R2HB/R3HB                                                 |

| R4B            |                   | DOD/D4D/ b15 b8 b7 b0                                     |

| R5B            |                   | R0B/R1B/<br>R4B/R5B                                       |

| R6B            |                   | h31 h24 h23 h16                                           |

| R7B            |                   | R2B/R3B/                                                  |

| R2R0B<br>R3R1B |                   | R6B/R7B Lj                                                |

| R6R4B          |                   | R2R0B/R3R1B/<br>R6R4B/R7R5B/ b31 b24 b23 b16 b15 b8 b7 b0 |

| R7R5B          |                   | K0K4D/K/K3D/                                              |

| A0B            |                   | A0B/A1B/A2B/                                              |

| A1B            |                   | A3B                                                       |

| A2B            |                   | R3R1R2R0B/ 663 656 648 640 632 624 616 68 60 R7R5R6R4B/   |

| A3B            |                   | A1A0B / A3A2B                                             |

| R3R1R2R0B      |                   | THINGSTHONES                                              |

| R7R5R6R4B      |                   |                                                           |

| A1A0B          |                   |                                                           |

| A3A2B          |                   |                                                           |

| 短縮即値           |                   |                                                           |

| #0             | ゼロ、または#IMMで示した即値が | b2 b0                                                     |

| #IMM:3         | 演算の対象となります。       | #IMM:3                                                    |

| #IMM:4         |                   |                                                           |

|                | ゼロフォーマットや、クイック    | b3 b0                                                     |

|                | フォーマットで使用されます。    | #IMM:4                                                    |

|                |                   |                                                           |

| 1              |                   |                                                           |

| スタックポイン   | ク相対                                                                                                                                |                                                                       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| dsp:8[SP] | スタックポインタ(SP)の値とディスプレースメント(dsp)の値を符号付きで加算した結果の下位32ビットが演算対象の実効アドレスとなります。  実効アドレスの範囲は、00000000h~ FFFFFFFFhです。 このアドレッシングはMOV命令で使用できます。 | メモリ dspの値が負のとき dsp → + レジスタ ↑ SP address → address dsp → + dspの値が正のとき |

|           |                                                                                                                                    |                                                                       |

# 2.6 特定命令アドレッシング

| 専用レジスタ直 | 接                    |                         |                                   |

|---------|----------------------|-------------------------|-----------------------------------|

| SB      | 指定した専用レジスタが演算の対象     |                         | 1 257 4                           |

| FB      | となります。               |                         | <sub>b31</sub> レジスタ <sub>b0</sub> |

| FLG     |                      | SB                      |                                   |

| SP      | SPを指定した場合、Uフラグで示す    |                         | <u>b31</u> <u>b0</u>              |

| ISP     | スタックポインタが対象となりま      | FB                      |                                   |

| INTB    | す。                   |                         | b31 b0                            |

| SVF     | 9 0                  | FLG                     |                                   |

| SVP     | このアドレッシングはADD:Q、     |                         | h24                               |

| VCT     |                      | SP                      | b31 b0                            |

| DMD0    | LDC、POPC、PUSHC、STC命令 | OI .                    |                                   |

| DMD1    | で使用できます。             | 100                     | b31 b0                            |

| DMD2    |                      | ISP                     |                                   |

| DMD3    |                      |                         | b31 b0                            |

| DCT0    |                      | INTB                    |                                   |

| DCT1    |                      |                         | b31 b0                            |

| DCT2    |                      | SVF                     |                                   |

| DCT2    |                      |                         | b31 b0                            |

| DCT3    |                      | SVP                     | 551 50                            |

| DCR0    |                      | OVI                     |                                   |

| DCR1    |                      | VOT                     | b31 b0                            |

| DCR2    |                      | VCT                     |                                   |

|         |                      | DMD0/DMD1/              | b31 b0                            |

| DSA0    |                      | DMD2/DMD3               |                                   |

| DSA1    |                      |                         | b31 b0                            |

| DSA2    |                      | DCT0/DCT1/              |                                   |

| DSA3    |                      | DCT2/DCT3               | b31 b0                            |

| DSR0    |                      | DCR0/DCR1/              |                                   |

| DSR1    |                      | DCR2/DCR3               |                                   |

| DSR2    |                      | DSA0/DSA1/              | b31 b0                            |

| DSR3    |                      | DSA2/DSA3               |                                   |

| DDA0    |                      | DSR0/DSR1/              | b31 b0                            |

| DDA1    |                      | DSR2/DSR3               |                                   |

| DDA2    |                      | DDA0/DDA1/              | <u>b31</u> <u>b0</u>              |

| DDA3    |                      | DDA0/DDA1/<br>DDA2/DDA3 |                                   |

| DDR0    |                      |                         | b31 b0                            |

| DDR1    |                      | DDR0/DDR1/              |                                   |

| DDR2    |                      | DDR2/DDR3               |                                   |

| DDR3    |                      |                         |                                   |

|         |                      |                         |                                   |

| FLG直接   |                      |                         |                                   |

| U       | 指定したフラグが演算の対象となり     |                         |                                   |

| [1      | ます。                  |                         |                                   |

| 0       |                      |                         | by レジスタ bo                        |

| В       | このアドレッシングはFCLR、FSET  |                         | 00                                |

| S       | 命令で使用できます。           | FLG                     | U,I,O,B,S,Z,D,C                   |

| Z       |                      |                         |                                   |

| D       |                      |                         |                                   |

| С       |                      |                         |                                   |

|         |                      |                         |                                   |

|         |                      |                         |                                   |

| 絶対                                       |                                                                                                                                                                 |                                                                                                                 |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| abs:16                                   | absで示した値が演算対象の実効アドレスとなります。                                                                                                                                      | メモリ<br>                                                                                                         |

|                                          | 実効アドレスの範囲は、<br>00000000h~0000FFFFhです。                                                                                                                           | abs:16                                                                                                          |

|                                          | このアドレッシングはLDCTX、<br>STCTX命令で使用できます。                                                                                                                             |                                                                                                                 |

|                                          | カウンタ相対                                                                                                                                                          |                                                                                                                 |

| label<br>(dsp:3)                         | 分岐距離指定子(.length)が ".S" の場合                                                                                                                                      | メモリ<br>                                                                                                         |

|                                          | 現在のプログラムカウンタ(PC)の値とディスプレースメント(dsp)の値を符号なしで加算した結果の下位32ビットが実効アドレスとなります。                                                                                           | 現在のPC値  dsp → + label                                                                                           |

|                                          | 使用できます。                                                                                                                                                         | +1 dsp +8<br>現在のPC値は「分岐命令の番地+1」です。                                                                              |

| label<br>(dsp:8)<br>(dsp:16)<br>(dsp:24) | 分岐距離指定子(.length)が ".B" または ".W"、".A" の場合<br>現在のプログラムカウンタ(PC)の値とディスプレースメント(dsp)の値を符号付きで加算した結果の下位32ビットが実効アドレスとなります。<br>このアドレッシングは、J <i>Cnd</i> 、JMP、JSR命令で使用できます。 | メモリ dspの値が負のとき   abel                                                                                           |

|                                          |                                                                                                                                                                 | はSpの値が正のとき  ".B"のとき、-128 dsp +127 ".W"のとき、-32768 dsp +32767 ".A"のとき、-8388608 dsp +8388607 現在のPC値は「分岐命令の番地+1」です。 |

# 2.7 ビット命令アドレッシング

このアドレッシングは以下の命令で使用できます。 BCLR, BSET, BNOT, BTST, BMCnd, BTSTC, BTSTS

| レジスタ直接                                                                               |                                                                                                                                                                      |                                                                                                                      |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| bit,R0H<br>bit,R0L<br>bit,R1H<br>bit,R1L<br>bit,R2H<br>bit,R2L<br>bit,R3H<br>bit,R3L | 指定したレジスタのビットが演算の対象となります。 ビット位置(bit)には0~7が指定できます。                                                                                                                     | レジスタ  bit,R0L/ bit,R1L  ビット位置(3)  bit,R0H/ bit,R1H  ビット位置(5)  bit,R2L/ bit,R3L  ビット位置(0)  bit,R2H/ bit,R3H  ビット位置(4) |

| 絶対<br>bit,abs:16                                                                     | absで示した値が演算対象の実効アドレスとなります。<br>実効アドレスの範囲は、000000000h~0000FFFhです。<br>ビット位置(bit)には0~7が指定できます。<br>このアドレッシングはBTST命令でのみ使用できます。                                             | メモリ<br>abs:16<br>ビット位置<br>(1)                                                                                        |

| 0番地相対<br>bit,dsp:16<br>bit,dsp:24                                                    | ディスプレースメント(dsp)で示した値を符号拡張した結果が示すアドレスのビットが演算対象となります。 指定できるアドレスの範囲は、dsp:16では00000000h~00007FFFhと、FFFF8000h~FFFFFFFhで、dsp:24では00000000h~007FFFFhと、FF80000h~FFFFFFFFhです。 | メモリ<br>符号拡張<br>dsp:16/dsp:24 → address<br>ピット位置<br>(2)                                                               |

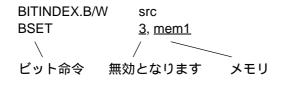

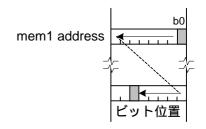

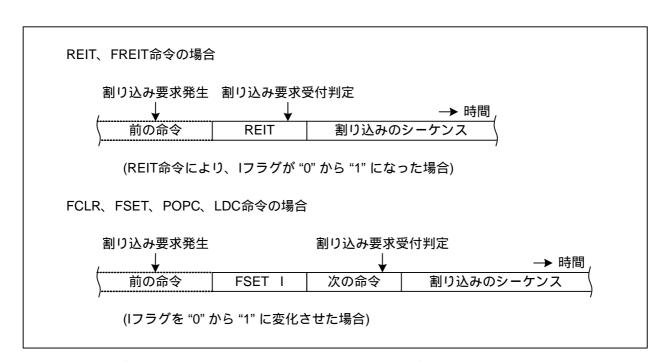

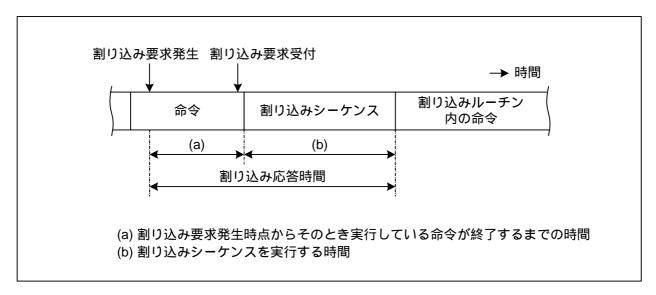

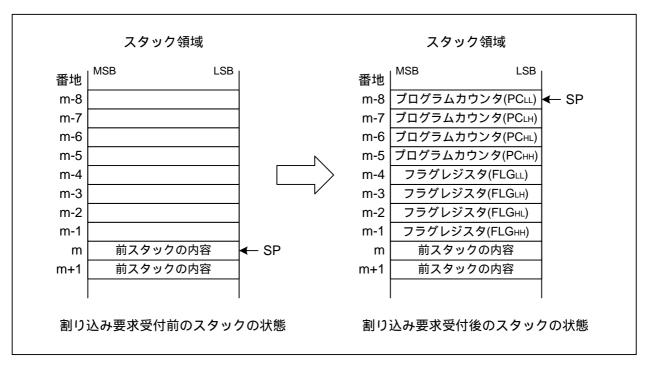

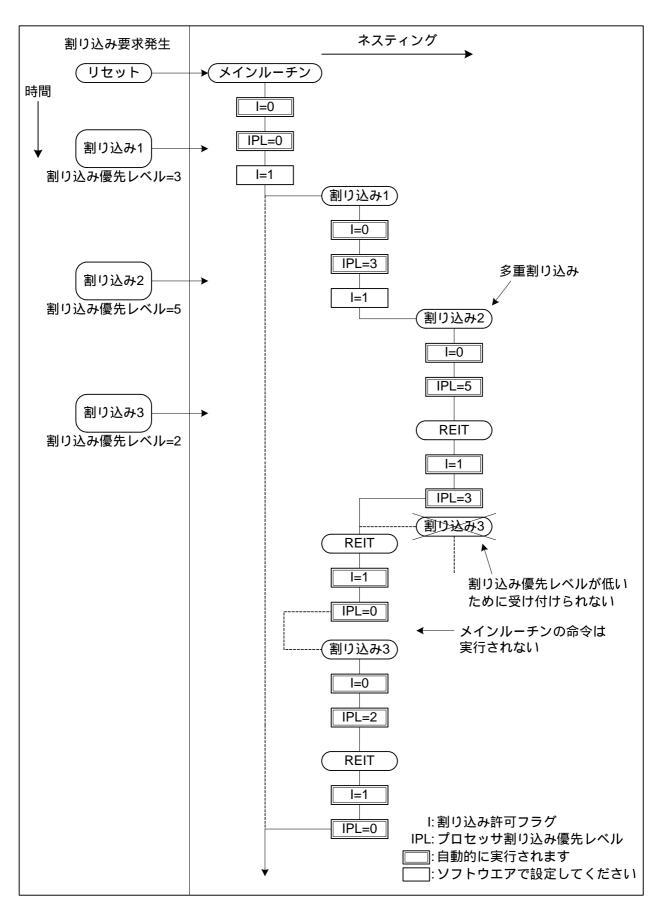

| アドレスレジス                                                                                                                                                                                                    | く 夕間接                                                                                                                                                |                                                                                          |