## カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

改訂一覧は表紙をクリックして直接ご覧になれます。 改訂一覧は改訂箇所をまとめたものであり、詳細については、 必ず本文の内容をご確認ください。

# H8S/2678グループ、 H8S/2678Rグループ

ハードウェアマニュアル

ルネサス16ビットシングルチップマイクロコンピュータ H8Sファミリ/ H8S/2600シリーズ

H8S/2676F-ZTAT<sup>™</sup> HD64F2676 H8S/2676 HD6432676 H8S/2675 HD6432675 H8S/2674R HD6412674R H8S/2673 HD6432673 H8S/2670 HD6412670

### 安全設計に関するお願い -

1. 弊社は品質、信頼性の向上に努めておりますが、半導体製品は故障が発生したり、 誤動作する場合があります。弊社の半導体製品の故障又は誤動作によって結果として、人身事故、火災事故、社会的損害などを生じさせないような安全性を考慮した 冗長設計、延焼対策設計、誤動作防止設計などの安全設計に十分ご留意ください。

### ■ 本資料ご利用に際しての留意事項 -

- 1. 本資料は、お客様が用途に応じた適切なルネサステクノロジ製品をご購入いただくための参考資料であり、本資料中に記載の技術情報についてルネサステクノロジが所有する知的財産権その他の権利の実施、使用を許諾するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例の使用に起因する損害、第三者所有の権利に対する侵害に関し、ルネサステクノロジは責任を負いません。

- 3. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他全ての情報 は本資料発行時点のものであり、ルネサステクノロジは、予告なしに、本資料に記載した製品または仕様を変更することがあります。ルネサステクノロジ半導体製品のご購入に当たりましては、事前にルネサステクノロジ、ルネサス販売または特約店へ最新の情報をご確認頂きますとともに、ルネサステクノロジホームページ (http://www.renesas.com) などを通じて公開される情報に常にご注意ください。

- 4. 本資料に記載した情報は、正確を期すため、慎重に制作したものですが万一本資料の記述誤りに起因する損害がお客様に生じた場合には、ルネサステクノロジはその責任を負いません。

- 5. 本資料に記載の製品データ、図、表に示す技術的な内容、プログラム及びアルゴリズムを流用する場合は、技術内容、プログラム、アルゴリズム単位で評価するだけでなく、システム全体で十分に評価し、お客様の責任において適用可否を判断してください。ルネサステクノロジは、適用可否に対する責任は負いません。

- 6. 本資料に記載された製品は、人命にかかわるような状況の下で使用される機器あるいはシステムに用いられることを目的として設計、製造されたものではありません。本資料に記載の製品を運輸、移動体用、医療用、航空宇宙用、原子力制御用、海底中継用機器あるいはシステムなど、特殊用途へのご利用をご検討の際には、ルネサステクノロジ、ルネサス販売または特約店へご照会ください。

- 7. 本資料の転載、複製については、文書によるルネサステクノロジの事前の承諾が必要です。

- 8. 本資料に関し詳細についてのお問い合わせ、その他お気付きの点がございましたらルネサステクノロジ、ルネサス販売または特約店までご照会ください。

## 製品に関する一般的注意事項

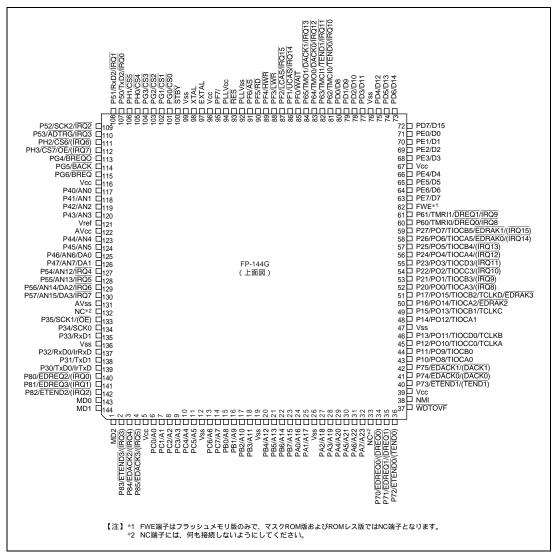

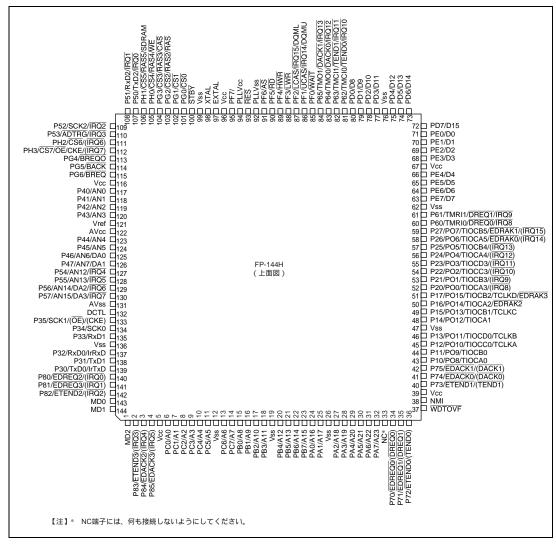

#### 1. NC 端子の処理

【注意】NC端子には、何も接続しないようにしてください。

NC(Non-Connection)端子は、内部回路に接続しない場合の他、テスト用端子やノイズ軽減などの目的で使用します。このため、NC端子には、何も接続しないようにしてください。

2. 未使用入力端子の処理

【注意】未使用の入力端子は、ハイまたはローレベルに固定してください。

CMOS製品の入力端子は、一般にハイインピーダンス入力となっています。未使用端子を開放状態で動作させると、周辺ノイズの誘導により中間レベルが発生し、内部で貫通電流が流れて誤動作を起こす恐れがあります。

未使用の入力端子は、入力をプルアップかプルダウンによって、ハイまたはローレベルに固定してください。

3. 初期化前の処置

【注意】電源投入時は,製品の状態は不定です。

すべての電源に電圧が印加され、リセット端子にローレベルが入力されるまでの間、内部回路は不確定であり、レジスタの設定や各端子の出力状態は不定となります。この不定状態によってシステムが誤動作を起こさないようにシステム設計を行ってください。

リセット機能を持つ製品は、電源投入後は、まずリセット動作を実行してください。

4. 未定義・リザーブアドレスのアクセス禁止

【注意】未定義・リザーブアドレスのアクセスを禁止します。

未定義・リザーブアドレスは、将来の機能拡張用の他、テスト用レジスタなどが割り付けられています。 これらのレジスタをアクセスしたときの動作および継続する動作については、保証できませんので、アクセスしないようにしてください。

## 本書の構成

本書は、以下の構成で制作しています。

- 1. 製品に関する一般的注意事項

- 2. 本書の構成

- 3. はじめに

- 4. 本版で改訂された箇所

改訂来歴は、前版の記載内容について訂正・追加された主な箇所についてまとめたものです。 改訂内容のすべてについて記載したものではありませんので、詳細については、本書の本文上 でご確認下さい。

- 5. 目次

- 6. 概要

- 7. 各機能モジュールの説明

- ・CPU およびシステム制御系

- ・内蔵周辺モジュール

各モジュールの機能説明の構成は、モジュール毎に異なりますが、一般的には、特長、 入出力端子、 レジスタの説明、 動作説明、 使用上の注意事項、等の節で構成されています。

本 LSI を用いた応用システムを設計する際、注意事項を十分確認の上設計してください。 各章の本文中には説明に対する注意事項と、各章の最後には使用上の注意事項があります。 必ずお読みください。(使用上の注意事項は必要により記載されます。)

- 8. レジスター覧

- 9. 電気的特性

- 10. 付録

- 11. 索引

## はじめに

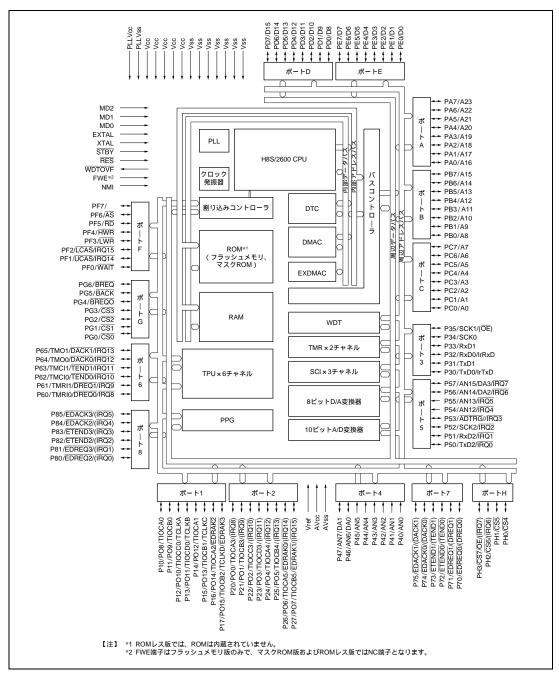

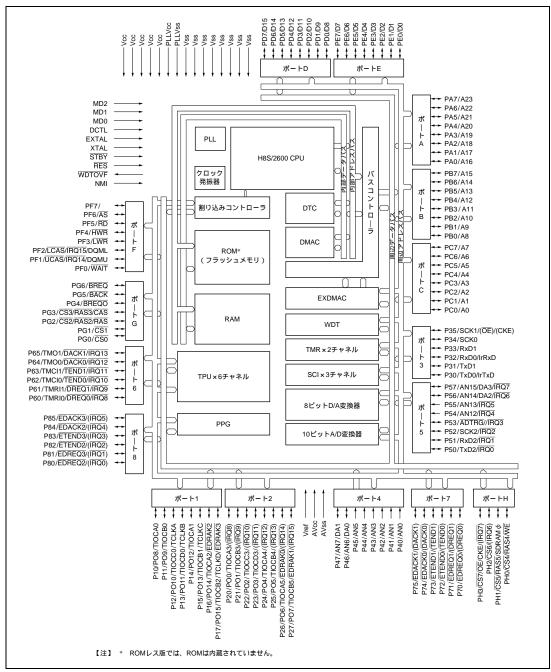

H8S/2678 グループ、H8S/2678R グループは、ルネサスオリジナルアーキテクチャを採用した H8S/2600 CPU を 核にして、システム構成に必要な周辺機能を集積したマイクロコンピュータ (MCU)です。

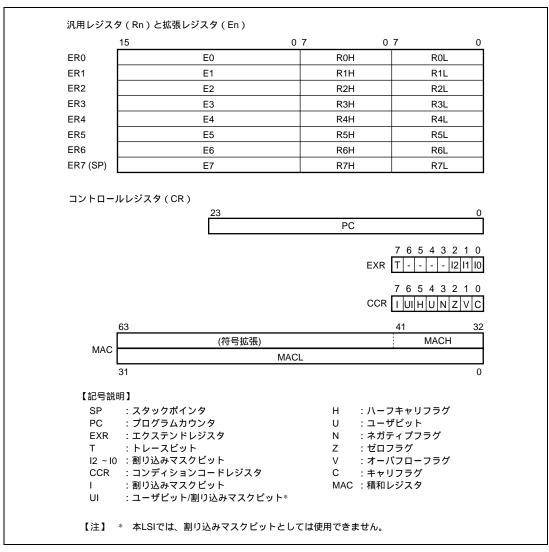

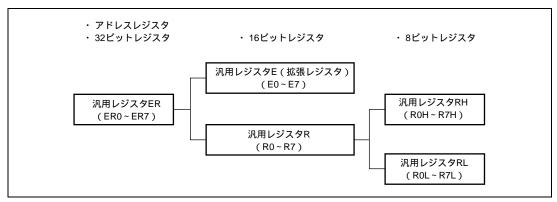

H8S/2600 CPU は、内部 32 ビット構成で、16 ビット×16 本の汎用レジスタと高速動作を指向した簡潔で最適化された命令セットを備えており、16M バイトのリニアなアドレス空間を扱うことができます。

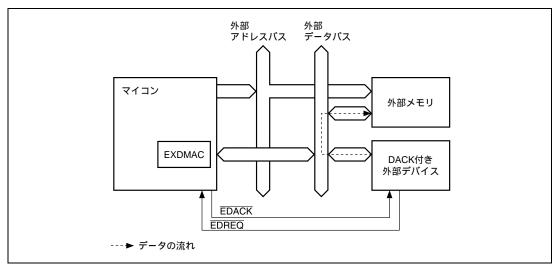

システム構成に必要な機能としては、DMA コントローラ (DMAC)、EXDMA コントローラ (EXDMAC)、データトランスファコントローラ (DTC)のバスマスタ、ROM、RAM のメモリ、16 ビットタイマパルスユニット(TPU)、プログラマブルパルスジェネレータ(PPG)、8 ビットタイマ(TMR)、ウォッチドッグタイマ(WDT)、シリアルコミュニケーションインタフェース(SCI、IrDA)、10 ビット A/D 変換器、8 ビット D/A 変換器、I/O ポートの周辺機能などを内蔵しています。

また、高機能バスコントローラを内蔵し、DRAM、SDRAM などの各種のメモリを高速かつ容易に接続できます。

内蔵 ROM は単一電源フラッシュメモリ(F- $ZTAT^{T*}$ \*)、マスク ROM があり、仕様流動性の高い応用機器、量産初期から本格的量産の各状況に応じた迅速かつ柔軟な対応が可能です。

【注】F-ZTAT<sup>™</sup>は(株)ルネサス テクノロジの商標です。

- 対象者 このマニュアルは、H8S/2678 グループ、H8S/2678R グループを用いた応用システムを設計するユーザ を対象としています。このマニュアルを使用される読者には、電気回路、論理回路、およびマイクロ コンピュータに関する基本的な知識を必要とします。

- 目的 このマニュアルは、H8S/2678 グループ、H8S/2678R グループのハードウェア機能と電気的特性をユーザに理解して頂くことを目的にしています。なお、実行命令の詳細については、「H8S/2600 シリーズ、H8S/2000 シリーズ ソフトウェアマニュアル」に記載していますので併せて御覧ください。

### 読み方

• 機能全体を理解しようとするとき。

目次に従って読んでください。

本書は、大きく分類すると、CPU、システム制御機能、周辺機能、電気的特性の順に構成されています。

• CPU機能の詳細を理解したいとき。

別冊の「H8S/2600シリーズ、H8S/2000シリーズ ソフトウェアマニュアル」を参照してください。

レジスタ名が分かっていて、詳細機能を知りたいとき。

本書の後ろに「索引」があります。索引からページ番号を検索してください。

「第23章 レジスター覧」にアドレス、ビット内容、初期化についてまとめています。

凡例 レジスタ表記 : 16 ビットタイマパルスユニット、シリアルコミュニケーションインタフェースなど、

同一または類似した機能が複数チャネルに存在する場合に次の表記を使用します。

XXX\_N (XXX は基本レジスタ名称、N はチャネル番号)

ビット表記順 : 左側が上位ビット、右側が下位ビットの順に表記します。

数字の表記 : 2 進数は B'XXXX、16 進数は H'XXXX、10 進数は XXXX 信号の表記 : ローアクティブの信号にはオーババーを付けます。  $\overline{XXXX}$

関連資料一覧 ウェブ・サイトに最新資料を掲載しています。ご入手の資料が最新版であるかを確認してください。 (http://japan.renesas.com/homepage.jsp)

## • H8S/2678グループ、H8S/2678Rグループに関するユーザーズマニュアル

| 資料名                                      | 資料番号       |

|------------------------------------------|------------|

| H8S/2678 グループ、H8S/2678R グループ ハードウェアマニュアル | 本マニュアル     |

| H8S/2600 グループ、H8S/2000 グループ ソフトウェアマニュアル  | RJJ09B0143 |

### • 開発ツール関連ユーザーズマニュアル

| 資料名                                                         | 資料番号            |

|-------------------------------------------------------------|-----------------|

| H8S、H8/300 シリーズ C/C++コンパイラ、アセンブラ、最適化リンケージエディタ<br>ユーザーズマニュアル | ADJ - 702 - 303 |

| H8S、H8/300 シリーズ シミュレータ・デバッガ(Windows 版)ユーザーズマニュアル            | ADJ - 702 - 163 |

| H8S、H8/300 シリーズ シミュレータ・デバッガ(UNIX 版)ユーザーズマニュアル               | ADJ - 702 - 355 |

| H8S、H8/300 シリーズ High-performance Embedded Workshop、         | ADJ 702 307     |

| High-performance Debugging Interface チュートリアル                |                 |

| High-performance Embedded Workshop ユーザーズマニュアル               | ADJ - 702 - 275 |

## • アプリケーションノート

| 資料名                                        | 資料番号            |

|--------------------------------------------|-----------------|

| H8S、H8/300 シリーズ C/C++コンパイラパッケージアプリケーションノート | RJJ05B0558      |

| F-ZTAT マイコンテクニカル Q&A                       | ADJ - 502 - 055 |

## 本版で改訂された箇所

| 修正項目 | ページ | 修正内容(詳細はマニュアル参照)            |

|------|-----|-----------------------------|

| 全体   |     | ● 社名変更による変更                 |

|      |     | 日立製作所 ルネサス テクノロジ            |

|      |     | ● 呼称変更による変更                 |

|      |     | H8S/2678 シリーズ H8S/2678 グループ |

## 目次

| 1.  | 概要.  |                                            | 1-1  |

|-----|------|--------------------------------------------|------|

| 1.1 | 4    | 寺長                                         | 1-1  |

| 1.2 | Į.   | 内部プロック図                                    | 1-3  |

| 1.3 | Ì    | <b>耑子説明</b>                                | 1-5  |

| 1   | 3.1  | ピン配置図                                      | 1-5  |

| 1   | 3.2  | 動作モード別ピン配置一覧                               | 1-7  |

| 1   | 3.3  | 端子機能                                       | 1-13 |

| 2   | CDII |                                            | 2.1  |

|     |      |                                            |      |

| 2.1 |      | 寺長                                         |      |

|     | 1.1  | H8S/2600 CPU と H8S/2000 CPU との相違点          |      |

|     | 1.2  | H8/300 CPU との相違点                           |      |

|     | 1.3  | H8/300H CPU との相違点                          |      |

| 2.2 |      | CPU動作モード                                   |      |

|     | 2.1  | ノーマルモード                                    |      |

| 2.  | 2.2  | アドバンストモード                                  |      |

| 2.3 |      | アドレス空間                                     |      |

| 2.4 |      | ノジスタの構成                                    | 2-9  |

| 2.4 | 4.1  | 汎用レジスタ                                     |      |

| 2.4 | 4.2  | プログラムカウンタ(PC)                              |      |

| 2.4 | 4.3  | エクステンドレジスタ(EXR)                            |      |

| 2.4 | 4.4  | コンディションコードレジスタ(CCR)                        | 2-12 |

| 2.4 | 4.5  | 積和レジスタ(MAC)                                | 2-13 |

| 2.4 | 4.6  | CPU 内部レジスタの初期値                             | 2-13 |

| 2.5 | =    | データ形式                                      | 2-14 |

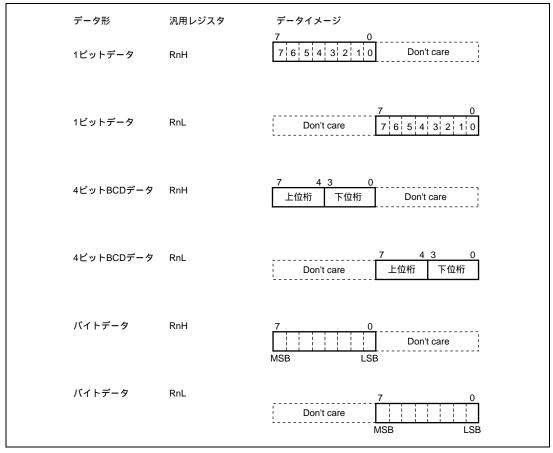

| 2.: | 5.1  | 汎用レジスタのデータ形式                               | 2-14 |

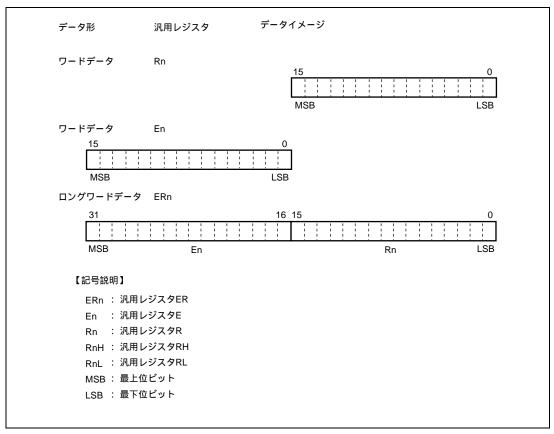

| 2.: | 5.2  | メモリ上でのデータ形式                                | 2-15 |

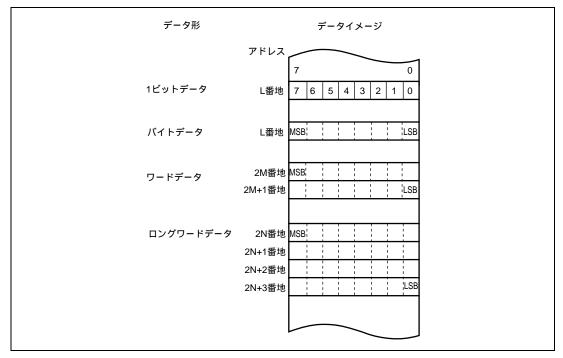

| 2.6 | î    | <b>冷令セット</b>                               | 2-17 |

| 2.0 | 6.1  | 命令の機能別一覧                                   | 2-18 |

| 2.0 | 6.2  | 命令の基本フォーマット                                | 2-28 |

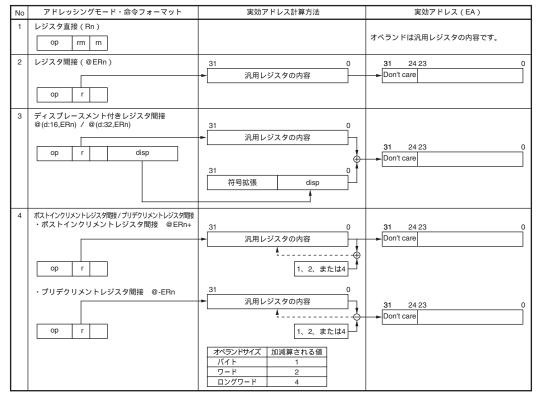

| 2.7 | -    | アドレッシングモードと実効アドレスの計算方法                     | 2-29 |

| 2.  | 7.1  | レジスタ直接 Rn                                  | 2-29 |

| 2.  | 7.2  | レジスタ間接 @ERn                                | 2-29 |

| 2.  | 7.3  | ディスプレースメント付きレジスタ @ (d:16,ERn)/@ (d:32,ERn) | 2-29 |

| 2.7.4  | ポストインクリメントレジスタ間接@ERn+/ プリデクリメントレジスタ間接@-ERn | 2-30 |

|--------|--------------------------------------------|------|

| 2.7.5  | 絶対アドレス @aa:8/@aa:16/@aa:24/@aa:32          | 2-30 |

| 2.7.6  | イミディエイト #xx:8/#xx:16/#xx:32                | 2-31 |

| 2.7.7  | プログラムカウンタ相対 @ (d:8, PC)/@ (d:16, PC)       | 2-31 |

| 2.7.8  | メモリ間接 @@aa:8                               | 2-31 |

| 2.7.9  | 実効アドレスの計算方法                                | 2-32 |

| 2.8    | 処理状態                                       | 2-35 |

| 2.9    | 使用上の注意事項                                   | 2-36 |

| 2.9.1  | ビット操作命令使用上の注意事項                            | 2-36 |

| 3. MC  | J 動作モード                                    | 3-1  |

| 3.1    | 動作モードの選択                                   | 3-1  |

| 3.2    | レジスタの説明                                    | 3-2  |

| 3.2.1  | モードコントロールレジスタ ( MDCR )                     | 3-2  |

| 3.2.2  | システムコントロールレジスタ ( SYSCR )                   | 3-3  |

| 3.3    | 各動作モードの説明                                  | 3-4  |

| 3.3.1  | モード1                                       | 3-4  |

| 3.3.2  | モード2                                       | 3-4  |

| 3.3.3  | モード3                                       | 3-4  |

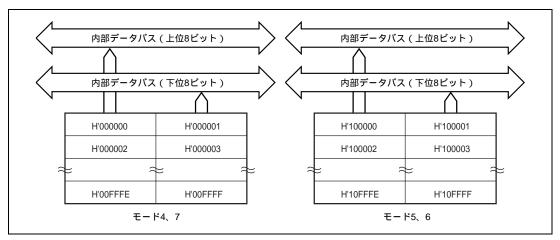

| 3.3.4  | モード4                                       | 3-4  |

| 3.3.5  | モード 5                                      | 3-5  |

| 3.3.6  | モード6                                       | 3-5  |

| 3.3.7  | モード7                                       | 3-5  |

| 3.3.8  | モード 10                                     | 3-6  |

| 3.3.9  | モード 11                                     | 3-6  |

| 3.3.10 | モード 12                                     | 3-6  |

| 3.3.11 | モード13                                      | 3-6  |

| 3.3.12 | モード 14                                     | 3-6  |

| 3.3.13 | モード 15                                     | 3-6  |

| 3.3.14 | 端子機能                                       | 3-7  |

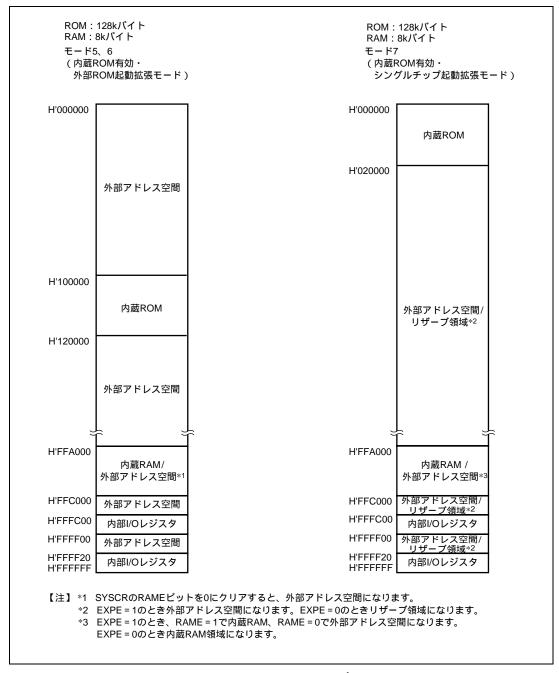

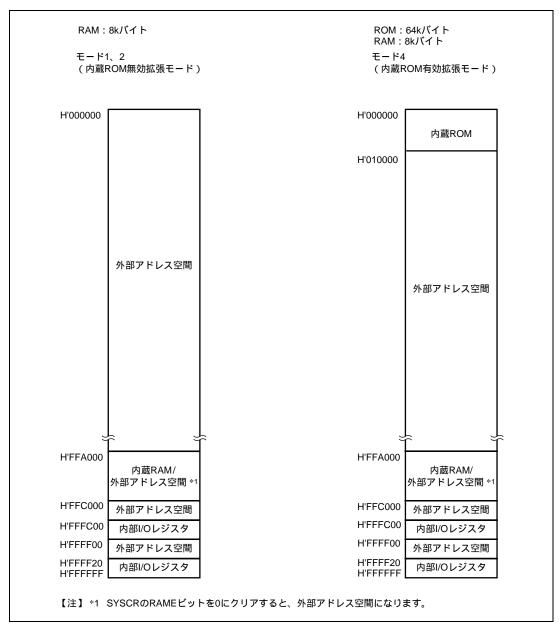

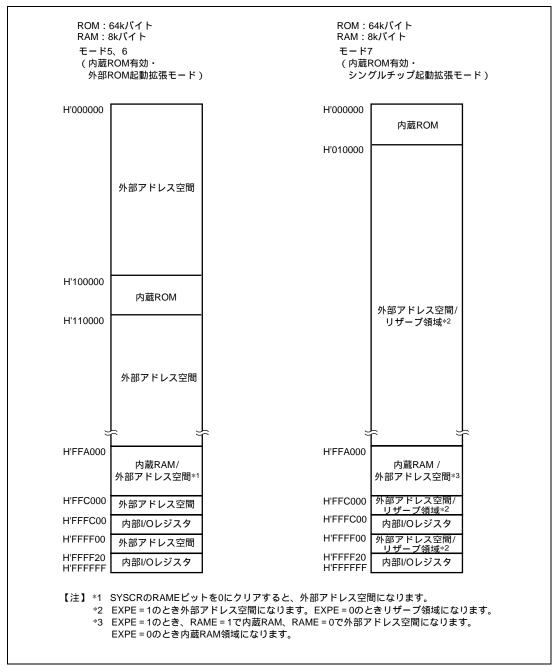

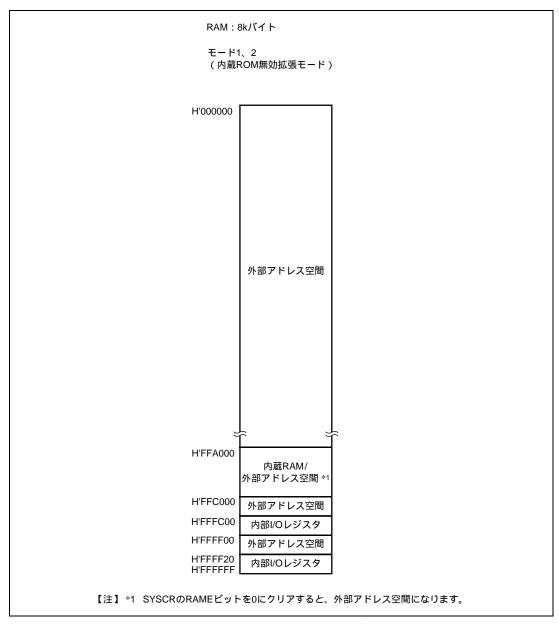

| 3.4    | 各動作モードのアドレスマップ                             | 3-8  |

| 4. 例列  | 処理                                         | 4-1  |

| 4.1    | 例外処理の種類と優先度                                | 4-1  |

| 4.2    | 例外処理要因とベクタテーブル                             | 4-2  |

| 4.3    | リセット                                       | 4-3  |

| 4.3.1  | リセット例外処理                                   | 4-3  |

| 4.3.2  | リセット直後の割り込み                                | 4-5  |

| 4.3.3  | リセット解除後の内蔵周辺機能                             | 4-5  |

| 4.4    | トレース例外処理                                   | 4-6  |

| 4.5   | 割り込み例外処理                              | 4-6  |

|-------|---------------------------------------|------|

| 4.6   | トラップ命令例外処理                            | 4-7  |

| 4.7   | 例外処理後のスタックの状態                         | 4-8  |

| 4.8   | 使用上の注意事項                              | 4-9  |

| 5. 割  | り込みコントローラ                             | 5-1  |

| 5.1   | 特長                                    | 5-1  |

| 5.2   | 入出力端子                                 | 5-2  |

| 5.3   | レジスタの説明                               | 5-3  |

| 5.3.1 | 割り込みコントロールレジスタ(INTCR)                 | 5-4  |

| 5.3.2 | インタラプトプライオリティレジスタ A ~ K(IPRA ~ IPRK)  | 5-5  |

| 5.3.3 | IRQ イネーブルレジスタ(IER)                    | 5-7  |

| 5.3.4 | IRQ センスコントロールレジスタ H、L ( ISCRH、ISCRL ) | 5-8  |

| 5.3.5 | IRQ ステータスレジスタ(ISR)                    | 5-11 |

| 5.3.6 | IRQ 端子セレクトレジスタ(ITSR )                 | 5-12 |

| 5.3.7 | ソフトウェアスタンバイ解除 IRQ イネーブルレジスタ(SSIER )   | 5-13 |

| 5.4   | 割り込み要因                                | 5-14 |

| 5.4.1 | 外部割り込み要因                              | 5-14 |

| 5.4.2 | 内部割り込み                                | 5-15 |

| 5.5   | 割り込み例外処理ベクタテーブル                       | 5-16 |

| 5.6   | 割り込み制御モードと割り込み動作                      | 5-20 |

| 5.6.1 | 割り込み制御モード 0                           | 5-20 |

| 5.6.2 | 割り込み制御モード 2                           | 5-22 |

| 5.6.3 | 割り込み例外処理シーケンス                         | 5-24 |

| 5.6.4 | 割り込み応答時間                              | 5-25 |

| 5.6.5 | 割り込みによる DTC、DMAC の起動                  | 5-26 |

| 5.7   | 使用上の注意事項                              | 5-28 |

| 5.7.1 | 割り込みの発生とディスエーブルとの競合                   | 5-28 |

| 5.7.2 | 割り込みを禁止している命令                         | 5-29 |

| 5.7.3 | 割り込み禁止期間                              | 5-29 |

| 5.7.4 | EEPMOV 命令実行中の割り込み                     | 5-29 |

| 5.7.5 | IRQ 端子セレクトレジスタ(ITSR)設定の変更             | 5-29 |

| 5.7.6 | IRQ ステータスレジスタ(ISR)について                | 5-29 |

| 6. バ  | スコントローラ(BSC)                          | 6-1  |

| 6.1   | 特長                                    | 6-1  |

| 6.2   | 入出力端子                                 | 6-3  |

| 6.3   | レジスタの説明                               |      |

| 6.3.1 | バスバス幅コントロールレジスタ(ABWCR)                | 6-6  |

| 6.3.2 | アクセスステートコントロールレジスタ(ASTCR)             | 6-6  |

| 6.3.3  | ウェイトコントロールレジスタ AH、AL、BH、BL                   |      |

|--------|----------------------------------------------|------|

|        | (WTCRAH, WTCRAL, WTCRBH, WTCRBL)             |      |

| 6.3.4  | リードストローブタイミングコントロールレジスタ(RDNCR)               |      |

| 6.3.5  | CS アサート期間コントロールレジスタ H、L(CSACRH、CSACRL)       | 6-11 |

| 6.3.6  | エリア 0 バースト ROM インタフェースコントロールレジスタ (BROMCRH)   |      |

|        | エリア 1 バースト ROM インタフェースコントロールレジスタ(BROMCRL)    |      |

| 6.3.7  | バスコントロールレジスタ (BCR)                           |      |

| 6.3.8  | DRAM コントロールレジスタ(DRAMCR)                      |      |

| 6.3.9  | DRAM アクセスコントロールレジスタ(DRACCR)                  |      |

| 6.3.10 | リフレッシュコントロールレジスタ(REFCR)                      |      |

| 6.3.11 | リフレッシュタイマカウンタ(RTCNT)                         |      |

| 6.3.12 | リフレッシュタイムコンスタントレジスタ(RTCOR)                   |      |

| 6.4    | バス制御                                         | 6-26 |

| 6.4.1  | エリア分割                                        | 6-26 |

| 6.4.2  | バス仕様                                         | 6-27 |

| 6.4.3  | メモリインタフェース                                   | 6-28 |

| 6.4.4  | チップセレクト信号                                    | 6-30 |

| 6.5    | 基本バスインタフェース                                  | 6-31 |

| 6.5.1  | データサイズとデータアライメント                             | 6-31 |

| 6.5.2  | 有効ストローブ                                      | 6-32 |

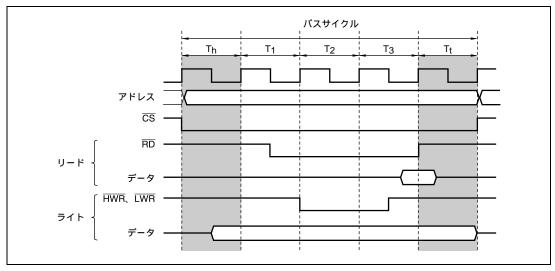

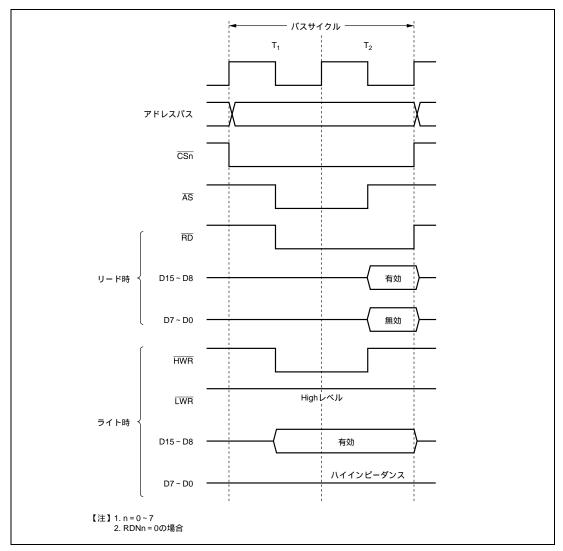

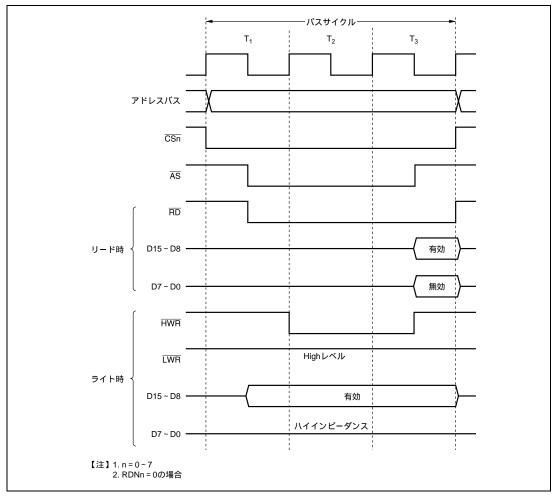

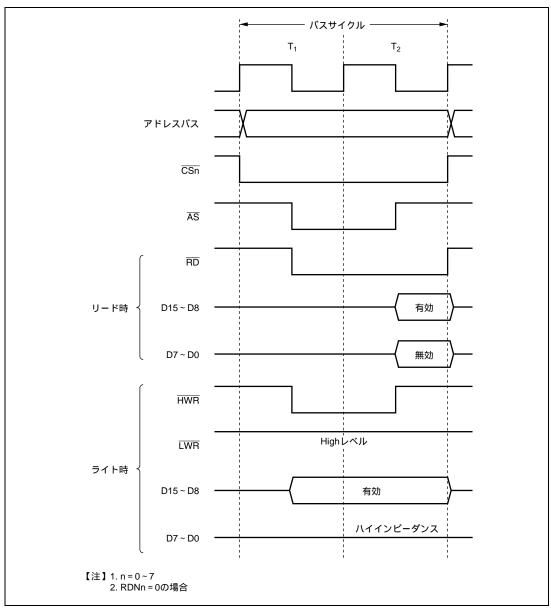

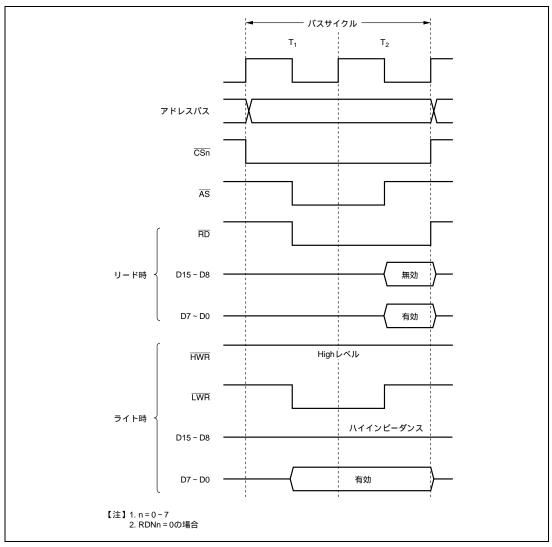

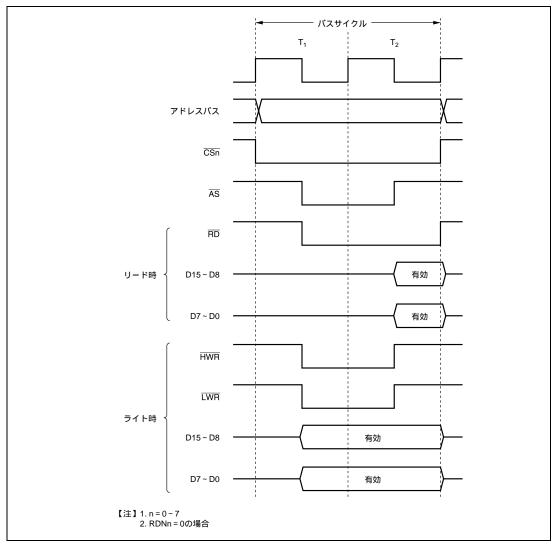

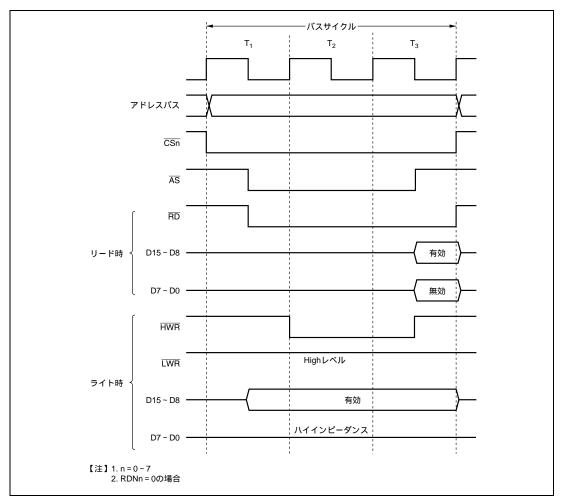

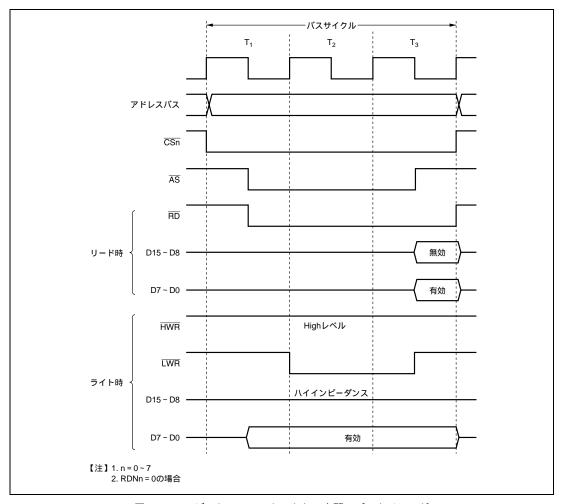

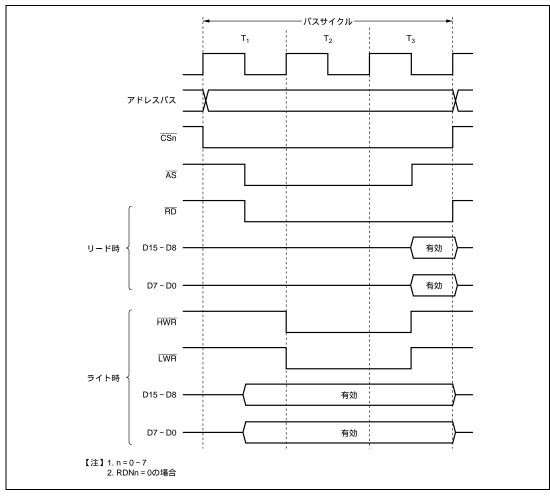

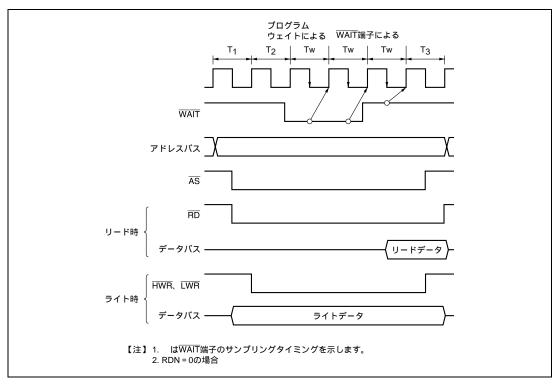

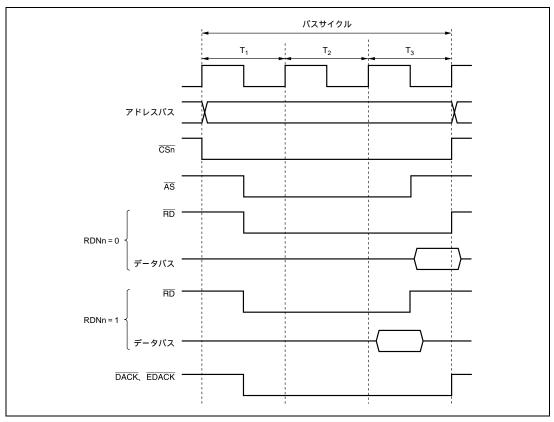

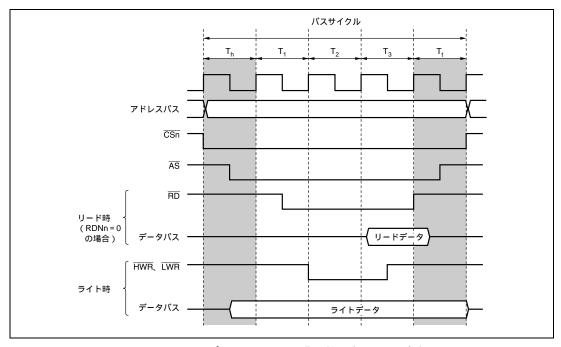

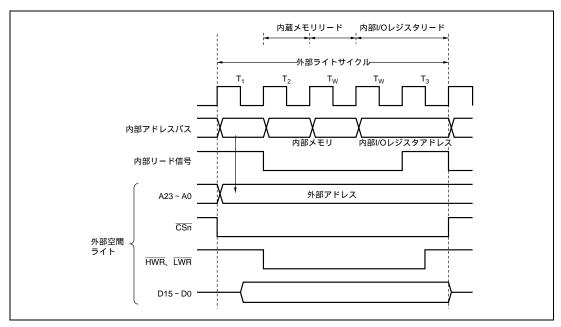

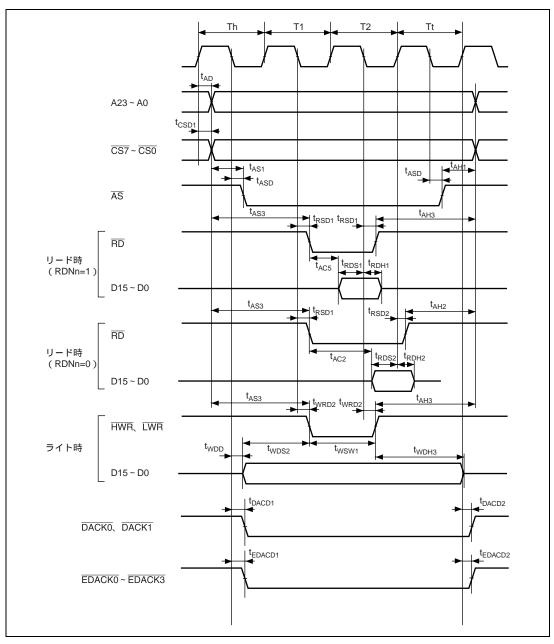

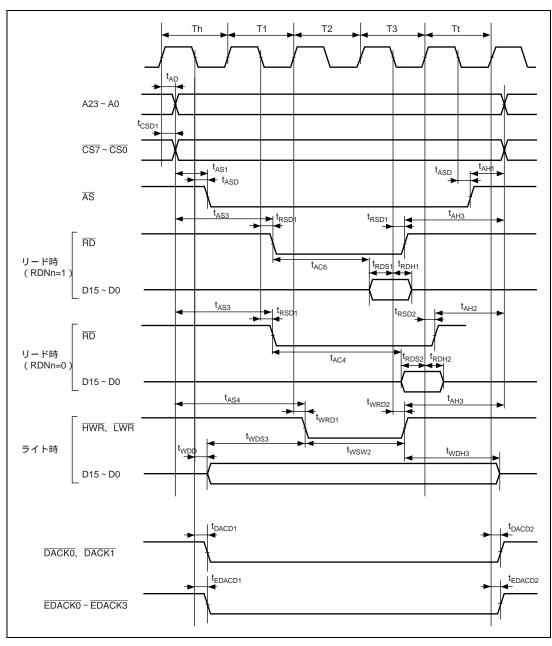

| 6.5.3  | 基本動作タイミング                                    | 6-33 |

| 6.5.4  | ウェイト制御                                       | 6-41 |

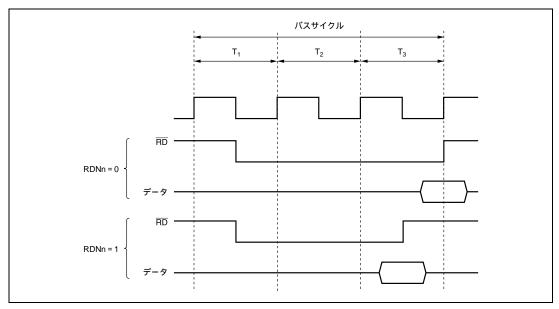

| 6.5.5  | リードストローブ ( RD ) タイミング                        | 6-42 |

| 6.5.6  | チップセレクト ( CS ) アサート期間拡張                      | 6-43 |

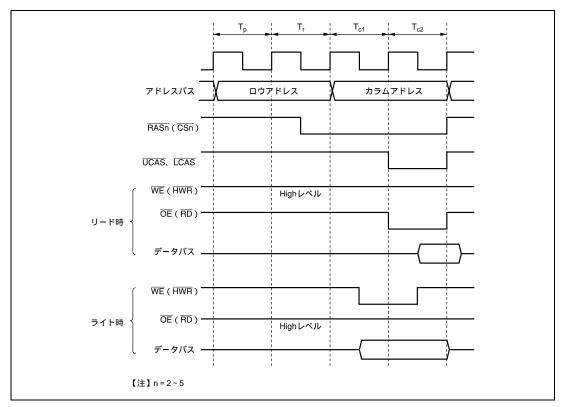

| 6.6    | DRAMインタフェース                                  | 6-44 |

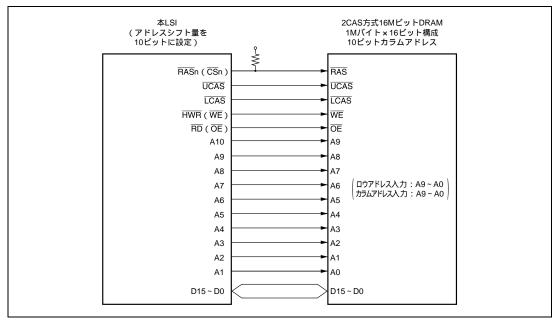

| 6.6.1  | DRAM 空間の設定                                   | 6-44 |

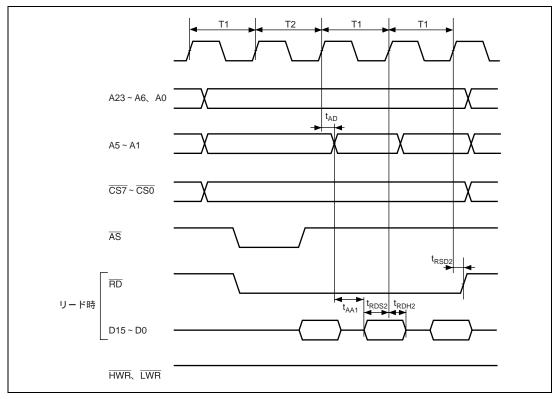

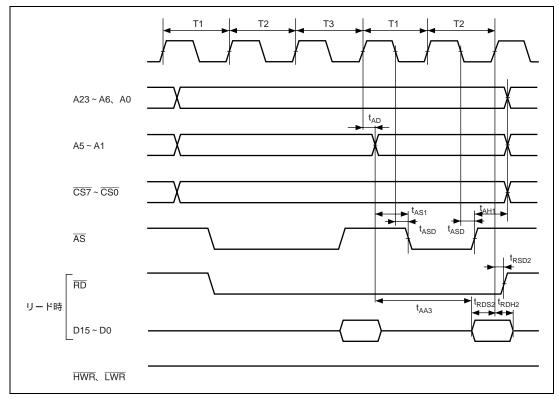

| 6.6.2  | アドレスマルチプレクス                                  | 6-44 |

| 6.6.3  | データバス                                        |      |

| 6.6.4  | DRAM インタフェース使用端子                             |      |

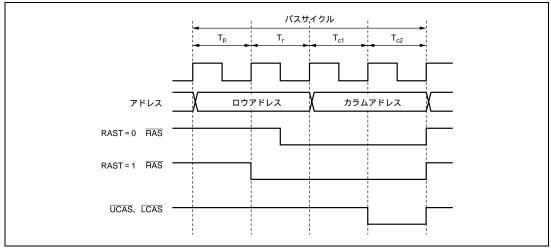

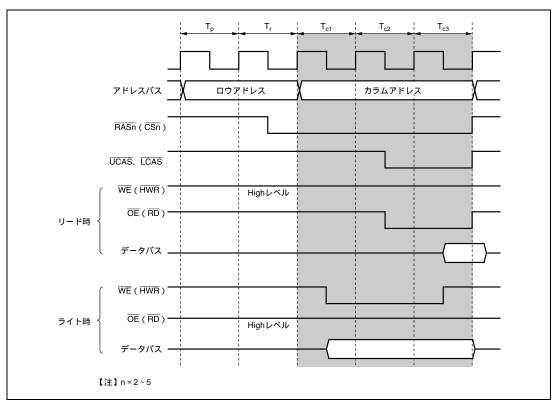

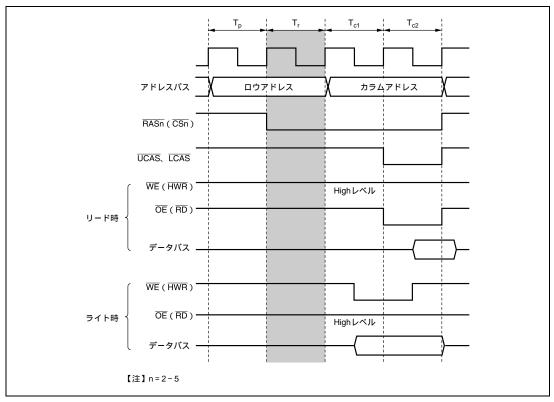

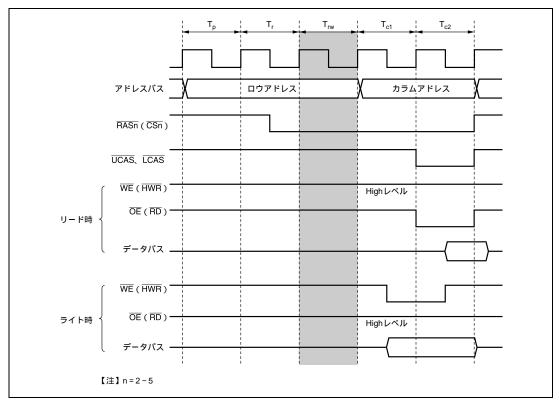

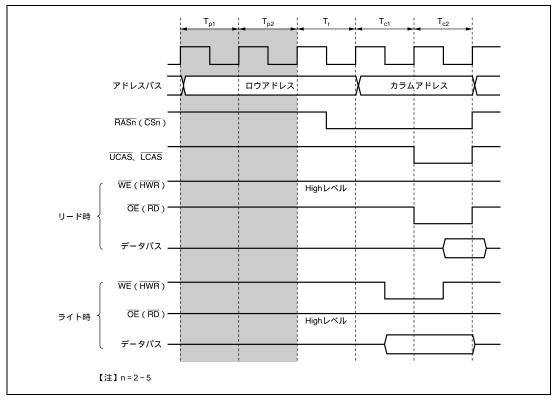

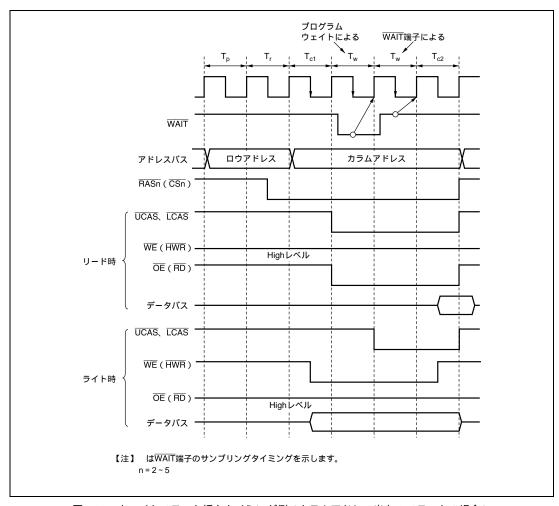

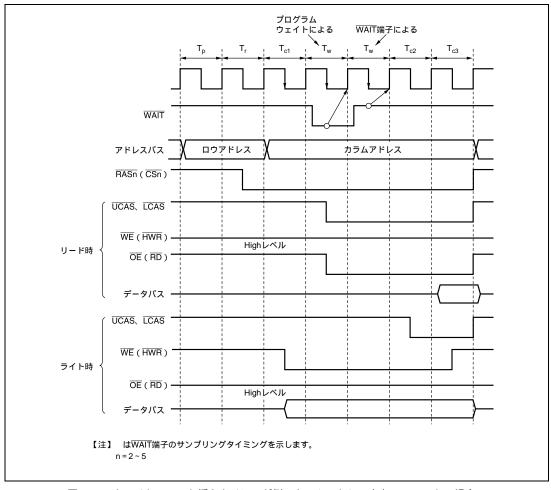

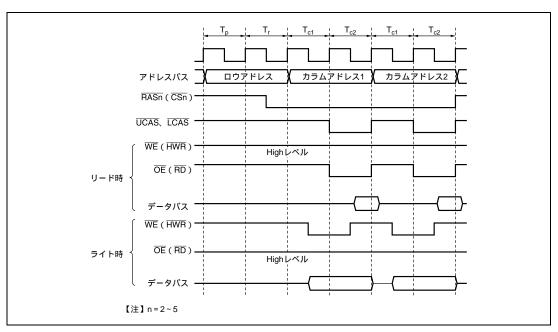

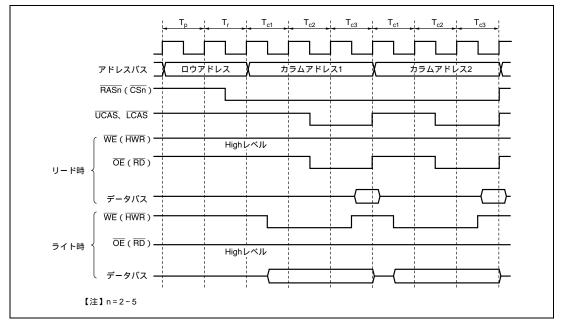

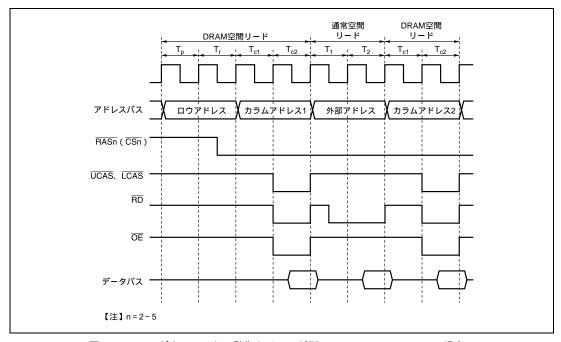

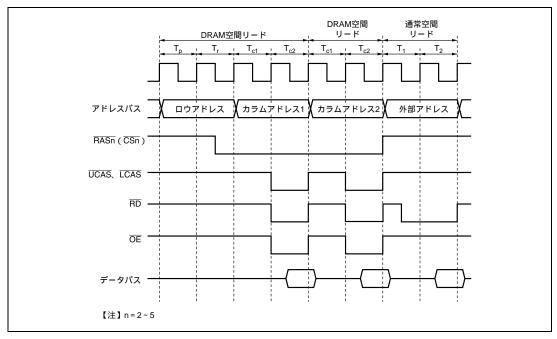

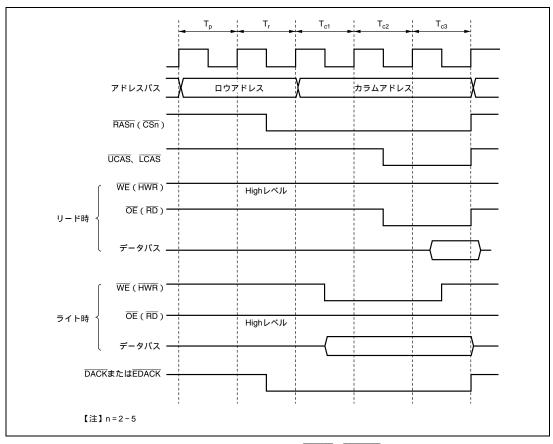

| 6.6.5  | 基本動作タイミング                                    |      |

| 6.6.6  | カラムアドレス出力サイクル制御                              |      |

| 6.6.7  | ロウアドレス出力ステート制御                               |      |

| 6.6.8  | プリチャージステート制御                                 |      |

| 6.6.9  | ウェイト制御                                       | 6-50 |

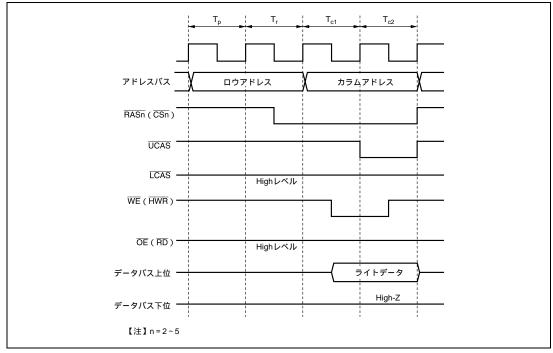

| 6.6.10 | バイトアクセス制御                                    |      |

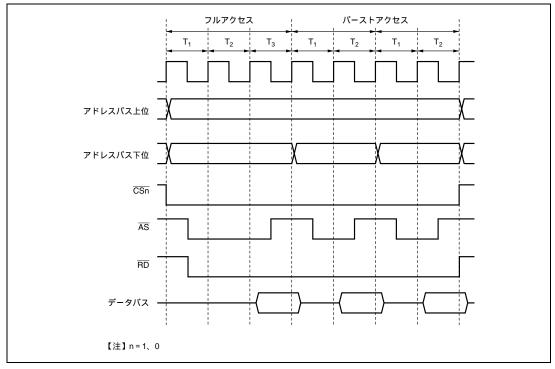

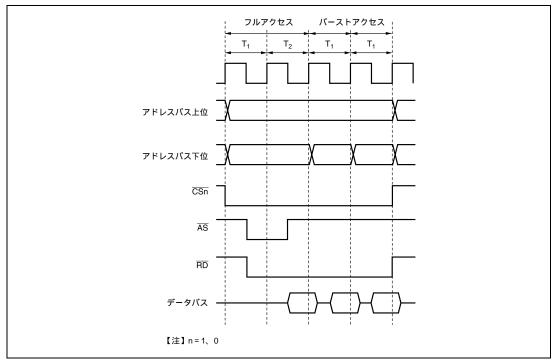

| 6.6.11 | バースト動作                                       |      |

| 6.6.12 | リフレッシュ制御                                     |      |

| 6.6.13 | DMAC および EXDMAC のシングルアドレス転送モードと DRAM インタフェース |      |

| 6.7    | シンクロナスDRAMインタフェース                            |      |

|        | 連続シンクロナス DRAM 空間の設定                          |      |

| 6.7.1  |                                              |      |

| 6.7.2  | アドレスマルチプレクス                                  | 0-06 |

| 6.7.3  | データバス                                                  | 6-66  |

|--------|--------------------------------------------------------|-------|

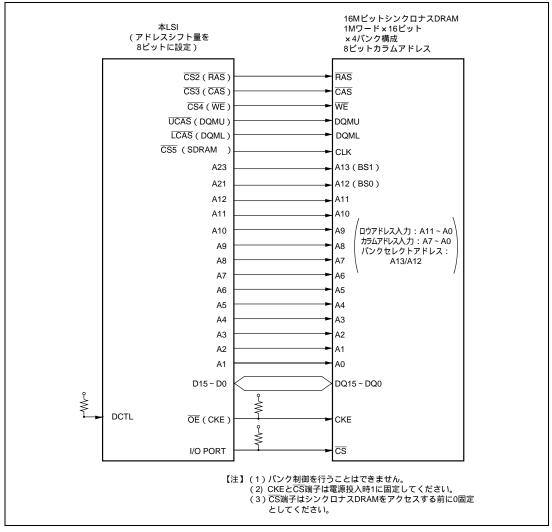

| 6.7.4  | シンクロナス DRAM インタフェース使用端子                                | 6-67  |

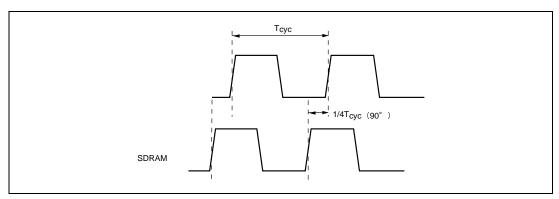

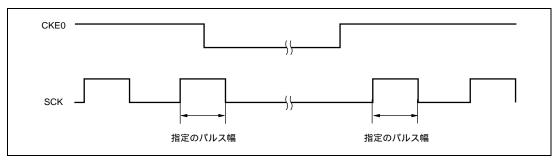

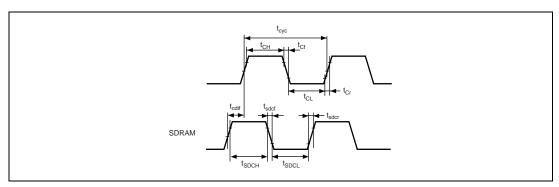

| 6.7.5  | シンクロナス DRAM 専用クロック                                     | 6-68  |

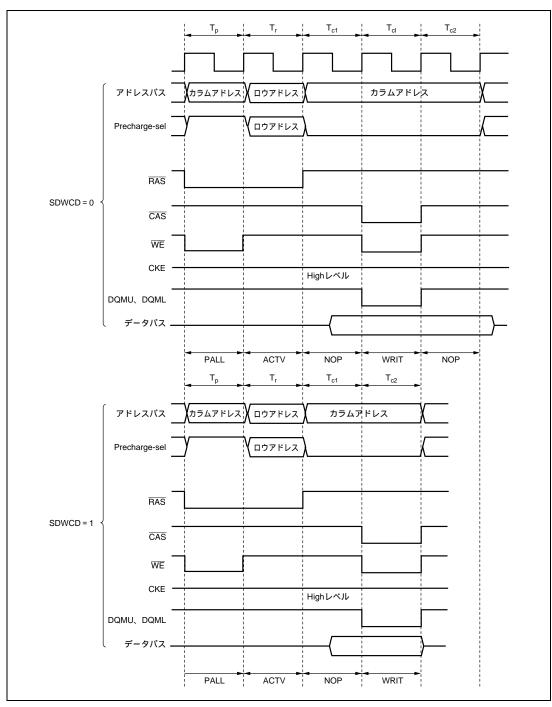

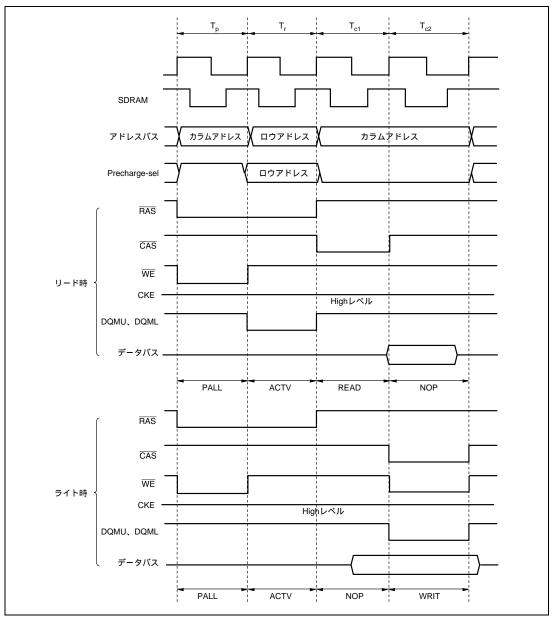

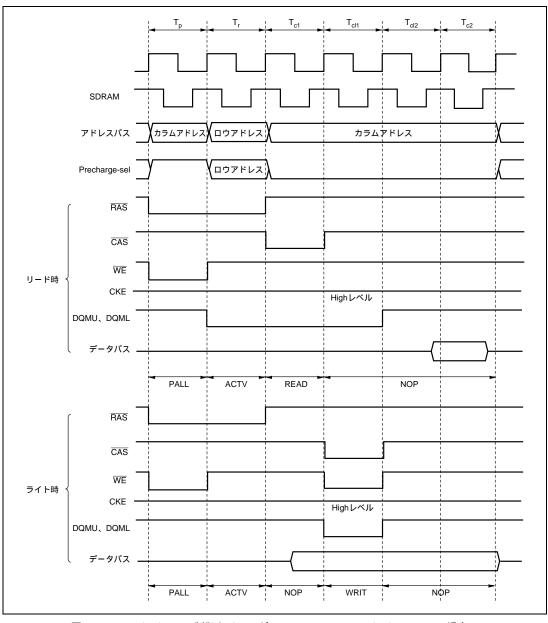

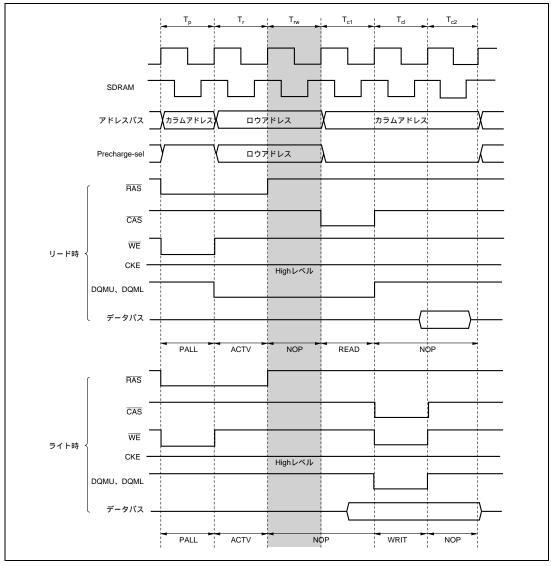

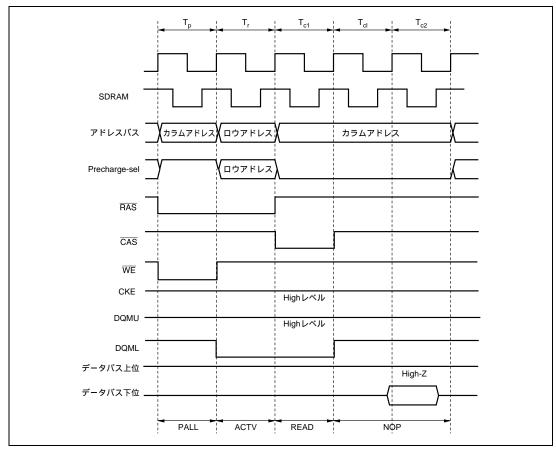

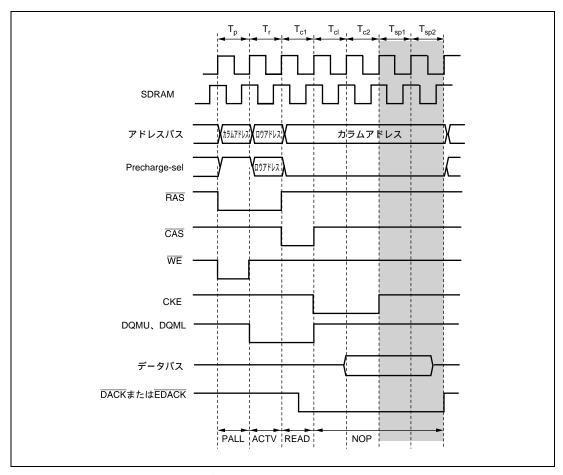

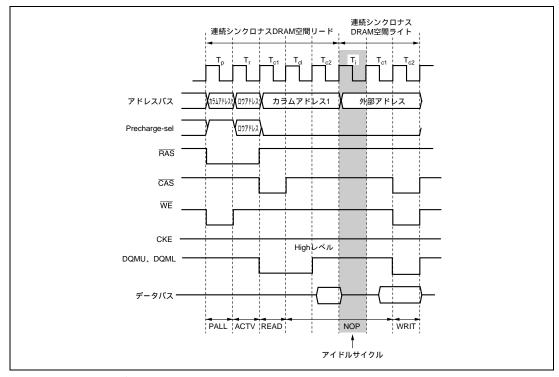

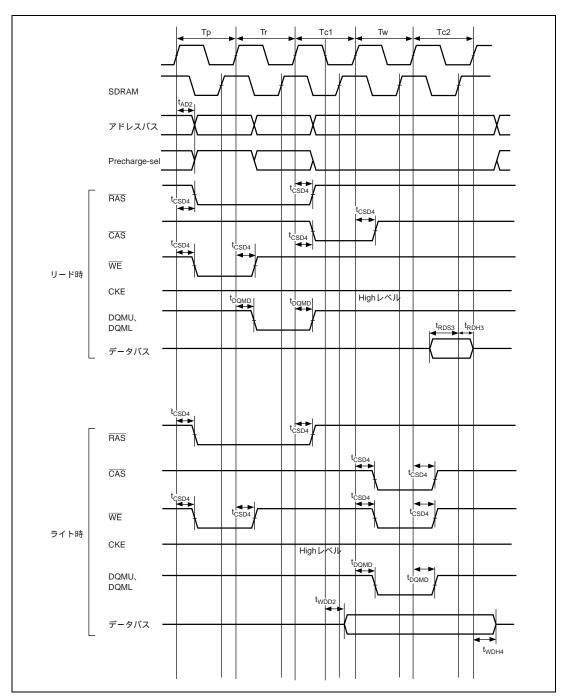

| 6.7.6  | 基本動作タイミング                                              | 6-68  |

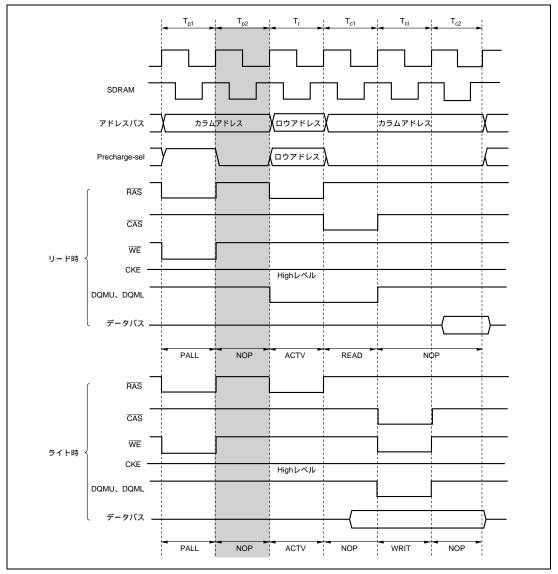

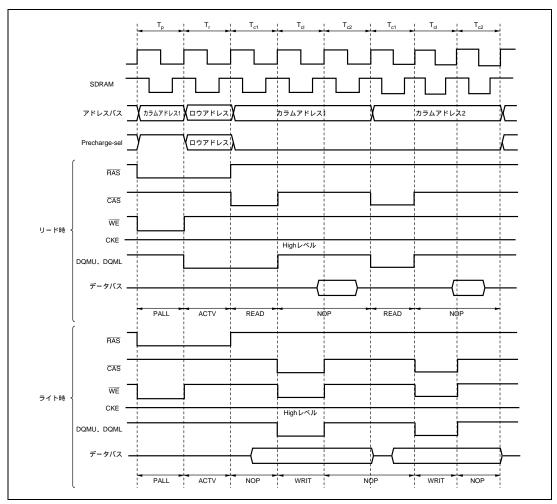

| 6.7.7  | CAS レイテンシ制御                                            | 6-70  |

| 6.7.8  | ロウアドレス出力ステート制御                                         | 6-72  |

| 6.7.9  | プリチャージステート数                                            | 6-73  |

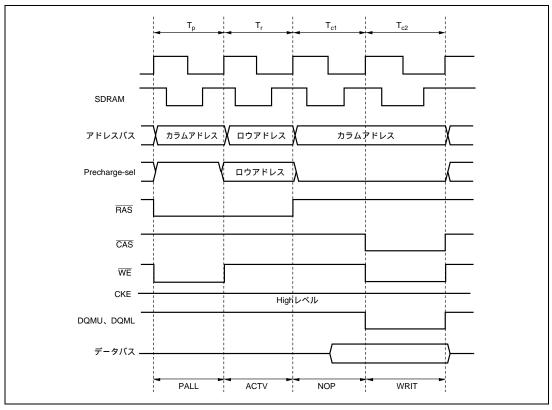

| 6.7.10 | ライトサイクル時のバスサイクル制御                                      | 6-74  |

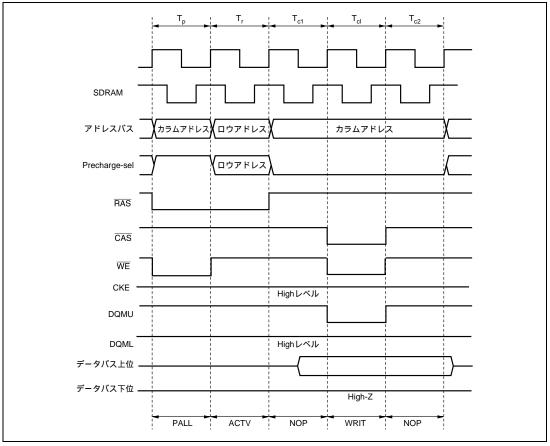

| 6.7.11 | バイトアクセス制御                                              | 6-75  |

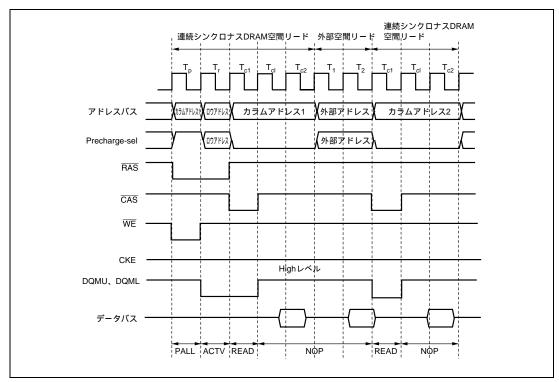

| 6.7.12 | パースト動作                                                 | 6-77  |

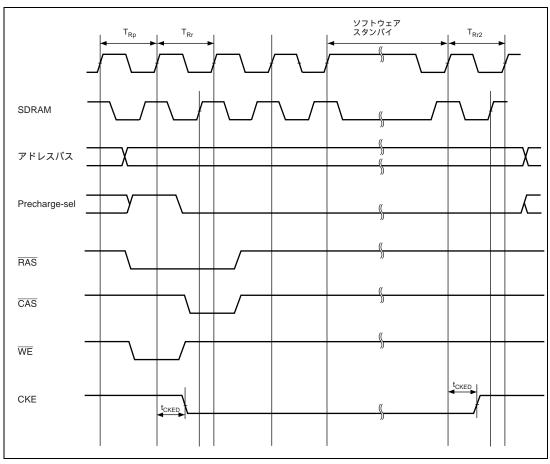

| 6.7.13 | リフレッシュ制御                                               | 6-80  |

| 6.7.14 | シンクロナス DRAM のモードレジスタ設定                                 | 6-85  |

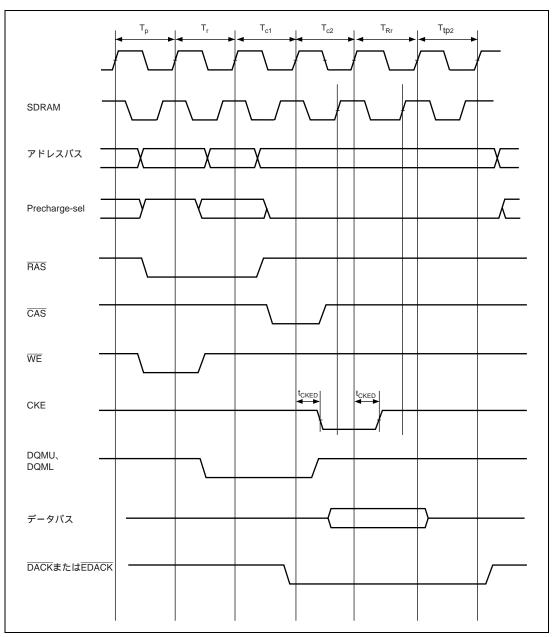

| 6.7.15 | DMAC および EXDMAC のシングルアドレス転送モードと<br>シンクロナス DRAM インタフェース | 6-86  |

| 6.8    | バーストROMインタフェース                                         | 6-90  |

| 6.8.1  | 基本タイミング                                                |       |

| 6.8.2  | ウェイト制御                                                 | 6-92  |

| 6.8.3  | ライトアクセス                                                | 6-92  |

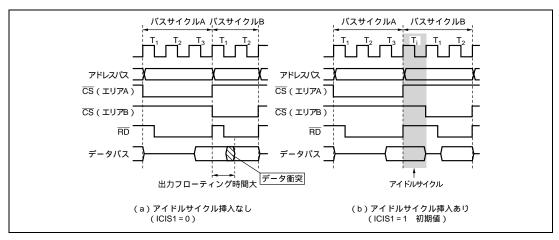

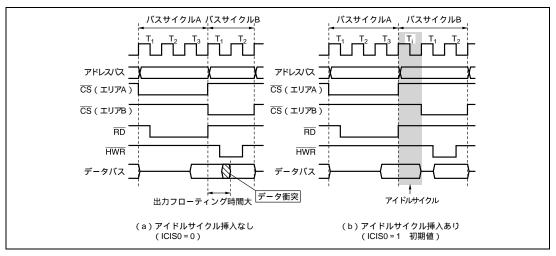

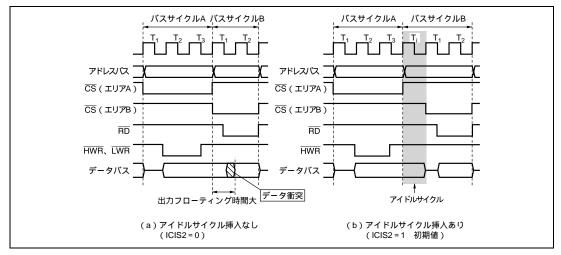

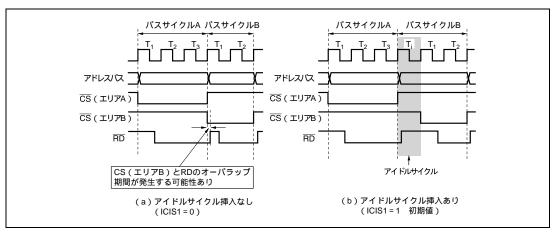

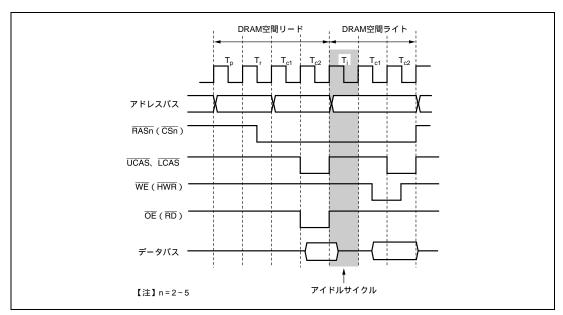

| 6.9    | アイドルサイクル                                               | 6-93  |

| 6.9.1  | 動作説明                                                   | 6-93  |

| 6.9.2  | アイドルサイクルでの端子状態                                         | 6-108 |

| 6.10   | ライトデータバッファ機能                                           | 6-109 |

| 6.11   | バス権解放                                                  | 6-110 |

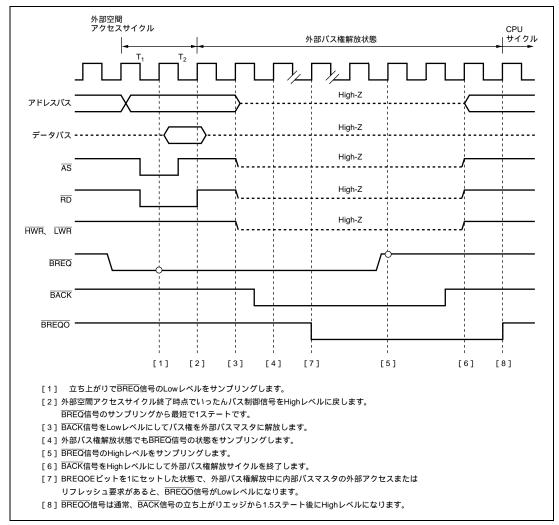

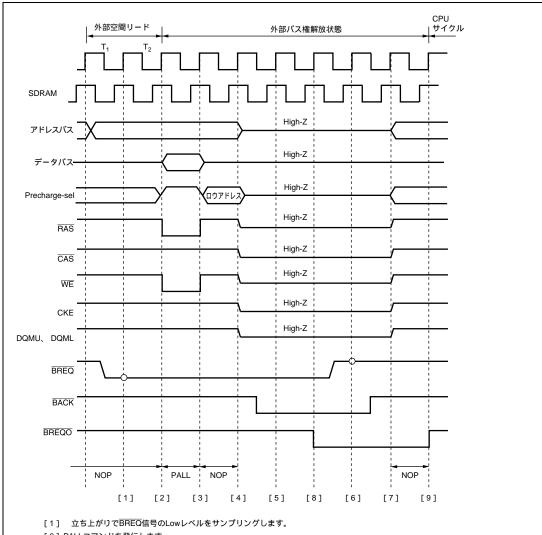

| 6.11.1 | 動作説明                                                   | 6-110 |

| 6.11.2 | 外部バス権解放状態での端子状態                                        | 6-111 |

| 6.11.3 | 遷移タイミング                                                | 6-112 |

| 6.12   | バスアービトレーション                                            | 6-114 |

| 6.12.1 | 動作説明                                                   | 6-114 |

| 6.12.2 | バス権移行タイミング                                             | 6-114 |

| 6.13   | リセットとバスコントローラ                                          | 6-116 |

| 6.14   | 使用上の注意事項                                               | 6-116 |

| 6.14.1 |                                                        |       |

| 6.14.2 | 外部バス権解放機能とソフトウェアスタンバイ                                  |       |

| 6.14.3 | 外部バス権解放機能と CBR リフレッシュ/オートリフレッシュ                        |       |

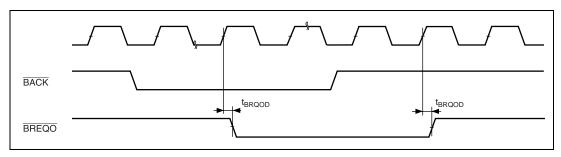

| 6.14.4 | BREQO 出力タイミング                                          |       |

| 6.14.5 | シンクロナス DRAM 使用上の注意                                     | 6-117 |

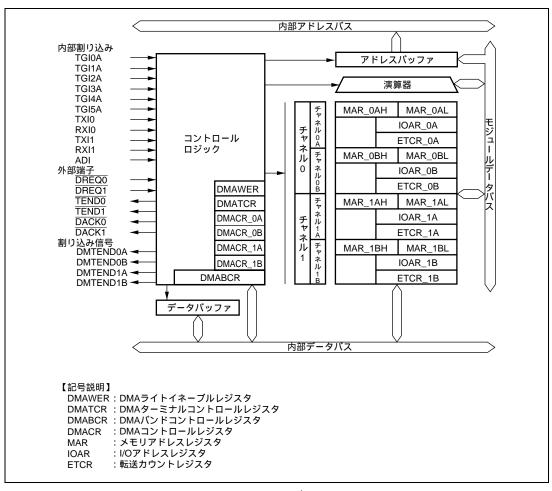

| 7. DM  | A コントローラ ( DMAC )                                      | 7-1   |

| 7.1    | 特長                                                     | 7-1   |

| 7.2    | 入出力端子                                                  | 7-3   |

| 7.3    | レジスタの説明                                                | 7-3   |

| 7.3.1  | メモリアドレスレジスタ(MARA、MARB)                 | 7-5  |

|--------|----------------------------------------|------|

| 7.3.2  | I/O アドレスレジスタ(IOARA、IOARB)              | 7-5  |

| 7.3.3  | 転送カウントレジスタ(ETCRA、ETCRB)                | 7-6  |

| 7.3.4  | DMA コントロールレジスタ(DMACRA、DMACRB)          | 7-6  |

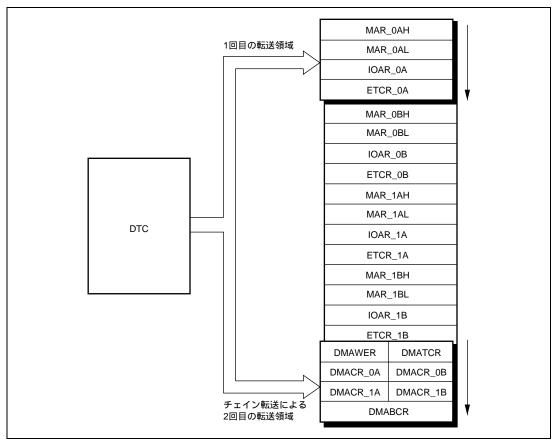

| 7.3.5  | DMA バンドコントロールレジスタ H、L(DMABCRH、DMABCRL) | 7-12 |

| 7.3.6  | DMA ライトイネーブルレジスタ ( DMAWER )            | 7-18 |

| 7.3.7  | DMA ターミナルコントロールレジスタ(DMATCR)            | 7-20 |

| 7.4    | 起動要因                                   | 7-21 |

| 7.4.1  | 内部割り込み要求による起動                          | 7-21 |

| 7.4.2  | 外部リクエストによる起動                           | 7-22 |

| 7.4.3  | オートリクエストによる起動                          | 7-22 |

| 7.5    | 動作説明                                   | 7-23 |

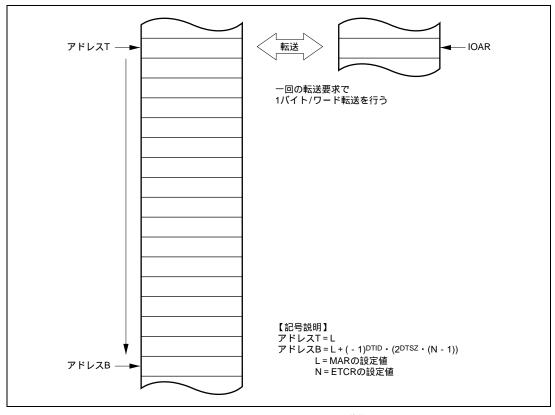

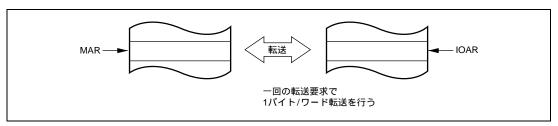

| 7.5.1  | 転送モード                                  | 7-23 |

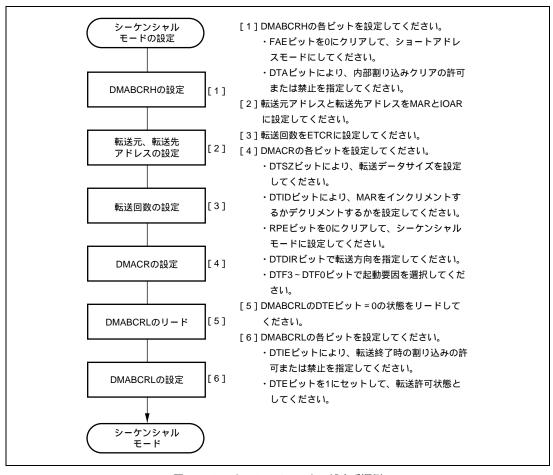

| 7.5.2  | シーケンシャルモード                             | 7-24 |

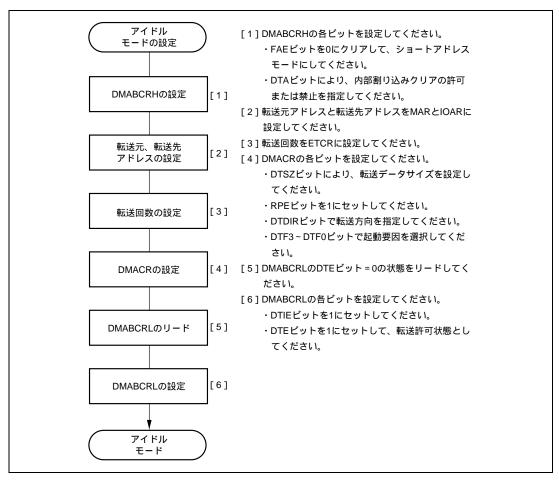

| 7.5.3  | アイドルモード                                | 7-27 |

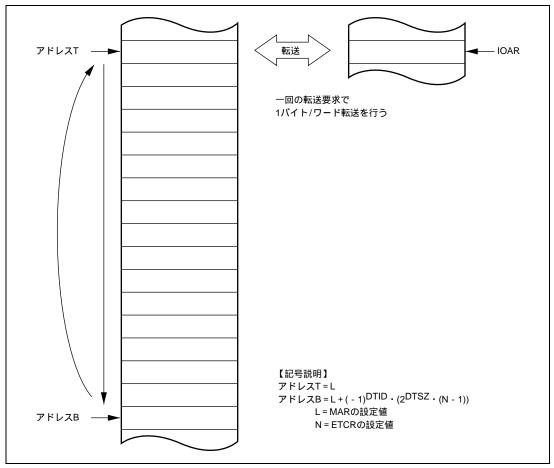

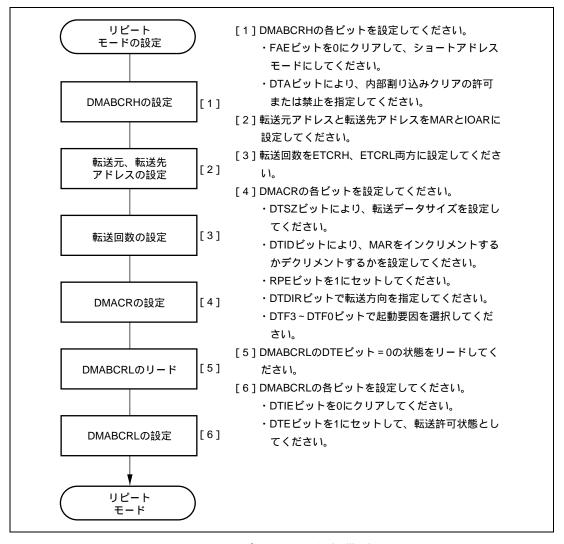

| 7.5.4  | リピートモード                                | 7-29 |

| 7.5.5  | シングルアドレスモード                            | 7-32 |

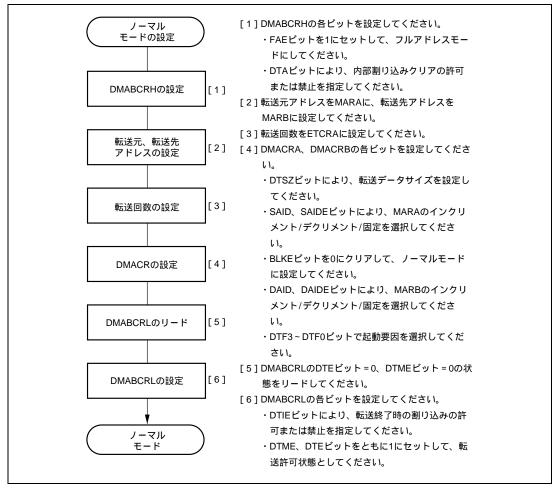

| 7.5.6  | ノーマルモード                                | 7-35 |

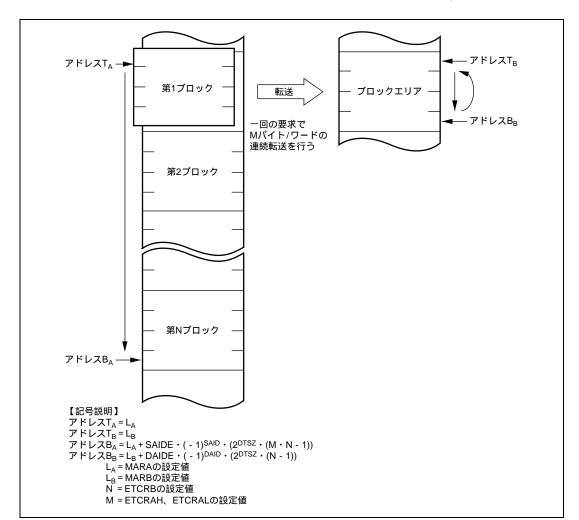

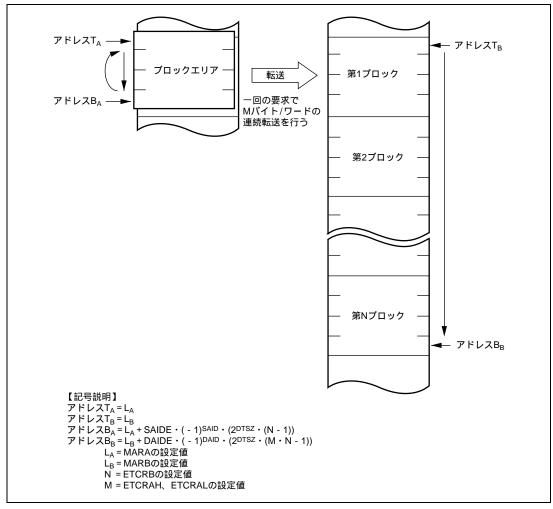

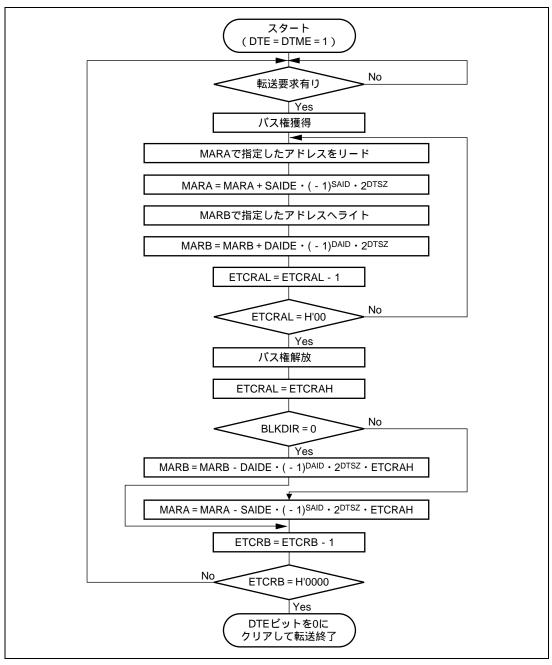

| 7.5.7  | ブロック転送モード                              | 7-38 |

| 7.5.8  | 基本バスサイクル                               | 7-43 |

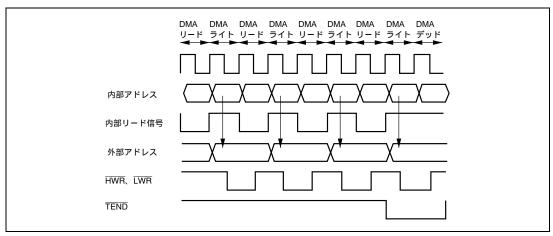

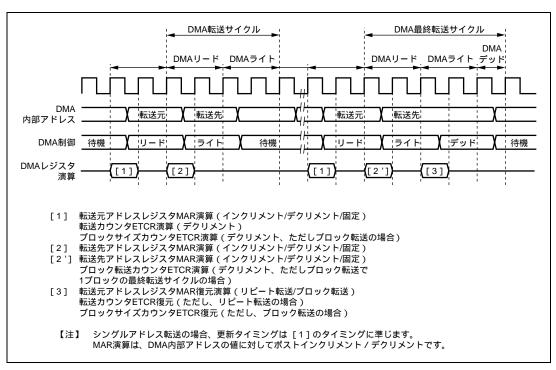

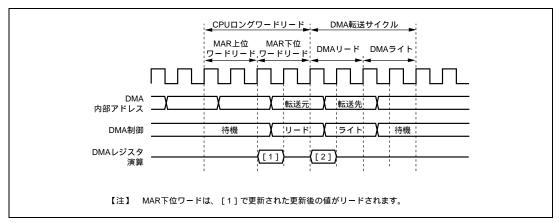

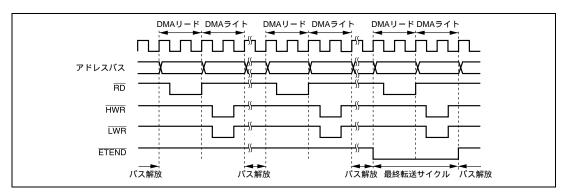

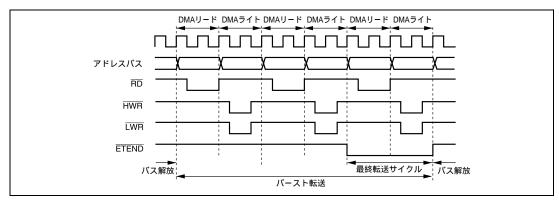

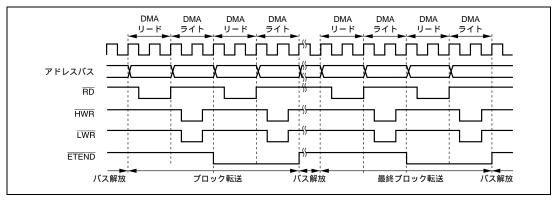

| 7.5.9  | DMA 転送 ( デュアルアドレスモード ) のバスサイクル         | 7-43 |

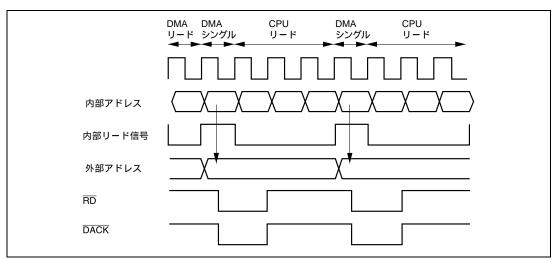

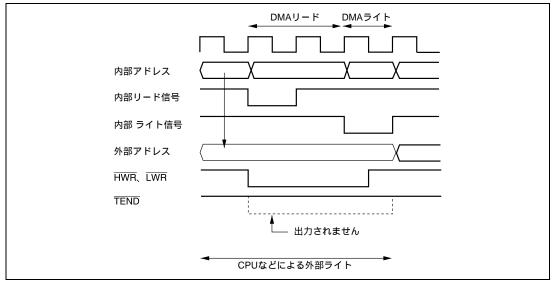

| 7.5.10 | DMA 転送 ( シングルアドレスモード ) のバスサイクル         | 7-50 |

| 7.5.11 | ライトデータバッファ機能                           | 7-53 |

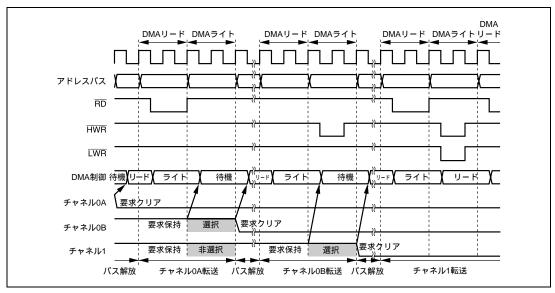

| 7.5.12 | 複数チャネルの動作                              | 7-55 |

| 7.5.13 | DMAC と外部バス権要求、リフレッシュサイクル、EXDMAC        | 7-56 |

| 7.5.14 | DMAC と NMI 割り込み                        | 7-56 |

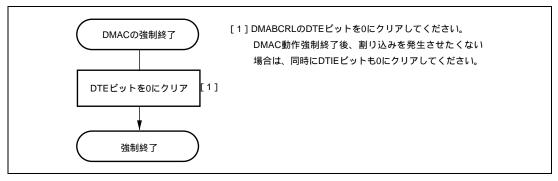

| 7.5.15 | DMAC の強制終了                             | 7-57 |

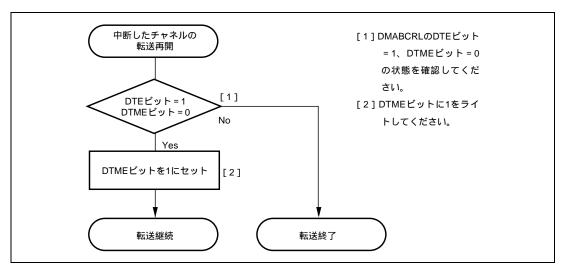

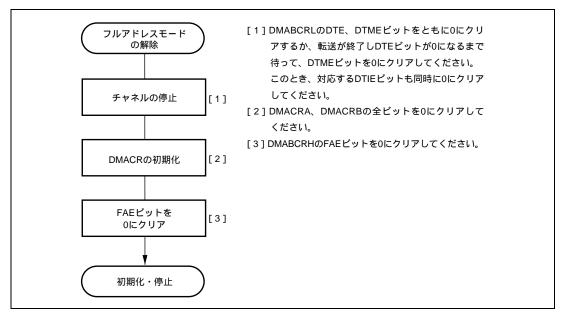

| 7.5.16 | フルアドレスモードの解除                           | 7-57 |

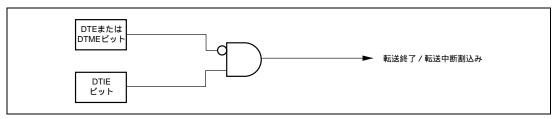

| 7.6    | 割り込み要因                                 | 7-59 |

| 7.7    | 使用上の注意事項                               | 7-60 |

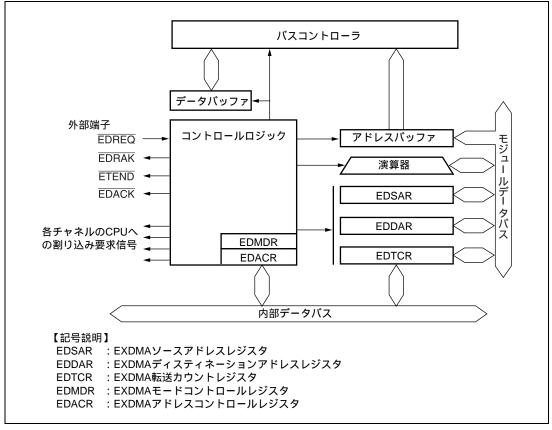

| 8. EXI | OMA コントローラ(EXDMAC)                     | 0.1  |

|        |                                        |      |

| 8.1    | 特長                                     |      |

| 8.2    | 入出力端子                                  |      |

| 8.3    | レジスタの説明                                |      |

| 8.3.1  | EXDMA ソースアドレスレジスタ(EDSAR)               |      |

| 8.3.2  | EXDMA ディスティネーションアドレスレジスタ(EDDAR)        |      |

| 8.3.3  | EXDMA 転送カウントレジスタ ( EDTCR )             |      |

| 8.3.4  | EXDMA モードコントロールレジスタ(EDMDR)             |      |

| 8.3.5  | EXDMA アドレスコントロールレジスタ ( EDACR )         | 8-9  |

| 8.4    | 動作説明                                 | 8-12 |

|--------|--------------------------------------|------|

| 8.4.1  | 転送モード                                | 8-12 |

| 8.4.2  | アドレスモード                              | 8-13 |

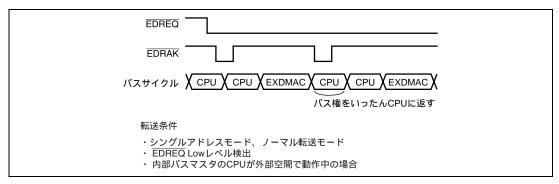

| 8.4.3  | DMA 転送要求                             | 8-15 |

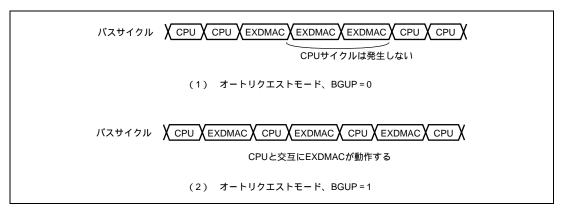

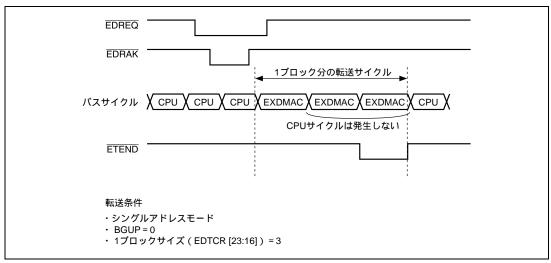

| 8.4.4  | バスモード                                | 8-16 |

| 8.4.5  | 転送モード                                | 8-18 |

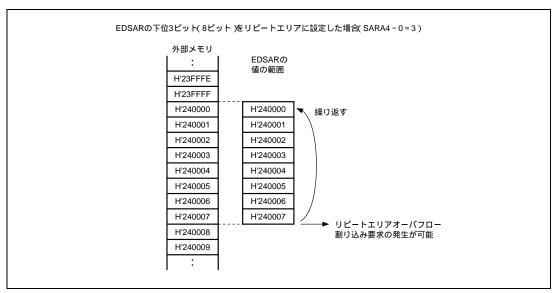

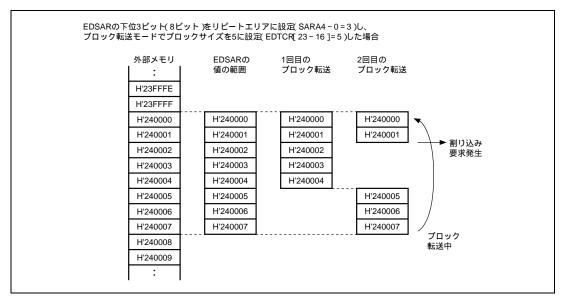

| 8.4.6  | リピートエリア機能                            | 8-20 |

| 8.4.7  | DMA 転送動作中のレジスタ                       | 8-21 |

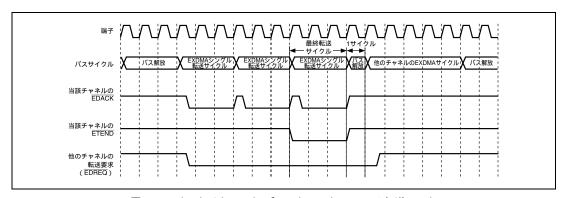

| 8.4.8  | チャネルの優先順位                            | 8-25 |

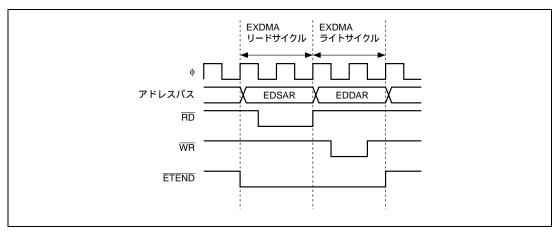

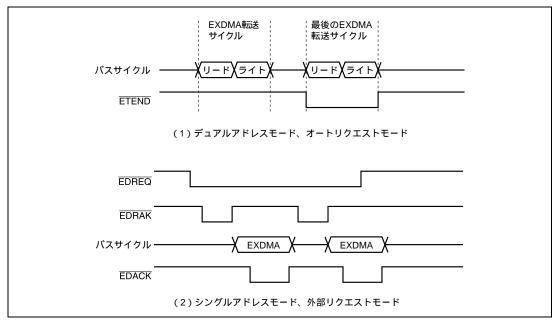

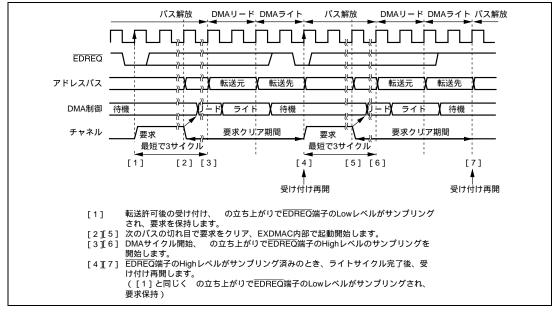

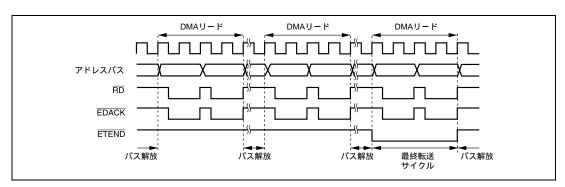

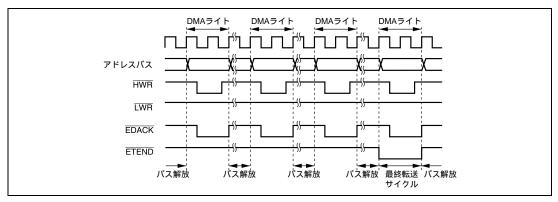

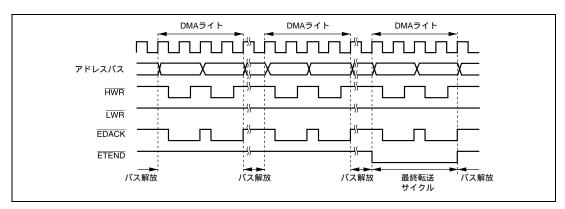

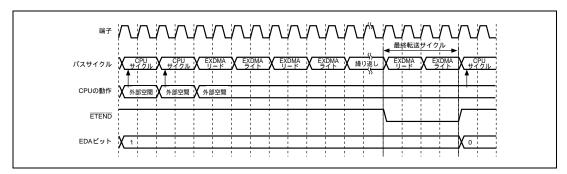

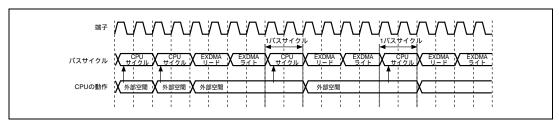

| 8.4.9  | EXDMAC 転送(デュアルアドレスモード)のバスサイクル        | 8-27 |

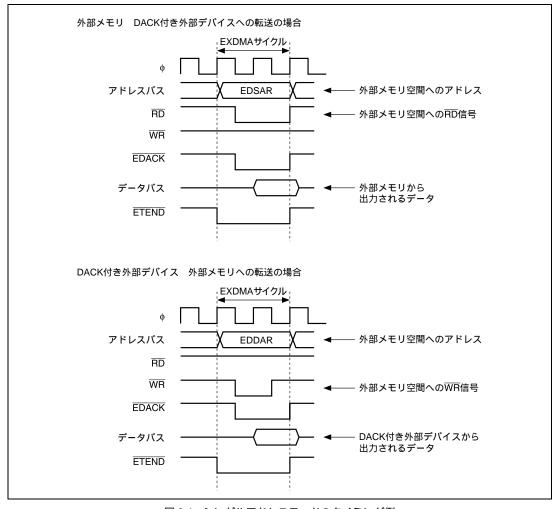

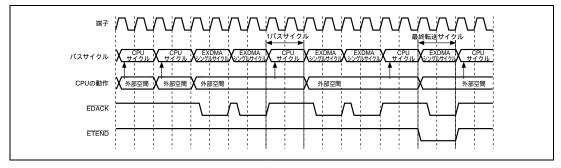

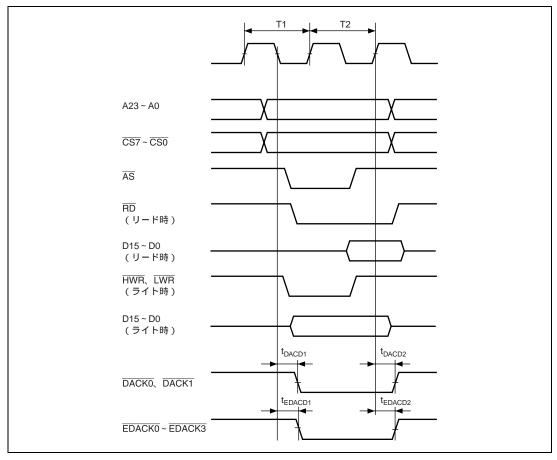

| 8.4.10 | EXDMAC 転送 ( シングルアドレスモード ) のバスタイミング   | 8-33 |

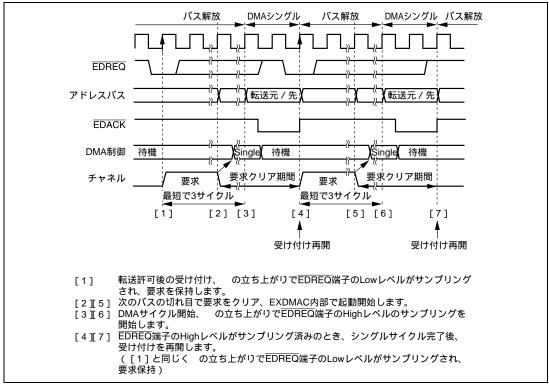

| 8.4.11 | 各モードの動作タイミング                         | 8-37 |

| 8.4.12 | DMA 転送終了                             | 8-48 |

| 8.4.13 | EXDMAC と他のバスマスタ                      | 8-49 |

| 8.5    | 割り込み要因                               | 8-50 |

| 8.6    | 使用上の注意事項                             | 8-52 |

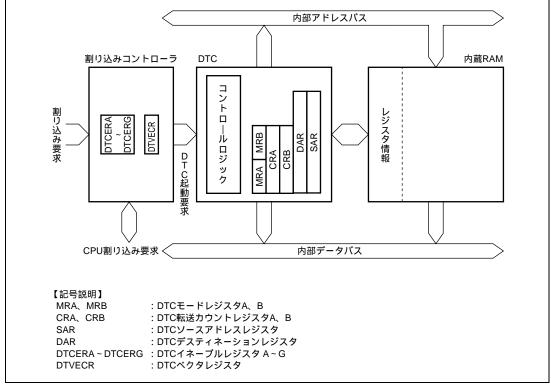

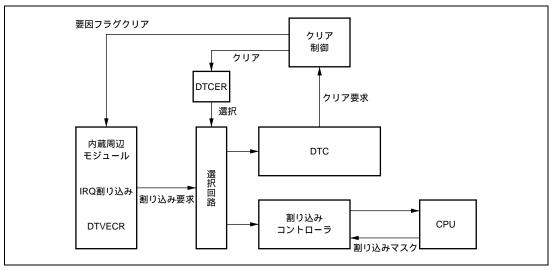

| 9. デー  | - タトランスファコントローラ(DTC)                 | 9-1  |

| 9.1    | 特長                                   | 9-1  |

| 9.2    | レジスタの説明                              | 9-2  |

| 9.2.1  | DTC モードレジスタ A ( MRA )                | 9-3  |

| 9.2.2  | DTC モードレジスタ B ( MRB )                | 9-4  |

| 9.2.3  | DTC ソースアドレスレジスタ ( SAR )              | 9-4  |

| 9.2.4  | DTC デスティネーションアドレスレジスタ ( DAR )        | 9-4  |

| 9.2.5  | DTC 転送カウントレジスタ A(CRA)                | 9-5  |

| 9.2.6  | DTC 転送カウントレジスタ B(CRB)                | 9-5  |

| 9.2.7  | DTC イネーブルレジスタ A~G ( DTCERA~ DTCERG ) | 9-5  |

| 9.2.8  | DTC ベクタレジスタ ( DTVECR )               | 9-6  |

| 9.3    | 起動要因                                 | 9-7  |

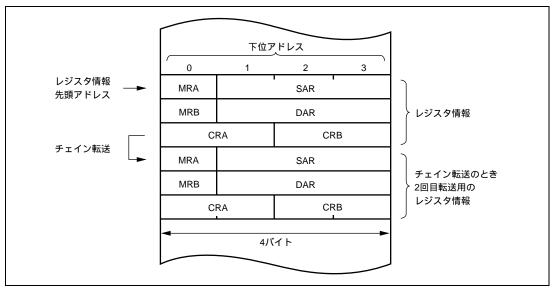

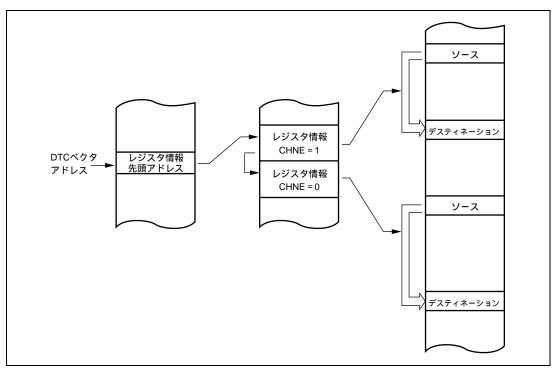

| 9.4    | レジスタ情報の配置とDTCベクタテーブル                 | 9-8  |

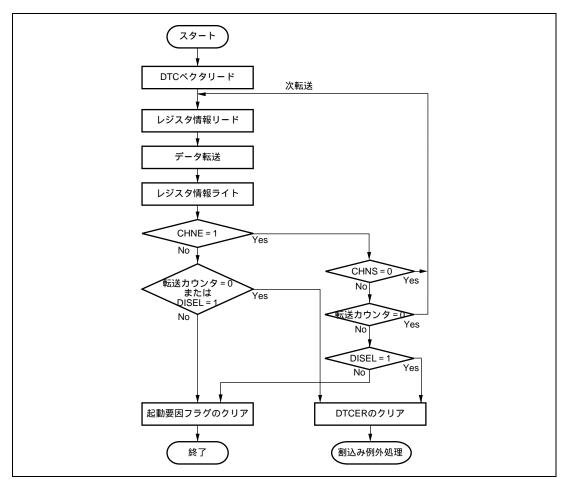

| 9.5    | 動作説明                                 | 9-11 |

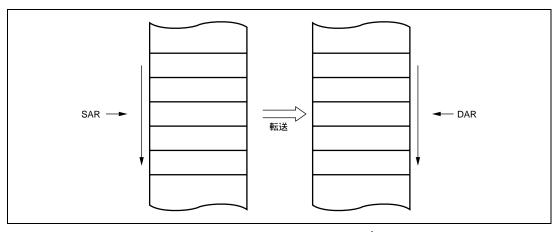

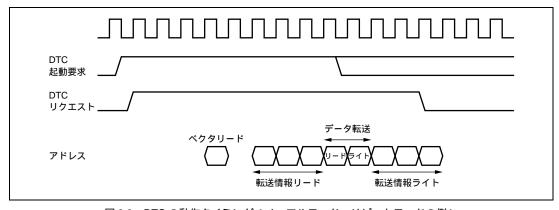

| 9.5.1  | ノーマルモード                              | 9-13 |

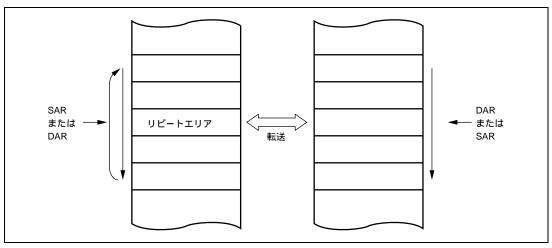

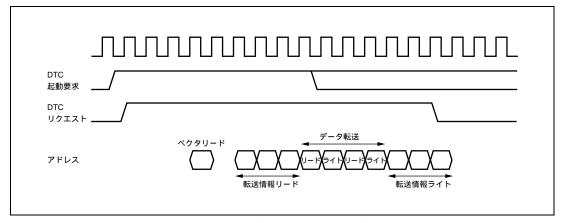

| 9.5.2  | リピートモード                              |      |

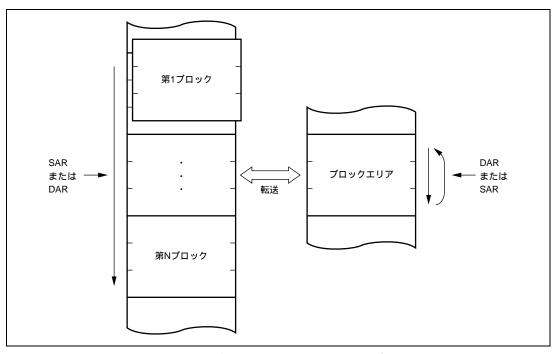

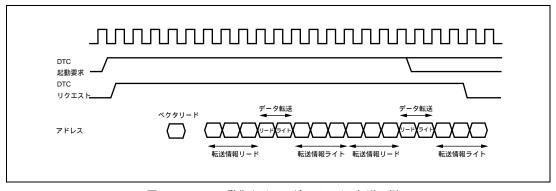

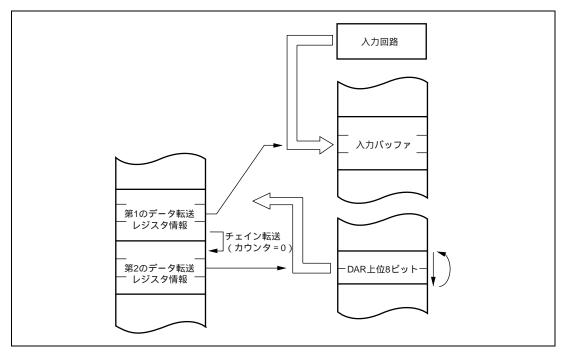

| 9.5.3  | プロック転送モード                            | 9-15 |

| 9.5.4  | チェイン転送                               | 9-16 |

| 9.5.5  | 割り込み要因                               | 9-17 |

| 9.5.6  | 動作タイミング                              |      |

| 9.5.7  | DTC 実行ステート数                          |      |

| 9.6    | DTC使用手順                              |      |

| 9.6.1  | 割り込みによる起動                            | 9-20 |

|        |                                      |      |

| 9.6.2   | ソフトウェアによる起動                     | 9-20  |

|---------|---------------------------------|-------|

| 9.7     | DTC使用例                          | 9-21  |

| 9.7.1   | ノーマルモード                         | 9-21  |

| 9.7.2   | チェイン転送                          | 9-21  |

| 9.7.3   | 転送カウンタ=0 のときのチェイン転送             | 9-22  |

| 9.7.4   | ソフトウェア起動                        | 9-23  |

| 9.8     | 使用上の注意事項                        | 9-24  |

| 9.8.1   | モジュールストップモードの設定                 | 9-24  |

| 9.8.2   | 内蔵 RAM                          | 9-24  |

| 9.8.3   | DTCE ビットの設定                     | 9-24  |

| 10. I/O | ポート                             | 10-1  |

| 10.1    | ポート1                            | 10-6  |

| 10.1.1  | ポート 1 データディレクションレジスタ(PIDDR)     | 10-6  |

| 10.1.2  | ポート 1 データレジスタ(PIDR)             | 10-6  |

| 10.1.3  | ポート 1 レジスタ ( PORT1 )            | 10-7  |

| 10.1.4  | 端子機能                            | 10-8  |

| 10.2    | ポート2                            | 10-16 |

| 10.2.1  | ポート 2 データディレクションレジスタ(P2DDR)     | 10-16 |

| 10.2.2  | ポート 2 データレジスタ(P2DR)             | 10-16 |

| 10.2.3  | ポート 2 レジスタ(PORT2)               | 10-17 |

| 10.2.4  | 端子機能                            | 10-18 |

| 10.3    | ポート3                            | 10-26 |

| 10.3.1  | ポート 3 データディレクションレジスタ(P3DDR)     | 10-26 |

| 10.3.2  | ポート 3 データレジスタ(P3DR)             | 10-26 |

| 10.3.3  | ポート 3 レジスタ(PORT3)               | 10-27 |

| 10.3.4  | ポート 3 オープンドレインコントロールレジスタ(P3ODR) | 10-27 |

| 10.3.5  | ポートファンクションコントロールレジスタ 2(PFCR2)   | 10-28 |

| 10.3.6  | 端子機能                            | 10-29 |

| 10.4    | ポート4                            | 10-32 |

| 10.4.1  | ポート 4 レジスタ ( PORT4 )            | 10-32 |

| 10.4.2  | 端子機能                            | 10-32 |

| 10.5    | ポート5                            | 10-33 |

| 10.5.1  | ポート 5 データディレクションレジスタ(P5DDR)     | 10-33 |

| 10.5.2  | ポート 5 データレジスタ(P5DR)             | 10-34 |

| 10.5.3  | ポート 5 レジスタ(PORT5)               | 10-34 |

| 10.5.4  | 端子機能                            | 10-34 |

| 10.6    | ポート6                            | 10-37 |

| 10.6.1  | ポート 6 データディレクションレジスタ(P6DDR)     | 10-37 |

| 10.6.2  | ポート 6 データレジスタ(P6DR)             | 10-37 |

| 10.6.3  |    | ポート 6 レジスタ(PORT6)                    | 10-38 |

|---------|----|--------------------------------------|-------|

| 10.6.4  |    | 端子機能                                 | 10-38 |

| 10.7    | ポ- | <b>- \</b> -7                        | 10-41 |

| 10.7.1  |    | ポート 7 データディレクションレジスタ(P7DDR)          | 10-41 |

| 10.7.2  |    | ポート 7 データレジスタ(P7DR)                  | 10-41 |

| 10.7.3  |    | ポート7 レジスタ(PORT7)                     | 10-42 |

| 10.7.4  |    | 端子機能                                 | 10-42 |

| 10.8    | ポ- | - <b>\</b> -8                        | 10-45 |

| 10.8.1  |    | ポート 8 データディレクションレジスタ(P8DDR)          | 10-45 |

| 10.8.2  |    | ポート 8 データレジスタ(P8DR)                  | 10-45 |

| 10.8.3  |    | ポート 8 レジスタ(PORT8)                    | 10-46 |

| 10.8.4  |    | 端子機能                                 | 10-46 |

| 10.9    | ポ- | - FA                                 | 10-49 |

| 10.9.1  |    | ポート A データディレクションレジスタ(PADDR)          | 10-49 |

| 10.9.2  |    | ポート A データレジスタ(PADR)                  | 10-50 |

| 10.9.3  |    | ポート A レジスタ(PORTA)                    | 10-50 |

| 10.9.4  |    | ポート A プルアップ MOS コントロールレジスタ(PAPCR)    | 10-51 |

| 10.9.5  |    | ポート A オープンドレインコントロールレジスタ(PAODR)      | 10-51 |

| 10.9.6  |    | ポートファンクションコントロールレジスタ 1(PFCR1)        | 10-52 |

| 10.9.7  |    | 端子機能                                 | 10-53 |

| 10.9.8  |    | ポート A 入力プルアップ MOS の状態                | 10-53 |

| 10.10   | ポ- | - <b>h</b> B                         | 10-54 |

| 10.10.1 |    | ポート B データディレクションレジスタ ( PBDDR )       | 10-54 |

| 10.10.2 | 2  | ポート B データレジスタ ( PBDR )               | 10-54 |

| 10.10.3 | ;  | ポート B レジスタ ( PORTB )                 | 10-55 |

| 10.10.4 | ļ  | ポート B プルアップ MOS コントロールレジスタ ( PBPCR ) | 10-55 |

| 10.10.5 | i  | 端子機能                                 | 10-56 |

| 10.10.6 | Ó  | ポート B 入力プルアップ MOS の状態                | 10-56 |

| 10.11   | ポ- | - FC                                 | 10-57 |

| 10.11.1 |    | ポート C データディレクションレジスタ ( PCDDR )       | 10-57 |

| 10.11.2 | 2  | ポート C データレジスタ ( PCDR )               | 10-57 |

| 10.11.3 | 3  | ポート C レジスタ ( PORTC )                 |       |

| 10.11.4 | ļ  | ポート C プルアップ MOS コントロールレジスタ ( PCPCR ) | 10-58 |

| 10.11.5 | i  | 端子機能                                 | 10-59 |

| 10.11.6 | )  | ポート C 入力プルアップ MOS の状態                | 10-59 |

| 10.12   | ポ- | - FD                                 | 10-60 |

| 10.12.1 |    | ポート D データディレクションレジスタ ( PDDDR )       | 10-60 |

| 10.12.2 | 2  | ポート D データレジスタ ( PDDR )               | 10-60 |

| 10.12.3 | 3  | ポート D レジスタ ( PORTD )                 | 10-61 |

| 10.12.4 | ļ  | ポート D プルアップ MOS コントロールレジスタ ( PDPCR ) | 10-61 |

| 10.12.5 | i  | モード別端子機能                             | 10-62 |

| 10.12.6  | ポート D 入力プルアップ MOS の状態             | 10-62 |

|----------|-----------------------------------|-------|

| 10.13    | ポートE                              | 10-63 |

| 10.13.1  | ポート E データディレクションレジスタ(PEDDR)       | 10-63 |

| 10.13.2  | ポート E データレジスタ(PEDR)               | 10-64 |

| 10.13.3  | ポート E レジスタ(PORTE)                 | 10-64 |

| 10.13.4  | ポート E プルアップ MOS コントロールレジスタ(PEPCR) | 10-65 |

| 10.13.5  | 端子機能                              | 10-65 |

| 10.13.6  | ポート E 入力プルアップ MOS の状態             | 10-66 |

| 10.14    | ポートF                              | 10-67 |

| 10.14.1  | ポート F データディレクションレジスタ(PFDDR)       | 10-67 |

| 10.14.2  | ポート F データレジスタ(PFDR)               | 10-68 |

| 10.14.3  | ポートFレジスタ(PORTF)                   | 10-68 |

| 10.14.4  | 端子機能                              | 10-69 |

| 10.15    | ポートG                              | 10-72 |

| 10.15.1  | ポート G データディレクションレジスタ(PGDDR)       | 10-72 |

| 10.15.2  | ポート G データレジスタ(PGDR)               | 10-73 |

| 10.15.3  | ポート G レジスタ(PORTG)                 | 10-73 |

| 10.15.4  | ポートファンクションコントロールレジスタ 0(PFCR0)     | 10-74 |

| 10.15.5  | 端子機能                              | 10-74 |

| 10.16    | ポートH                              | 10-76 |

| 10.16.1  | ポート H データディレクションレジスタ(PHDDR)       | 10-76 |

| 10.16.2  | ポート H データレジスタ(PHDR)               | 10-77 |

| 10.16.3  | ポート H レジスタ(PORTH)                 | 10-77 |

| 10.16.4  | 端子機能                              | 10-78 |

|          |                                   |       |

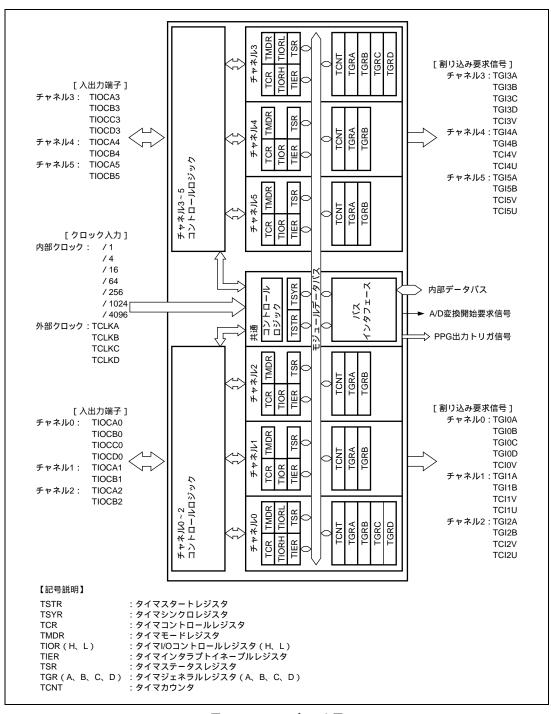

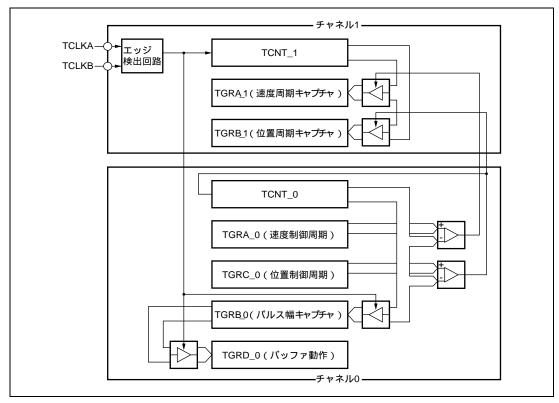

| 11. 16 t | ごットタイマパルスユニット(TPU)                | 11-1  |

| 11.1     | 特長                                | 11-1  |

| 11.2     | 入出力端子                             | 11-5  |

| 11.3     | レジスタの説明                           | 11-6  |

| 11.3.1   | タイマコントロールレジスタ(TCR)                | 11-8  |

| 11.3.2   | タイマモードレジスタ(TMDR)                  | 11-11 |

| 11.3.3   | タイマ I/O コントロールレジスタ(TIOR)          | 11-12 |

| 11.3.4   | タイマインタラプトイネーブルレジスタ(TIER)          | 11-29 |

| 11.3.5   | タイマステータスレジスタ ( TSR )              | 11-30 |

| 11.3.6   | タイマカウンタ(TCNT)                     | 11-32 |

| 11.3.7   | タイマジェネラルレジスタ ( TGR )              | 11-32 |

| 11.3.8   | タイマスタートレジスタ(TSTR)                 | 11-33 |

| 11.3.9   | タイマシンクロレジスタ(TSYR)                 | 11-33 |

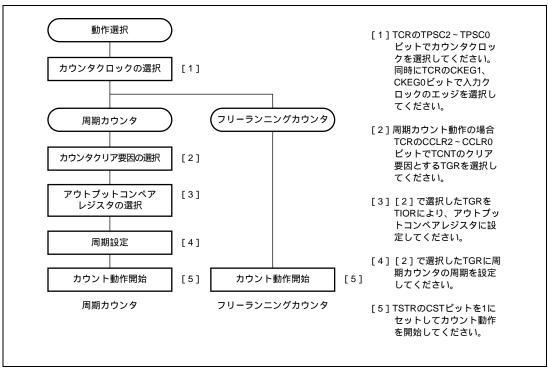

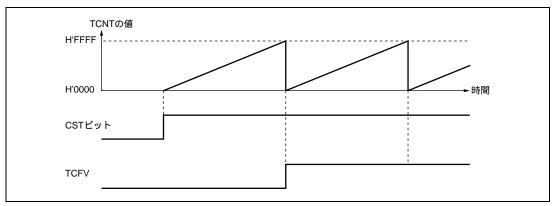

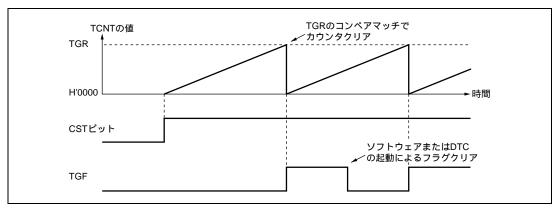

| 11.4     | 動作説明                              | 11-34 |

| 11.4.1   | 基本動作                              | 11-34 |

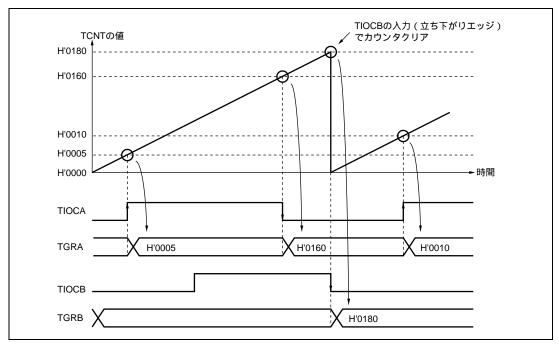

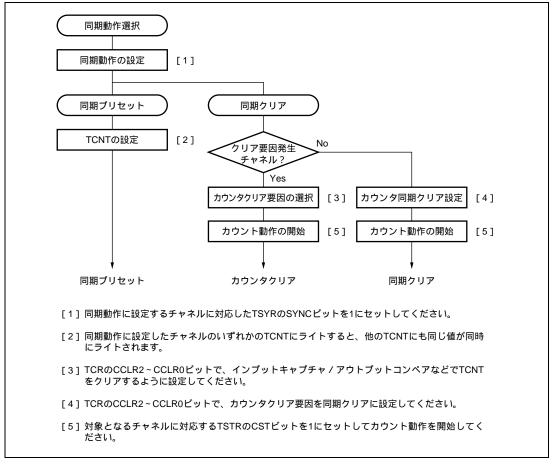

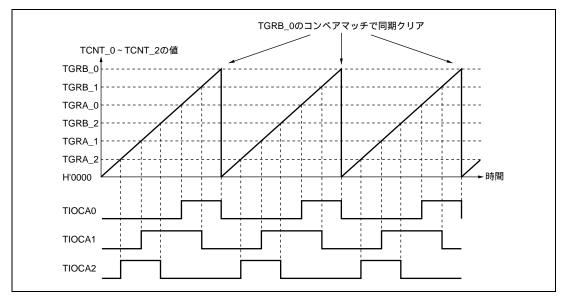

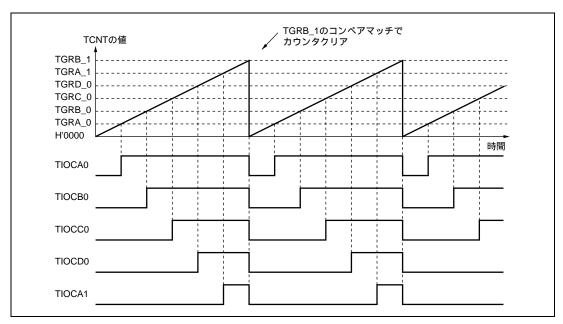

| 11.4.2  | 同期動作                              | 11-39 |

|---------|-----------------------------------|-------|

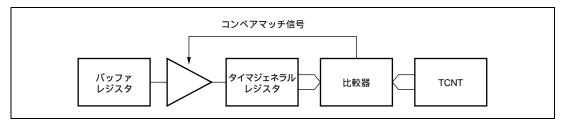

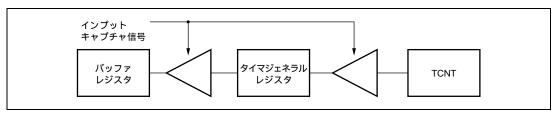

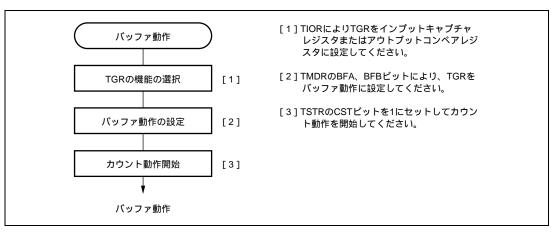

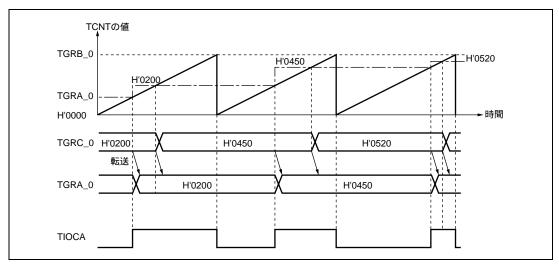

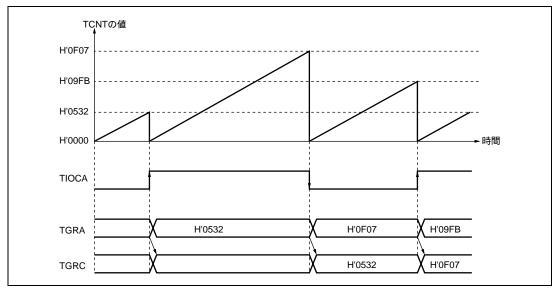

| 11.4.3  | バッファ動作                            | 11-41 |

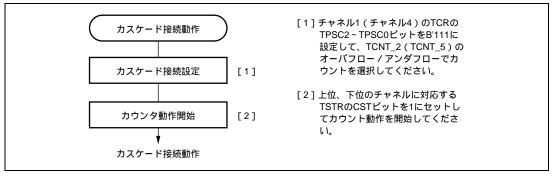

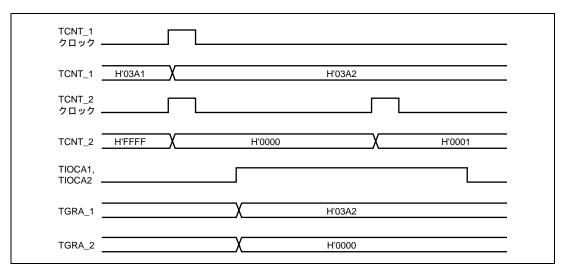

| 11.4.4  | カスケード接続動作                         | 11-44 |

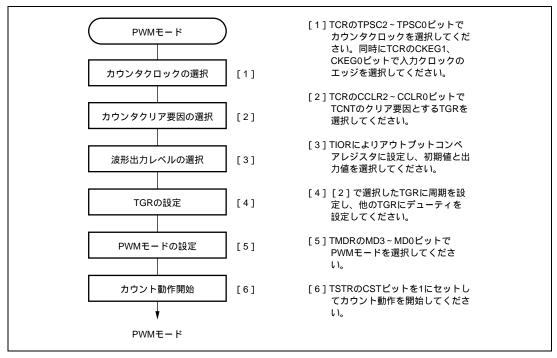

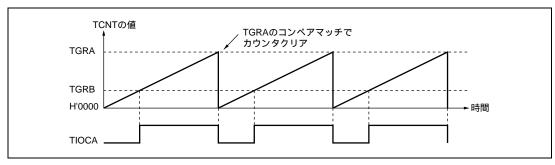

| 11.4.5  | PWM モード                           | 11-46 |

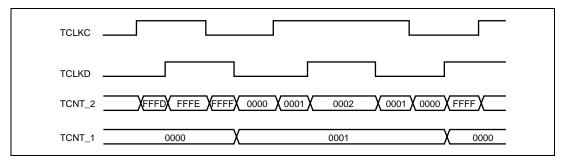

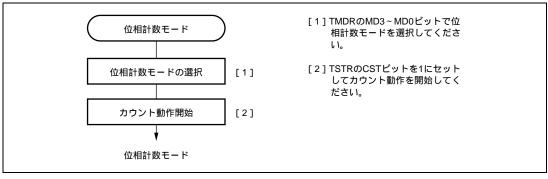

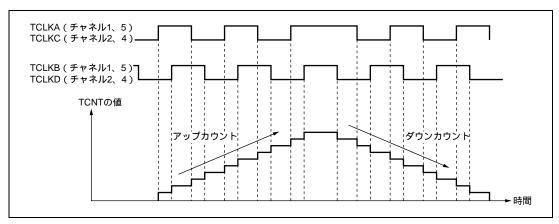

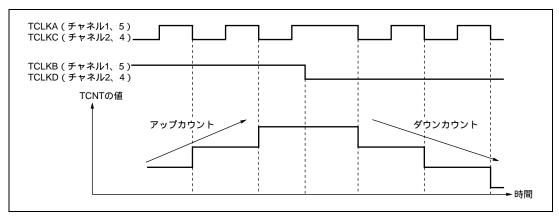

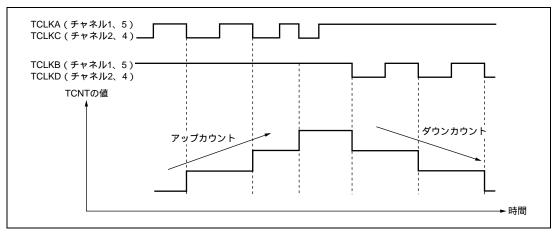

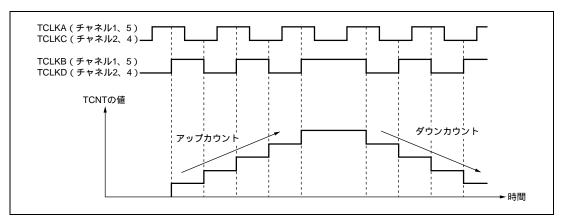

| 11.4.6  | 位相計数モード                           | 11-51 |

| 11.5    | 割り込み要因                            | 11-56 |

| 11.6    | DTCの起動                            | 11-58 |

| 11.7    | DMACの起動                           | 11-58 |

| 11.8    | A/D変換器の起動                         | 11-58 |

| 11.9    | 動作タイミング                           | 11-59 |

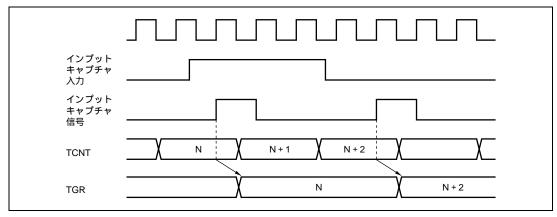

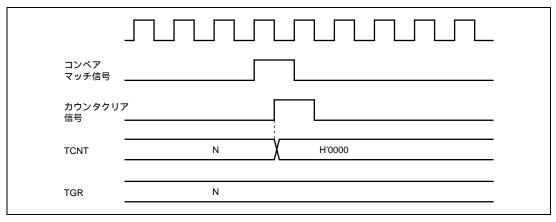

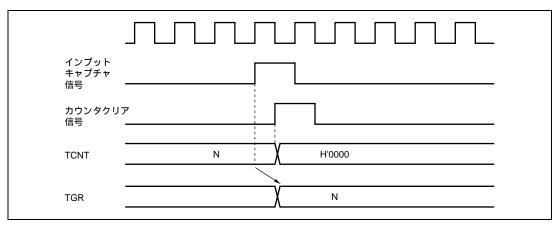

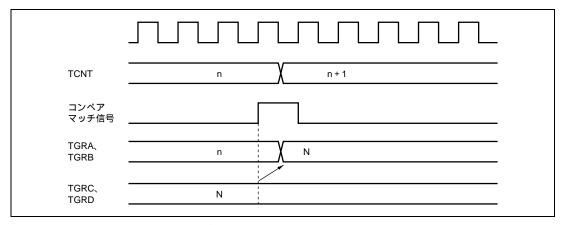

| 11.9.1  | 入出力タイミング                          | 11-59 |

| 11.9.2  | 割り込み信号タイミング                       | 11-63 |

| 11.10   | 使用上の注意事項                          | 11-67 |

| 11.10.1 | モジュールストップモードの設定                   | 11-67 |

| 11.10.2 | 2 入力クロックの制限事項                     | 11-67 |

| 11.10.3 | 8 周期設定上の注意事項                      | 11-67 |

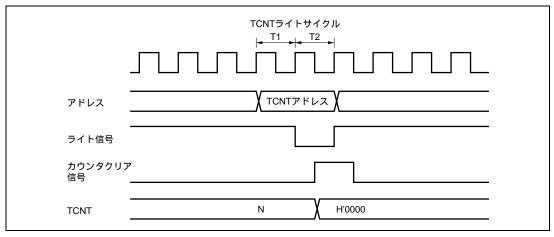

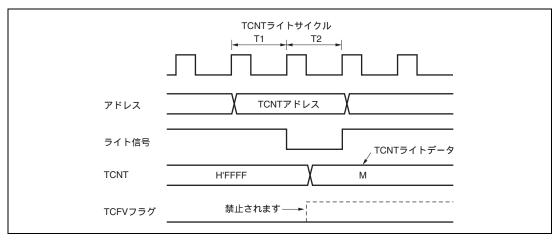

| 11.10.4 | I TCNT のライトとクリアの競合                | 11-68 |

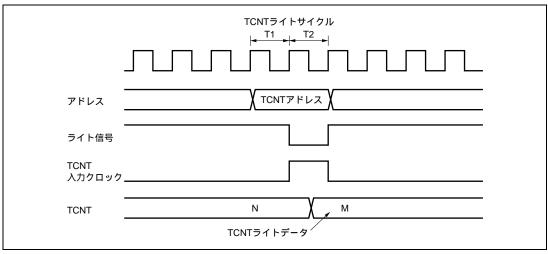

| 11.10.5 | 5 TCNT のライトとカウントアップの競合            | 11-68 |

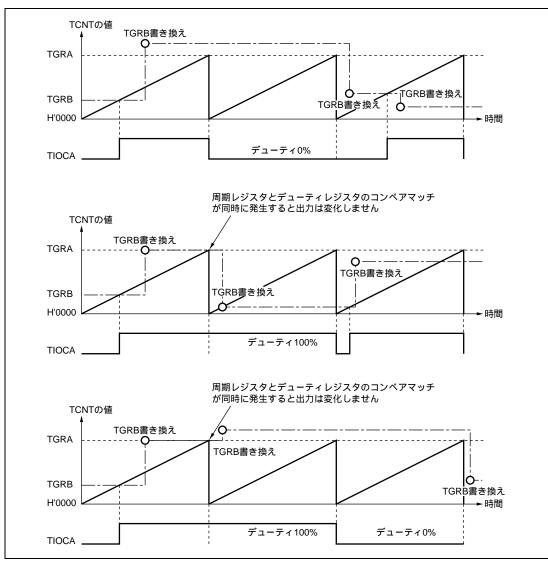

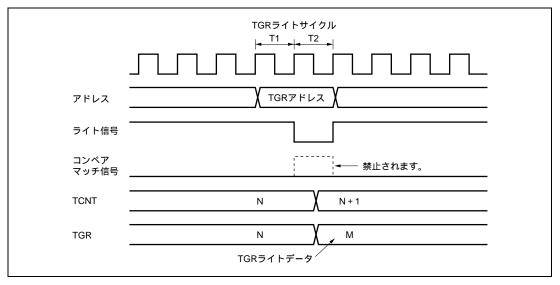

| 11.10.6 | 5 TGR のライトとコンペアマッチの競合             | 11-69 |

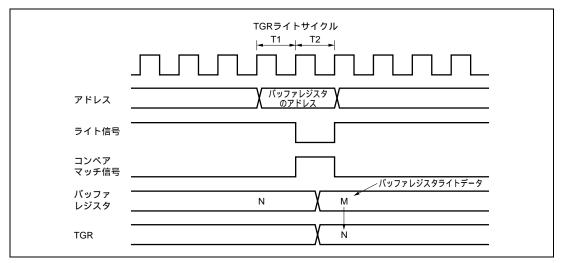

| 11.10.7 | / バッファレジスタのライトとコンペアマッチの競合         | 11-70 |

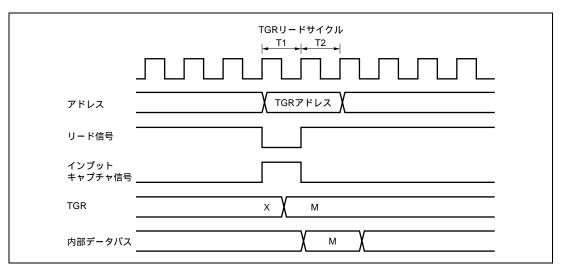

| 11.10.8 | 3 TGR のリードとインプットキャプチャの競合          | 11-71 |

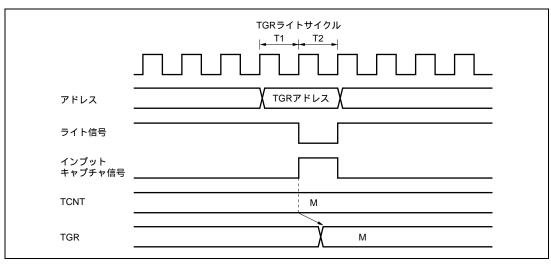

| 11.10.9 | ) TGR のライトとインプットキャプチャの競合          | 11-71 |

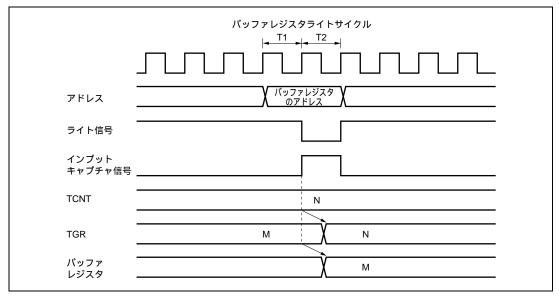

| 11.10.1 | 0 バッファレジスタのライトとインプットキャプチャの競合      | 11-72 |

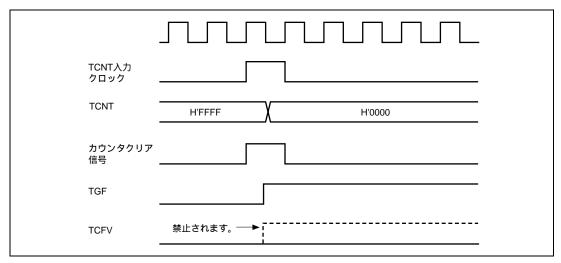

| 11.10.1 | 1 オーバフロー/アンダフローとカウンタクリアの競合        | 11-73 |

| 11.10.1 | 2 TCNT のライトとオーバフロー/アンダフローの競合      | 11-74 |

| 11.10.1 | 3 入出力端子の兼用                        | 11-74 |

| 11.10.1 | 4 モジュールストップ時の割り込み                 | 11-74 |

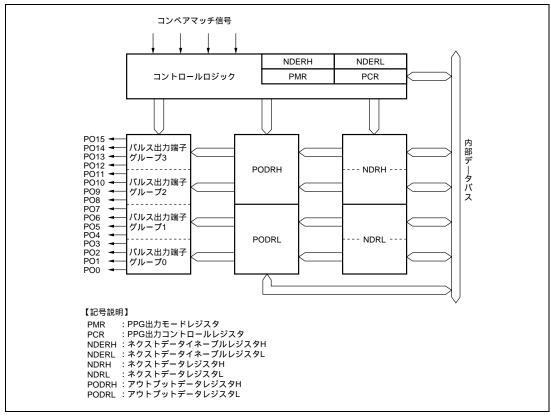

| 12. プロ  | グラマブルパルスジェネレータ(PPG)               | 12-1  |

| 12.1    | 特長                                | 12-1  |

| 12.2    | 入出力端子                             | 12-3  |

| 12.3    | レジスタの説明                           | 12-3  |

| 12.3.1  | ネクストデータイネーブルレジスタ H、L(NDERH、NDERL) |       |

| 12.3.2  | アウトプットデータレジスタ H、L(PODRH、PODRL)    |       |

| 12.3.3  | ネクストデータレジスタ H、L ( NDRH、NDRL )     | 12-6  |

| 12.3.4  | PPG 出力コントロールレジスタ(PCR )            | 12-8  |

| 12.3.5  | PPG 出力モードレジスタ(PMR )               |       |

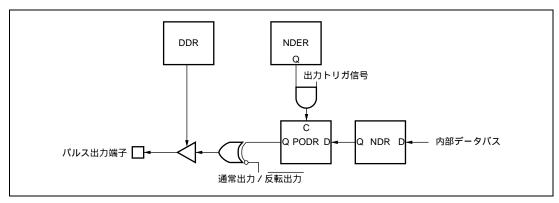

| 12.4    | 動作説明                              |       |

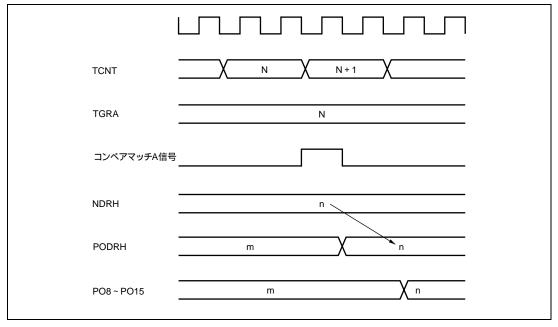

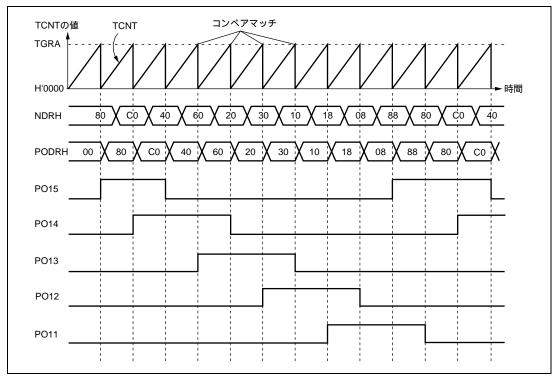

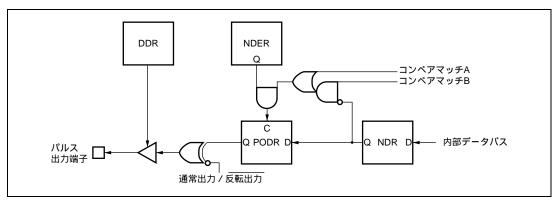

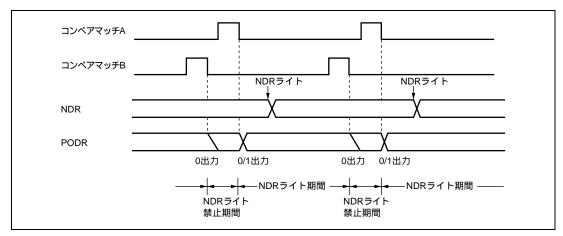

| 12.4.1  | 出力タイミング                           | 12-11 |

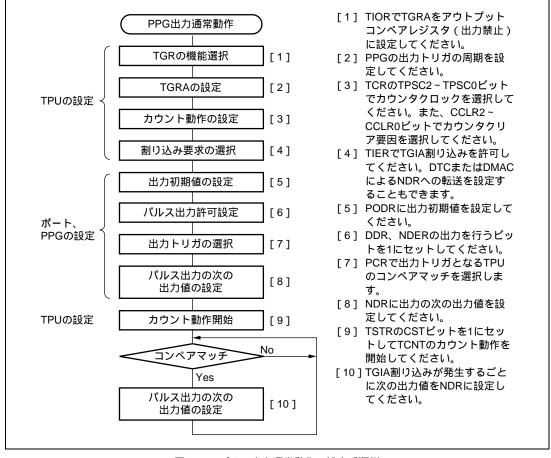

| 12.4.2  | 通常動作のパルス出力設定手順例                   | 12-12 |

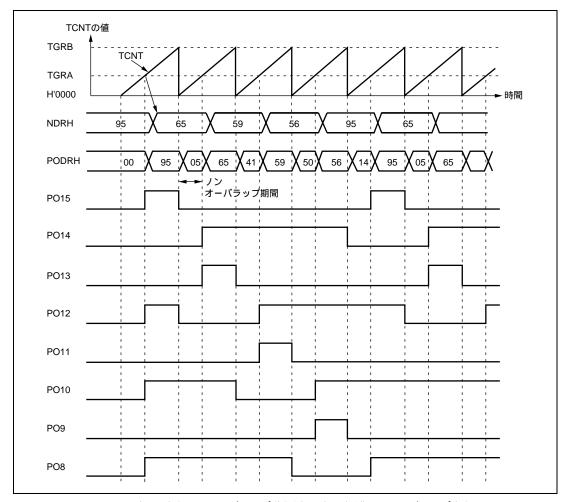

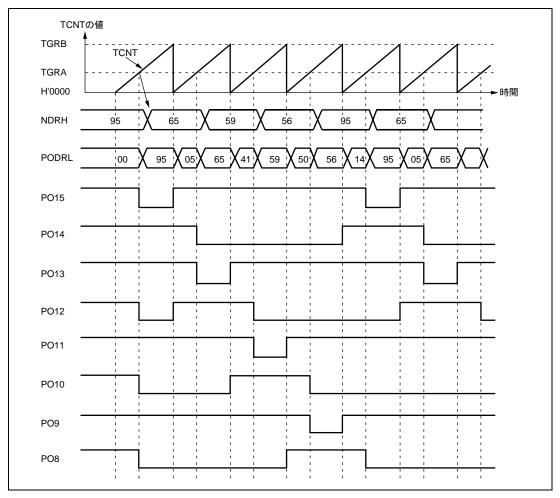

| 12.4.3 | パルス出力通常動作例(5 相パルス出力例)               | 12-13 |

|--------|-------------------------------------|-------|

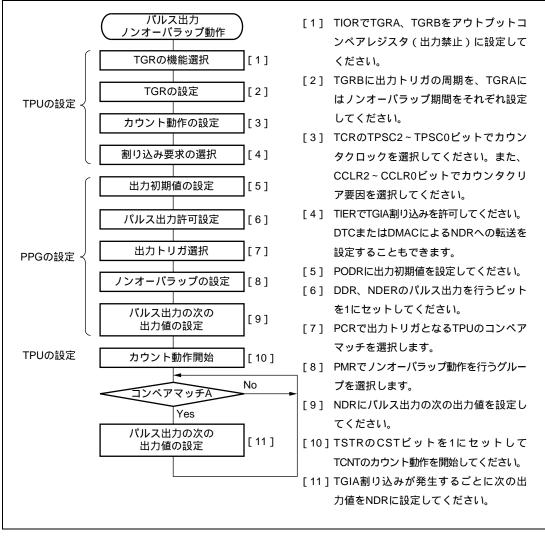

| 12.4.4 | パルス出力ノンオーバラップ動作                     | 12-14 |

| 12.4.5 | ノンオーバラップ動作のパルス出力設定手順例               | 12-16 |

| 12.4.6 | パルス出力ノンオーバラップ動作例(4 相の相補ノンオーバラップ出力例) | 12-17 |

| 12.4.7 | パルス反転出力                             | 12-19 |

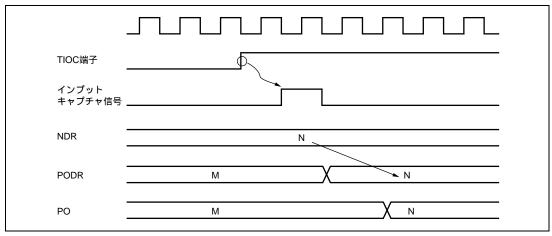

| 12.4.8 | インプットキャプチャによるパルス出力                  | 12-20 |

| 12.5   | 使用上の注意事項                            | 12-20 |

| 12.5.1 | モジュールストップモードの設定                     | 12-20 |

| 12.5.2 | パルス出力端子の動作                          | 12-20 |

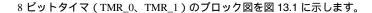

| 13. 8ピ | 「ットタイマ(TMR)                         | 13-1  |

| 13.1   | 特長                                  | 13-1  |

| 13.2   | 入出力端子                               | 13-3  |

| 13.3   | レジスタの説明                             | 13-3  |

| 13.3.1 | タイマカウンタ(TCNT)                       | 13-4  |

| 13.3.2 | タイムコンスタントレジスタ A(TCORA)              | 13-4  |

| 13.3.3 | タイムコンスタントレジスタ B(TCORB)              | 13-4  |

| 13.3.4 | タイマコントロールレジスタ ( TCR )               | 13-5  |

| 13.3.5 | タイマコントロール/ステータスレジスタ ( TCSR )        | 13-7  |

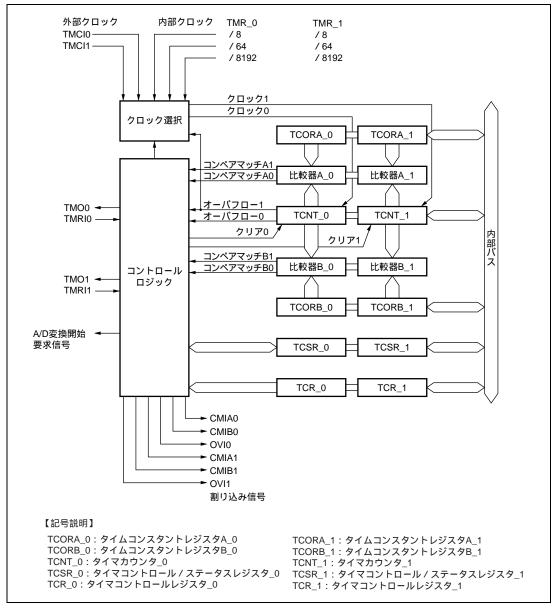

| 13.4   | 動作説明                                | 13-9  |

| 13.4.1 | パルス出力                               | 13-9  |

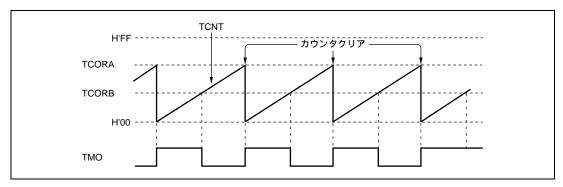

| 13.1   | 動作タイミング                             | 13-10 |

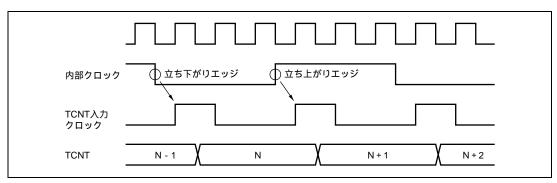

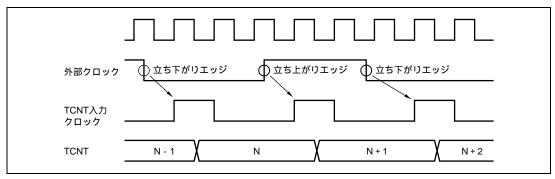

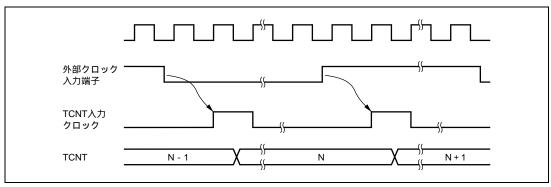

| 13.5.1 | TCNT のカウントタイミング                     |       |

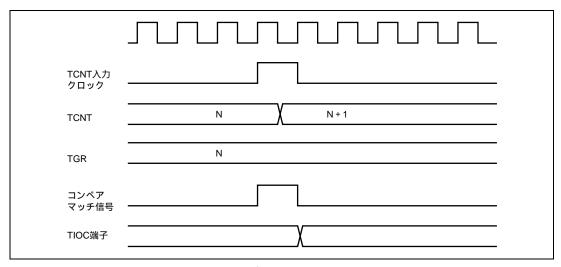

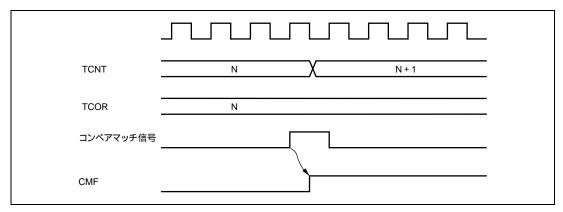

| 13.5.2 | コンペアマッチ時の CMFA、CMFB フラグのセットタイミング    | 13-10 |

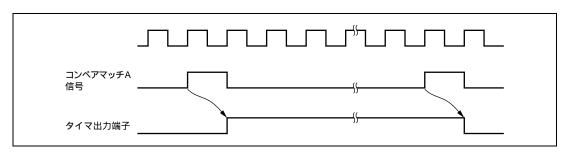

| 13.5.3 | コンペアマッチ時のタイマ出力タイミング                 |       |

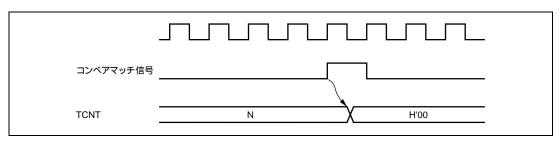

| 13.5.4 | コンペアマッチによるカウンタクリアタイミング              | 13-11 |

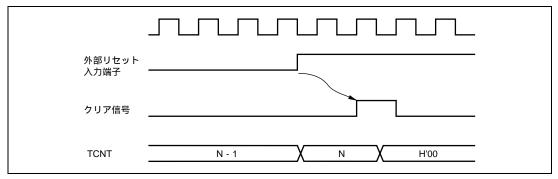

| 13.5.5 | TCNT の外部リセットタイミング                   | 13-12 |

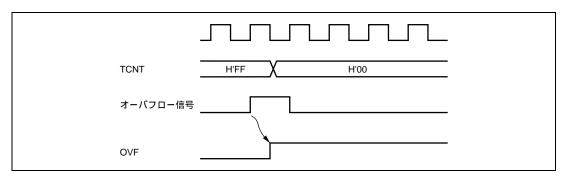

| 13.5.6 | オーバフローフラグ(OVF)のセットタイミング             |       |

| 13.6   | カスケード接続時の動作                         | 13-13 |

| 13.6.1 | 16 ビットカウントモード                       |       |

| 13.6.2 | コンペアマッチカウントモード                      | 13-13 |

| 13.7   | 割り込み要因                              | 13-14 |

| 13.7.1 | 割り込み要因と DTC 起動                      | 13-14 |

| 13.7.2 | A/D 変換器の起動                          | 13-14 |

| 13.8   | 使用上の注意                              |       |

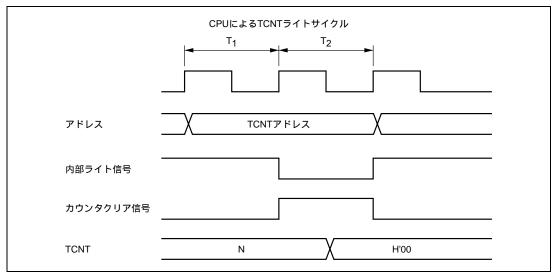

| 13.8.1 | TCNT のライトとカウンタクリアの競合                |       |

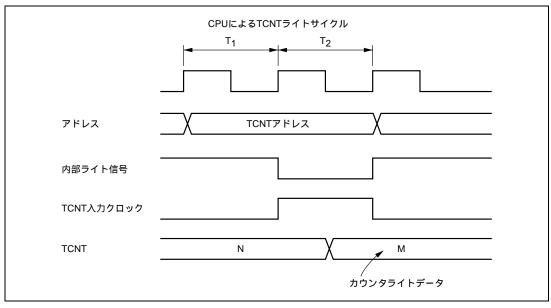

| 13.8.2 | TCNT のライトとカウントアップの競合                | 13-15 |

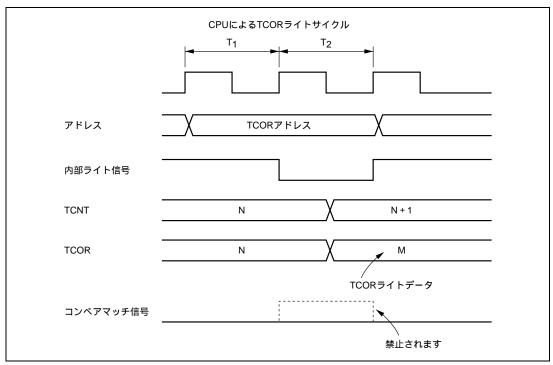

| 13.8.3 | TCOR のライトとコンペアマッチの競合                | 13-16 |

| 13.8.4 | コンペアマッチ A、B の競合                     | 13-16 |

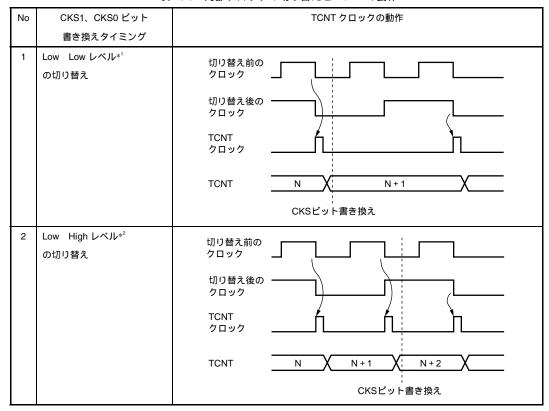

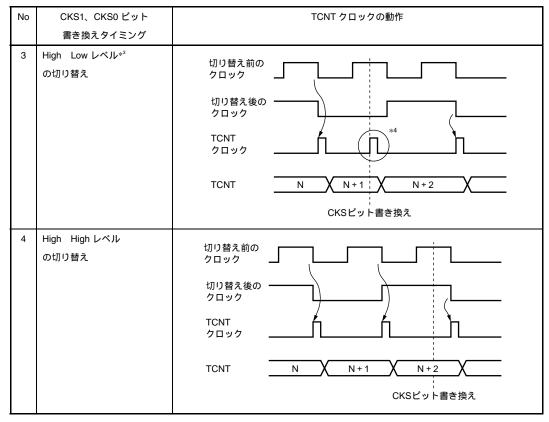

| 13.8.5 | 内部クロックの切り替えと TCNT の動作               | 13-17 |

| 13.8.6  | カスケード接続時のモード設定                   | 13-18 |

|---------|----------------------------------|-------|

| 13.8.7  | モジュールストップモード時の割り込み               | 13-18 |

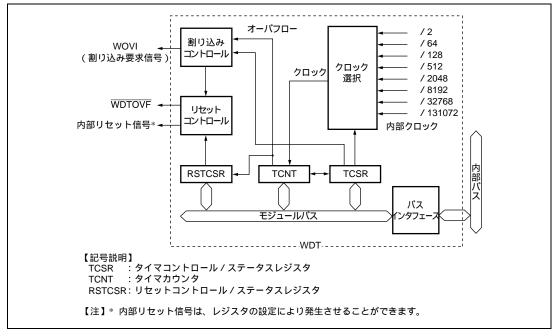

| 14. ウォ  | ッチドッグタイマ(WDT)                    | 14-1  |

| 14.1    | 特長                               | 14-1  |

| 14.2    | 入出力端子                            | 14-2  |

| 14.3    | レジスタの説明                          | 14-2  |

| 14.3.1  | タイマカウンタ ( TCNT )                 | 14-2  |

| 14.3.2  | タイマコントロール/ステータスレジスタ(TCSR)        | 14-3  |

| 14.3.3  | リセットコントロール/ステータスレジスタ(RSTCSR)     | 14-4  |

| 14.4    | 動作説明                             | 14-5  |

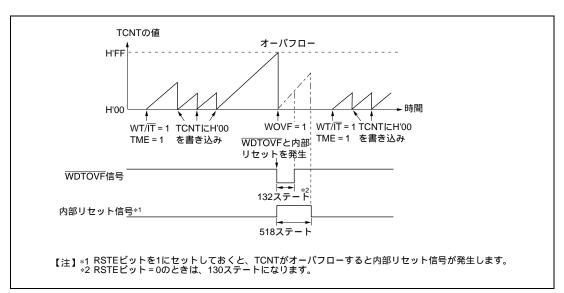

| 14.4.1  | ウォッチドッグタイマモード                    | 14-5  |

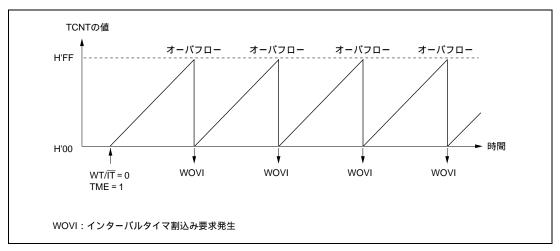

| 14.4.2  | インターバルタイマモード                     | 14-6  |

| 14.5    | 割り込み要因                           | 14-6  |

| 14.6    | 使用上の注意事項                         | 14-7  |

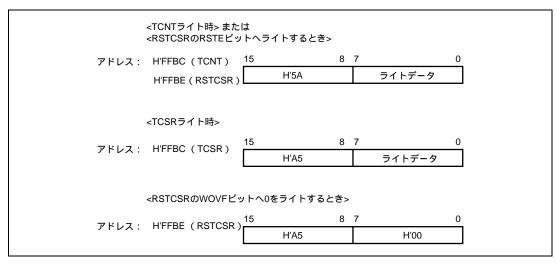

| 14.6.1  | レジスタアクセス時の注意                     | 14-7  |

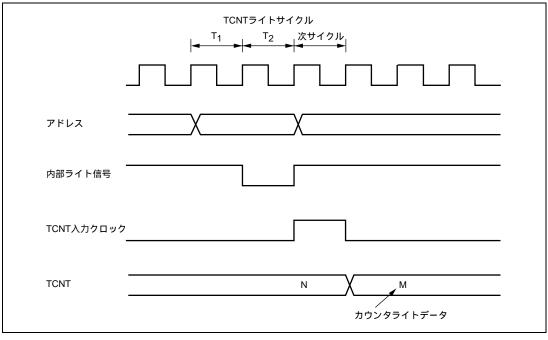

| 14.6.2  | タイマカウンタ(TCNT)のライトとカウントアップの競合     | 14-8  |

| 14.6.3  | CKS2~CKS0 ビットの書き換え               | 14-8  |

| 14.6.4  | ウォッチドッグタイマモードとインターバルタイマモードの切り替え  | 14-8  |

| 14.6.5  | ウォッチドッグタイマモードでの内部リセット            | 14-9  |

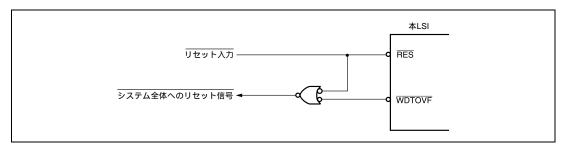

| 14.6.6  | WDTOVF 信号によるシステムのリセット            | 14-9  |

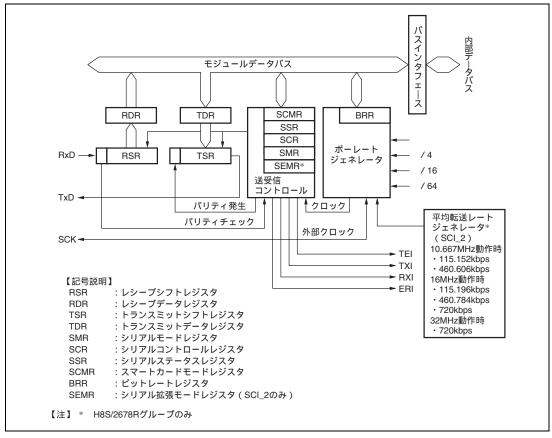

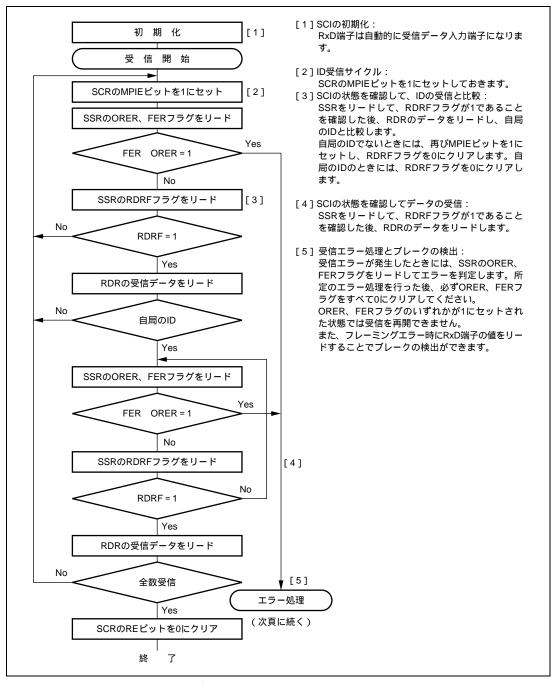

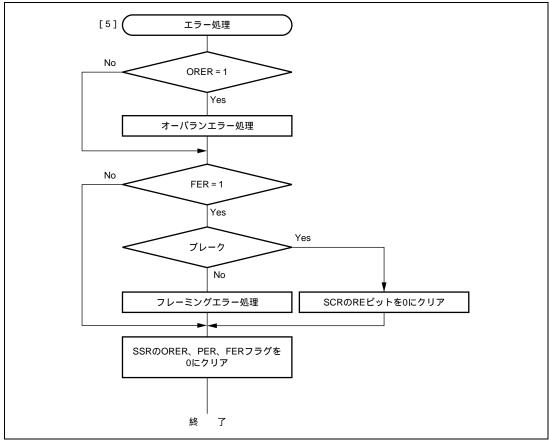

| 5 シロ    | アルコミュニケーションインタフェース (SCI、IrDA)    | 15-1  |

|         | 特長                               |       |

| 15.1    |                                  |       |

| 15.2    | 入出力端子                            |       |

| 15.3    | レジスタの説明                          |       |

| 15.3.1  | レシーブシフトレジスタ(RSR)                 |       |

| 15.3.2  | レシーブデータレジスタ(RDR)                 |       |

| 15.3.3  | トランスミットデータレジスタ (TDR)             |       |

| 15.3.4  | トランスミットシフトレジスタ (TSR)             |       |

| 15.3.5  | シリアルモードレジスタ(SMR)                 |       |

| 15.3.6  | シリアルコントロールレジスタ(SCR)              |       |

| 15.3.7  | シリアルステータスレジスタ ( SSR )            |       |

| 15.3.8  | スマートカードモードレジスタ(SCMR)             |       |

| 15.3.9  | ビットレートレジスタ (BRR)                 | 15-14 |

| 15.3.10 | IrDA コントロールレジスタ(IrCR)            | 15-22 |

| 15.3.11 | シリアル拡張モードレジスタ(SEMR )             | 15-23 |

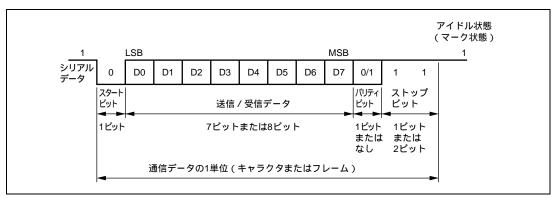

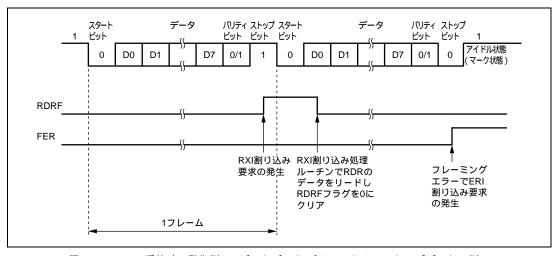

| 15.4    | 調歩同期式モードの動作                      | 15-24 |

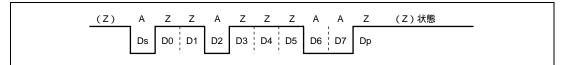

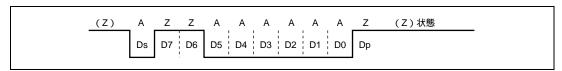

| 15.4.1  | 送受信フォーマット                        |       |

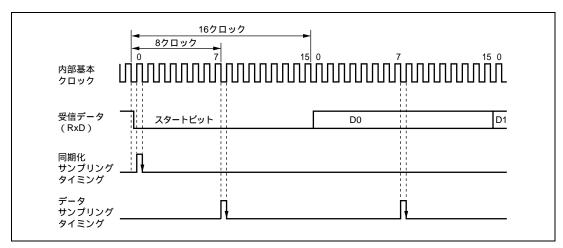

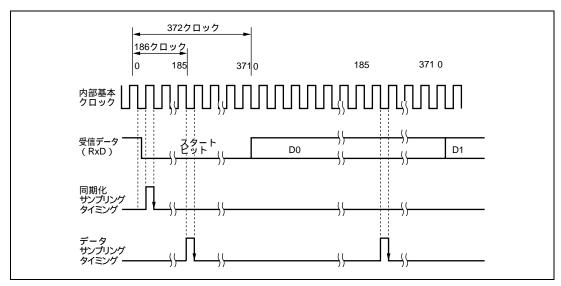

| 15.4.2  | 調歩同期式モードの受信データサンプリングタイミングと受信マージン | 15-26 |

| 15.4.3  | クロック                               | 15-27 |

|---------|------------------------------------|-------|

| 15.4.4  | SCI の初期化(調歩同期式)                    | 15-28 |

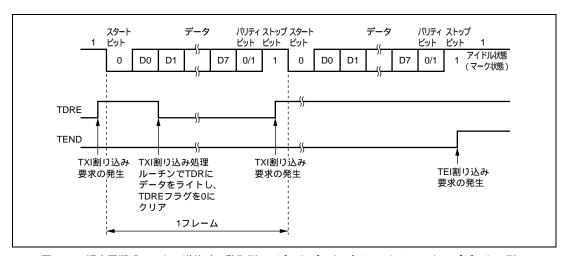

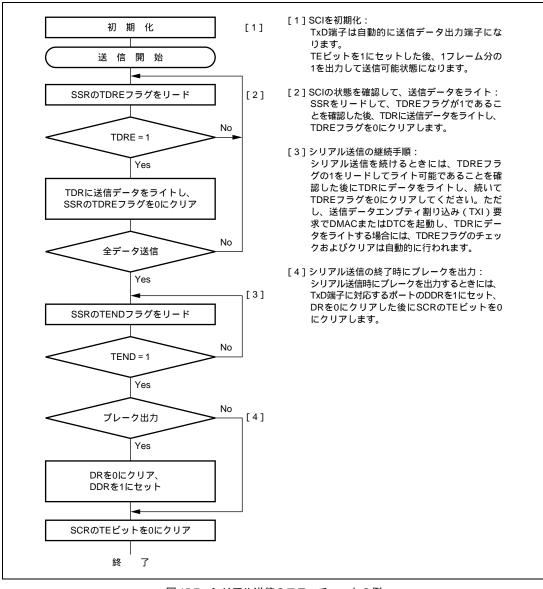

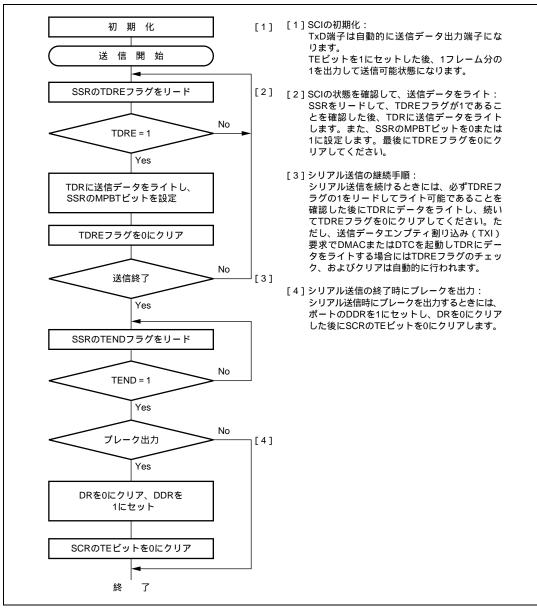

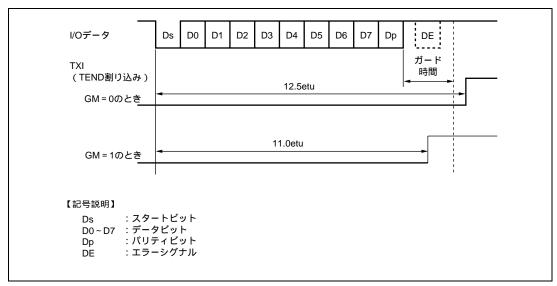

| 15.4.5  | データ送信(調歩同期式)                       | 15-29 |

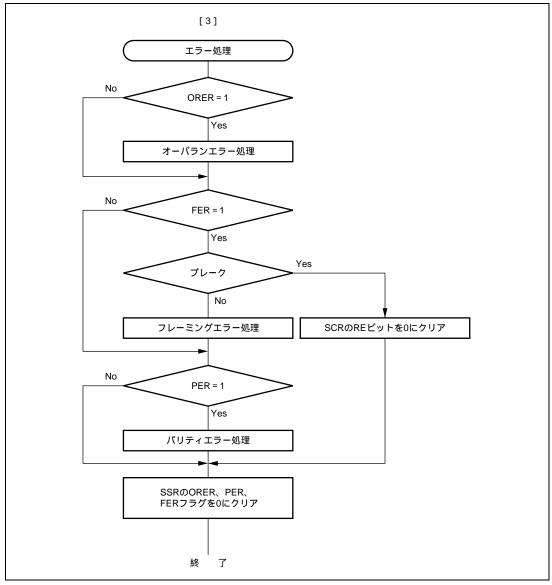

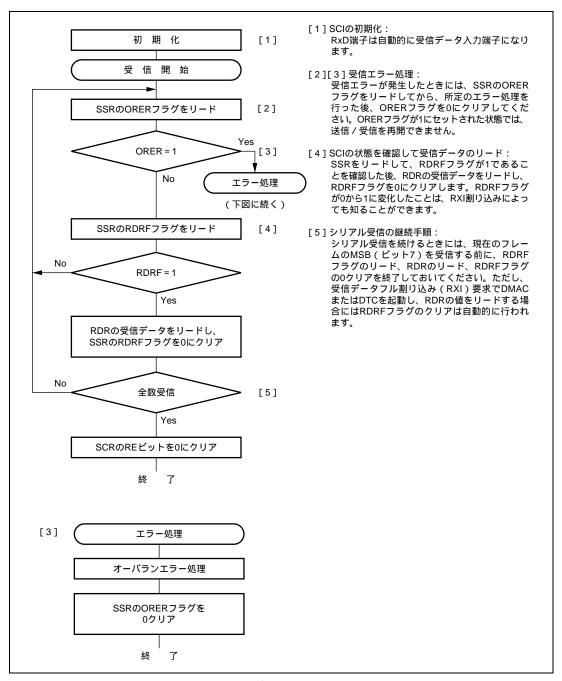

| 15.4.6  | シリアルデータ受信(調歩同期式)                   | 15-31 |

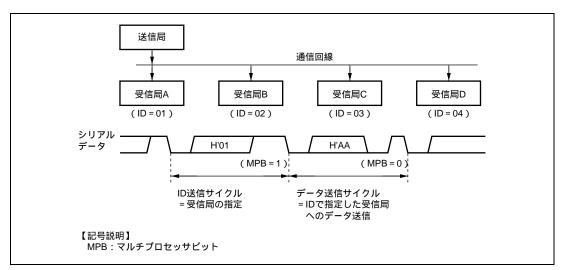

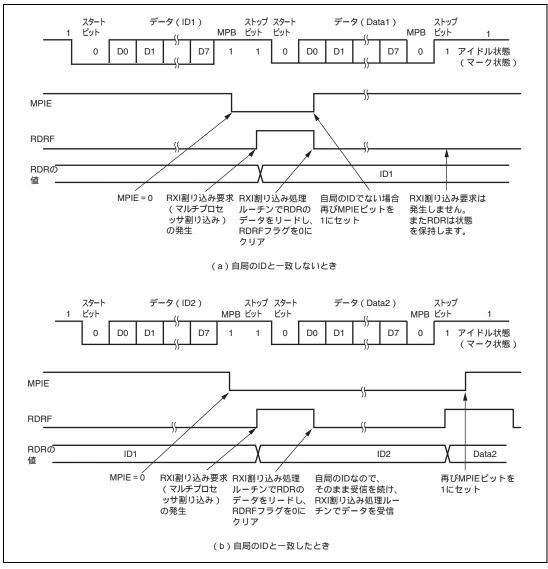

| 15.5    | マルチプロセッサ通信機能                       | 15-34 |

| 15.5.1  | マルチプロセッサシリアルデータ送信                  | 15-35 |

| 15.5.2  | マルチプロセッサシリアルデータ受信                  | 15-36 |

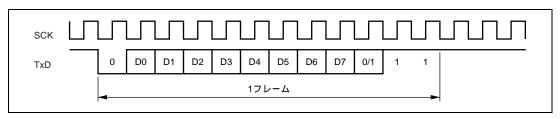

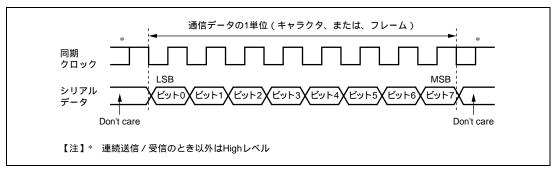

| 15.6    | クロック同期式モードの動作                      | 15-39 |

| 15.6.1  | クロック                               | 15-39 |

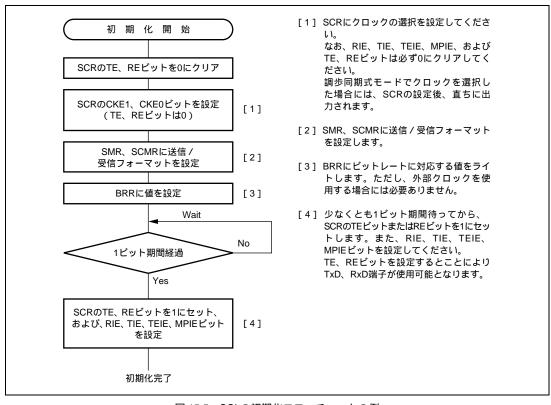

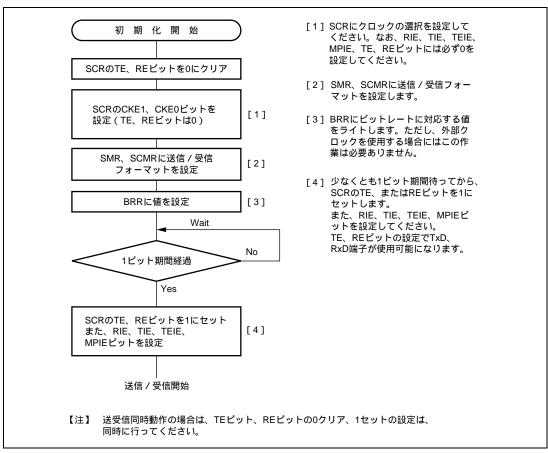

| 15.6.2  | SCI の初期化                           | 15-40 |

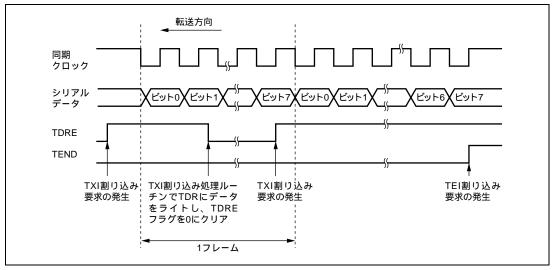

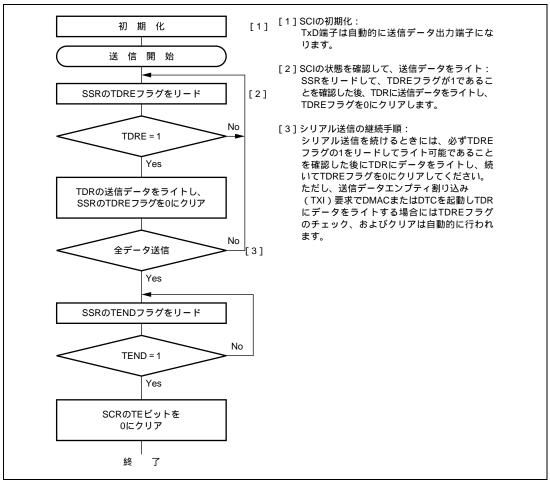

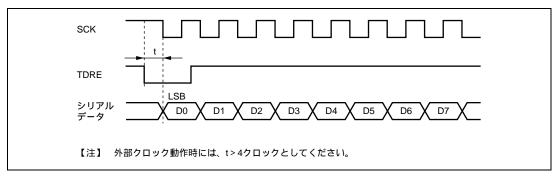

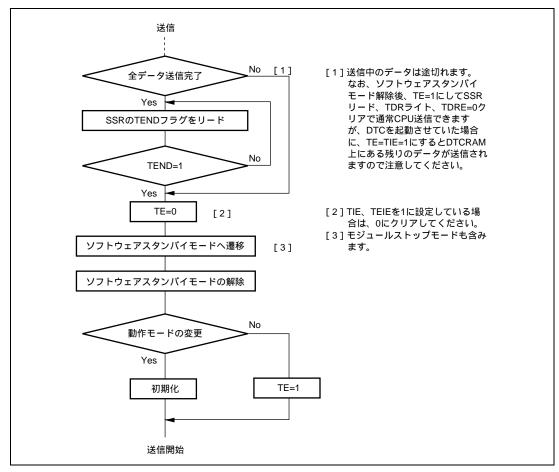

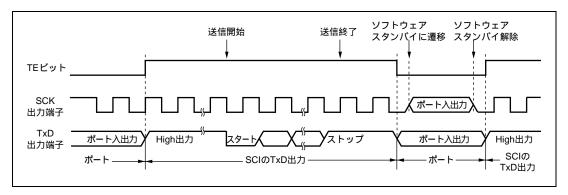

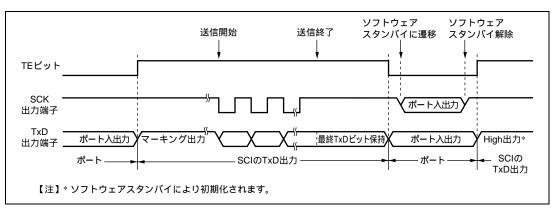

| 15.6.3  | シリアルデータ送信(クロック同期式)                 | 15-41 |

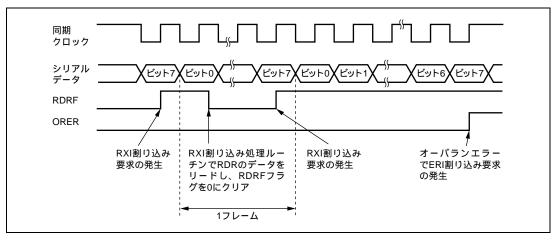

| 15.6.4  | シリアルデータ受信(クロック同期式)                 | 15-43 |

| 15.6.5  | シリアルデータ送受信同時動作(クロック同期式)            | 15-45 |

| 15.7    | スマートカードインタフェースの動作説明                | 15-47 |

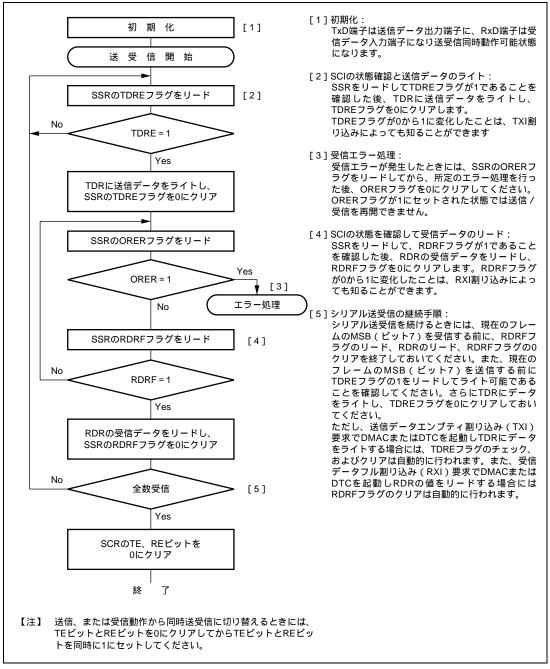

| 15.7.1  | 接続例                                | 15-47 |

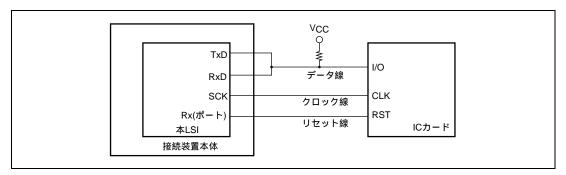

| 15.7.2  | データフォーマット(ブロック転送モード時を除く)           | 15-48 |

| 15.7.3  | プロック転送モード                          | 15-49 |

| 15.7.4  | 受信データサンプリングタイミングと受信マージン            | 15-50 |

| 15.7.5  | 初期設定                               | 15-51 |

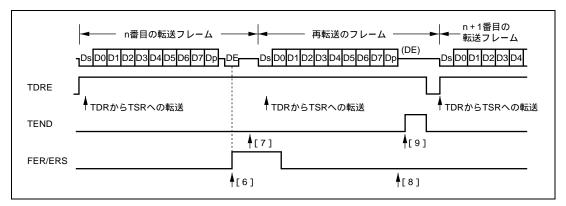

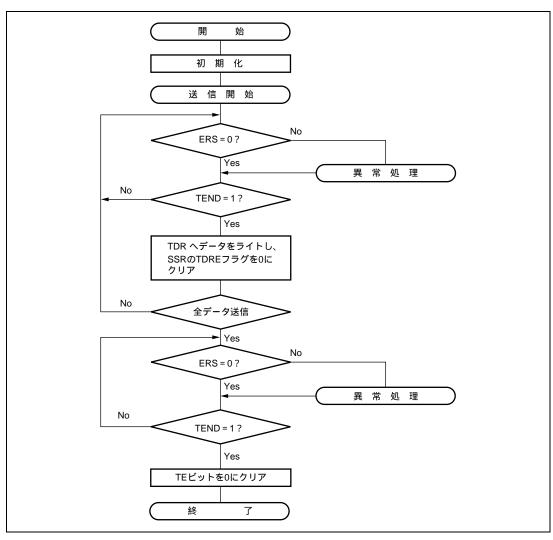

| 15.7.6  | データ送信(ブロック転送モードを除く)                | 15-52 |

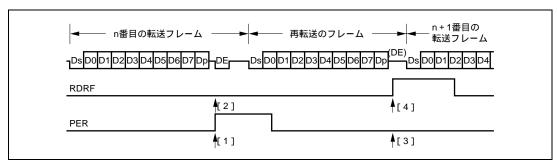

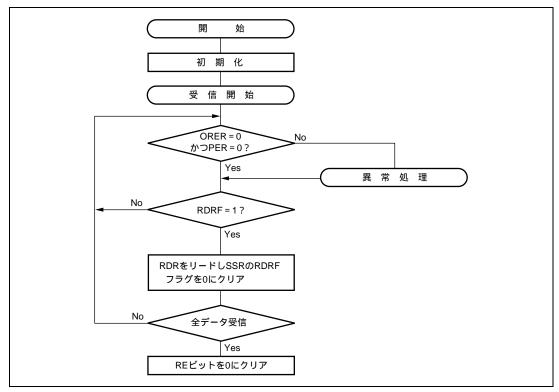

| 15.7.7  | シリアルデータ受信 ( ブロック転送モードを除く )         | 15-55 |

| 15.7.8  | クロック出力制御                           | 15-57 |

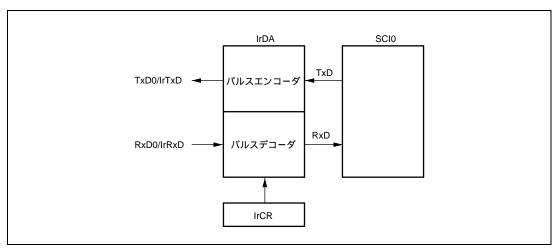

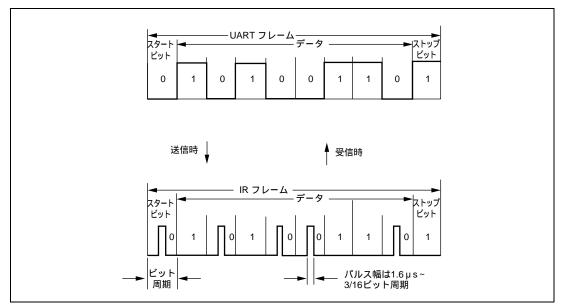

| 15.8    | IrDA動作                             | 15-59 |

| 15.9    | 割り込み要因                             |       |

| 15.9.1  | 通常のシリアルコミュニケーションインタフェースモードにおける割り込み | 15-62 |

| 15.9.2  | スマートカードインタフェースモードにおける割り込み          | 15-63 |

| 15.10   | 使用上の注意事項                           | 15-64 |

| 15.10.1 | モジュールストップモードの設定                    | 15-64 |

| 15.10.2 | 2 プレークの検出と処理について                   | 15-64 |

| 15.10.3 | マーク状態とブレークの送出                      | 15-64 |

| 15.10.4 | - 受信エラーフラグと送信動作について(クロック同期式モードのみ)  | 15-64 |

| 15.10.5 | TDR へのライトと TDRE フラグの関係について         | 15-64 |

| 15.10.6 | 5 DMAC または DTC 使用上の制約事項            | 15-65 |

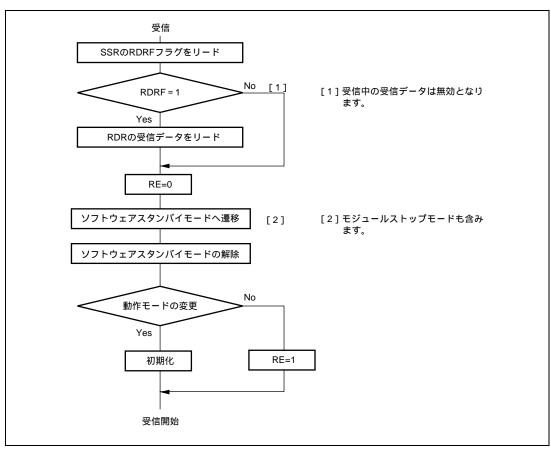

| 15.10.7 | 7 モード遷移時の動作について                    | 15-65 |

| 16. A/D | 变换器                                | 16-1  |

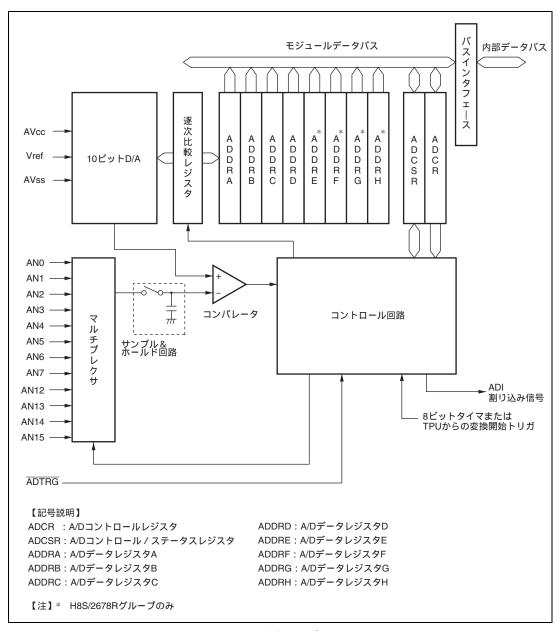

| 16.1    | 特長                                 | 16-1  |

| 16.2    | 入出力端子                              | 16-3  |

| 16.3    | レジスタの説明                            | 16-4  |

| 1631    | Δ/D データレジスタ Δ~H(ΔDDRΔ~ADDRH)       | 16-4  |

| 16.3.2  | A/D コントロール/ステータスレジスタ(ADCSR)            | 16-5  |

|---------|----------------------------------------|-------|

| 16.3.3  | A/D コントロールレジスタ(ADCR)                   | 16-8  |

| 16.4    | 動作説明                                   | 16-9  |

| 16.4.1  | シングルモード                                | 16-9  |

| 16.4.2  | スキャンモード                                | 16-10 |

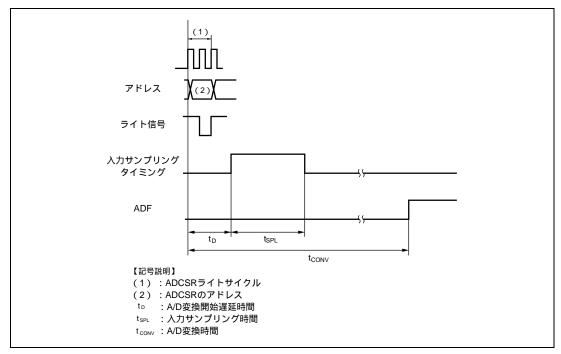

| 16.4.3  | 入力サンプリングと A/D 変換時間                     | 16-10 |

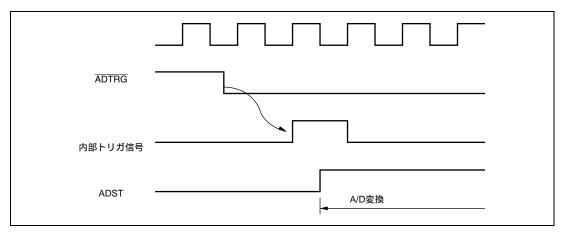

| 16.4.4  | 外部トリガ入力タイミング                           | 16-12 |

| 16.5    | 割り込み要因                                 | 16-13 |

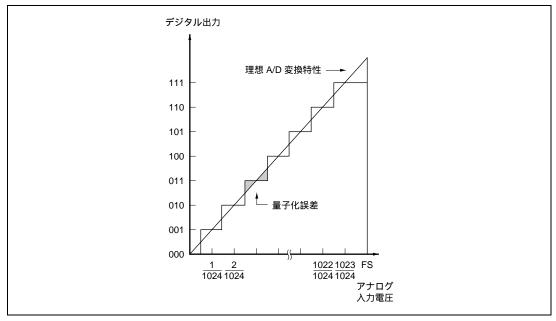

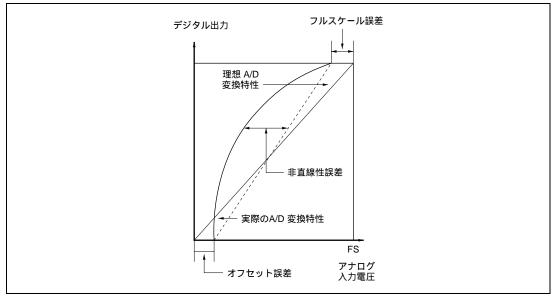

| 16.6    | A/D変換精度の定義                             | 16-13 |

| 16.7    | 使用上の注意事項                               | 16-15 |

| 16.7.1  | モジュールストップモードの設定                        | 16-15 |

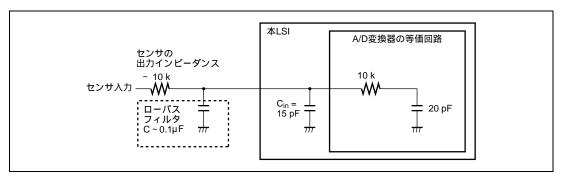

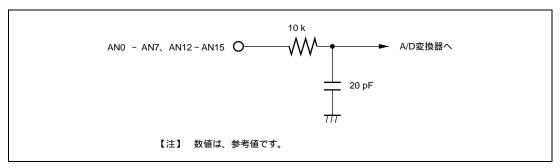

| 16.7.2  | 許容信号源インピーダンスについて                       | 16-15 |

| 16.7.3  | 絶対精度への影響                               | 16-15 |

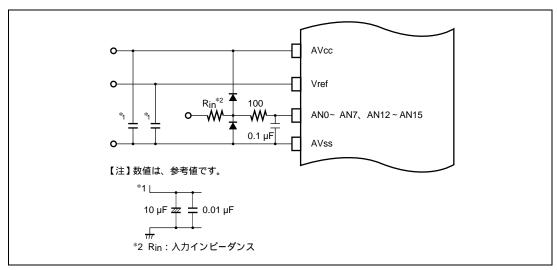

| 16.7.4  | アナログ電源端子他の設定範囲                         | 16-15 |

| 16.7.5  | ボード設計上の注意                              | 16-16 |

| 16.7.6  | ノイズ対策上の注意                              | 16-16 |

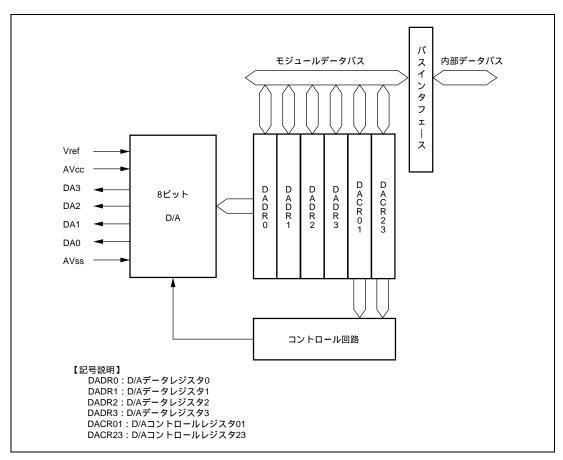

| 17. D/A | 变换器                                    | 17-1  |

| 17.1    | 特長                                     | 17-1  |

| 17.2    | 入出力端子                                  | 17-2  |

| 17.3    | レジスタの説明                                | 17-2  |

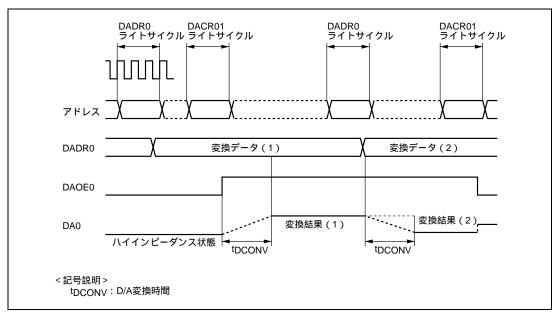

| 17.3.1  | D/A データレジスタ 0~3 ( DADR0~DADR3 )        | 17-2  |

| 17.3.2  | D/A コントロールレジスタ 01、23 ( DACR01、DACR23 ) | 17-3  |

| 17.4    | 動作説明                                   | 17-5  |

| 17.5    | 使用上の注意事項                               | 17-6  |

| 17.5.1  | モジュールストップモードの設定                        | 17-6  |

| 17.5.2  | ソフトウェアスタンバイモード時の D/A 出力保持機能            | 17-6  |

| 18. RAN | Λ                                      | 18-1  |

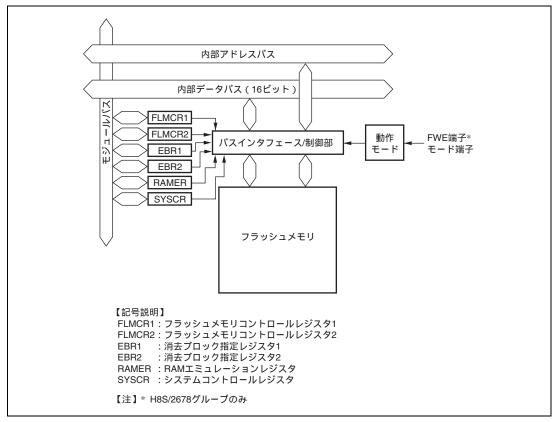

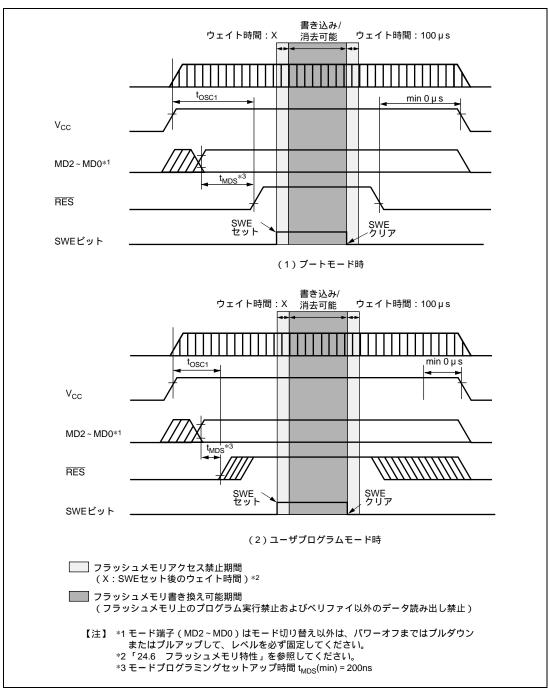

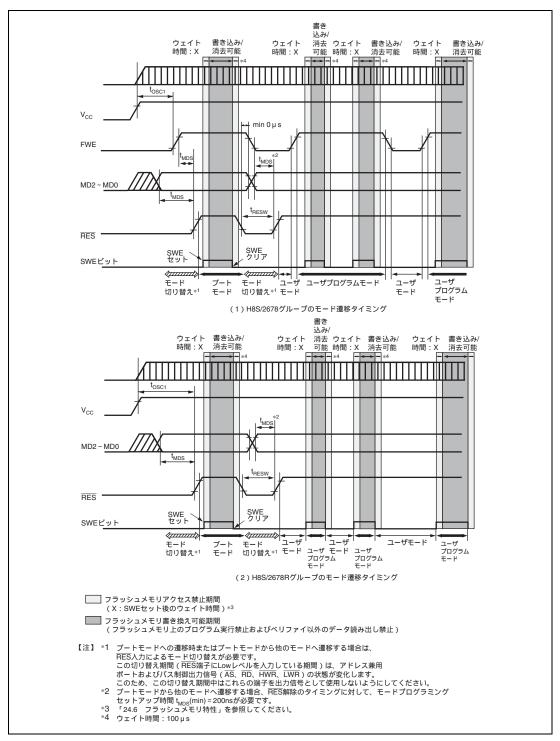

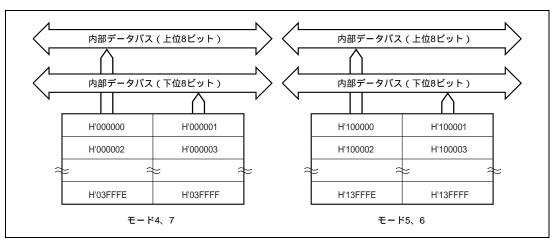

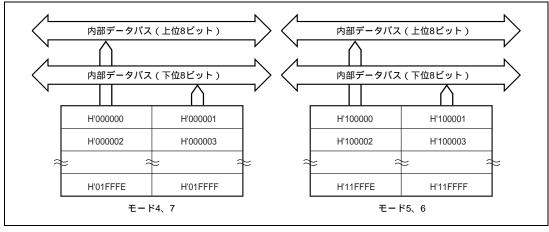

| 19. フラ  | ・ッシュメモリ(F-ZTAT 版)                      | 19-1  |

| 19.1    | 特長                                     | 19-1  |

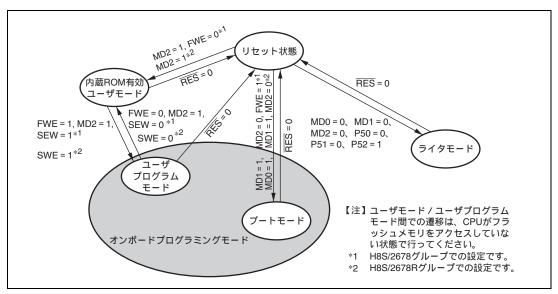

| 19.2    | モード遷移図                                 |       |

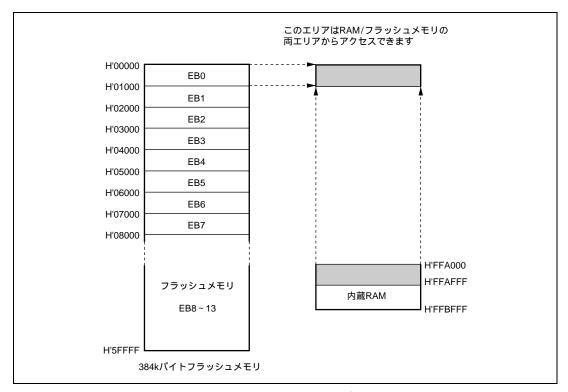

| 19.3    | プロック構成                                 |       |

| 19.4    |                                        |       |

| 19.5    | レジスタの説明                                |       |

| 19.5.1  | フラッシュメモリコントロールレジスタ 1 (FLMCR1)          |       |

| 19.5.2  | フラッシュメモリコントロールレジスタ 2 (FLMCR2)          |       |

| 19.5.3  | 消去ブロック指定レジスタ 1 (EBR1)                  |       |

| 19.5.4  | 消去プロック指定レジスタ 2 (EBR2)                  |       |

|         |                                        |       |

| 19.5.5 | RAM エミュレーションレジスタ(RAMER)                   | 19-13 |

|--------|-------------------------------------------|-------|

| 19.6   | オンボードプログラミングモード                           |       |

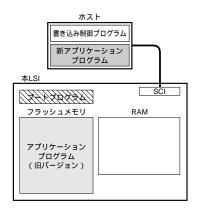

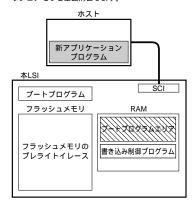

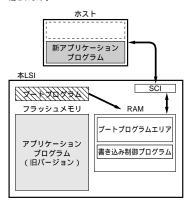

| 19.0   | ブートモード                                    |       |

| 19.6.2 |                                           |       |

| 19.7   | RAMによるフラッシュメモリのエミュレーション                   |       |

| 19.8   | フラッシュメモリの書き込み/消去                          |       |

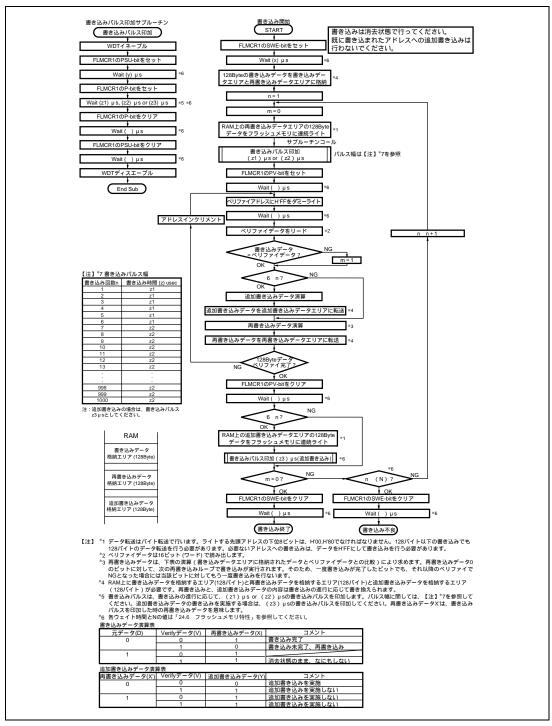

| 19.8.1 | プログラム/プログラムベリファイ                          |       |

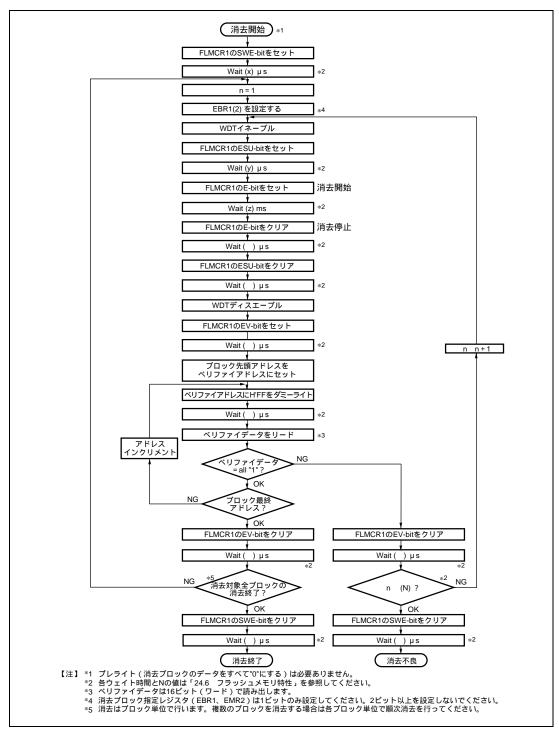

| 19.8.2 | イレース/イレースベリファイ                            |       |

| 19.8.3 | フラッシュメモリの書き込み/消去時の割り込み                    |       |

| 19.9   | 書き込み/消去プロテクト                              |       |

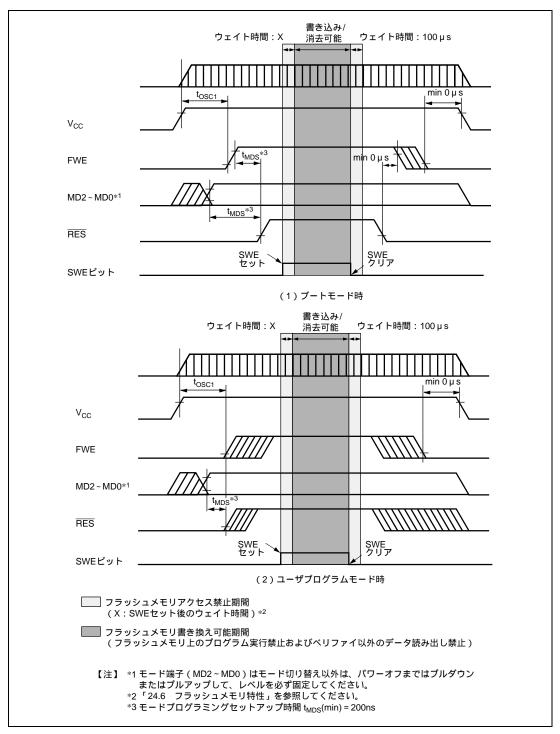

| 19.9.1 | ハードウェアプロテクト                               |       |

| 19.9.2 | ソフトウェアプロテクト                               | 19-25 |

| 19.9.3 | エラープロテクト                                  | 19-25 |

| 19.10  | ライタモード                                    | 19-26 |

| 19.11  | フラッシュメモリの低消費電力動作                          | 19-26 |

| 19.12  | 使用上の注意事項                                  | 19-26 |

| 19.13  | F-ZTATマイコンのマスクROM化時の注意事項                  | 19-32 |

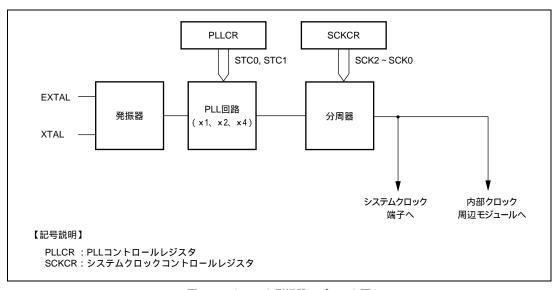

| 21. クロ | 1ック発振器                                    | 21-1  |

| 21.1   | レジスタの説明                                   | 21-2  |

| 21.1.1 | システムクロックコントロールレジスタ(SCKCR)                 | 21-2  |

| 21.1.2 | PLL コントロールレジスタ ( PLLCR )                  | 21-3  |

| 21.2   | 発振器                                       | 21-3  |

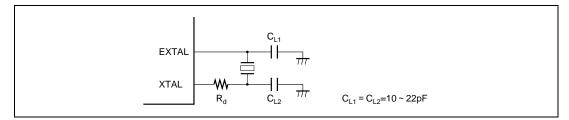

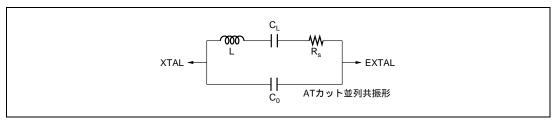

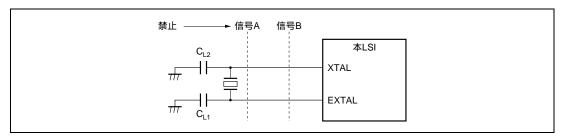

| 21.2.1 | 水晶発振子を接続する方法                              | 21-3  |

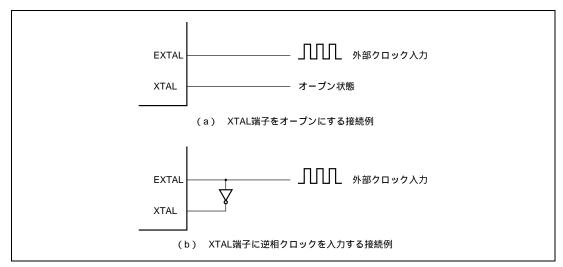

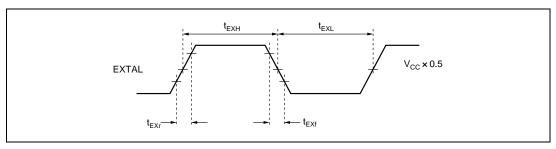

| 21.2.2 | 外部クロックを入力する方法                             | 21-4  |

| 21.3   | PLL回路                                     | 21-6  |

| 21.4   | 分周器                                       | 21-6  |

| 21.5   | 使用上の注意事項                                  | 21-7  |

| 21.5.1 | クロック発振器に関する使用上の注意事項                       | 21-7  |

| 21.5.2 | · • · · · · · · · · · · · · · · · · · ·   |       |

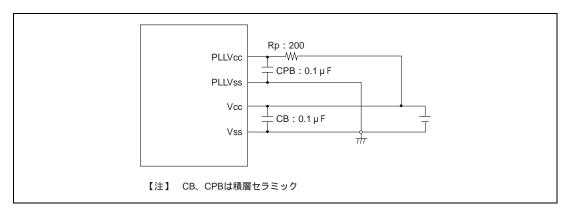

| 21.5.3 | ボード設計上の注意事項                               | 21-7  |

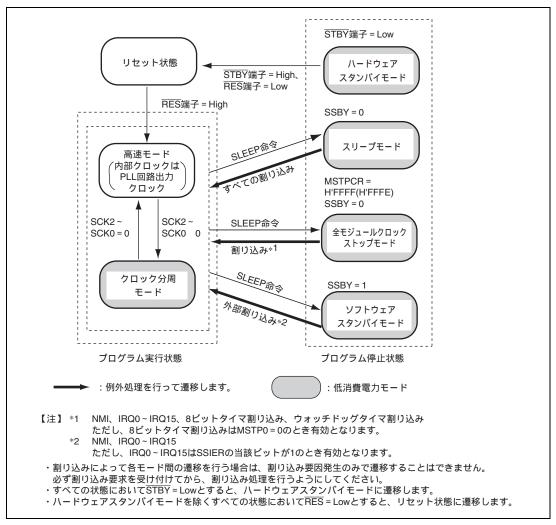

| 22. 低消 | <b>i</b> 費電力状態                            | 22-1  |

| 22.1   | レジスタの説明                                   | 22-4  |

| 22.1.1 | スタンバイコントロールレジスタ ( SBYCR )                 | 22.4  |

| 22.1.2 | , , , , , , , , , , , , , , , , , , , ,   |       |

|        | モジュールストップコントロールレジスタ H、L (MSTPCRH、MSTPCRL) |       |

| 22.2   |                                           | 22-6  |

| 22.2.2                                                 | スリープモード                    | 22-7                   |

|--------------------------------------------------------|----------------------------|------------------------|

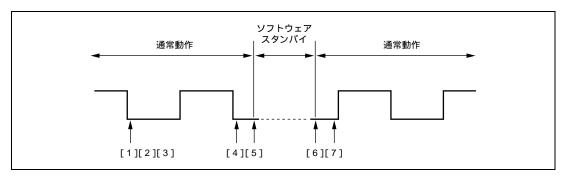

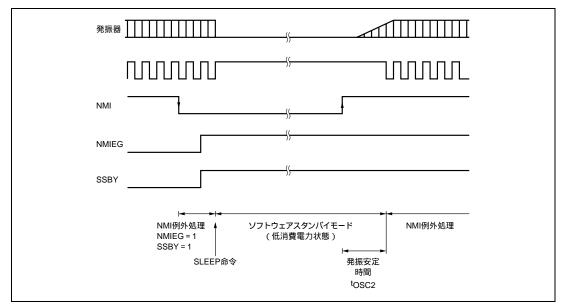

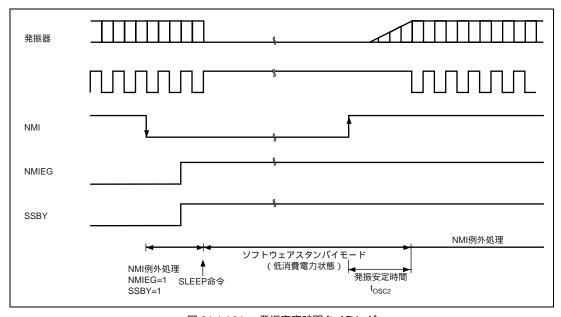

| 22.2.3                                                 | ソフトウェアスタンバイモード             | 22-8                   |

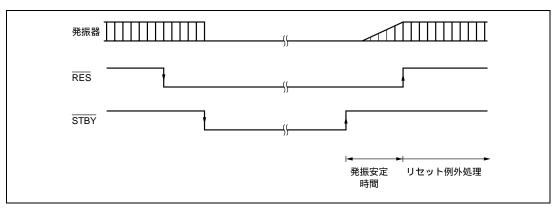

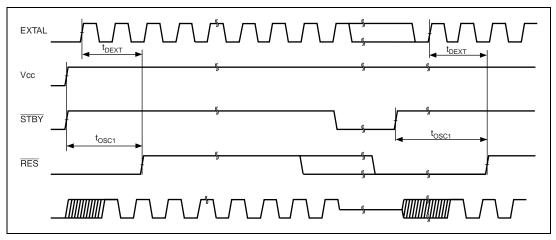

| 22.2.4                                                 | ハードウェアスタンバイモード             | 22-11                  |

| 22.2.5                                                 | モジュールストップモード               | 22-12                  |

| 22.2.6                                                 | 全モジュールクロックストップモード          | 22-12                  |

| 22.3                                                   | クロック出力制御                   | 22-12                  |

| 22.4                                                   | 使用上の注意事項                   | 22-13                  |

| 22.4.1                                                 | I/O ポートの状態                 | 22-13                  |

| 22.4.2                                                 | 発振安定待機中の消費電流               | 22-13                  |

| 22.4.3                                                 | EXDMAC、DMAC、DTC のモジュールストップ | 22-13                  |

| 22.4.4                                                 | 内蔵周辺モジュールの割り込み             | 22-13                  |

| 22.4.5                                                 | MSTPCR のライト                | 22-13                  |

|                                                        |                            |                        |

| 23. レシ                                                 | ブスター覧                      | 23-1                   |

| 23.1                                                   | レジスタアドレス一覧(アドレス順)          | 23-2                   |

| 23.2                                                   | レジスタビット一覧                  | 23-11                  |

| 23.3                                                   | 各動作モードにおけるレジスタの状態          | 23-24                  |

|                                                        |                            |                        |

| 24. 電気                                                 | 〔的特性                       | 24-1                   |

| 24.1                                                   | 絶対最大定格                     |                        |

|                                                        |                            | 24-1                   |

| 24.2                                                   | DC特性                       |                        |

| 24.2<br>24.3                                           | DC特性AC特性                   | 24-2                   |

|                                                        |                            | 24-2                   |

| 24.3                                                   | AC特性                       |                        |

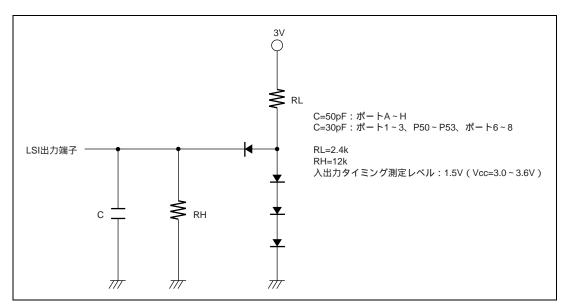

| 24.3<br>24.4                                           | AC特性                       | 24-2<br>24-39<br>24-39 |

| 24.3<br>24.4<br>24.5                                   | AC特性<br>A/D变換特性<br>D/A变換特性 |                        |

| 24.3<br>24.4<br>24.5<br>24.6<br>24.7                   | AC特性                       | 24-2                   |

| 24.3<br>24.4<br>24.5<br>24.6<br>24.7                   | AC特性                       |                        |

| 24.3<br>24.4<br>24.5<br>24.6<br>24.7<br>付録             | AC特性                       |                        |

| 24.3<br>24.4<br>24.5<br>24.6<br>24.7<br>付録<br>A.<br>B. | AC特性                       |                        |

| 24.3<br>24.4<br>24.5<br>24.6<br>24.7<br>付録             | AC特性                       |                        |

| 24.3<br>24.4<br>24.5<br>24.6<br>24.7<br>付録<br>A.<br>B. | AC特性                       |                        |

## 図目次

| 1. | 概要…    |                        | 1-1  |

|----|--------|------------------------|------|

|    | 図 1.1  | H8S/2678 グループ 内部ブロック図  | 1-3  |

|    | 図 1.2  | H8S/2678R グループ 内部プロック図 | 1-4  |

|    | 図 1.3  | H8S/2678 グループ ピン配置図    |      |

|    | 図 1.4  | H8S/2678R グループ ピン配置図   |      |

| 2. | CPU    |                        | 2-1  |

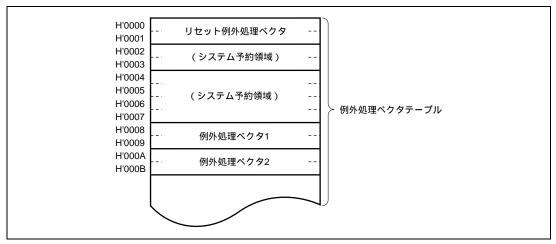

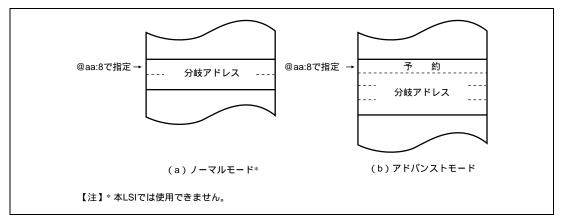

|    | 図 2.1  | 例外処理ベクタテーブル(ノーマルモード)   | 2-5  |

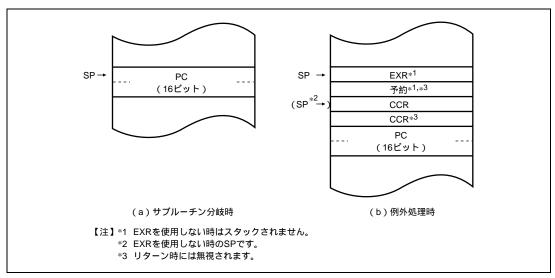

|    | 図 2.2  | ノーマルモードのスタック構造         | 2-5  |

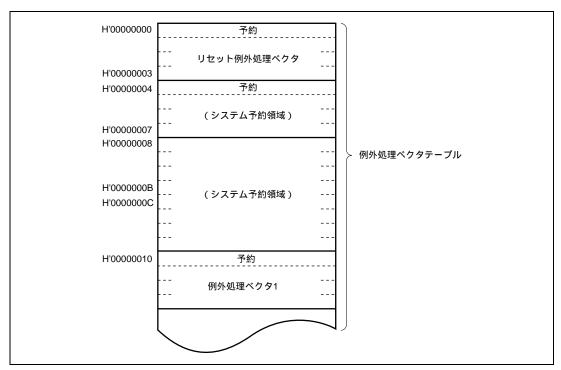

|    | 図 2.3  | 例外処理ベクタテーブル(アドバンストモード) | 2-6  |

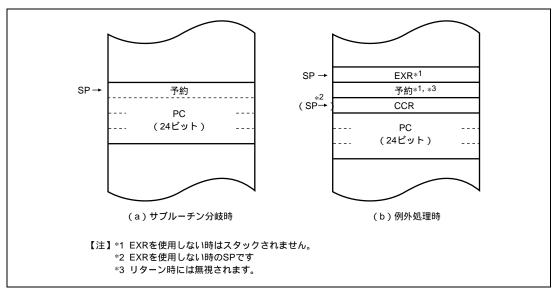

|    | 図 2.4  | アドバンストモードのスタック構造       | 2-7  |

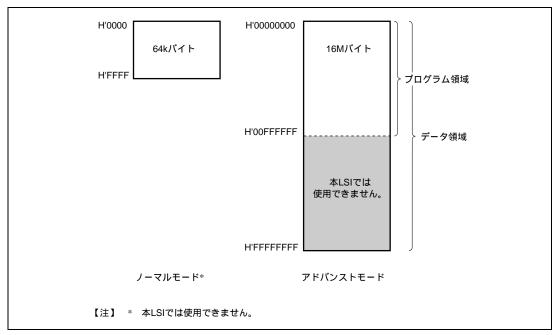

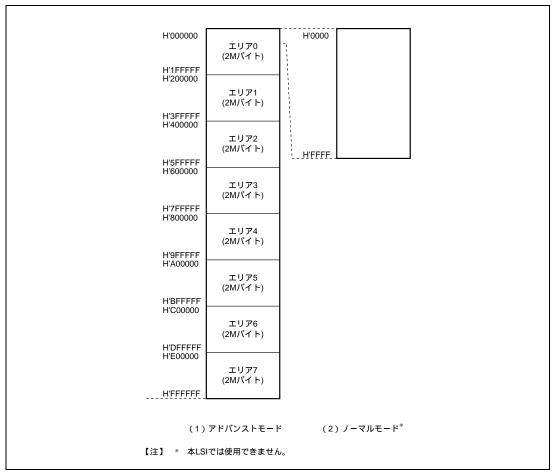

|    | 図 2.5  | アドレス空間                 | 2-8  |

|    | 図 2.6  | CPU 内部レジスタ構成           | 2-9  |

|    | 図 2.7  | 汎用レジスタの使用方法            | 2-10 |

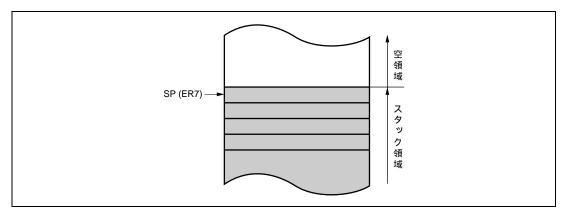

|    | 図 2.8  | スタックの状態                | 2-11 |

|    | 図 2.9  | 汎用レジスタのデータ形式 (1)       | 2-14 |

|    | 図 2.9  | 汎用レジスタのデータ形式 (2)       | 2-15 |

|    | 図 2.10 | メモリ上でのデータ形式            | 2-16 |

|    | 図 2.11 | 命令フォーマットの例             | 2-28 |

|    | 図 2.12 | メモリ間接による分岐アドレスの指定      | 2-32 |

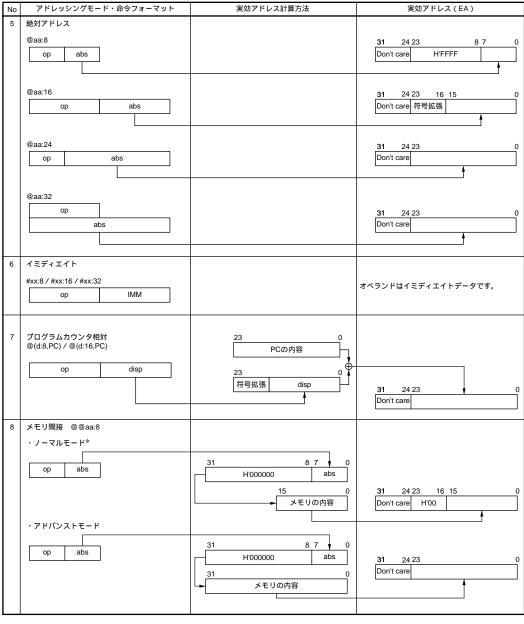

|    | 図 2.13 | 状態遷移図                  | 2-36 |

| 3. | MCU I  | 動作モード                  | 3-1  |

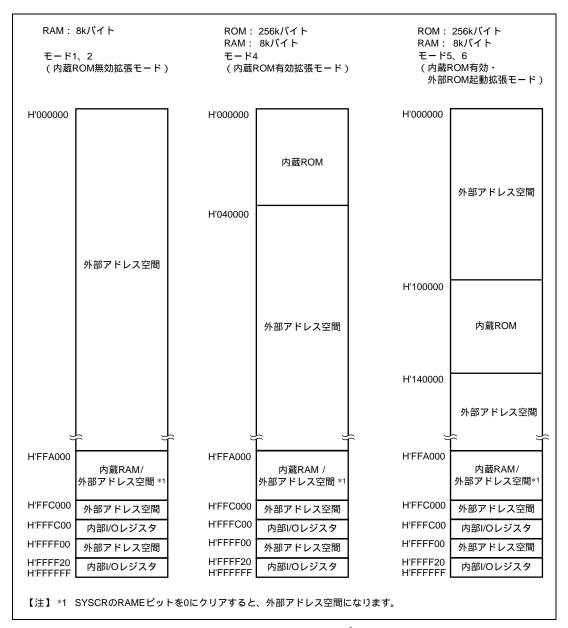

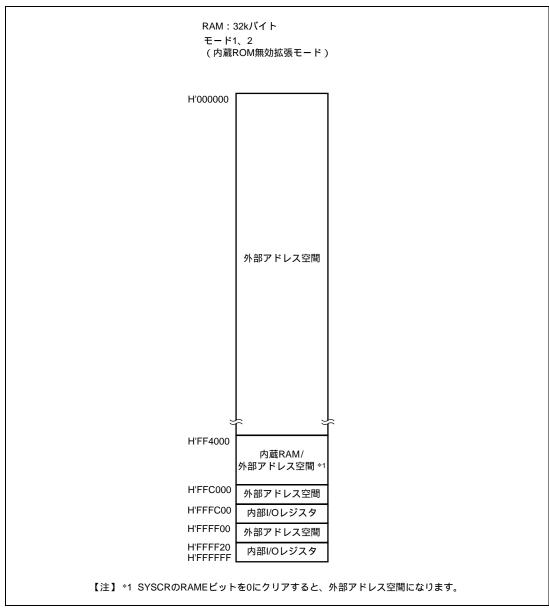

|    | 図 3.1  | H8S/2676 アドレスマップ (1)   | 3-8  |

|    | 図 3.1  | H8S/2676 アドレスマップ ( 2 ) | 3-9  |

|    | 図 3.1  | H8S/2676 アドレスマップ (3)   | 3-10 |

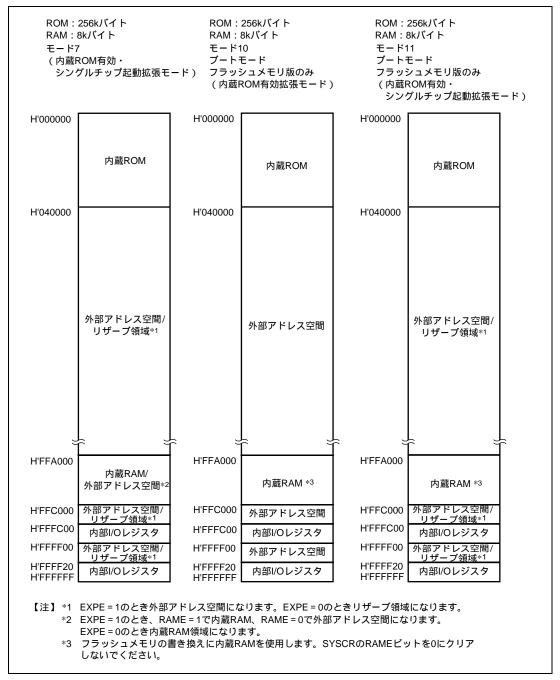

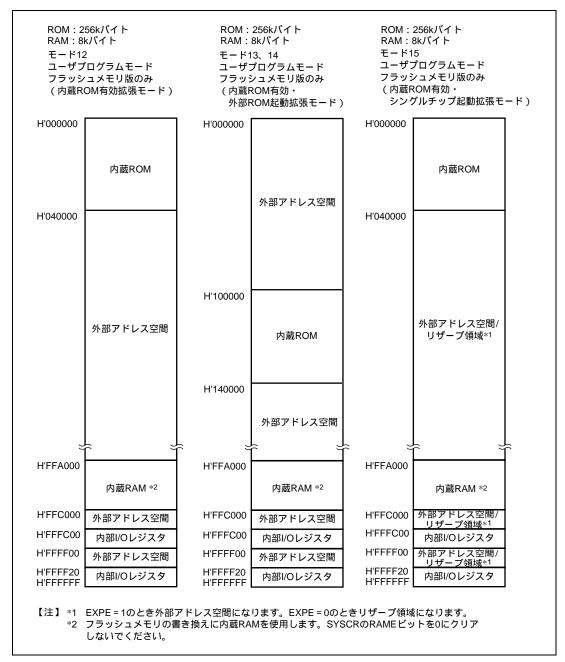

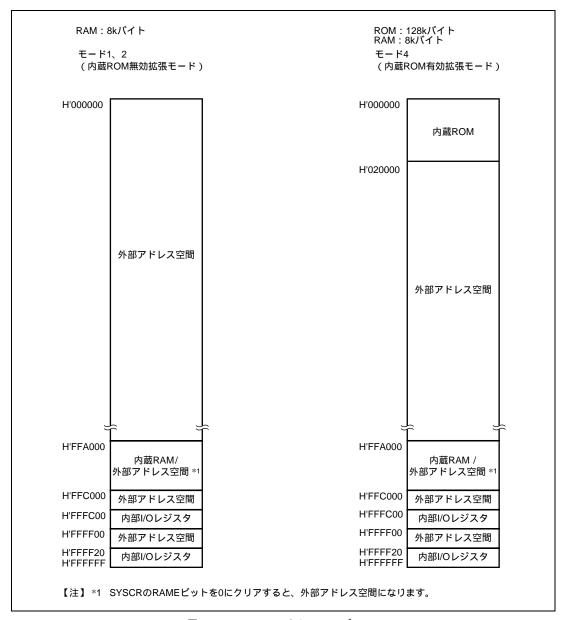

|    | 図 3.2  | H8S/2675 アドレスマップ (1)   | 3-11 |

|    | 図 3.2  | H8S/2675 アドレスマップ ( 2 ) | 3-12 |

|    | 図 3.3  | H8S/2673 アドレスマップ (1)   | 3-13 |

|    | 図 3.3  | H8S/2673 アドレスマップ (2)   | 3-14 |

|    | 図 3.4  | H8S/2670 アドレスマップ       | 3-15 |

|    | 図 3.5  | H8S/2674R アドレスマップ      | 3-16 |

| 4. | 例外処Ŧ   | 里                                                    | 4-1  |

|----|--------|------------------------------------------------------|------|

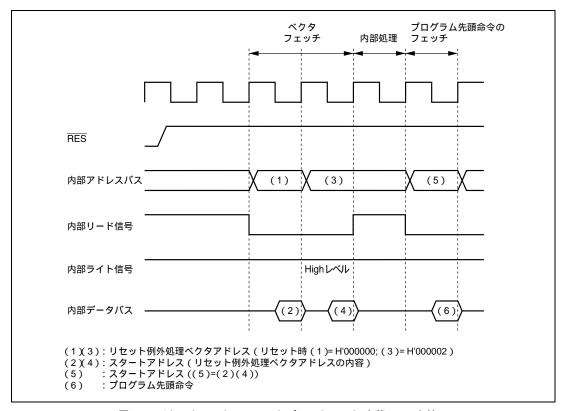

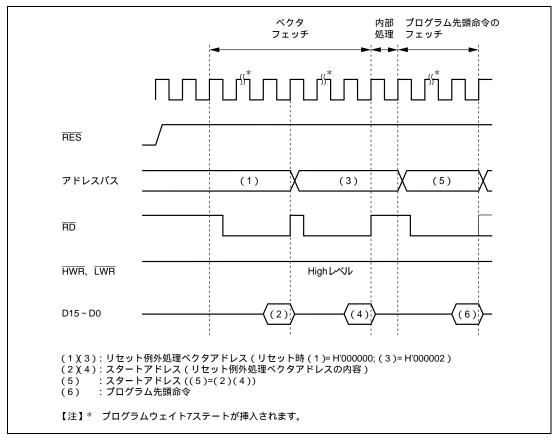

|    | 図 4.1  | リセットシーケンス(アドバンストモード/内蔵 ROM 有効)                       | 4-4  |

|    | 図 4.2  | リセットシーケンス(アドバンストモード/内蔵 ROM 無効)                       | 4-5  |

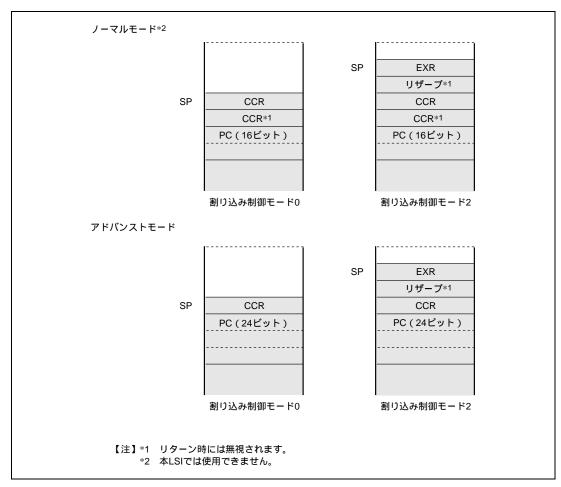

|    | 図 4.3  | 例外処理終了後のスタックの状態                                      | 4-8  |

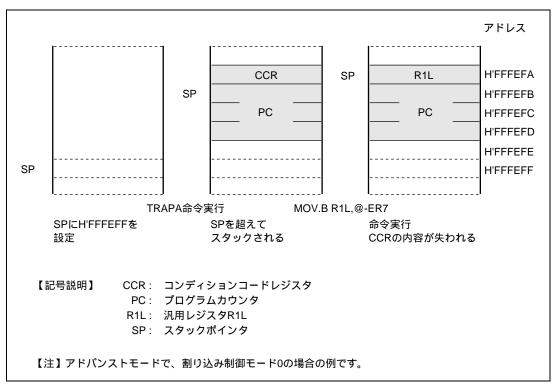

|    | 図 4.4  | SP を奇数に設定したときの動作                                     | 4-9  |

| 5. | 割り込む   | <del>ゕ</del> コントローラ                                  | 5-1  |

|    | 図 5.1  | 割り込みコントローラのブロック図                                     | 5-2  |

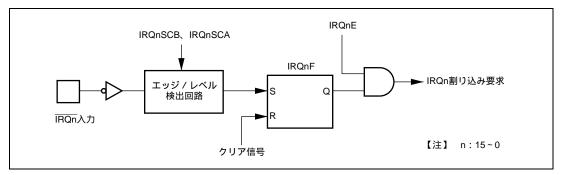

|    | 図 5.2  | IRQ15~IRQ0 割り込みのブロック図                                | 5-15 |

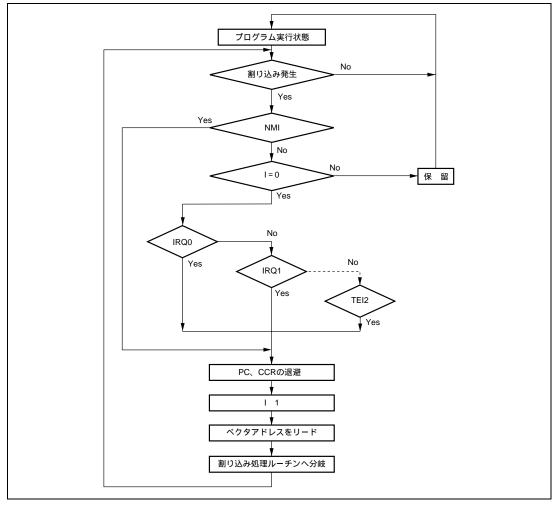

|    | 図 5.3  | 割り込み制御モード 0 の割り込み受け付けまでのフロー                          | 5-21 |

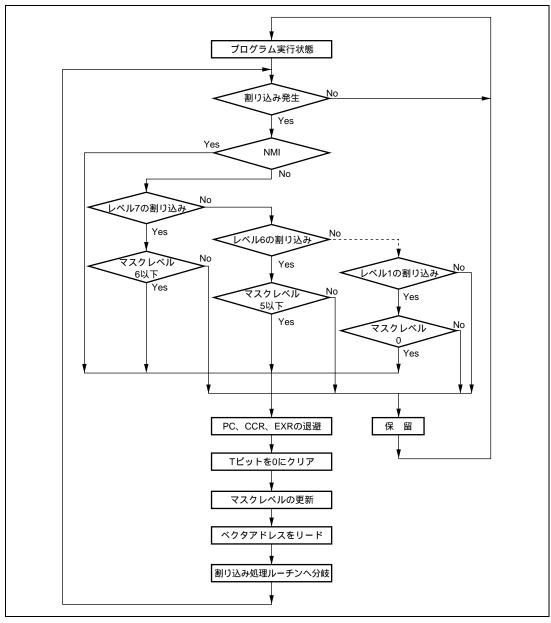

|    | 図 5.4  | 割り込み制御モード2の割り込み受け付けまでのフロー                            | 5-23 |

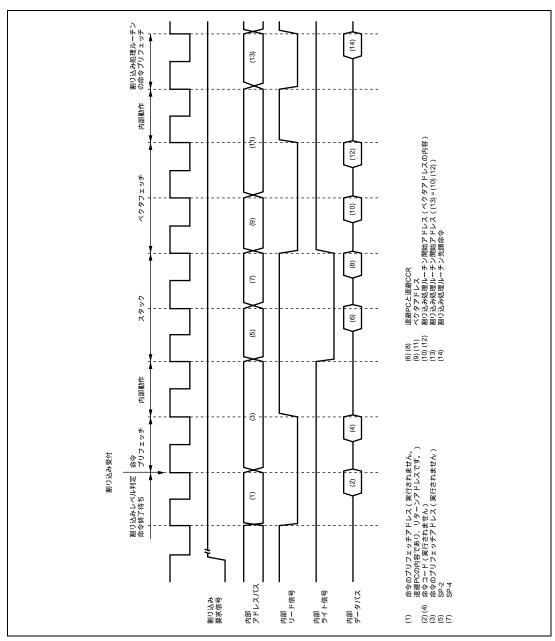

|    | 図 5.5  | 割り込み例外処理                                             | 5-24 |

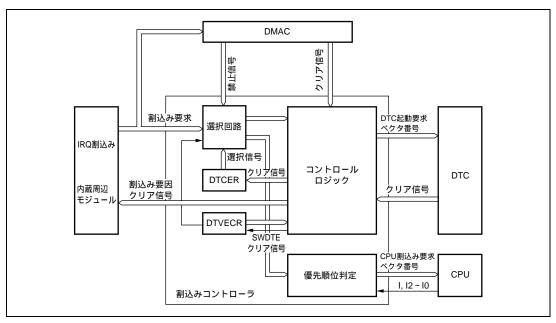

|    | 図 5.6  | DTC、DMAC と割り込みコントローラ                                 | 5-26 |

|    | 図 5.7  | 割り込みの発生とディスエーブルの競合                                   | 5-28 |

| 6. | バスコ    | ントローラ(BSC)                                           | 6-1  |

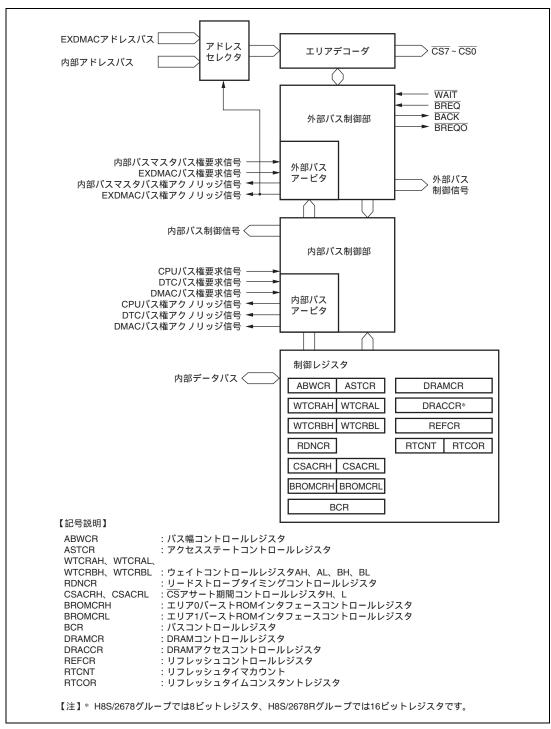

|    | 図 6.1  | バスコントローラのブロック図                                       | 6-2  |

|    | 図 6.2  | リードストローブネゲートタイミング (3 ステートアクセス空間の場合)                  | 6-11 |

|    | 図 6.3  | CS、アドレスアサート期間拡張 (3 ステートアクセス空間、RDNn=0 の場合)            | 6-12 |

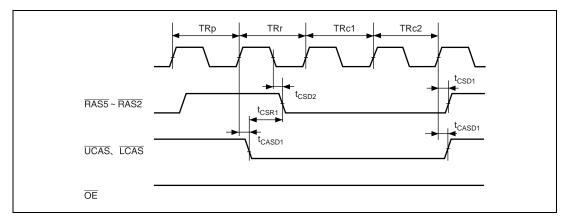

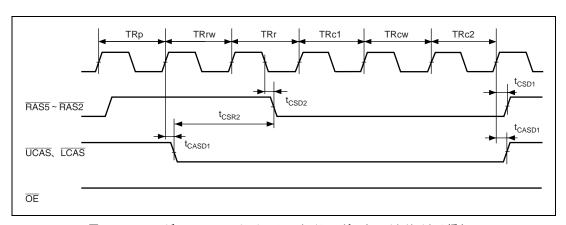

|    | 図 6.4  | RAS 信号アサートタイミング<br>(カラムアドレス出力サイクル 2 ステート、フルアクセスする場合) | 6-19 |

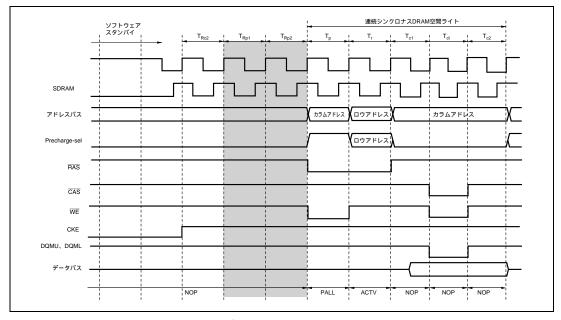

|    | 図 6.5  | 連続シンクロナス DRAM 空間ライトアクセス時の CAS レイテンシ制御サイクル            |      |

|    |        | 無効タイミング ( CAS レイテンシ 2 の場合 )                          | 6-22 |

|    | 図 6.6  | エリア分割の様子                                             | 6-26 |

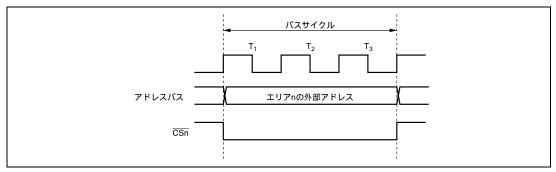

|    | 図 6.7  | <u>CSn</u> 信号出力タイミング (n=0~7)                         | 6-30 |

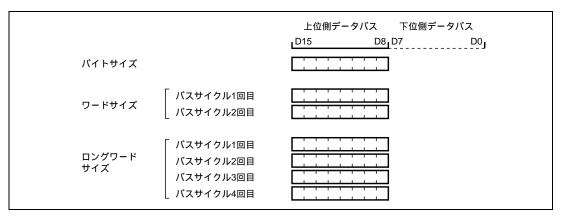

|    | 図 6.8  | アクセスサイズとデータアライメント制御(8 ビットアクセス空間)                     | 6-31 |

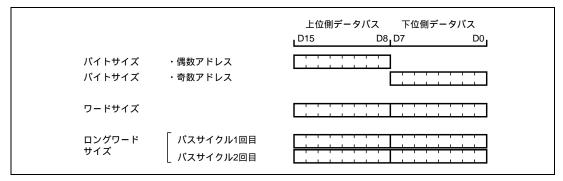

|    | 図 6.9  | アクセスサイズとデータアライメント制御(16 ビットアクセス空間)                    | 6-32 |

|    | 図 6.10 | 8 ビット 2 ステートアクセス空間のバスタイミング                           | 6-33 |

|    | 図 6.11 | 8 ビット 3 ステートアクセス空間のバスタイミング                           | 6-34 |

|    | 図 6.12 | 16 ビット 2 ステートアクセス空間のバスタイミング(偶数アドレスバイトアクセス)           | 6-35 |

|    | 図 6.13 | 16 ビット 2 ステートアクセス空間のバスタイミング ( 奇数アドレスバイトアクセス )        | 6-36 |

|    | 図 6.14 | 16 ビット 2 ステートアクセス空間のバスタイミング(ワードアクセス)                 | 6-37 |

|    | 図 6.15 | 16 ビット 3 ステートアクセス空間のバスタイミング(偶数アドレスバイトアクセス)           | 6-38 |

|    | 図 6.16 | 16 ビット 3 ステートアクセス空間のバスタイミング ( 奇数アドレスバイトアクセス )        |      |

|    | 図 6.17 | 16 ビット 3 ステートアクセス空間のバスタイミング(ワードアクセス)                 |      |

|    | 図 6.18 | ウェイトステート挿入タイミング例                                     |      |

|    | 図 6.19 | リードストローブタイミング例                                       |      |

|    | 図 6.20 | チップセレクトアサート期間拡張時タイミング例                               |      |

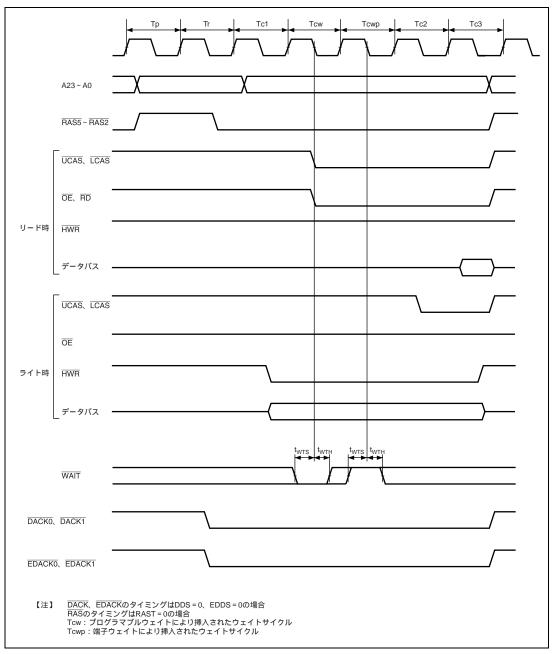

|    | 図 6.21 | DRAM 基本アクセスタイミング(RAST = 0、CAST = 0 の場合)              |      |

|    |        |                                                      |      |

| 図 6.22        | カラムアドレス出力サイクル 3 ステートの場合のアクセスタイミング例<br>(RAST = 0 の場合)                               | 6-47 |

|---------------|------------------------------------------------------------------------------------|------|

| 図 6.23        | RAS 信号が Tr ステートの先頭から Low レベルとなる場合のアクセスタイミング例<br>(CAST = 0 の場合)                     | 6-48 |

| 図 6.24        | ロウアドレス出力保持ステート数が 1 ステート時のタイミング例                                                    |      |

| ₩ <i>(</i> 25 | (RAST=0、CAST=0の場合)                                                                 |      |

| 図 6.25        | プリチャージサイクル2ステート時のタイミング例(RAST=0、CAST=0の場合)                                          |      |

| 図 6.26        | ウェイトステート挿入タイミング例(カラムアドレス出力2ステートの場合)                                                |      |

| 図 6.27        | ウェイトステート挿入タイミング例 (カラムアドレス出力 3 ステートの場合)                                             | 6-53 |

| 図 6.28        | CAS2 本方式の制御タイミング<br>(上位バイトライトアクセス時、RAST = 0、CAST = 0 の場合)                          | 6-54 |

| 図 6.29        | CAS2 本方式の接続例                                                                       | 6-54 |

| 図 6.30        | 高速ページモードの動作タイミング(RAST = 0、CAST = 0 の場合)                                            | 6-55 |

| 図 6.31        | 高速ページモードの動作タイミング(RAST = 0、CAST = 1 の場合)                                            | 6-56 |

| 図 6.32        | RAS ダウンモードの動作タイミング例(RAST = 0、CAST = 0 の場合)                                         | 6-57 |

| 図 6.33        | RAS アップモードの動作タイミング例(RAST = 0、CAST = 0 の場合)                                         | 6-58 |

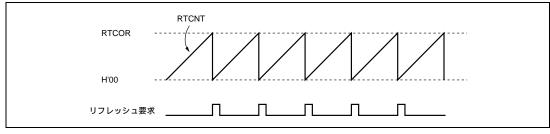

| 図 6.34        | RTCNT の動作                                                                          | 6-59 |

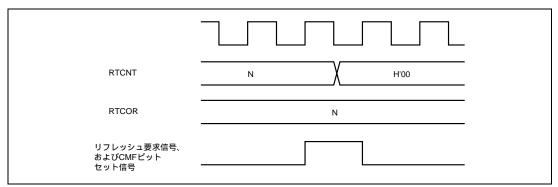

| 図 6.35        | コンペアマッチのタイミング                                                                      | 6-59 |

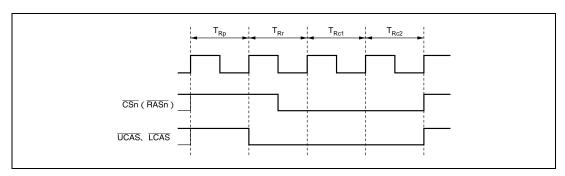

| 図 6.36        | CBR リフレッシュタイミング                                                                    | 6-59 |

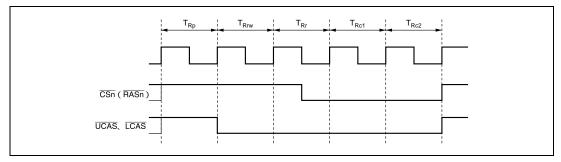

| 図 6.37        | CBR リフレッシュタイミング (RCW1=0、RCW0=1、RLW1=0、RLW0=0の場合)                                   | 6-60 |

| 図 6.38        | CBR リフレッシュタイミング例(CBRM=1 のとき)                                                       | 6-60 |

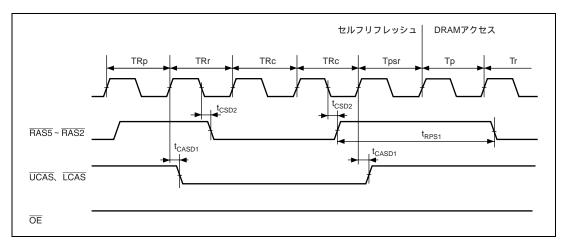

| 図 6.39        | セルフリフレッシュタイミング                                                                     | 6-61 |

| 図 6.40        | セルフリフレッシュ直後のプリチャージ時間を2ステート増加した場合のタイミング例                                            | 6-62 |

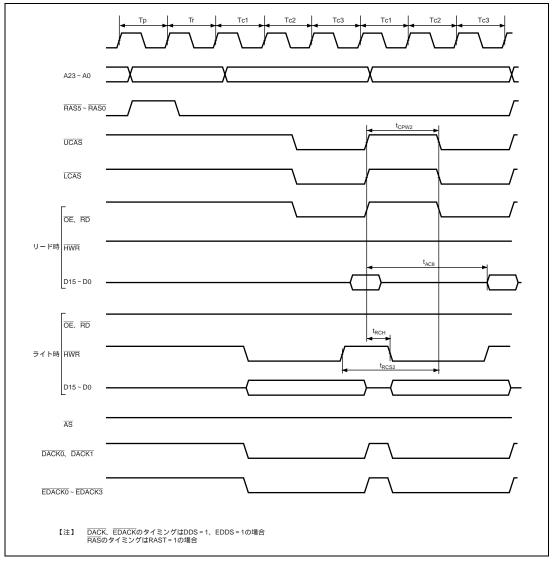

| 図 6.41        | DDS = 1 または EDDS = 1 の場合の DACK、EDACK 出力タイミング例<br>(RAST = 0、CAST = 0 の場合)           | 6-63 |

| 図 6.42        | DDS = 0 または EDDS = 0 の場合の DACK、EDACK 出力タイミング例<br>(RAST = 0、CAST = 1 の場合)           | 6-64 |

| 図 6.43        | と SDRAM の関係 ( PLL 周波数逓倍率×1、×2 の場合 )                                                | 6-68 |

| 図 6.44        | シンクロナス DRAM 基本アクセスタイミング ( CAS レイテンシ 1 の場合 )                                        | 6-69 |

| 図 6.45        | CAS レイテンシ制御タイミング ( SDWCD = 0、CAS レイテンシ 3 の場合 )                                     | 6-71 |

| 図 6.46        | ロウアドレス出力保持ステート数が 1 ステート時のタイミング例<br>( RCD1 = 0、RCD0 = 1、SDWCD = 0、CAS レイテンシ 2 の場合 ) | 6-72 |

| 図 6.47        | プリチャージサイクル 2 ステート時のタイミング例<br>(TPC1 = 0、TPC0 = 1、SDWCD = 0、CAS レイテンシ 2 の場合)         |      |

| 図 6.48        | ( IPCI = 0、 IPCO = 1、 SDWCD = 0、 CAS レイナフシ 2 の場合 )                                 |      |

| 図 6.49        | DQMU、DQML による制御タイミング<br>(上位パイトライトアクセス時、SDWCD = 0 の場合、CAS レイテンシ 2 の場合 )             |      |

| 図 6.50        | DQMU、DQML による制御タイミング<br>(下位バイトリードアクセス時、CAS レイテンシ 2 の場合 )                           |      |

| 図 6.51        | DQMU、DQML によるパイト制御の接続例                                                             |      |

| 図 6.52        | バーストアクセスの動作タイミング(BE=1、SDWCD=0、CAS レイテンシ 2 の場合)                                     |      |

| 図 6.53        | RAS ダウンモードの動作タイミング例 ( BE = 1、CAS レイテンシ 2 の場合 )                                          | 6-80  |

|---------------|-----------------------------------------------------------------------------------------|-------|

| 図 6.54        | オートリフレッシュタイミング                                                                          | 6-81  |

| 図 6.55        | オートリフレッシュタイミング                                                                          |       |

|               | (TPC=1、TPC0=1、RCW1=0、RCW0=1の場合)                                                         | 6-82  |

| 図 6.56        | オートリフレッシュタイミング                                                                          |       |

|               | (TPC=0、TPC0=0、RLW1=0、RLW0=1の場合)                                                         | 6-83  |

| 図 6.57        | セルフリフレッシュタイミング                                                                          |       |

|               | (TPC1=1、TPC0=0、RCW1=0、RCW0=0、RLW1=0、RLW0=0の場合)                                          | 6-84  |

| 図 6.58        | セルフリフレッシュ直後のプリチャージ時間を2ステート増加した場合のタイミング例                                                 |       |

|               | (TPCS2~TPCS0=H'2、TPC1=0、TPC0=0、CAS レイテンシ 2 の場合)                                         |       |

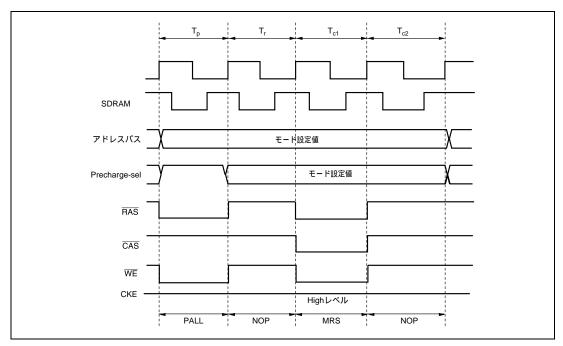

| 図 6.59        | シンクロナス DRAM モード設定タイミング                                                                  |       |

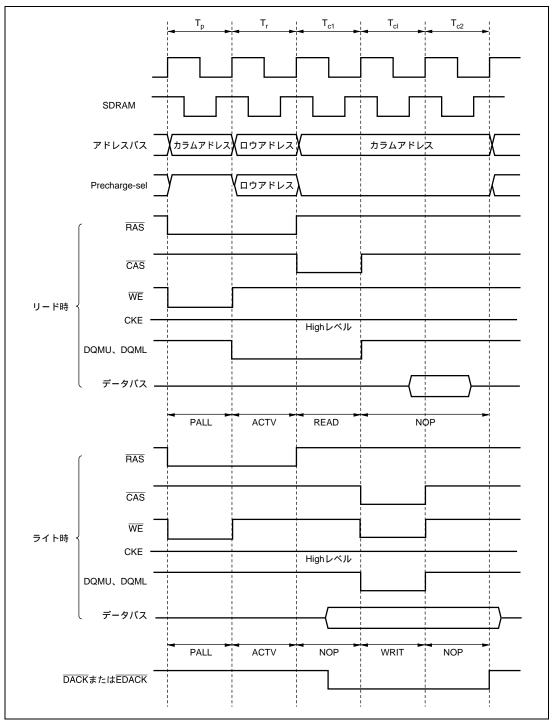

| 図 6.60        | DDS=1 または EDDS=1 の場合の DACK、EDACK 出力タイミング例                                               | 6-87  |

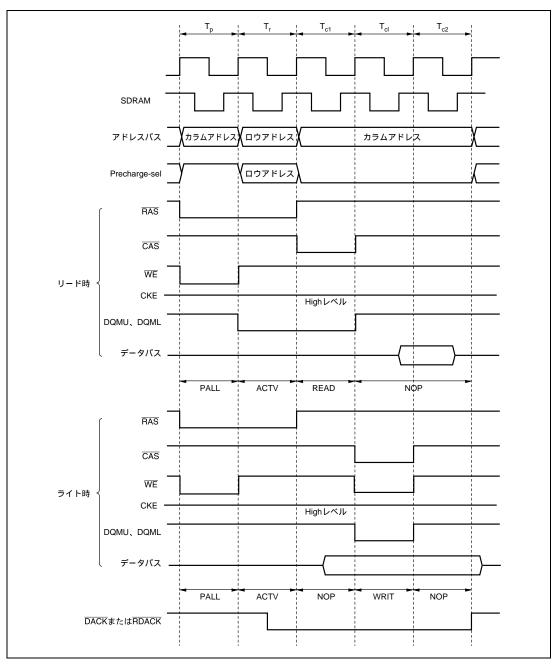

| 図 6.61        | DDS=0 または EDDS=0 の場合の DACK、EDACK 出力タイミング例                                               | 6-89  |

| 図 6.62        | リードデータを2ステート拡張した場合のタイミング例                                                               |       |

|               | (DDS=1またはEDDS=1、RDXC1=0、RDXC0=1、CAS レイテンシ 2 の場合)                                        | 6-90  |

| 図 6.63        | バースト ROM アクセスタイミング例(ASTn = 1、バーストサイクル 2 ステートの場合)                                        | 6-91  |

| 図 6.64        | バースト ROM アクセスタイミング例(ASTn = 0、バーストサイクル 1 ステートの場合)                                        | 6-92  |

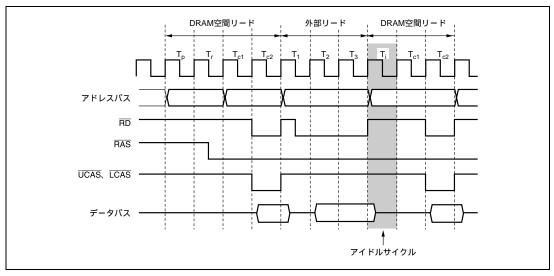

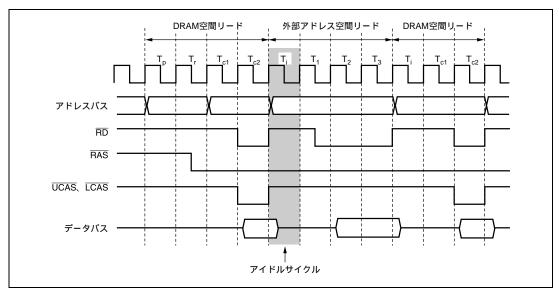

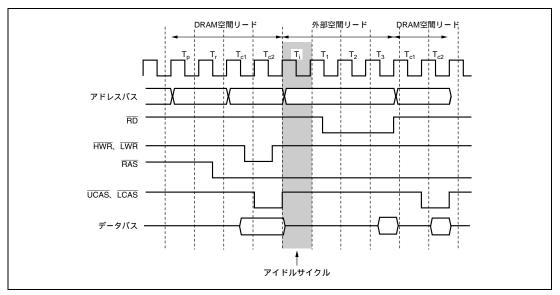

| 図 6.65        | アイドルサイクル動作例(異なるエリア間での連続リード)                                                             | 6-93  |

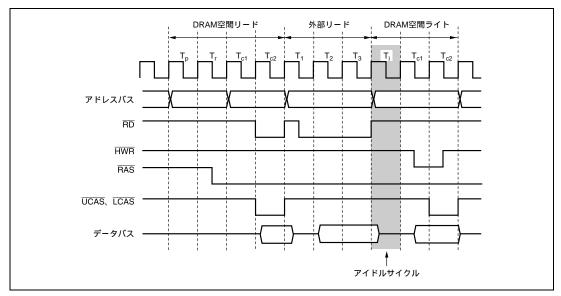

| 図 6.66        | アイドルサイクル動作例(リード後のライト)                                                                   | 6-94  |

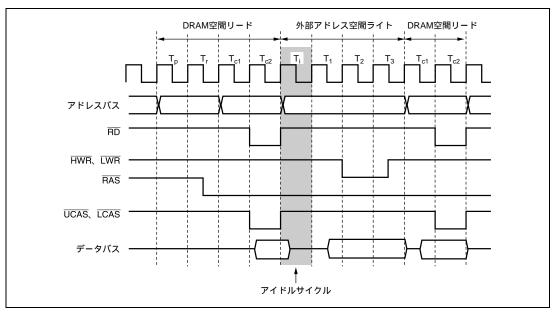

| 図 6.67        | アイドルサイクル動作例(ライト後のリード)                                                                   | 6-95  |

| 図 6.68        | チップセレクト ( CS ) とリード ( RD ) の関係                                                          | 6-95  |

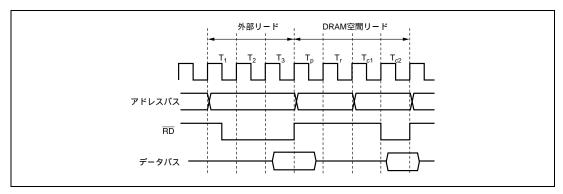

| 図 6.69        | 外部リード後の DRAM フルアクセス例(CAST = 0 の場合)                                                      | 6-96  |

| 図 6.70        | RAS ダウンモード時のアイドルサイクル動作例(異なるエリア間での連続リード)                                                 |       |

|               | (IDLC=0、RAST=0、CAST=0の場合)                                                               | 6-96  |

| 図 6.71        | RAS ダウンモード時のアイドルサイクル動作例(リード後のライト)                                                       |       |

|               | (IDLC=0、RAST=0、CAST=0の場合)                                                               | 6-97  |

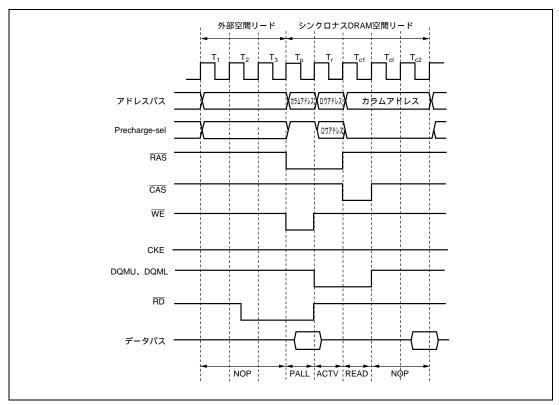

| 図 6.72        | 外部リード後のシンクロナス DRAM フルアクセス例 ( CAS レイテンシ 2 の場合 )                                          | 6-98  |

| 図 6.73        | RAS ダウンモード時のアイドルサイクル動作例(異なるエリアのリード)                                                     |       |

|               | (IDLC=0、CAS レイテンシ 2 の場合)                                                                | 6-99  |

| 図 6.74        | RAS ダウンモード時のアイドルサイクル動作例 ( 異なるエリアのリード )                                                  |       |

|               | ( IDLC = 1、CAS レイテンシ 2 の場合 )                                                            | 6-100 |

| 図 6.75        | RAS ダウンモード時のアイドルサイクル動作例(リード後のライト)                                                       |       |

| _             | (IDLC = 0、CAS レイテンシ 2 の場合)                                                              | 6-101 |

| 図 6.76        | DRAM アクセス後のアイドルサイクル動作例(異なるエリア間での連続リード)                                                  | 6 102 |

|               | (IDLC=0、RAST=0、CAST=0の場合)                                                               | 6-102 |

| 図 6.77        | DRAM アクセス後のアイドルサイクル動作例(リード後のライト)                                                        | ( 102 |

| SW 6 70       | (IDLC=0、RAST=0、CAST=0の場合)                                                               | 0-102 |

| 図 6.78        | DRAM ライトアクセス後のアイドルサイクル動作例<br>(IDLC=0、ICIS1=0、RAST=0、CAST=0 の場合)                         | 6 102 |

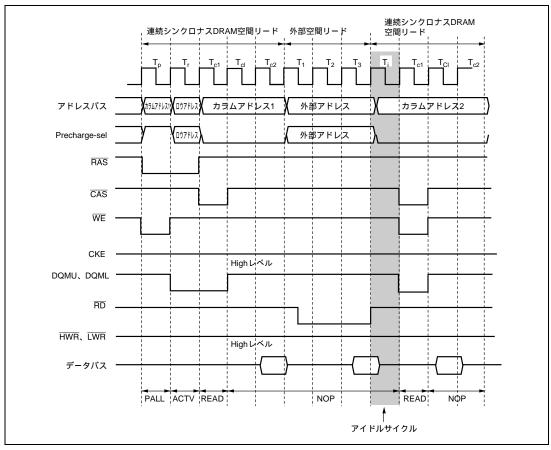

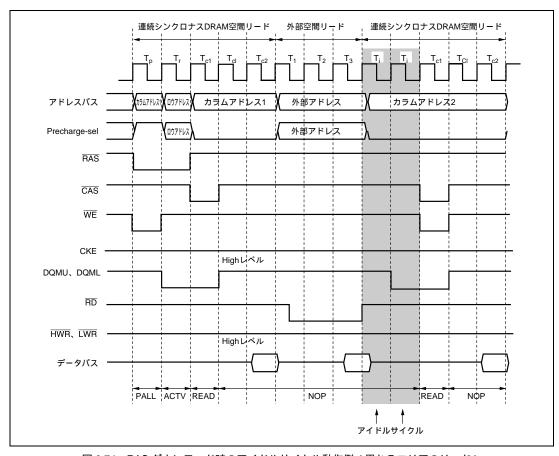

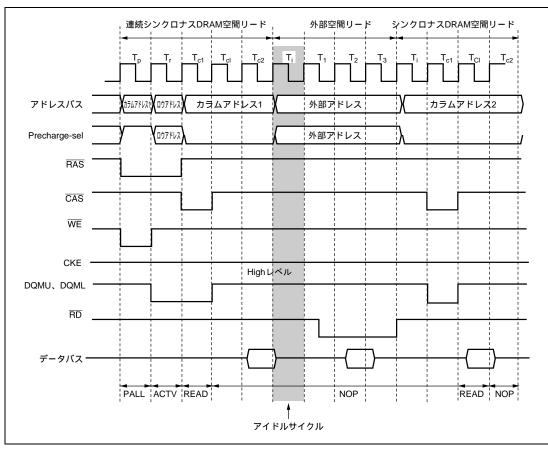

| 図 6.79        | 連続シンクロナス DRAM 空間リードアクセス後のアイドルサイクル動作例                                                    | 0-103 |

| 凶 0./9        | 理                                                                                       | 6-104 |

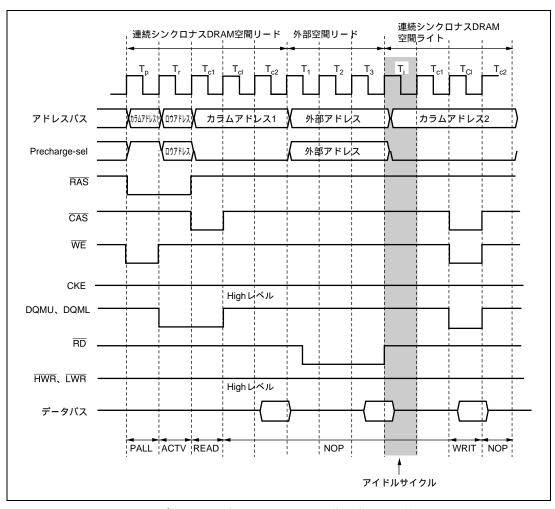

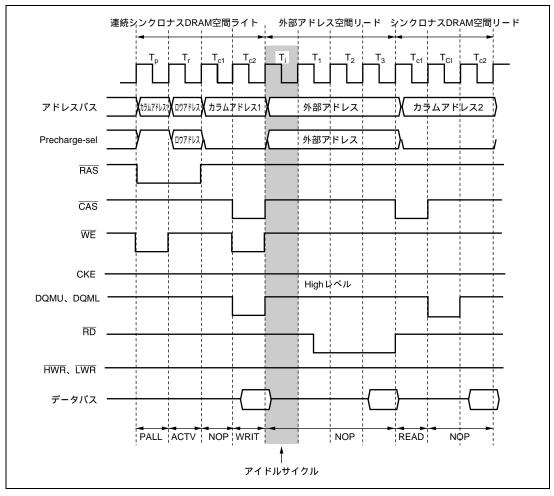

| 図 6.80        | 連続シンクロナス DRAM 空間ライトアクセス後のアイドルサイクル動作例                                                    | 0-104 |

| <u>⊸</u> 0.80 | 注続シフクロテス DRAM 空间フィドアクセス後のアイドルサイクル動作例<br>(IDLC = 0、ICIS1 = 0、SDWCD = 1、CAS レイテンシ 2 の場合 ) | 6-105 |

|    | 図 6.81 | RAS ダウンモードで DRAM 空間へのリードとライトが連続したときに<br>アイドルサイクルを挿入する場合のタイミング例 | 6-107 |

|----|--------|----------------------------------------------------------------|-------|

|    | 図 6.82 | RAS ダウンモードで連続シンクロナス DRAM 空間へのリードとライトが連続したときに                   | 0 107 |

|    | Z 0.02 | アイドルサイクルを挿入する場合のタイミング例                                         |       |

|    |        | (SDWCD=1、CAS レイテンシ 2 の場合)                                      | 6-108 |

|    | 図 6.83 | ライトデータバッファ機能使用時のタイミング例                                         | 6-109 |

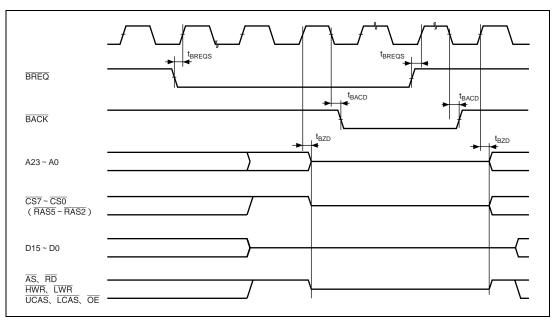

|    | 図 6.84 | バス権解放状態遷移タイミング                                                 | 6-112 |

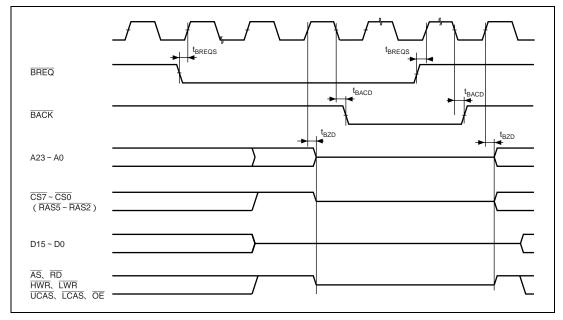

|    | 図 6.85 | シンクロナス DRAM インタフェース時のバス解放状態遷移タイミング                             | 6-113 |

| 7. | DMA ⊐  | ントローラ ( DMAC )                                                 | 7-1   |

|    | 図 7.1  | DMAC のブロック図                                                    | 7-2   |

|    | 図 7.2  | DTC によるレジスタ再設定領域 ( チャネル 0A )                                   | 7-19  |

|    | 図 7.3  | シーケンシャルモードの動作                                                  | 7-25  |

|    | 図 7.4  | シーケンシャルモードの設定手順例                                               | 7-26  |

|    | 図 7.5  | アイドルモードの動作                                                     | 7-27  |

|    | 図 7.6  | アイドルモードの設定手順例                                                  | 7-28  |

|    | 図 7.7  | リピートモードの動作                                                     | 7-30  |

|    | 図 7.8  | リピートモードの設定手順例                                                  | 7-31  |

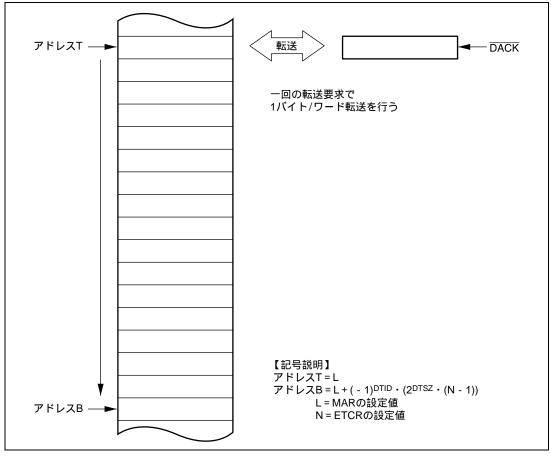

|    | 図 7.9  | シングルアドレスモード ( シーケンシャルモード指定 ) の動作                               | 7-33  |

|    | 図 7.10 | シングルアドレスモード ( シーケンシャルモード指定 ) の設定手順例                            | 7-34  |

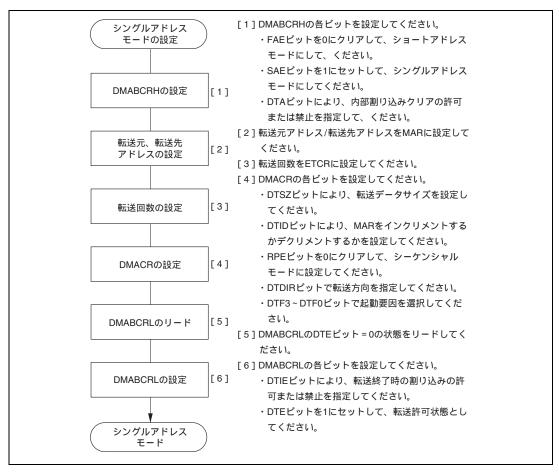

|    | 図 7.11 | ノーマルモードの動作                                                     | 7-36  |

|    | 図 7.12 | ノーマルモードの設定手順例                                                  | 7-37  |

|    | 図 7.13 | ブロック転送モードの動作(BLKDIR = 0)                                       | 7-39  |

|    | 図 7.14 | ブロック転送モードの動作(BLKDIR = 1 )                                      | 7-40  |

|    | 図 7.15 | ブロック転送モードの動作フロー                                                | 7-41  |

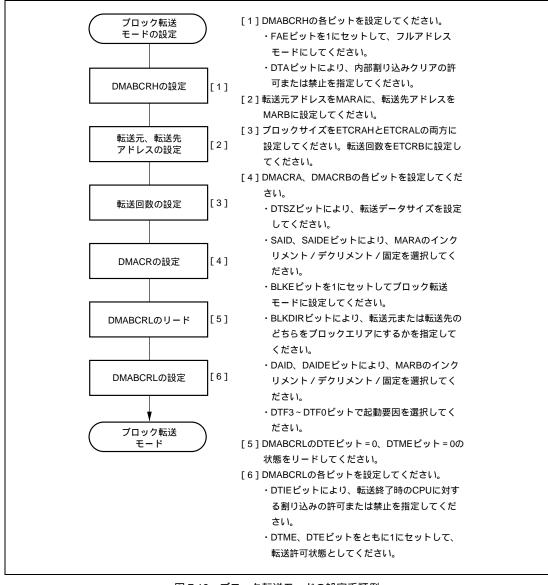

|    | 図 7.16 | ブロック転送モードの設定手順例                                                | 7-42  |

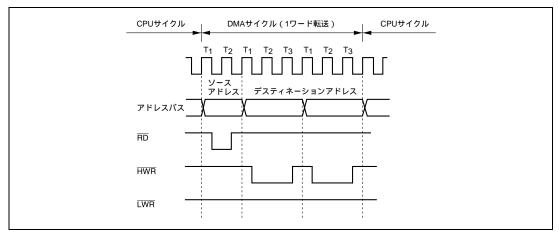

|    | 図 7.17 | DMA 転送バスタイミング例                                                 | 7-43  |

|    | 図 7.18 | ショートアドレスモード転送例                                                 | 7-43  |

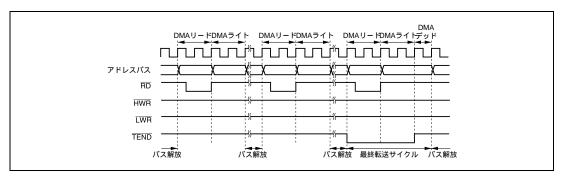

|    | 図 7.19 | フルアドレスモード(サイクルスチール)転送例                                         | 7-44  |

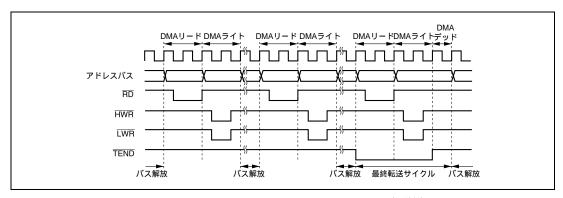

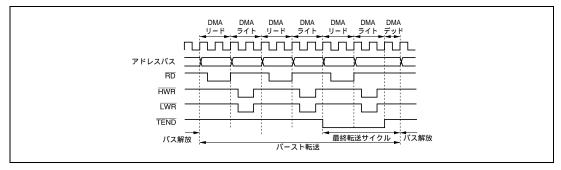

|    | 図 7.20 | フルアドレスモード ( バーストモード ) 転送例                                      | 7-45  |

|    | 図 7.21 | フルアドレスモード(プロック転送モード)転送例                                        | 7-45  |

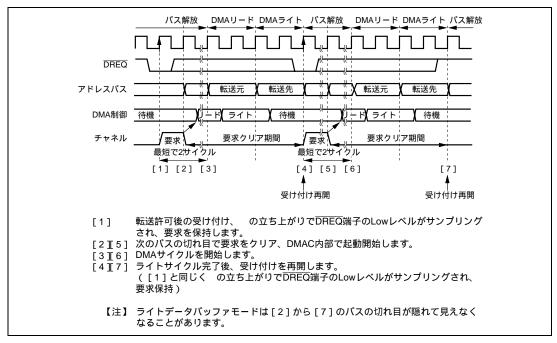

|    | 図 7.22 | DREQ 端子立ち下がりエッジ起動のノーマルモード転送例                                   | 7-46  |

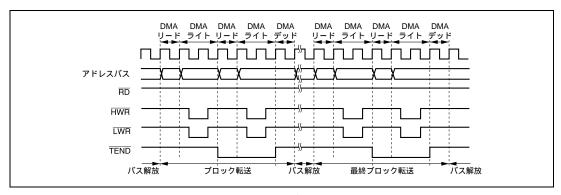

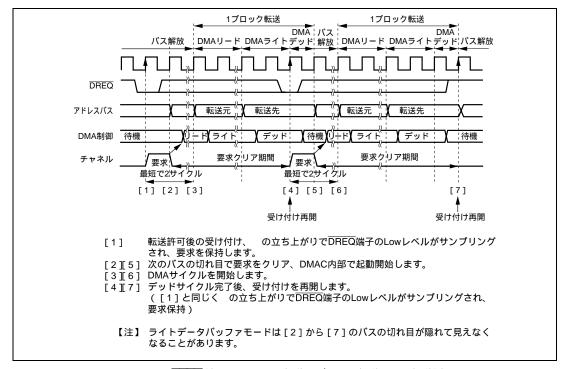

|    | 図 7.23 | DREQ 端子立ち下がりエッジ起動のブロック転送モード転送例                                 | 7-47  |

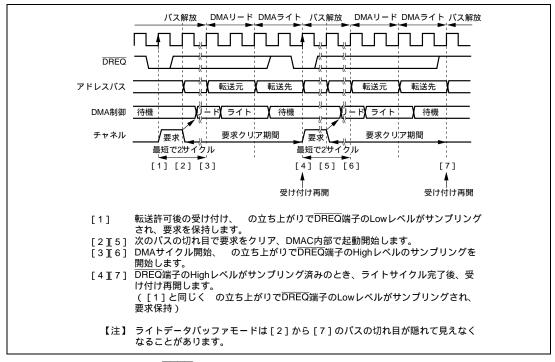

|    | 図 7.24 | DREQ 端子 Low レベル起動のノーマルモード転送例                                   | 7-48  |

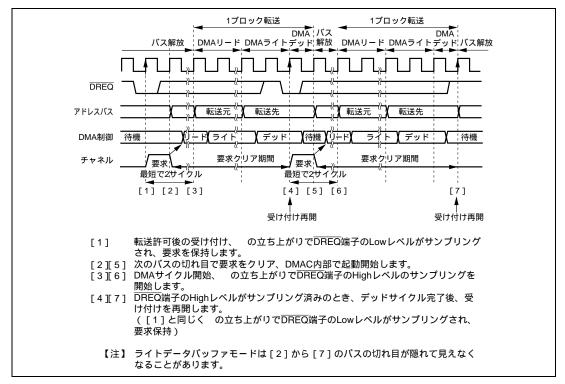

|    | 図 7.25 | DREQ         端子 Low レベル起動のブロック転送モード転送例                         | 7-49  |

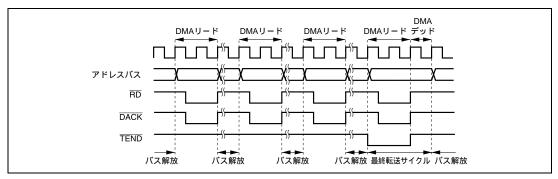

|    | 図 7.26 | シングルアドレスモード(バイトリード)転送例                                         | 7-50  |

|    | 図 7.27 | シングルアドレスモード(ワードリード)転送例                                         | 7-50  |

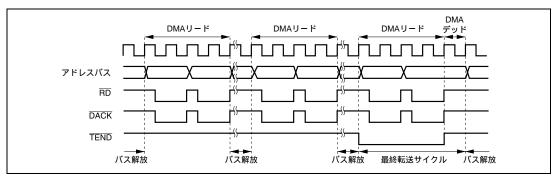

|    | 図 7.28 | シングルアドレスモード(バイトライト)転送例                                         | 7-51  |

|    | 図 7.29 | シングルアドレスモード(ワードライト)転送例                                         | 7-51  |

|    | 図 7.30 | DREQ 端子立ち下がりエッジ起動のシングルアドレスモード転送例                               | 7-52  |

|    | 図 7.31 | DREO 端子 Low レベル起動のシングルアドレスモード転送例                               | 7-53  |

|    | 図 7.32 | ライトデータバッファ機能を用いたデュアルアドレス転送例       | 7-54 |

|----|--------|-----------------------------------|------|

|    | 図 7.33 | ライトデータバッファ機能を用いたシングルアドレス転送例       | 7-54 |

|    | 図 7.34 | 複数チャネル転送例                         | 7-55 |

|    | 図 7.35 | NMI 割り込みにより中断したチャネルの転送継続手順例       | 7-56 |

|    | 図 7.36 | DMAC の強制終了手順例                     | 7-57 |

|    | 図 7.37 | フルアドレスモード解除手順例                    | 7-58 |

|    | 図 7.38 | 転送終了/転送中断割り込みのプロック図               | 7-59 |

|    | 図 7.39 | DMAC のレジスタの更新タイミング                | 7-60 |

|    | 図 7.40 | DMAC レジスタの更新と CPU リードの競合          | 7-61 |

|    | 図 7.41 | TEND 端子に Low レベルが出力されない例          | 7-63 |

| 8. | EXDMA  | コントローラ ( EXDMAC )                 | 8-1  |

|    | 図 8.1  | EXDMAC のブロック図                     | 8-2  |

|    | 図 8.2  | デュアルアドレスモードのタイミング例                | 8-13 |

|    | 図 8.3  | シングルアドレスモードでのデータの流れ               | 8-14 |

|    | 図 8.4  | シングルアドレスモードのタイミング例                | 8-15 |

|    | 図 8.5  | サイクルスチールモードのタイミング例                | 8-17 |

|    | 図 8.6  | バーストモードのタイミング例                    | 8-17 |

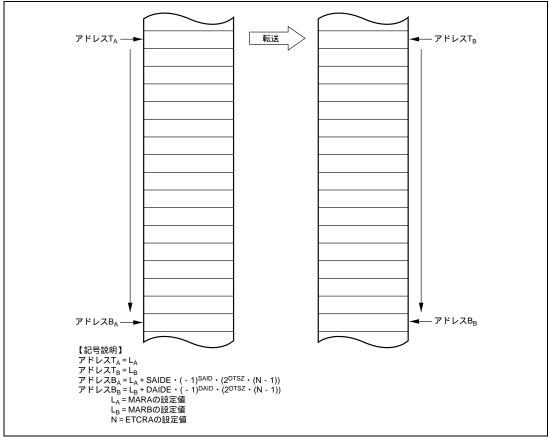

|    | 図 8.7  | ノーマル転送モードの例                       | 8-18 |

|    | 図 8.8  | ブロック転送モードの例                       | 8-19 |

|    | 図 8.9  | リピートエリア機能の例                       | 8-20 |

|    | 図 8.10 | ブロック転送モードとリピートエリア機能を併用したときの例      | 8-21 |

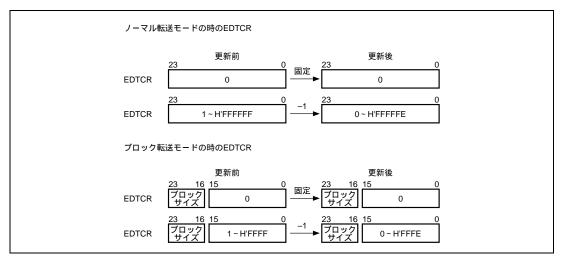

|    | 図 8.11 | ノーマル転送モードとブロック転送モード時の EDTCR の更新動作 | 8-23 |

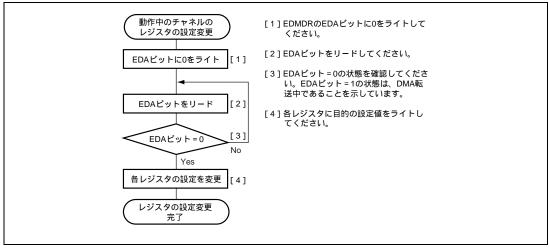

|    | 図 8.12 | 動作中のチャネルのレジスタの設定を変更するときの手順        | 8-24 |

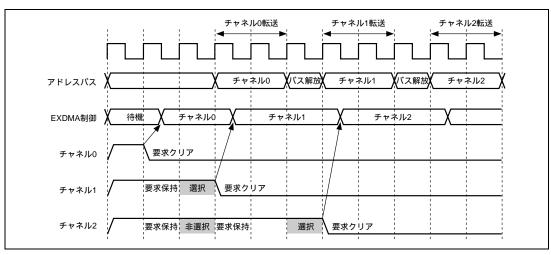

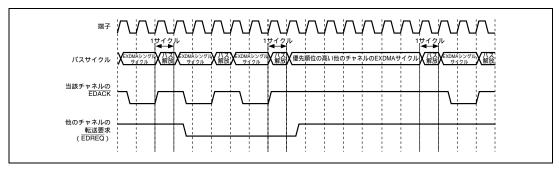

|    | 図 8.13 | チャネルの優先順位のタイミング例                  | 8-25 |

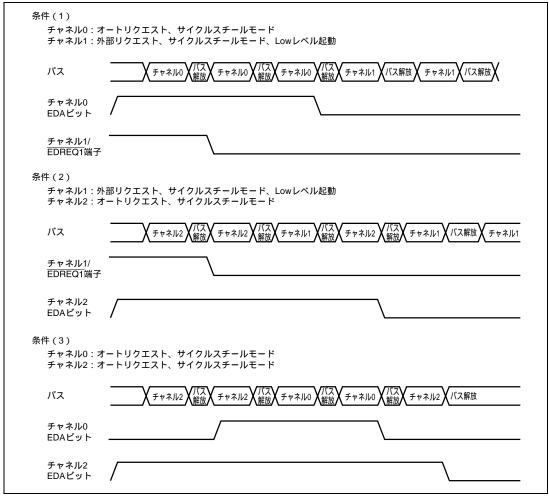

|    | 図 8.14 | チャネルの優先順位のタイミング例                  | 8-26 |

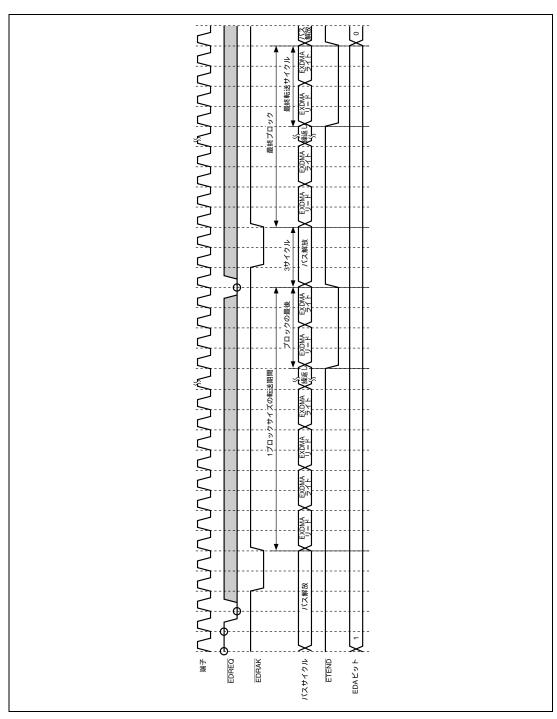

|    | 図 8.15 | ノーマル転送モード ( サイクルスチールモード ) 転送例     | 8-27 |

|    | 図 8.16 | ノーマル転送モード ( バーストモード ) 転送例         | 8-27 |

|    | 図 8.17 | プロック転送モード ( サイクルスチールモード ) 転送例     | 8-28 |

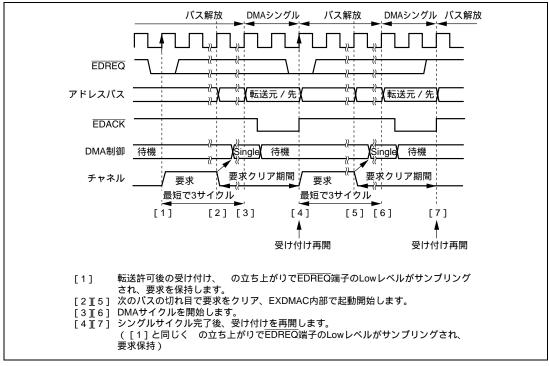

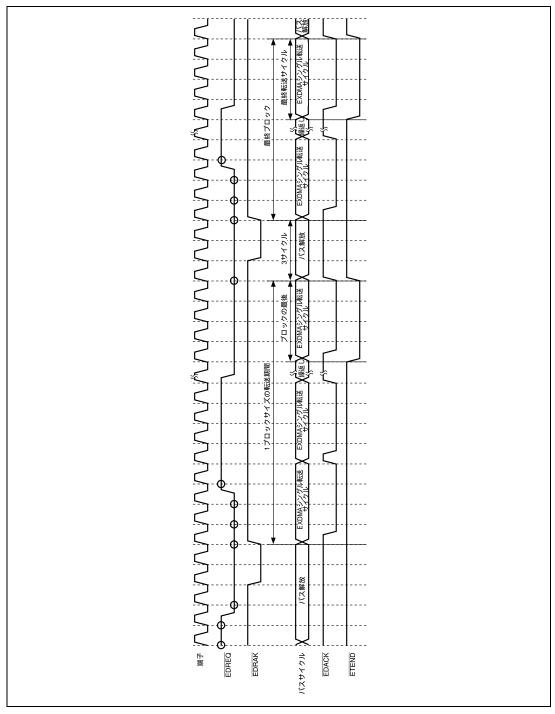

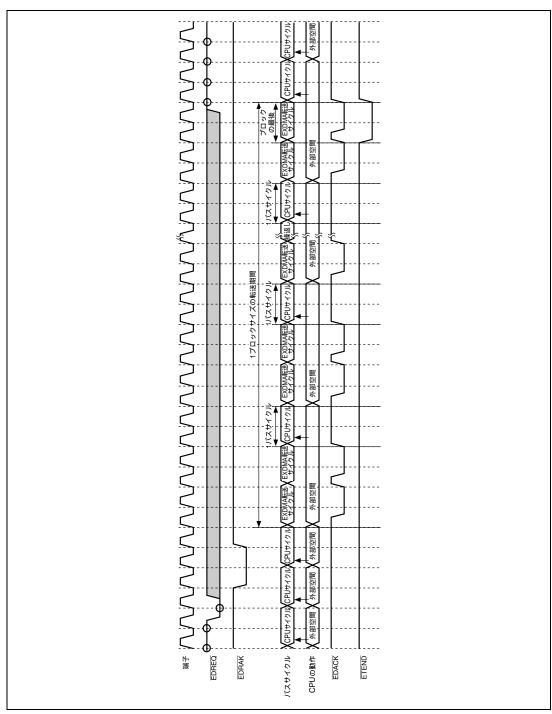

|    | 図 8.18 | EDREQ   端子立ち下がりエッジ起動のノーマルモード転送例   | 8-29 |

|    | 図 8.19 | EDREQ   端子立ち下がりエッジ起動のプロック転送モード転送例 | 8-30 |

|    | 図 8.20 | EDREQ レベル起動のノーマルモード転送例            | 8-31 |

|    | 図 8.21 | EDREQ レベル起動のブロック転送モード転送例          | 8-32 |

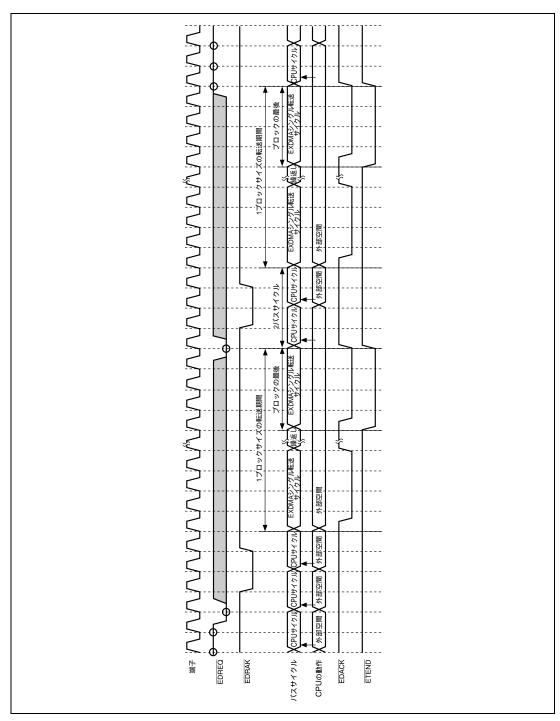

|    | 図 8.22 | シングルアドレスモード ( バイトリード ) 転送例        | 8-33 |

|    | 図 8.23 | シングルアドレスモード(ワードリード)転送例            | 8-33 |

|    | 図 8.24 | シングルアドレスモード ( バイトライト ) 転送例        | 8-34 |

|    | 図 8.25 | シングルアドレスモード(ワードライト)転送例            | 8-34 |

|    | 図 8.26 | EDREQ 端子立ち下がりエッジ起動のシングルアドレスモード転送例 | 8-35 |

|    | 図 8.27 | EDREQ 端子 Low レベル起動のシングルアドレスモード転送例 | 8-36 |

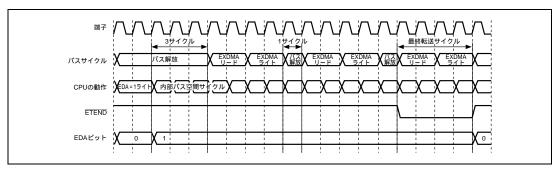

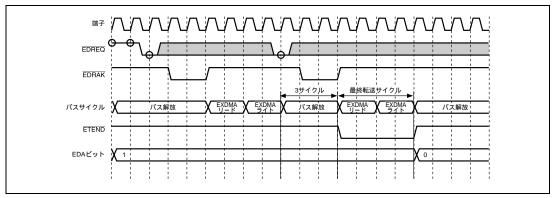

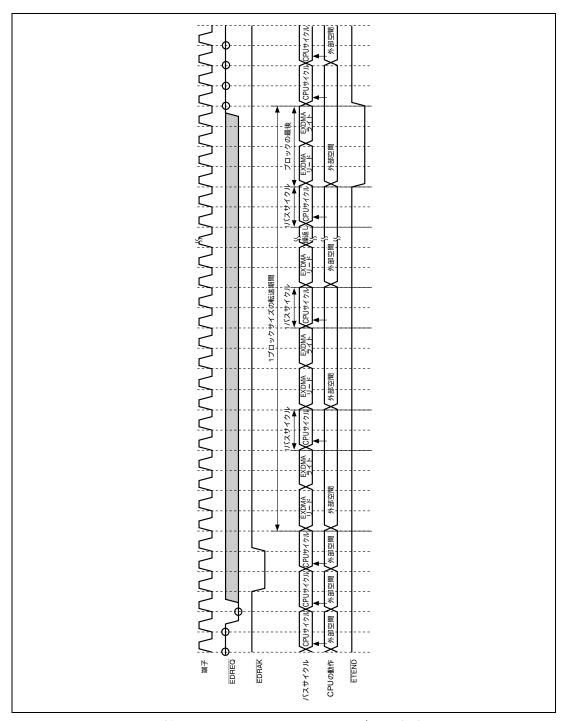

|    | 図 8.28 | オートリクエスト/サイクルスチールモード/ノーマル転送モード    | ^    |

|    |        | (競合がない場合/デュアルアドレスモード)             | 8-37 |

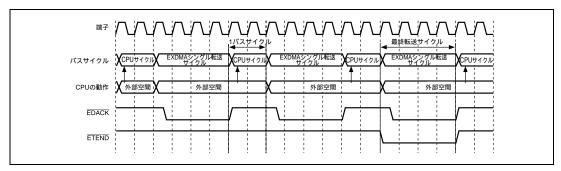

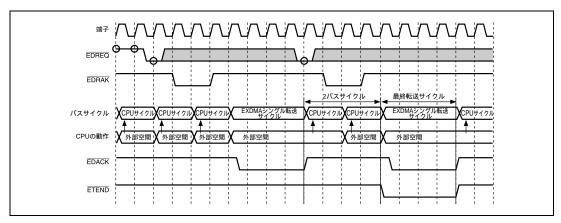

|    | 図 8.29 | オートリクエスト/サイクルスチールモード/ノーマル転送モード<br>(CPU サイクルあり/シングルアドレスモード)       | 8-37 |

|----|--------|------------------------------------------------------------------|------|

|    | 図 8.30 | オートリクエスト/サイクルスチールモード/ノーマル転送モード                                   |      |

|    | _      | (他のチャネルと競合する場合/シングルアドレスモード)                                      | 8-38 |

|    | 図 8.31 | オートリクエスト/バーストモード/ノーマル転送モード                                       |      |

|    | _      | (CPU サイクルあり/デュアルアドレスモード/BGUP=0)                                  | 8-38 |

|    | 図 8.32 | オートリクエスト/バーストモード/ノーマル転送モード<br>(CPU サイクルあり/デュアルアドレスモード/BGUP = 1 ) | 8-38 |

|    | 図 8.33 | オートリクエスト/バーストモード/ノーマル転送モード                                       |      |

|    |        | ( CPU サイクルあり/シングルアドレスモード/BGUP = 1 )                              | 8-39 |

|    | 図 8.34 | オートリクエスト/バーストモード/ノーマル転送モード                                       |      |

|    |        | (他のチャネルと競合する場合/シングルアドレスモード)                                      | 8-39 |

|    | 図 8.35 | 外部リクエスト/サイクルスチールモード/ノーマル転送モード                                    |      |

|    |        | (競合がない場合/デュアルアドレスモード/Low レベル検出)                                  | 8-40 |

|    | 図 8.36 | 外部リクエスト/サイクルスチールモード/ノーマル転送モード                                    |      |

|    |        | ( CPU サイクルあり/シングルアドレスモード/Low レベル検出 )                             | 8-40 |

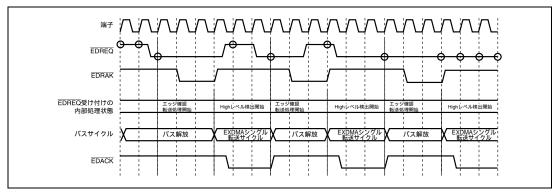

|    | 図 8.37 | 外部リクエスト/サイクルスチールモード/ノーマル転送モード                                    |      |

|    |        | (競合がない場合/シングルアドレスモード/立ち下がりエッジ検出)                                 | 8-40 |

|    | 図 8.38 | 外部リクエスト/サイクルスチールモード/ノーマル転送モード                                    |      |

|    |        | (他のチャネルと競合する場合/デュアルアドレスモード/Low レベル検出)                            | 8-41 |

|    | 図 8.39 | 外部リクエスト/サイクルスチールモード/ブロック転送モード                                    |      |

|    |        | (競合がない場合/デュアルアドレスモード/Low レベル検出/BGUP=0)                           | 8-42 |

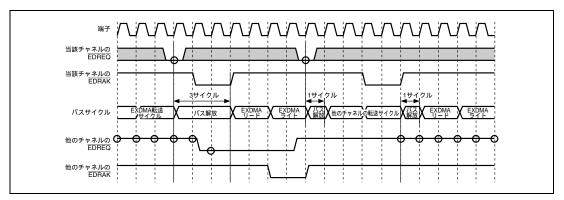

|    | 図 8.40 | 外部リクエスト/サイクルスチールモード/プロック転送モード                                    |      |

|    |        | (競合がない場合/シングルアドレスモード/立ち下がりエッジ検出/BGUP=0)                          | 8-43 |

|    | 図 8.41 | 外部リクエスト/サイクルスチールモード/ブロック転送モード                                    |      |

|    |        | ( CPU サイクルあり/シングルアドレスモード/Low レベル検出/BGUP = 0 )                    | 8-44 |

|    | 図 8.42 | 外部リクエスト/サイクルスチールモード/ブロック転送モード                                    |      |

|    |        | ( CPU サイクルあり/デュアルアドレスモード/Low レベル検出/BGUP = 1 )                    | 8-45 |

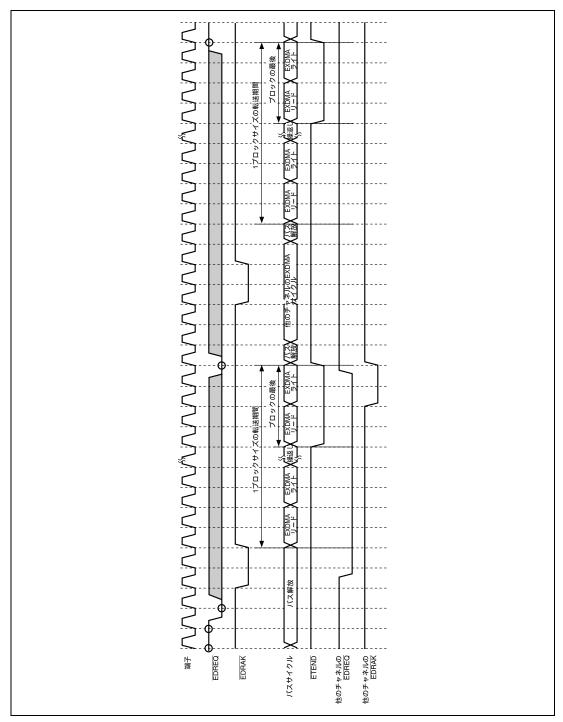

|    | 図 8.43 | 外部リクエスト/サイクルスチールモード/ブロック転送モード                                    |      |

|    |        | ( CPU サイクルあり/シングルアドレスモード/Low レベル検出/BGUP = 1 )                    | 8-46 |

|    | 図 8.44 | 外部リクエスト/サイクルスチールモード/プロック転送モード                                    |      |

|    |        | (他のチャネルと競合する場合/デュアルアドレスモード/Low レベル検出)                            | 8-47 |

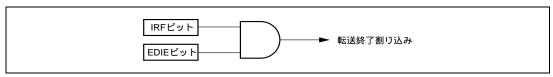

|    | 図 8.45 | 転送終了割り込みのブロック図                                                   | 8-50 |

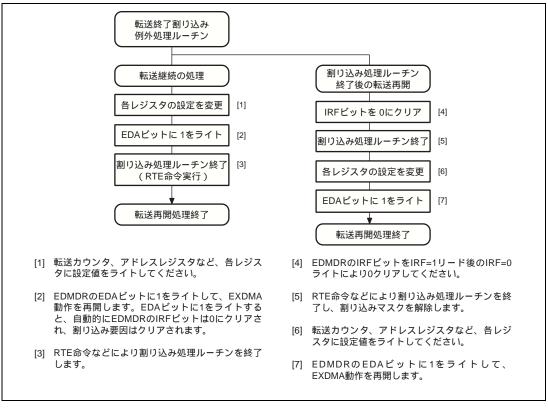

|    | 図 8.46 | 転送終了割り込みが発生したチャネルの転送再開手順例                                        | 8-51 |

| 9. | データト   | 〜ランスファコントローラ(DTC)                                                | 9-1  |

|    | 図 9.1  | DTC のブロック図                                                       | 9-2  |

|    | 図 9.2  | DTC 起動要因制御ブロック図                                                  |      |

|    | 図 9.3  | アドレス空間上での DTC レジスタ情報の配置                                          |      |

|    | 図 9.4  | DTC 動作フローチャート                                                    |      |

|    |        |                                                                  |      |

|    | 図 9.5  | ノーマルモードのメモリマップ                                                   |      |

|    | 図 9.6  | リピートモードのメモリマップ                                                   |      |

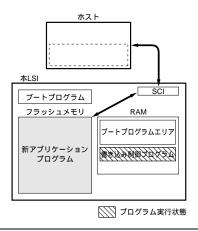

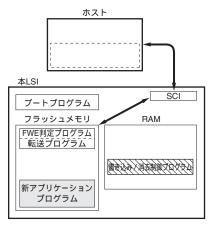

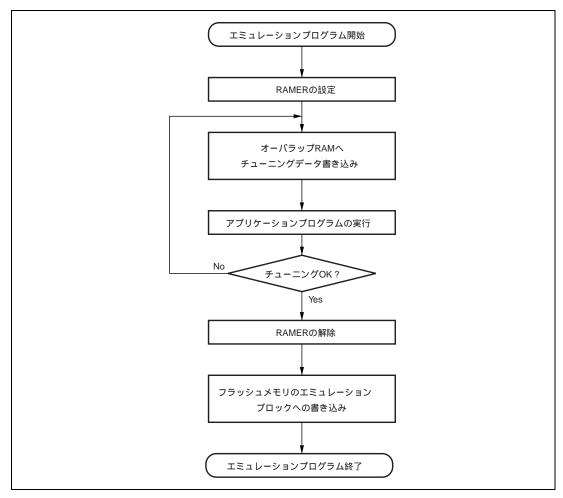

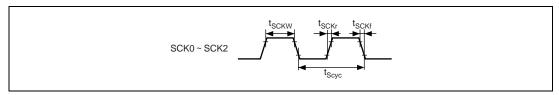

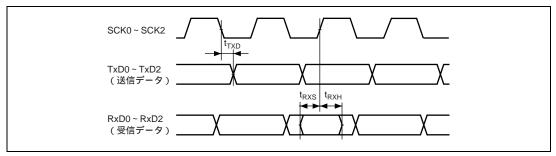

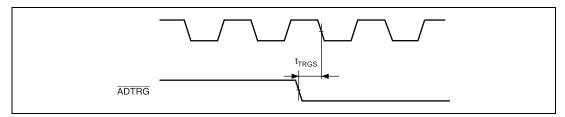

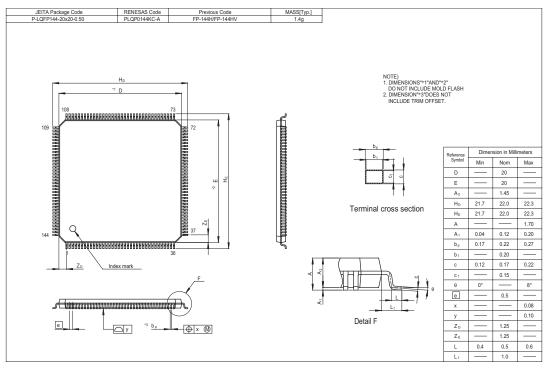

|    | 図 9.7  | プロック転送モードのメモリマップ                                                 | 9-15 |