# RAA730502

# モノリシック・プログラマブル・アナログ IC

R02DS0010JJ0120 Rev.1.20 2014.05.31

#### 概要

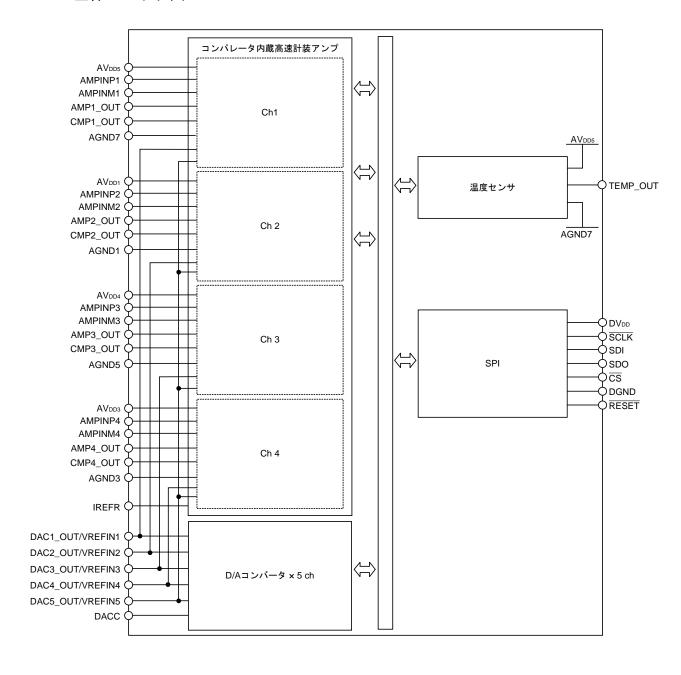

RAA730502 は、モータ制御向け電流センス用アナログ・フロントエンド回路として、コンパレータ内蔵高速計装アンプ、D/A コンバータ、温度センサ等を一式内蔵したモノリシック・プログラマブル・アナログ ICです。外部デバイスからの各機能ブロックへの制御は、シリアル・ペリフェラル・インタフェース(SPI)を採用することでパッケージの小型化および制御ピン数の低減を実現します。また、パッケージは、48 ピン LQFPを採用し、セットの小型化に対応しています。

#### 特徴

- コンパレータ内蔵高速計装アンプ 4 ch 内蔵

- D/A コンバータ 5 ch 内蔵

- 温度センサ回路 1 ch 内蔵

- SPI 1ch 内蔵

- 低消費電流モード内蔵

- 動作電圧範囲: 3.0V ≦ V<sub>DD</sub> ≦ 5.5V

- 動作温度範囲:-40°C≦ TA ≦ 105°C

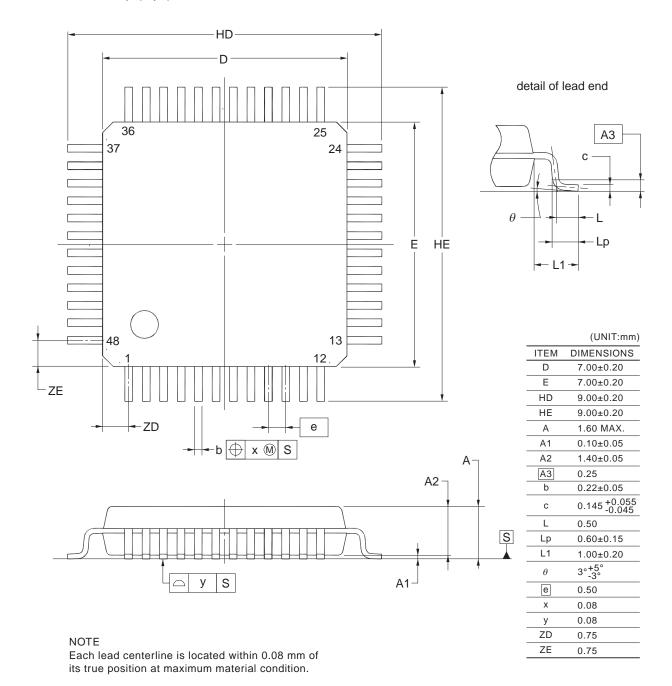

- パッケージ: 48 ピン・プラスチック LQFP (ファインピッチ) (7×7)

#### 応用分野

- 家電製品

- · 空気清浄機

- ・エアコン

- 冷蔵庫

- ・ 食器洗い機

- 電動自転車

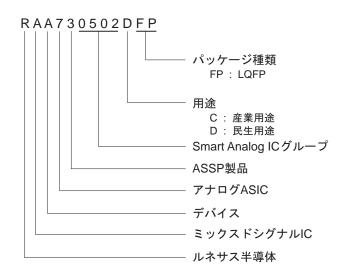

RAA730502 オーダ情報

### オーダ情報

| ピン数  | パッケージ                          | オーダ名称                      |

|------|--------------------------------|----------------------------|

| 48ピン | 48ピン・プラスチックLQFP(ファインピッチ) (7×7) | RAA730502CFP, RAA730502DFP |

### 読み方

このマニュアルを読むにあたっては、電気、電子回路の一般知識を必要とします。

□一通りの機能を理解しようとするとき

型名

- →目次に従って読んでください。

- □改訂された箇所

- →本文欄外の★印は、本版で改訂された主な箇所を示しています。

この"★"を PDF 上でコピーして「検索する文字列」に指定することによって、改版箇所を容易に検索できます。

### 凡例

データ表記の重み : 左が上位桁、右が下位桁

rクティブ・ロウの表記 :  $\overline{\times \times \times}$  (端子、信号名称に上線)

注: 本文中につけた注の説明

注意: 気をつけて読んでいただきたい内容

備考:本文の補足説明

数の表記 : 2 進数…××××または××××B

10 進数···×××× 16 進数···××××H

# 目次

| 1. | 端子  | 子接続図                     | 5  |

|----|-----|--------------------------|----|

|    | 1.1 | 端子レイアウト                  | 5  |

|    | 1.2 | 全体ブロック図                  | 6  |

|    | 1.3 | 端子機能                     | 7  |

|    | 1.4 | 未使用時の端子処理                | 9  |

|    | 1.5 | 入出力回路図                   | 10 |

| 2. | コン  | ノパレータ内蔵高速計装アンプ           | 15 |

|    | 2.1 | コンパレータ内蔵高速計装アンプの機能概要     | 15 |

|    | 2.2 | ブロック図                    | 15 |

|    | 2.3 | コンパレータ内蔵高速計装アンプを制御するレジスタ | 16 |

|    | 2.4 | コンパレータ内蔵高速計装アンプ          | 18 |

| 3. | D/A | 、コンバータ                   | 19 |

|    | 3.1 | D/Aコンバータの機能概要            | 19 |

|    | 3.2 | ブロック図                    | 19 |

|    | 3.3 | D/Aコンバータを制御するレジスタ        | 20 |

|    | 3.4 | D/Aコンバータの動作手順            | 22 |

|    | 3.5 | D/Aコンバータ使用上の注意点          | 23 |

| 4. | 温度  | きセンサ回路                   | 24 |

|    | 4.1 | 温度センサ回路の機能概要             | 24 |

|    | 4.2 | ブロック図                    | 24 |

|    | 4.3 | 温度センサ回路を制御するレジスタ         | 25 |

|    | 4.4 | 温度センサの動作手順               | 26 |

| 5. | SPI |                          | 27 |

|    | 5.1 | SPIの機能                   | 27 |

|    | 5.2 | SPI通信動作                  | 28 |

| 6. | リセ  | zット機能                    | 29 |

|    | 6.1 | リセットの機能概要                | 29 |

|    | 6.2 | リセットを制御するレジスタ            | 32 |

| 7. | 電気  | 贰的特性                     | 33 |

|    | 7.1 | 絶対最大定格                   | 33 |

|    | 7.2 | 動作条件                     | 34 |

|    |     |                          |    |

RAA730502 目次

| 7.3  | 電源電流特性    | 34 |

|------|-----------|----|

| 7.4  | 各機能の電気的特性 | 35 |

| 8 PK | C 外形図     | 42 |

# 1. 端子接続図

### 1.1 端子レイアウト

注意 1. AGND1, AGND2, AGND3, AGND4, AGND5, AGND6, AGND7, DGND は同電位としてください。

- 2. AVDD1, AVDD2, AVDD3, AVDD4, AVDD5, DVDD は同電位としてください。

- 3. DACC はコンデンサ(100 nF: 推奨)を介し、AGND2 に接続してください。

- 4. IREFR は抵抗(56 kΩ:推奨)を介し、AGND7 に接続してください。

- 5. N.C は AGND1 に接続してください。

### 1.2 全体ブロック図

# 1.3 端子機能

表 1-1 端子機能一覧 (1/2)

| 端子<br>番号 | 端子名               | 入出力 | 端子機能                         |

|----------|-------------------|-----|------------------------------|

| 1        | AGND1             | _   | コンパレータ内蔵高速計装アンプ Ch2 用 GND 端子 |

| 2        | DAC2_OUT/         | 入出力 | D/A コンバータ Ch2 出力端子/          |

|          | VREFIN2           |     | コンパレータ内蔵高速計装アンプ Ch2 基準電圧入力端子 |

| 3        | AMPINP2           | 入力  | コンパレータ内蔵高速計装アンプ Ch2 入力端子(+)  |

| 4        | AMPINM2           | 入力  | コンパレータ内蔵高速計装アンプ Ch2 入力端子(-)  |

| 5        | AV <sub>DD1</sub> | 1   | コンパレータ内蔵高速計装アンプ Ch2 用電源端子    |

| 6        | DACC              | 出力  | D/A コンバータ抵抗アレイ安定容量接続端子       |

| 7        | AMP2_OUT          | 出力  | 高速計装アンプ Ch2 出力端子             |

| 8        | AGND2             | ı   | D/A コンバータ用 GND 端子            |

| 9        | CMP2_OUT          | 出力  | コンパレータ Ch2 出力端子              |

| 10       | AV <sub>DD2</sub> | -   | D/A コンバータ用電源端子               |

| 11       | AMPINP4           | 入力  | コンパレータ内蔵高速計装アンプ Ch4 入力端子(+)  |

| 12       | AMPINM4           | 入力  | コンパレータ内蔵高速計装アンプ Ch4 入力端子(-)  |

| 13       | DAC5_OUT/         | 入出力 | D/A コンバータ Ch5 出力端子/          |

|          | VREFIN5           |     | コンパレータ用基準電圧入力端子              |

| 14       | AVDD3             | -   | コンパレータ内蔵高速計装アンプ Ch4 用電源端子    |

| 15       | AMP4_OUT          | 出力  | 高速計装アンプ Ch4 出力端子             |

| 16       | AGND3             | _   | コンパレータ内蔵高速計装アンプ Ch4 用 GND 端子 |

| 17       | CMP4_OUT          | 出力  | コンパレータ Ch4 出力端子              |

| 18       | AGND4             | -   | コンパレータ内蔵高速計装アンプ Ch2 用 GND 端子 |

| 19       | CMP3_OUT          | 出力  | コンパレータ Ch3 出力端子              |

| 20       | AV <sub>DD4</sub> | _   | コンパレータ内蔵高速計装アンプ Ch3 用電源端子    |

| 21       | AMP3_OUT          | 出力  | 高速計装アンプ Ch3 出力端子             |

| 22       | AGND5             | -   | コンパレータ内蔵高速計装アンプ Ch3 用 GND 端子 |

| 23       | DAC4_OUT/         | 入出力 | D/A コンバータ Ch4 出力端子/          |

|          | VREFIN4           |     | コンパレータ内蔵高速計装アンプ Ch4 基準電圧入力端子 |

| 24       | AMPINM3           | 入力  | コンパレータ内蔵高速計装アンプ Ch3 入力端子(-)  |

| 25       | AMPINP3           | 入力  | コンパレータ内蔵高速計装アンプ Ch3 入力端子(+)  |

| 26       | AGND6             | _   | 温度センサ用 GND 端子                |

| 27       | CMP1_OUT          | 出力  | コンパレータ Ch1 出力端子              |

| 28       | AGND7             | _   | 温度センサ用 GND 端子                |

| 29       | DAC3_OUT/         | 入出力 | D/A コンバータ Ch3 出力端子/          |

|          | VREFIN3           |     | コンパレータ内蔵高速計装アンプ Ch3 基準電圧入力端子 |

| 30       | IREFR             | 出力  | 内部基準電流安定抵抗接続端子               |

| 31       | AMP1_OUT          | 出力  | 高速計装アンプ Ch1 出力端子             |

| 32       | TEMP_OUT          | 出力  | 温度センサ出力                      |

| 33       | AV <sub>DD5</sub> | _   | コンパレータ内蔵高速計装アンプ Ch1 用電源端子    |

| 34       | AMPINP1           | 入力  | コンパレータ内蔵高速計装アンプ Ch1 入力端子(+)  |

| 35       | AMPINM1           | 入力  | コンパレータ内蔵高速計装アンプ Ch1 入力端子(-)  |

### 表 1-1 端子機能一覧 (2/2)

| 端子 | 端子名              | 入出力 | 端子機能                         |

|----|------------------|-----|------------------------------|

| 番号 |                  |     |                              |

| 36 | DAC1_OUT/        | 入出力 | D/A コンバータ Ch1 出力端子/          |

|    | VREFIN1          |     | コンパレータ内蔵高速計装アンプ Ch1 基準電圧入力端子 |

| 37 | DVDD             | -   | SPI 用電源端子                    |

| 38 | DGND             | -   | SPI 用 GND 端子                 |

| 39 | SCLK             | 入力  | SPI 用シリアル・クロック入力端子           |

| 40 | SDO              | 出力  | SPI 用シリアル・データ出力端子            |

| 41 | SDI              | 入力  | SPI 用シリアル・データ入力端子            |

| 42 | CS               | 入力  | SPI 用チップ・セレクト入力端子            |

| 43 | N.C <sup>注</sup> | ı   | Non-connection               |

| 44 | N.C <sup>注</sup> | ı   |                              |

| 45 | N.C <sup>注</sup> |     |                              |

| 46 | N.C <sup>注</sup> | _   |                              |

| 47 | N.C <sup>注</sup> | -   |                              |

| 48 | RESET            | 入力  | 外部リセット入力端子                   |

注 AGND1に接続してください。

# 1.4 未使用時の端子処理

表 1-2. 未使用時の端子処理

| 端子名       | 入出力 | 未使用時の推奨接続方法                   |

|-----------|-----|-------------------------------|

| DAC2_OUT/ | 入出力 | オープンにしてください。                  |

| VREFIN2   |     |                               |

| AMPINP2   | 入力  | AGND1 に直接接続してください。            |

| AMPINM2   | 入力  |                               |

| AMP2_OUT  | 出力  | オープンにしてください。                  |

| CMP2_OUT  | 出力  |                               |

| AMPINP4   | 入力  | AGND3 に直接接続してください。            |

| AMPINM4   | 入力  |                               |

| DAC5_OUT/ | 入出力 | オープンにしてください。                  |

| VREFIN5   |     |                               |

| AMP4_OUT  | 出力  |                               |

| CMP4_OUT  | 出力  |                               |

| CMP3_OUT  | 出力  |                               |

| AMP3_OUT  | 出力  |                               |

| DAC4_OUT/ | 入出力 |                               |

| VREFIN4   |     |                               |

| AMPINM3   | 入力  | AGND5 に直接接続してください。            |

| AMPINP3   | 入力  |                               |

| CMP1_OUT  | 出力  | オープンにしてください。                  |

| DAC3_OUT/ | 出力  |                               |

| VREFIN3   |     |                               |

| AMP1_OUT  | 出力  |                               |

| TEMP_OUT  | 出力  |                               |

| AMPINP1   | 入力  | AGND7 に直接接続してください。            |

| AMPINM1   | 入力  |                               |

| DAC1_OUT/ | 入出力 | オープンにしてください。                  |

| VREFIN1   |     |                               |

| SCLK      | 入力  |                               |

| SDO       | 出力  |                               |

| SDI       | 入力  |                               |

| CS        | 入力  |                               |

| N.C       | _   | AGND1 に直接接続してください。            |

| RESET     | 入力  | DVpp に直接接続、または抵抗を介して接続してください。 |

# 1.5 入出力回路図

等価回路 端子名 等価回路 端子名 AMPINM1 AMPINM2  $AV_{DD1}$  $AV_{DD5}$ AMPINP1 AMPINP2 IN O INO AGND7 AGND1 AMPINM3 AMPINM4 AV<sub>DD4</sub> **AV**DD3 AMPINP3 AMPINP4 INO INO AGND3 AGND5

図 1-1 入出力回路タイプ (1/5)

図 1-1 入出力回路タイプ (2/5)

| 端子名      | 等価回路                  | 端子名      | 等価回路           |

|----------|-----------------------|----------|----------------|

| AMP1_OUT | AVDD5<br>OUT<br>AGND7 | AMP2_OUT | AVDD1<br>AGND1 |

| AMP3_OUT | AVDD4<br>O OUT        | AMP4_OUT | AVDD3<br>AGND3 |

図 1-1 入出力回路タイプ (3/5)

| 端子名      | 等価回路  | 端子名      | 等価回路  |

|----------|-------|----------|-------|

| CMP1_OUT | AGND7 | CMP2_OUT | AGND1 |

| CMP3_OUT | AGND5 | CMP4_OUT | AGND3 |

図 1-1 入出力回路タイプ (4/5)

| 端子名                                          | 等価回路                       | 端子名                                          | 等価回路                                   |

|----------------------------------------------|----------------------------|----------------------------------------------|----------------------------------------|

| DAC1_OUT/<br>VREFIN1<br>DAC2_OUT/<br>VREFIN2 | AVDD1 O IN/OUT AGND1 AGND1 | DAC3_OUT/<br>VREFIN3<br>DAC4_OUT/<br>VREFIN4 | AVDD3 O IN/OUT AGND3 AGND3             |

| DAC5_OUT/<br>VREFIN5                         | AVDD2 O IN/OUT AGND2 AGND2 | SCLK<br>SDI<br>CS                            | DVDD DVDD DVDD DVDD DVDD DVDD DVDD DVD |

図 1-1 入出力回路タイプ (5/5)

| 端子名      | 等価回路                    | 端子名   | 等価回路                            |

|----------|-------------------------|-------|---------------------------------|

| TEMP_OUT | AVDD5 O OUT AGND7 AGND7 | RESET | ヒステリシス特性を有するシュミット・トリガ入力となっています。 |

| SDO      | DGND OUT                |       |                                 |

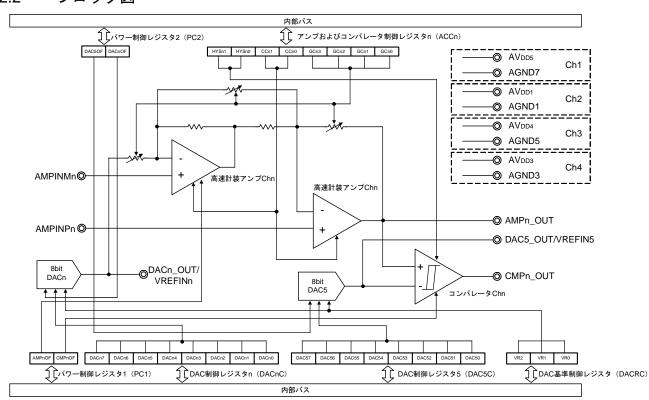

## 2. コンパレータ内蔵高速計装アンプ

RAA730502 は、コンパレータ内蔵高速計装アンプを 4 ch 搭載しています。

#### ★2.1 コンパレータ内蔵高速計装アンプの機能概要

コンパレータ内蔵高速計装アンプは、高速計装アンプ部とコンパレータ部で構成されます。

- 高速計装アンプ部

- 増幅率を10 dB~34 dBまで13ステップで選択可能

- 動作モードを4通りから選択可能

- D/AコンバータCh1~4で基準電圧を調整可能

- パワーオフ機能を搭載

- コンパレータ部

- 高速計装アンプの出力信号を、コンパレータの+側入力信号とし比較出力可能

- D/AコンバータCh5で基準電圧を調整可能

- パワーオフ機能を搭載

また、コンパレータ内蔵高速計装アンプでは、DACn\_OUT( $n=1\sim5$ )出力信号を基準電圧として使用できます。D/Aコンバータを使用しない場合は、DACn\_OUT / VREFINn( $n=1\sim5$ )端子から外部基準電圧を入力します。D/Aコンバータの使用に関しては、3. D/Aコンバータを参照してください。

#### 2.2 ブロック図

注意 コンパレータ機能を使用する場合は、CMPn\_OUT 端子にプルアップ抵抗(2.2 k $\Omega$ : 推奨)を接続してください。

備考 n = 1~4

### 2.3 コンパレータ内蔵高速計装アンプを制御するレジスタ

コンパレータ内蔵高速計装アンプでは、次の2種類のレジスタを使用します。

- アンプおよびコンパレータ制御レジスタ 1, 2, 3, 4 (ACC1, ACC2, ACC3, ACC4)

- パワー制御レジスタ 1 (PC1)

#### (1) アンプおよびコンパレータ制御レジスタ 1, 2, 3, 4 (ACC1, ACC2, ACC3, ACC4)

コンパレータ内蔵高速計装アンプ Ch1~Ch4 の動作モード、増幅率およびコンパレータのヒステリシス幅を設定するレジスタです。リセット信号の発生により、00Hになります。

アドレス: 00H (n = 1), 01H (n = 2), 02H (n = 3), 03H (n = 4) リセット時: 00H R/W

|      | 7     | 6     | 5    | 4    | 3    | 2    | 1    | 0    |

|------|-------|-------|------|------|------|------|------|------|

| ACCn | HYSn1 | HYSn0 | CCn1 | CCn0 | GCn3 | GCn2 | GCn1 | GCn0 |

| HYSn1 | HYSn0 | ヒステリシス幅(Typ.) |

|-------|-------|---------------|

| 0     | 0     | 200 mV        |

| 0     | 1     | 100 mV        |

| 1     | 0     | 50 mV         |

| 1     | 1     | ヒステリシスなし      |

| CCn1 | CCn0 | コンパレータ内蔵高速計装アンプの動作モード |

|------|------|-----------------------|

| 0    | 0    | 高速モード                 |

| 0    | 1    | 中速モード2                |

| 1    | 0    | 中速モード1                |

| 1    | 1    | 低速モード                 |

| GCn3 | GCn2 | GCn1 | GCn0 | コンパレータ内蔵高速計装アンプの増幅率(Typ.) |

|------|------|------|------|---------------------------|

| 0    | 0    | 0    | 0    | 10 dB                     |

| 0    | 0    | 0    | 1    | 12 dB                     |

| 0    | 0    | 1    | 0    | 14 dB                     |

| 0    | 0    | 1    | 1    | 16 dB                     |

| 0    | 1    | 0    | 0    | 18 dB                     |

| 0    | 1    | 0    | 1    | 20 dB                     |

| 0    | 1    | 1    | 0    | 22 dB                     |

| 0    | 1    | 1    | 1    | 24 dB                     |

| 1    | 0    | 0    | 0    | 26 dB                     |

| 1    | 0    | 0    | 1    | 28 dB                     |

| 1    | 0    | 1    | 0    | 30 dB                     |

| 1    | 0    | 1    | 1    | 32 dB                     |

| 1    | 1    | 0    | 0    | 34 dB                     |

| 上記以外 |      |      |      | 設定禁止                      |

備考 n=1~4

### (2) パワー制御レジスタ 1 (PC1)

コンパレータ内蔵高速計装アンプの動作許可/停止を設定するレジスタです。

使用しない機能は、動作停止させることで、低消費電力化とノイズ低減をはかります。

コンパレータ内蔵高速計装アンプ  $Ch1\sim Ch4$  を使用するときは、コンパレータ  $Ch1\sim Ch4$  に、高速計装アンプ  $Ch1\sim Ch4$  に対応する制御ビットに 1 を設定してください。

リセット信号の発生により、00Hになります。

#### アドレス: 0AH リセット時: 00H R/W

| _   | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-----|--------|--------|--------|--------|--------|--------|--------|--------|

| PC1 | CMP4OF | CMP3OF | CMP2OF | CMP10F | AMP4OF | AMP3OF | AMP2OF | AMP1OF |

| CMP4OF | コンパレータ Ch4 の動作制御 |

|--------|------------------|

| 0      | コンパレータ Ch4 動作停止  |

| 1      | コンパレータ Ch4 動作許可  |

|   | CMP3OF | コンパレータ Ch3 の動作制御 |

|---|--------|------------------|

|   | 0      | コンパレータ Ch3 動作停止  |

| Ī | 1      | コンパレータ Ch3 動作許可  |

| CMP2OF | コンパレータ Ch2 の動作制御 |

|--------|------------------|

| 0      | コンパレータ Ch2 動作停止  |

| 1      | コンパレータ Ch2 動作許可  |

| CMP1 | OF |                 | コンパレータ Ch1 の動作制御 |

|------|----|-----------------|------------------|

| 0    |    | コンパレータ Ch1 動作停止 |                  |

| 1    |    | コンパレータ Ch1 動作許可 |                  |

| AMP4OF | 高速計装アンプ Ch4 の動作制御 |  |  |  |

|--------|-------------------|--|--|--|

| 0      | 高速計装アンプ Ch4 動作停止  |  |  |  |

| 1      | 高速計装アンプ Ch4 動作許可  |  |  |  |

| AMP3OF | 高速計装アンプ Ch3 の動作制御 |

|--------|-------------------|

| 0      | 高速計装アンプ Ch3 動作停止  |

| 1      | 高速計装アンプ Ch3 動作許可  |

| AMP2OF | 高速計装アンプ Ch2 の動作制御 |

|--------|-------------------|

| 0      | 高速計装アンプ Ch2 動作停止  |

| 1      | 高速計装アンプ Ch2 動作許可  |

| AMP10F | 高速計装アンプ Ch1 の動作制御 |  |  |  |

|--------|-------------------|--|--|--|

| 0      | 高速計装アンプ Ch1 動作停止  |  |  |  |

| 1      | 高速計装アンプ Ch1 動作許可  |  |  |  |

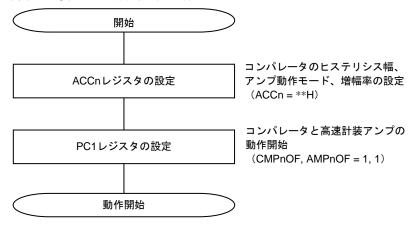

### 2.4 コンパレータ内蔵高速計装アンプ

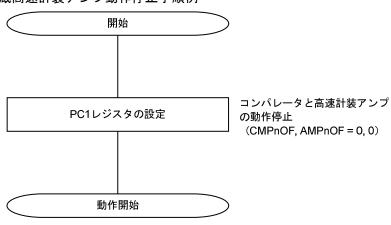

コンパレータ内蔵高速計装アンプの動作開始手順と動作停止手順を以下に示します。

#### コンパレータ内蔵高速計装アンプ動作開始手順例

### コンパレータ内蔵高速計装アンプ動作停止手順例

備考 \* : don't care n = 1~4

# 3. D/A コンバータ

RAA73502 は、D/A コンバータを 5ch 搭載しています。

### ★ 3.1 D/A コンバータの機能概要

D/A コンバータは、ディジタル入力をアナログ信号に変換する 8 ビット分解能のコンバータです。 D/A コンバータには、次のような機能があります。

- 8 ビット分解能 (×5ch: Ch1~Ch5)

- R-2R ラダー方式

- アナログ電圧出力:出力電圧値は、以下の式で計算できます。

出力電圧値= { (基準電圧上限値-基準電圧下限値) × m/256 } +基準電圧下限値 (m=0~255:DACnC レジスタに設定した値)

コールジスタに設定した値)

- コンパレータ内蔵高速計装アンプの基準電圧調整機能

- パワーオフ機能を搭載

備考 n=1~5

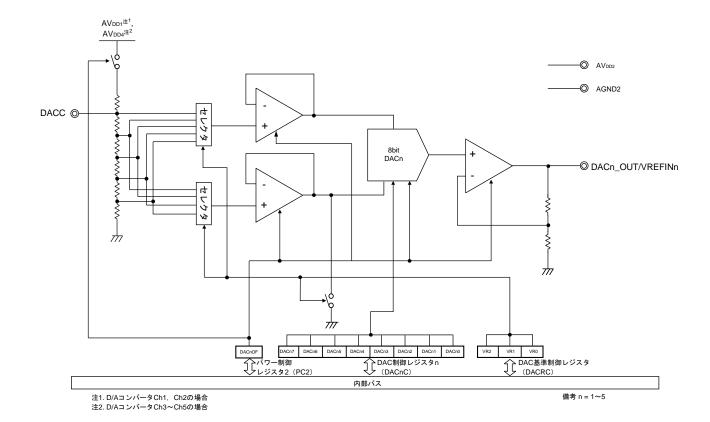

#### 3.2 ブロック図

### 3.3 D/A コンバータを制御するレジスタ

D/A コンバータでは、次の3種類のレジスタを使用します。

- DAC 制御レジスタ 1, 2, 3, 4, 5 (DAC1C, DAC2C, DAC3C, DAC4C, DAC5C)

- DAC 基準制御レジスタ (DACRC)

- パワー制御レジスタ 2 (PC2)

### (1) DAC 制御レジスタ 1, 2, 3, 4, 5 (DAC1C, DAC2C, DAC3C, DAC4C, DAC5C)

DACn\_OUT 端子に出力するアナログ電圧値を設定するレジスタです。

DACn\_OUT 出力信号は、コンパレータ内蔵高速計装アンプの基準電圧として使用できます。

リセット信号の発生により、80Hになります。

アドレス: 04H (n = 1), 05H (n = 2), 06H (n = 3), 07H (n = 4), 08H (n = 5) リセット時: 80H R/W

| _     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| DACnC | DACn7 | DACn6 | DACn5 | DACn4 | DACn3 | DACn2 | DACn1 | DACn0 |

#### 備考 1. n = 1~5

2. 出力電圧値の算出に関しては、3.1 D/Aコンバータの機能概要を参照してください。

#### ★ (2) DAC 基準制御レジスタ (DACRC)

D/A コンバータ  $Ch1 \sim Ch5$  の基準電圧の上限値(VRT)と下限値(VRB)を選択するレジスタです。 リセット信号の発生により、00H になります。

アドレス:09H リセット時:00H R/W

|       | 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0   |

|-------|---|---|---|---|---|-----|-----|-----|

| DACRC | 0 | 0 | 0 | 0 | 0 | VR2 | VR1 | VR0 |

| VR2 | VR1 | VR0 | 基準電圧上降                  | 艮値(Typ.)                | 基準電圧下降                  | 艮値(Typ.)                |

|-----|-----|-----|-------------------------|-------------------------|-------------------------|-------------------------|

|     |     |     | D/A コンバータ               | D/A コンバータ               | D/A コンバータ               | D/A コンバータ               |

|     |     |     | Ch1, Ch2                | Ch3~Ch5                 | Ch1, Ch2                | Ch3~Ch5                 |

| 0   | 0   | 0   | AV <sub>DD1</sub>       | AV <sub>DD4</sub>       | AGND1                   | AGND5                   |

| 0   | 0   | 1   | AV <sub>DD1</sub> × 1/5 | AV <sub>DD4</sub> × 1/5 | AGND1                   | AGND5                   |

| 0   | 1   | 0   | AV <sub>DD1</sub> × 2/5 | AV <sub>DD4</sub> × 2/5 | AV <sub>DD1</sub> × 1/5 | $AV_{DD4} \times 1/5$   |

| 0   | 1   | 1   | AV <sub>DD1</sub> × 3/5 | $AV_{DD4} \times 3/5$   | AV <sub>DD1</sub> × 2/5 | $AV_{DD4} \times 2/5$   |

| 1   | 0   | 0   | $AV_{DD1} \times 4/5$   | $AV_{DD4} \times 4/5$   | AV <sub>DD1</sub> × 3/5 | $AV_{DD4} \times 3/5$   |

| 1   | 0   | 1   | AV <sub>DD1</sub>       | AV <sub>DD4</sub>       | AV <sub>DD1</sub> × 4/5 | $AV_{DD4} \times 4/5$   |

| 1   | 1   | 0   | AV <sub>DD1</sub> × 4/5 | $AV_{DD4} \times 4/5$   | AV <sub>DD1</sub> × 1/5 | AV <sub>DD4</sub> × 1/5 |

| 1   | 1   | 1   | 設定禁止                    |                         |                         |                         |

備考 ビット 7~3 は 0 固定です。(1 ライトによる書き換え禁止)

### (3) パワー制御レジスタ 2 (PC2)

D/A コンバータ、温度センサ回路の動作許可/停止を設定するレジスタです。

使用しない機能は、動作停止させることで、低消費電力化とノイズ低減をはかります。

D/A コンバータ  $Ch1\sim Ch5$  のいずれかを使用するときは、必ずビット  $4\sim 0$  の対応する制御ビットに 1 を設定してください。

リセット信号の発生により、00Hになります。

#### アドレス: 0BH リセット時: 00H R/W

| _   | 7 | 6 | 5      | 4      | 3      | 2      | 1      | 0      |

|-----|---|---|--------|--------|--------|--------|--------|--------|

| PC2 | 0 | 0 | TEMPOF | DAC5OF | DAC4OF | DAC3OF | DAC2OF | DAC1OF |

| DAC5OF | D/A コンバータ Ch5 の動作制御 |

|--------|---------------------|

| 0      | D/A コンバータ Ch5 の動作停止 |

| 1      | D/A コンバータ Ch5 の動作許可 |

| DAC4OF | D/A コンバータ Ch4 の動作制御 |

|--------|---------------------|

| 0      | D/A コンバータ Ch4 の動作停止 |

| 1      | D/A コンバータ Ch4 の動作許可 |

| ĺ | DAC3OF | D/A コンバータ Ch3 の動作制御 |

|---|--------|---------------------|

|   | 0      | D/A コンバータ Ch3 の動作停止 |

|   | 1      | D/A コンバータ Ch3 の動作許可 |

| DAC2OF | D/A コンバータ Ch2 の動作制御 |

|--------|---------------------|

| 0      | D/A コンバータ Ch2 の動作停止 |

| 1      | D/A コンバータ Ch2 の動作許可 |

| DAC10F | D/A コンバータ Ch1 の動作制御 |  |  |

|--------|---------------------|--|--|

| 0      | D/A コンバータ Ch1 の動作停止 |  |  |

| 1      | D/A コンバータ Ch1 の動作許可 |  |  |

備考 ビット 7,6 は0 固定です。(1 ライトによる書き換え禁止)

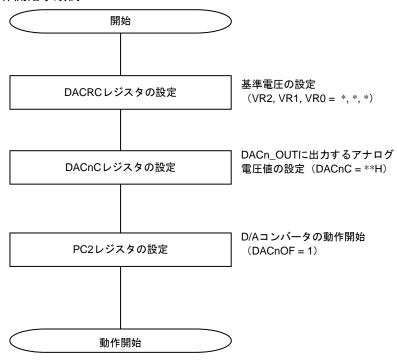

### 3.4 D/A コンバータの動作手順

D/A コンバータの動作開始手順と動作停止手順を以下に示します。

#### D/A コンバータ動作開始手順例

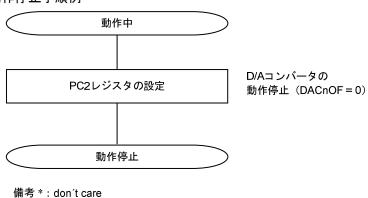

#### D/A コンバータ動作停止手順例

n = 1~5

### 3.5 D/A コンバータ使用上の注意点

D/A コンバータを使用する際の注意事項を次に示します。

(1) D/Aコンバータの出力インピーダンスが高いため、DACn\_OUTから電流を取り出すことはできません。 負荷の入力インピーダンスが低い場合には、負荷とDACn\_OUT端子の間にフォロアアンプを挿入して使 用してください。また、フォロアアンプや負荷までの配線は極力短くするようにしてください(出力インピーダンスが高いため)。配線が長くなるような場合は、グランド・パターンで囲むなどの処置をしてください。

(2) VREFINnに外部基準電源を入力する場合は、DACnOF=0にしてください。

備考 n=1~5

RAA730502 4. 温度センサ回路

# 4. 温度センサ回路

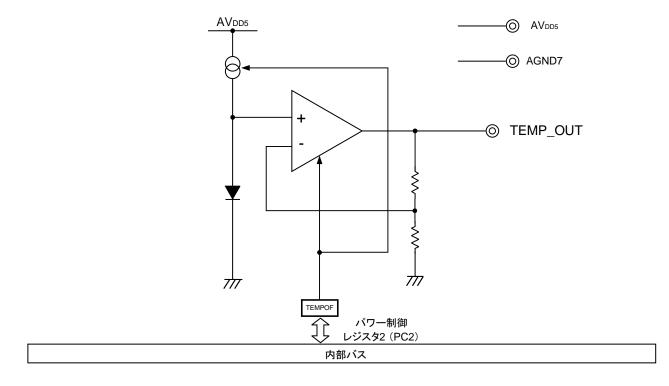

RAA730502 は、温度センサ回路を 1 ch 搭載しています。

### 4.1 温度センサ回路の機能概要

温度センサ回路には、次のような機能があります。

- 出力電圧温度係数: -5 mV/°C (Typ.)

- パワーオフ機能を搭載

### 4.2 ブロック図

RAA730502 4. 温度センサ回路

### 4.3 温度センサ回路を制御するレジスタ

温度センサ回路では、次のレジスタを使用します。

• パワー制御レジスタ 2 (PC2)

### (1) パワー制御レジスタ 2 (PC2)

温度センサ回路、D/A コンバータの動作許可/停止を設定するレジスタです。 使用しない機能は、動作停止させることで、低消費電力化とノイズ低減をはかります。 温度センサ回路を使用するときは、ビット 5 に 1 を設定してください。 リセット信号の発生により、00Hになります。

#### アドレス: 0BH リセット時: 00H R/W

| _   | 7 | 6 | 5      | 4      | 3      | 2      | 1      | 0      |

|-----|---|---|--------|--------|--------|--------|--------|--------|

| PC2 | 0 | 0 | TEMPOF | DAC5OF | DAC4OF | DAC3OF | DAC2OF | DAC1OF |

|   | TEMPOF | 温度センサ回路の動作制御 |

|---|--------|--------------|

| ĺ | 0      | 温度センサ回路の動作停止 |

|   | 1      | 温度センサ回路の動作許可 |

備考 ビット 7,6 は0 固定です。(1 ライトによる書き換え禁止)

RAA730502 4. 温度センサ回路

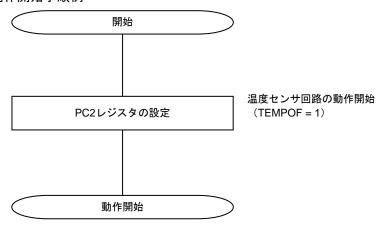

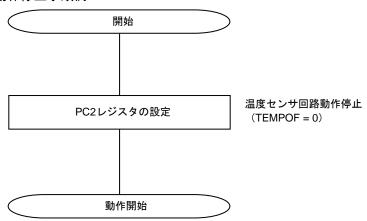

### 4.4 温度センサの動作手順

温度センサ回路の動作開始手順と動作停止手順を以下に示します。

#### 温度センサ回路動作開始手順例

#### 温度センサ回路 動作停止手順例

RAA730502 5. SPI

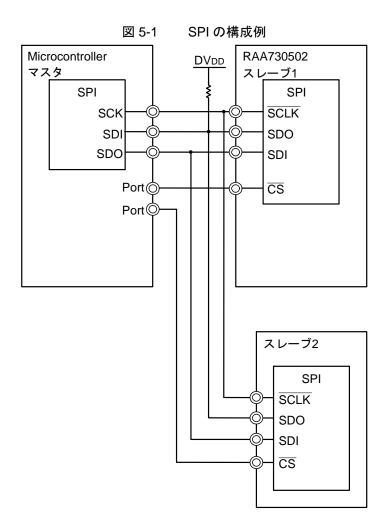

### 5. SPI

### 5.1 SPI の機能

SPI は、シリアル・クロック( $\overline{SCLK}$ )とシリアル・データ(SDI、SDO)、チップ・セレクト入力( $\overline{CS}$ )の 4本のラインによるクロック同期式通信にて、外部機器からの制御インタフェースに使用します。

#### [データ送受信]

- 16 ビット単位のデータ長

- MSB ファースト

★ 注意 DVDDに電源投入後、SPIとの通信を開始する前に、RESET 端子に外部リセットを入力させる必要があります。 詳細は、6. リセット機能を参照してください。 RAA730502 5. SPI

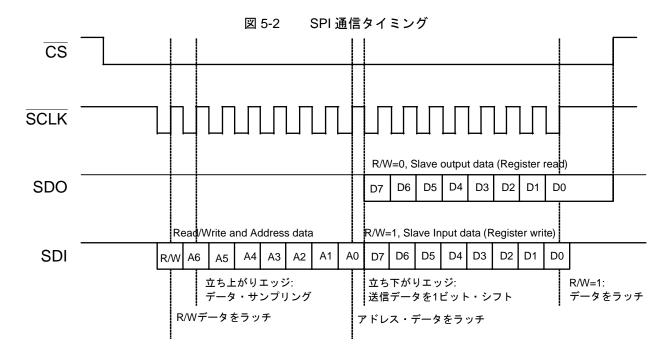

#### 5.2 SPI 通信動作

16 ビット単位でデータの送受信を行います。 $\overline{CS} = Low$  の場合,データの送受信が可能です。データは,シリアル・クロックの立ち下がりエッジに同期して 1 ビットごとに送信され、シリアル・クロックの立ち上がりエッジに同期して 1 ビットごとに受信します。R/W ビット=1 の場合, $\overline{CS}$  の立ち下がり後 16 回目の  $\overline{SCLK}$  立ち上がりエッジ検出時に,アドレス・データに応じた SPI 制御レジスタヘデータが書き込まれ,その内容の動作が実行されます。R/W ビット = 0 の場合, $\overline{CS}$  の立ち下がり後 9 回目以降の  $\overline{SCLK}$  立ち下がりエッジに同期して,アドレス・データに応じたレジスタデータを出力します。

表 5-1 SPI 制御レジスター覧

| アドレス | SPI制御レジスタ名称               | R/W | リセット時             |

|------|---------------------------|-----|-------------------|

| 00H  | アンプおよびコンパレータ制御レジスタ1(ACC1) | R/W | 00H               |

| 01H  | アンプおよびコンパレータ制御レジスタ2(ACC2) | R/W | 00H               |

| 02H  | アンプおよびコンパレータ制御レジスタ3(ACC3) | R/W | 00H               |

| 03H  | アンプおよびコンパレータ制御レジスタ4(ACC4) | R/W | 00H               |

| 04H  | DAC制御レジスタ1(DAC1C)         | R/W | 80H               |

| 05H  | DAC制御レジスタ2(DAC2C)         | R/W | 80H               |

| 06H  | DAC制御レジスタ3(DAC3C)         | R/W | 80H               |

| 07H  | DAC制御レジスタ4(DAC4C)         | R/W | 80H               |

| 08H  | DAC制御レジスタ5(DAC5C)         | R/W | 80H               |

| 09H  | DAC基準制御レジスタ(DACRC)        | R/W | 00H               |

| 0AH  | パワー制御レジスタ1 (PC1)          | R/W | 00H               |

| 0BH  | パワー制御レジスタ2 (PC2)          | R/W | 00H               |

| 0CH  | リセット制御レジスタ(RC)            | R/W | 00H <sup>注1</sup> |

| 0DH  | テスト・レジスタ <sup>注2</sup>    | R/W | 00H               |

- 注 1. リセット制御レジスタ (RC) による内部リセットの場合、リセット制御レジスタ (RC) は初期化 (00H) されません。詳細は、6. リセット機能を参照してください。

- 2. テスト・レジスタの書き替えは禁止です。

# ★6. リセット機能

#### 6.1 リセットの機能概要

RAA730502 は、リセット機能を搭載しています。リセットの発生により、SPI 制御レジスタが初期化されます。リセットを発生させる方法には、次の3種類があります。

- RESET 端子へのリセット信号入力による外部リセット

- リセット制御レジスタ (RC) による内部リセット (RESET ビットへの1 ライト)

- パワーオン・リセット (POR) 回路による内部リセット

外部リセットと内部リセットの機能は、以下のとおりです。

- $DV_{DD}$ に電源投入後、SPI との通信を開始する前に、 $\overline{RESET}$  端子による外部リセットを発生させる必要があります。

- リセットがかかると、各機能ブロックは、表 6-1 に示すような状態になります。また、リセット受け付け 後の SPI 制御レジスタの状態は、表 6-2 に示すような状態になり、その際の端子状態は、表 6-3 に示すよ うな様態になります。

- 外部リセットでは、RESET 端子にロー・レベルが入力されることでリセットがかかり、内部リセットでは、リセット制御レジスタ (RC) の RESET ビットへの1 ライト、もしくは、POR 回路での電圧検出によりリセットがかかります。

- 外部リセットでは、RESET端子にロー・レベルが入力された後、ハイ・レベルが入力されると、リセットが解除されます。内部リセットでは、リセット制御レジスタ(RC)のRESET ビットへの0ライト、もしくは、POR回路での電圧検出によりリセットが解除されます。

- POR 回路での電圧検出による内部リセットでは、電源電圧  $(AV_{DDI} \sim AV_{DDS}, DV_{DD})$   $\leq$ 検出電圧  $(V_{PDR})$  になるとリセットがかかり、電源電圧  $(AV_{DDI} \sim AV_{DDS}, DV_{DD})$   $\geq$ 検出電圧  $(V_{POR})$  になるとリセットが解除されます。検出電圧に関しては、7.4(5) パワーオン・リセット (POR) 回路の電気的特性を参照してください。

注意 外部リセットを行う場合、RESET端子に 10μs 以上のロー・レベルを入力してください。

#### 表 6-1 リセット期間中の動作状態

| 機能ブロック              | RESET端子による外部リセット<br>または、POR回路による内部リセット | リセット制御レジスタ(RC)<br>による内部リセット |

|---------------------|----------------------------------------|-----------------------------|

| コンパレータ内蔵<br>高速計装アンプ | 動作停止                                   |                             |

| D/Aコンバータ            | 動作停止                                   |                             |

| SPI                 | 動作停止 動作可能                              |                             |

#### 表 6-2 リセット受け付け後の SPI 制御レジスタの状態

|      |                           | リセット受け             | け付け後の状態           |

|------|---------------------------|--------------------|-------------------|

| アドレス | SPI制御レジスタ名称               | 外部リセット時            | 内部リセット時           |

|      |                           | 内部リセット時<br>(POR回路) | (RCレジスタ)          |

| 00H  | アンプおよびコンパレータ制御レジスタ1(ACC1) | 00H                | 00H               |

| 01H  | アンプおよびコンパレータ制御レジスタ2(ACC2) | 00H                | 00H               |

| 02H  | アンプおよびコンパレータ制御レジスタ3(ACC3) | 00H                | 00H               |

| 03H  | アンプおよびコンパレータ制御レジスタ4(ACC4) | 00H                | 00H               |

| 04H  | DAC制御レジスタ1(DAC1C)         | 80H                | 80H               |

| 05H  | DAC制御レジスタ2(DAC2C)         | 80H                | 80H               |

| 06H  | DAC制御レジスタ3(DAC3C)         | 80H                | 80H               |

| 07H  | DAC制御レジスタ4(DAC4C)         | 80H                | 80H               |

| 08H  | DAC制御レジスタ5 (DAC5C)        | 80H                | 80H               |

| 09H  | DAC基準制御レジスタ(DACRC)        | 00H                | 00H               |

| 0AH  | パワー制御レジスタ1 (PC1)          | 00H                | 00H               |

| 0ВН  | パワー制御レジスタ2 (PC2)          | 00H                | 00H               |

| 0CH  | リセット制御レジスタ(RC)            | 00H                | 01H <sup>注1</sup> |

| 0DH  | テスト・レジスタ <sup>注2</sup>    | 00H                | 00H               |

注 1. リセット制御レジスタ(RC)による内部リセットの場合、リセット制御レジスタ(RC)は初期化(00H)されません。 $\overline{\text{RESET}}$ 端子への外部リセット入力、POR 回路による内部リセット、または、RESET ビットへの 0 ライトにより初期化(00H)されます。

2. テスト・レジスタの書き替えは禁止です。

表 6-3 リセット後の端子状態

| 端子名              | RESET端子による外部リセット<br>または、POR回路による内部リセット | リセット制御レジスタ(RC)<br>による内部リセット |

|------------------|----------------------------------------|-----------------------------|

| DAC2_OUT/VREFIN2 | プルダウン入力                                | プルダウン入力                     |

| AMPINP2          | Hi-Z                                   | Hi-Z                        |

| AMPINM2          | Hi-Z                                   | Hi-Z                        |

| AMP2_OUT         | プルダウン                                  | プルダウン                       |

| CMP2_OUT         | Hi-Z(オープン・ドレイン)                        | Hi-Z(オープン・ドレイン)             |

| AMPINP4          | Hi-Z                                   | Hi-Z                        |

| AMPINM4          | Hi-Z                                   | Hi-Z                        |

| DAC5_OUT/VREFIN5 | プルダウン入力                                | プルダウン入力                     |

| AMP4_OUT         | プルダウン                                  | プルダウン                       |

| CMP4_OUT         | Hi-Z(オープン・ドレイン)                        | Hi-Z(オープン・ドレイン)             |

| CMP3_OUT         | Hi-Z(オープン・ドレイン)                        | Hi-Z(オープン・ドレイン)             |

| AMP_OUT3         | プルダウン                                  | プルダウン                       |

| DAC4_OUT/VREFIN4 | プルダウン入力                                | プルダウン入力                     |

| AMPINM3          | Hi-Z                                   | Hi-Z                        |

| AMPINP3          | Hi-Z                                   | Hi-Z                        |

| CMP1_OUT         | Hi-Z(オープン・ドレイン)                        | Hi-Z(オープン・ドレイン)             |

| DAC3_OUT/VREFIN3 | プルダウン入力                                | プルダウン入力                     |

| AMP1_OUT         | プルダウン                                  | プルダウン                       |

| TEMP_OUT         | プルダウン                                  | プルダウン                       |

| AMPINP1          | Hi-Z                                   | Hi-Z                        |

| AMPINM1          | Hi-Z                                   | Hi-Z                        |

| DAC1_OUT/VREFIN1 | プルダウン入力                                | プルダウン入力                     |

| SCLK             | プルアップ入力                                | プルアップ入力                     |

| SDO              | Hi-Z(オープン・ドレイン)                        | Hi-Z(オープン・ドレイン)             |

| SDI              | プルアップ入力                                | プルアップ入力                     |

| <u>cs</u>        | プルアップ入力                                | プルアップ入力                     |

#### 6.2 リセットを制御するレジスタ

#### (1) リセット制御レジスタ (RC)

リセット制御レジスタ (RC) は、リセットを制御するレジスタです。

RESET ビットへの 1 ライトにより、内部リセットを発生させることができます。リセット制御レジスタ (RC) 自身の初期化 (00H) は、RESET 端子による外部リセット、または POR 回路による内部リセット、もしくは RESET ビットへの 0 ライトにより行います。

アドレス: 0CH リセット時: 00H <sup>注</sup> R/W

| 略号 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|----|---|---|---|---|---|---|---|-------|

| RC | 0 | 0 | 0 | 0 | 0 | 0 | 0 | RESET |

| RESET | 内部リセット信号の要求                 |

|-------|-----------------------------|

| 0     | 内部リセット信号を要求しない、または内部リセットの解除 |

| 1     | 内部リセット信号を要求、または内部リセット信号が発生中 |

- 注 リセット制御レジスタ (RC) による内部リセットの場合、リセット制御レジスタ (RC) は初期化 (00H) されません。RESET 端子への外部リセット入力、POR 回路による内部リセット、または、RESET ビットへの 0 ライトにより初期化 (00H) されます。

- 注意 RESET ビット= 1 の場合、リセット制御レジスタ(RC)以外のレジスタへの書き込み動作は無視されます。 外部リセットもしくは POR 回路での内部リセットによるリセット制御レジスタ(RC)の初期化(00H)、も しくは RESET ビットへの 0 ライトにより、レジスタへの書き込みが可能となります。

- 備考 ビット 7~1 は 0 固定です。(1 ライトによる書き換え禁止)

# 7. 電気的特性

### 7.1 絶対最大定格

$(T_A = 25^{\circ}C)$

| 項目     | 略号               | 条件                                                                                                                                         | 定格                           | 単位 |

|--------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----|

| 電源電圧   | AVDD             | AVDD1, AVDD2, AVDD3, AVDD4, AVDD5                                                                                                          | -0.3~+6.0                    | V  |

|        | DV <sub>DD</sub> | DV <sub>DD</sub>                                                                                                                           | -0.3~+6.0                    | V  |

|        | AGND             | AGND1, AGND2, AGND3,<br>AGND4, AGND5, AGND6,<br>AGND7                                                                                      | -0.3~+0.3                    | V  |

|        | DGND             | DGND                                                                                                                                       | -0.3~+0.3                    | V  |

| 入力電圧   | Vii              | AMPINP1, AMPINP2, AMPINP3, AMPINP4, AMPINM1, AMPINM2, AMPINM3, AMPINM4, VREFIN1, VREFIN2, VREFIN3, VREFIN4, VREFIN5, RESET                 | -0.3~AVDD + 0.3 <sup>注</sup> | V  |

|        | V <sub>12</sub>  | SCLK, SDI, CS                                                                                                                              | -0.3∼DVpp + 0.3 <sup>注</sup> | V  |

| 出力電圧   | Vo1              | AMP1_OUT, AMP2_OUT, AMP3_OUT, AMP4_OUT, CMP1_OUT, CMP2_OUT, CMP3_OUT, CMP4_OUT, TEMP_OUT, DAC1_OUT, DAC2_OUT, DAC3_OUT, DAC4_OUT, DAC5_OUT | -0.3~AVDD + 0.3 <sup>注</sup> | V  |

|        | Vo <sub>2</sub>  | SDO                                                                                                                                        | -0.3~DVpp + 0.3 注            | V  |

| 出力電流   | lo <sub>1</sub>  | AMP1_OUT, AMP2_OUT, AMP3_OUT, AMP4_OUT, TEMP_OUT, DAC1_OUT, DAC2_OUT, DAC3_OUT, DAC4_OUT, DAC5_OUT                                         | 1                            | mA |

|        | lo <sub>2</sub>  | CMP1_OUT, CMP2_OUT,<br>CMP3_OUT, CMP4_OUT                                                                                                  | 5                            | mA |

|        | Юз               | SDO                                                                                                                                        | -10                          | mA |

| 動作周囲温度 | TA               |                                                                                                                                            | -40 <b>~</b> +105            | °C |

| 保存温度   | Tstg             |                                                                                                                                            | -40 <b>~</b> +125            | °C |

注 6.0 V 以下であること。

注意 各項目のうち1項目でも、また一瞬でも絶対最大定格を越えると、製品の品質を損なう恐れがあります。 つまり絶対最大定格とは、製品に物理的損傷を与えかねない定格値です。必ずこの定格値を超えない状態で、製品 をご使用ください。

### ★ 7.2 動作条件

| 項目     | 略号    | 条件                                         | MIN | TYP | MAX | 単位 |

|--------|-------|--------------------------------------------|-----|-----|-----|----|

| 電源電圧範囲 | VDDOP | AVDD1, AVDD2, AVDD3, AVDD4,<br>AVDD5, DVDD | 3.0 | I   | 5.5 | V  |

| 動作温度範囲 | Тор   |                                            | -40 | ı   | 105 | °C |

## 7.3 電源電流特性

$(-40^{\circ}C \leqq \text{ Ta} \leqq 105^{\circ}\text{C, AVdd1} = \text{AVdd2} = \text{AVdd3} = \text{AVdd4} = \text{AVdd5} = \text{DVdd} = 5.0 \text{ V, Rirefr} = 56 \text{ k}\Omega)$

| 項目   | 略号                  | 条件                   | 規格  |      |      | 単位 |

|------|---------------------|----------------------|-----|------|------|----|

|      |                     |                      | MIN | TYP  | MAX  |    |

| 電源電流 | Istby1 <sup>注</sup> | PC1 = 00H, PC2 = 00H | _   | 340  | 520  | μΑ |

|      | lm11 <sup>注</sup>   | PC1 = FFH, PC2 = 3FH | _   | 11.1 | 18.5 | mA |

|      |                     | CCn1, CCn2 = 0, 0    |     |      |      |    |

|      | I <sub>m12</sub> 注  | PC1 = FFH, PC2 = 3FH | _   | 9.8  | 16.8 | mA |

|      |                     | CCn1, CCn2 = 0, 1    |     |      |      |    |

|      | I <sub>m21</sub> 注  | PC1 = FFH, PC2 = 3FH | _   | 8.5  | 15.0 | mA |

|      |                     | CCn1, CCn2 = 1, 0    |     |      |      |    |

|      | I <sub>m22</sub> 注  | PC1 = FFH, PC2 = 3FH | _   | 7.7  | 13.9 | mA |

|      |                     | CCn1, CCn2 = 1, 1    |     |      |      |    |

備考 n=1~4

注 AVDD1, AVDD2, AVDD3, AVDD4, AVDD5, DVDD 内部電源に流れるトータル電流です。ただし、プルアップ抵抗に流れる電流は含みません。入力端子を AVDD1, AVDD2, AVDD3, AVDD4, AVDD5, DVDD または AGND1, AGND2, AGND3, AGND4, AGND5, AGND6, AGND7, DGND に固定した状態での入力リーク電流は含みます。

### 7.4 各機能の電気的特性

## (1) コンパレータ内蔵高速計装アンプ(高速計装アンプ部)

$(-40^{\circ}C \le T_{A} \le 105^{\circ}C, AV_{DD1} = AV_{DD2} = AV_{DD3} = AV_{DD4} = AV_{DD5} = DV_{DD} = 5.0 \text{ V}, VREFINn = 1.75 \text{ V}, AMPnOF = 1, CMPnOF = 0, Rirefr = 56 k}$

|   | 項目             | 略号         | 条件                                                                                                                                         |                        | 規格   |                        | 単位  |

|---|----------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------------------------|-----|

|   |                |            |                                                                                                                                            | MIN                    | TYP  | MAX                    |     |

| 洋 | 肖費電流 注         | Icc00      | CCn1, CCn0 = 0, 0                                                                                                                          | -                      | 2.04 | 2.82                   | mA  |

|   |                | Icc01      | CCn1, CCn0 = 0, 1                                                                                                                          | -                      | 1.7  | 2.36                   | mA  |

|   |                | Icc10      | CCn1, CCn0 = 1, 0                                                                                                                          | -                      | 1.28 | 1.88                   | mA  |

|   |                | lcc11      | CCn1, CCn0 = 1, 1                                                                                                                          | _                      | 1.02 | 1.58                   | mA  |

| 7 | 入力電圧           | VINL       |                                                                                                                                            | AGND+0.72              | _    | _                      | V   |

|   |                | VINH       |                                                                                                                                            | _                      | _    | AV <sub>DD</sub> - 2.0 | V   |

| Н | 出力電圧           | VOUTL      | IOL = -0.2 mA, CCn1, CCn0 = 0, 0                                                                                                           | _                      | _    | AGND+0.2               | V   |

|   |                | VOUTH      | IOH = +0.2 mA, CCn1, CCn0 = 0, 0                                                                                                           | AV <sub>DD</sub> - 0.2 | _    | _                      | V   |

|   | セットリング・<br>タイム | tset_ampoo | CCn1, CCn0 = 0, 0<br>GCn3, GCn2, GCn1, GCn0 = 0, 0, 0, 0 (10 dB)<br>CL = 30 pF, 出力電圧 1V <sub>PP</sub> 時,<br>出力収束電圧 V <sub>PP</sub> =999 mV | -                      | -    | 0.6                    | μѕ  |

|   |                | tset_amp01 | CCn1, CCn0 = 0, 1<br>GCn3, GCn2, GCn1, GCn0 = 0, 0, 0, 0 (10 dB)<br>CL = 30 pF, 出力電圧 1V <sub>PP</sub> 時,<br>出力収束電圧 V <sub>PP</sub> =999 mV | -                      | -    | 0.7                    | μs  |

|   |                | tset_amp10 | CCn1, CCn0 = 1, 0<br>GCn3, GCn2, GCn1, GCn0 = 0, 0, 0, 0 (10 dB)<br>CL = 30 pF, 出力電圧 1V <sub>PP</sub> 時,<br>出力収束電圧 V <sub>PP</sub> =999 mV | -                      | -    | 1.0                    | μs  |

|   |                | tset_amp11 | CCn1, CCn0 = 1, 1<br>GCn3, GCn2, GCn1, GCn0 = 0, 0, 0, 0 (10 dB)<br>CL = 30 pF, 出力電圧 1V <sub>PP</sub> 時,<br>出力収束電圧 V <sub>PP</sub> =999 mV | -                      | -    | 1.8                    | μѕ  |

| 禾 | 刊得帯域幅          | GBW00      | RL = 無負荷, CL = 30 pF,<br>VREFINn = 1.5~1.75 V<br>CCn1, CCn0 = 0, 0<br>GCn3, GCn2, GCn1, GCn0 = 1, 0, 0, 0 (26 dB)                          | -                      | 10   | -                      | MHz |

|   |                | GBW01      | RL = 無負荷、CL = 30 pF,<br>VREFINn = 1.5~1.75 V<br>CCn1, CCn0 = 0, 1<br>GCn3, GCn2, GCn1, GCn0 = 1, 0, 0, 0 (26 dB)                           | _                      | 8.5  | _                      | MHz |

|   |                | GBW10      | RL = 無負荷、CL = 30 pF,<br>VREFINn = 1.5~1.75 V<br>CCn1, CCn0 = 1, 0<br>GCn3, GCn2, GCn1, GCn0 = 1, 0, 0, 0 (26 dB)                           | -                      | 7    | -                      | MHz |

|   |                | GBW11      | RL = 無負荷、CL = 30 pF,<br>VREFINn = 1.5~1.75 V<br>CCn1, CCn0 = 1, 1<br>GCn3, GCn2, GCn1, GCn0 = 1, 0, 0, 0 (26 dB)                           | -                      | 5    | -                      | MHz |

注 コンパレータ部の動作停止状態における、高速計装アンプ×1チャネル分の値です。

備考 n=1~4

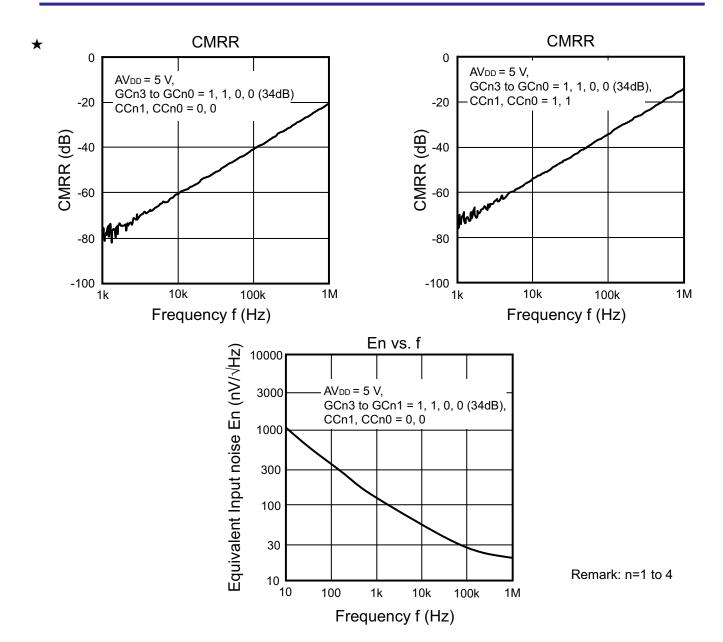

| 項目      | 略号     | 条件                                          |     | 規格  |     | 単位    |

|---------|--------|---------------------------------------------|-----|-----|-----|-------|

|         |        |                                             | MIN | TYP | MAX |       |

| 入力換算ノイズ | En00   | f = 1 kHz,                                  | _   | 125 | _   | nV/   |

|         |        | CCn1, CCn0 = 0, 0                           |     |     |     | √Hz   |

|         |        | GCn3, GCn2, GCn1, GCn0 = 1, 0, 0, 0 (26 dB) |     |     |     |       |

|         | En01   | f = 1 kHz                                   | -   | 130 |     | nV/   |

|         |        | CCn1, CCn0 = 0, 1                           |     |     |     | √Hz   |

|         |        | GCn3, GCn2, GCn1, GCn0 = 1, 0, 0, 0 (26 dB) |     |     |     |       |

|         | En10   | f = 1 kHz                                   | _   | 135 | _   | nV/   |

|         |        | CCn1, CCn0 = 1, 0                           |     |     |     | √Hz   |

|         |        | GCn3, GCn2, GCn1, GCn0 = 1, 0, 0, 0 (26 dB) |     |     |     |       |

|         | En11   | f = 1 kHz                                   | -   | 155 | _   | nV/   |

|         |        | CCn1, CCn0 = 1, 1                           |     |     |     | √Hz   |

|         |        | GCn3, GCn2, GCn1, GCn0 = 1, 0, 0, 0 (26 dB) |     |     |     |       |

| 入力換算    | VOFF   | CCn1, CCn0 = 0, 0                           | -10 | _   | +10 | mV    |

| オフセット電圧 |        | GCn3, GCn2, GCn1, GCn0 = 1, 0, 0, 0 (26 dB) |     |     |     |       |

| 入力換算    | VOTC   |                                             | _   | ±6  | _   | μV/°C |

| オフセット   |        |                                             |     |     |     |       |

| 電圧温度係数  |        |                                             |     |     |     |       |

| スルーレート  | SR00   | CL = 30 pF,                                 | -   | 20  | _   | V/μs  |

|         |        | CCn1, CCn0 = 0, 0                           |     |     |     |       |

|         |        | GCn3, GCn2, GCn1, GCn0 = 0, 0, 0, 0 (10 dB) |     |     |     |       |

|         | SR01   | CL = 30 pF,                                 | -   | 15  |     | V/μs  |

|         |        | CCn1, CCn0 = 0, 1                           |     |     |     |       |

|         |        | GCn3, GCn2, GCn1, GCn0 = 0, 0, 0, 0 (10 dB) |     |     |     |       |

|         | SR10   | CL = 30 pF,                                 | -   | 10  | -   | V/μs  |

|         |        | CCn1, CCn0 = 1, 0                           |     |     |     |       |

|         |        | GCn3, GCn2, GCn1, GCn0 = 0, 0, 0, 0 (10 dB) |     |     |     |       |

|         | SR11   | CL = 30 pF,                                 | -   | 5   |     | V/μs  |

|         |        | CCn1, CCn0 = 1, 1                           |     |     |     |       |

|         |        | GCn3, GCn2, GCn1, GCn0 = 0, 0, 0, 0 (10 dB) |     |     |     |       |

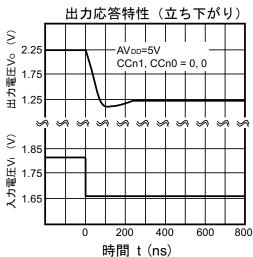

| 同相信号除去比 | CMRR00 | f = 1 kHz,                                  | -   | 75  |     | dB    |

|         |        | CCn1, CCn0 = 0, 0                           |     |     |     |       |

|         |        | GCn3, GCn2, GCn1, GCn0 = 1, 0, 0, 0 (26 dB) |     |     |     |       |

|         | CMRR01 | f = 1 kHz                                   | _   | 74  | -   | dB    |

|         |        | CCn1, CCn0 = 0, 1                           |     |     |     |       |

|         |        | GCn3, GCn2, GCn1, GCn0 = 1, 0, 0, 0 (26 dB) |     |     |     |       |

|         | CMRR10 | f = 1 kHz                                   | _   | 73  | _   | dB    |

|         |        | CCn1, CCn0 = 1, 0                           |     |     |     |       |

|         |        | GCn3, GCn2, GCn1, GCn0 = 1, 0, 0, 0 (26 dB) |     |     |     |       |

|         | CMRR11 | f = 1 kHz                                   | _   | 72  | _   | dB    |

|         |        | CCn1, CCn0 = 1, 1                           |     |     |     |       |

|         |        | GCn3, GCn2, GCn1, GCn0 = 1, 0, 0, 0 (26 dB) |     |     |     |       |

備考 n = 1~4

| 項目      | 略号         | 条件                                           |      | 規格  |     | 単位 |

|---------|------------|----------------------------------------------|------|-----|-----|----|

|         |            |                                              | MIN  | TYP | MAX |    |

| 電源電圧    | PSRR00     | f = 1 kHz,                                   | _    | 60  | _   | dB |

| 変動除去比   |            | CCn1, CCn0 = 0, 0                            |      |     |     |    |

|         |            | GCn3, GCn2, GCn1, GCn0 = 1, 0, 0, 0 (26 dB)  |      |     |     |    |

|         |            | VCM = AGND + 0.72 V∼AV <sub>DD</sub> - 2.5 V |      |     |     |    |

|         | PSRR01     | f = 1 kHz,                                   | _    | 63  | _   | dB |

|         |            | CCn1, CCn0 = 0, 1                            |      |     |     |    |

|         |            | GCn3, GCn2, GCn1, GCn0 = 1, 0, 0, 0 (26 dB)  |      |     |     |    |

|         |            | VCM = AGND + 0.72 V∼AV <sub>DD</sub> - 2.5 V |      |     |     |    |

|         | PSRR10     | f = 1 kHz,                                   | _    | 65  | _   | dB |

|         |            | CCn1, CCn0 = 1, 0                            |      |     |     |    |

|         |            | GCn3, GCn2, GCn1, GCn0 = 1, 0, 0, 0 (26 dB)  |      |     |     |    |

|         |            | VCM = AGND + 0.72 V∼AV <sub>DD</sub> - 2.5 V |      |     |     |    |

|         | PSRR11     | f = 1 kHz,                                   | _    | 65  | _   | dB |

|         |            | CCn1, CCn0 = 1, 1                            |      |     |     |    |

|         |            | GCn3, GCn2, GCn1, GCn0 = 1, 0, 0, 0 (26 dB)  |      |     |     |    |

|         |            | VCM = AGND + 0.72 V∼AV <sub>DD</sub> - 2.5 V |      |     |     |    |

| ゲイン設定誤差 | GAIN_Accu1 | $T_A = 25^{\circ}C$                          | -0.8 | _   | 0.8 | dB |

|         |            | VCM = AGND + 0.72V~AVDD - 2.5 V              |      |     |     |    |

|         | GAIN_Accu2 |                                              | -1.2 | _   | 1.2 | dB |

|         |            | $VCM = AGND + 0.72V \sim AVDD - 2.5 V$       |      |     |     |    |

備考 n = 1~4

## (2) コンパレータ内蔵高速計装アンプ(コンパレータ部)

$(-40^{\circ}C \le T_{A} \le 105^{\circ}C, AV_{DD1} = AV_{DD2} = AV_{DD3} = AV_{DD4} = AV_{DD5} = DV_{DD} = 5.0V, VREFINn = 1.75 V, AMPnOF = 0, CMPnOF = 1, Rirefr = 56 k\Omega)$

| 項目                | 略号     | 条件                                          | 規格         |            |                        | 単位 |

|-------------------|--------|---------------------------------------------|------------|------------|------------------------|----|

|                   |        |                                             | MIN        | TYP        | MAX                    |    |

| 消費電流 <sup>注</sup> | Icc00  |                                             | -          | 68         | 92                     | μΑ |

| 同相入力              | VIL    | HYSn1, HYSn0 = 1, 1                         | AGND + 0.1 | ı          | -                      | ٧  |

| 電圧範囲              | ViH    | HYSn1, HYSn0 = 1, 1                         | _          | ı          | AV <sub>DD</sub> - 2.0 | V  |

| 出力電圧範囲            | VOL    | RL = $2.2 kΩ \pm 1 \%$                      | _          | AGND + 0.1 | AGND + 0.2             | ٧  |

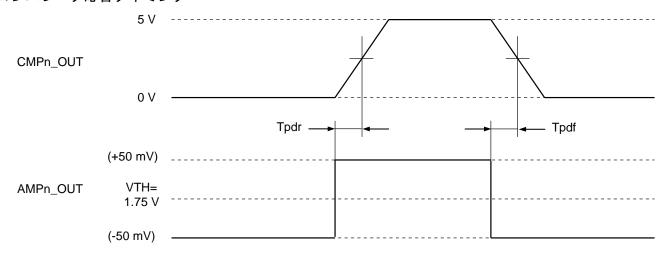

| 応答時間              | Tpdr   | VREFIN5 = 1.0V, HYSn1, HYSn0 = 1, 1,        | _          | 100        | 150                    | ns |

|                   |        | CL = 20 pF, RL = 2.2 k $\Omega$ , オーバー・ドライブ |            |            |                        |    |

|                   | Tpdf   | 電圧 = 100 mV                                 | _          | 40         | 100                    | ns |

| ヒステリシス            | HYST00 | HYSn1, HYSn0 = 0, 0                         | 100        | 200        | 305                    | mV |

|                   | HYST01 | HYSn1, HYSn0 = 0, 1                         | 45         | 100        | 151                    | mV |

|                   | HYST10 | HYSn1, HYSn0 = 1, 0                         | 19         | 50         | 78                     | mV |

| 入力オフセット           | VOFF   | VREFIN5 = 1.75 V                            | -10        | _          | 10                     | mV |

| 電圧                |        |                                             |            |            |                        |    |

注 高速計装アンプ部の動作停止状態における、コンパレータ×1チャネル分の値です。

備考 n = 1~5

## コンパレータ応答タイミング

備考 n=1~4

## (3) D/A コンバータ

$(-40^{\circ}C \leq T_{A} \leq 105^{\circ}C, \text{ AVdd1} = \text{AVdd2} = \text{AVdd3} = \text{AVdd4} = \text{AVdd5} = \text{DVdd} = 5.0 \text{ V}, \text{ DACnOF} = 1, \text{ Rirefr} = 56 \text{ k}\Omega)$

| 項目        | 略号     | 条件                      | 規格  |      | 単位   |     |

|-----------|--------|-------------------------|-----|------|------|-----|

|           |        |                         | MIN | TYP  | MAX  |     |

| 消費電流      | I_DAC1 | VR2, VR1, VR0 = 0, 0, 0 | _   | 1.37 | 1.72 | mA  |

|           | I_DAC2 | VR2, VR1, VR0 = 0, 1, 0 | _   | 2.13 | 2.7  | mA  |

| 分解能       | Res    |                         | _   | ı    | 8    | bit |

| セットリング・   | tset   |                         | -   | -    | 100  | μs  |

| タイム       |        |                         |     |      |      |     |

| 微分直線性誤差 注 | DNL    | VR2, VR1, VR0 = 0, 0, 0 | -2  |      | 2    | LSB |

| 積分直線性誤差   | INL    | VR2, VR1, VR0 = 0, 0, 0 | -2  | _    | 2    | LSB |

注 単調性は保証されます。

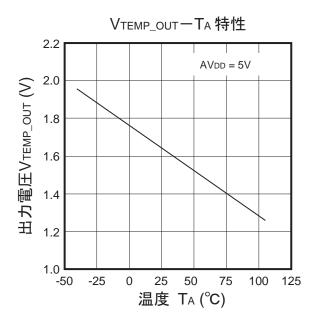

## (4) 温度センサ回路

$(-40^{\circ}C \leq T_{A} \leq 105^{\circ}C, \text{ AVdd1} = \text{AVdd2} = \text{AVdd3} = \text{AVdd4} = \text{AVdd5} = \text{DVdd} = 5.0 \text{ V}, \text{ TEMPOF} = 1, \text{ Rirefr} = 56 \text{ k}\Omega)$

| 項目   | 略号              | 条件                    | 規格  |      | 単位  |       |

|------|-----------------|-----------------------|-----|------|-----|-------|

|      |                 |                       | MIN | TYP  | MAX |       |

| 消費電流 | IccA            |                       | -   | 320  | 650 | μΑ    |

| 出力電圧 | Vo              | T <sub>A</sub> = 25°C | -   | 1.67 | ı   | V     |

| 温度感度 | T <sub>SE</sub> |                       | -   | -5.0 | ı   | mV/°C |

## (5) パワーオン·リセット(POR)回路

$(-40^{\circ}C \ \leq \ T_{\text{A}} \ \leq \ 105^{\circ}C, \ \text{AVdd1} = \text{AVdd2} = \text{AVdd3} = \text{AVdd4} = \text{AVdd5} = \text{DVdd} = 5.0 \ \text{V}, \ \text{Rirefr} = 56 \ \text{k}\Omega)$

| 項目     | 略号               | 条件       | 規格   |      | 単位   |    |

|--------|------------------|----------|------|------|------|----|

|        |                  |          | MIN  | TYP  | MAX  |    |

| 検出電圧   | VPOR             | 電源立ち上がり時 | 1.45 | 2.19 | 2.8  | V  |

|        | V <sub>PDR</sub> | 電源立ち下がり時 | 1.3  | 1.98 | 2.55 | V  |

| 最小パルス幅 | T <sub>PW</sub>  |          | 200  | ı    | _    | μs |

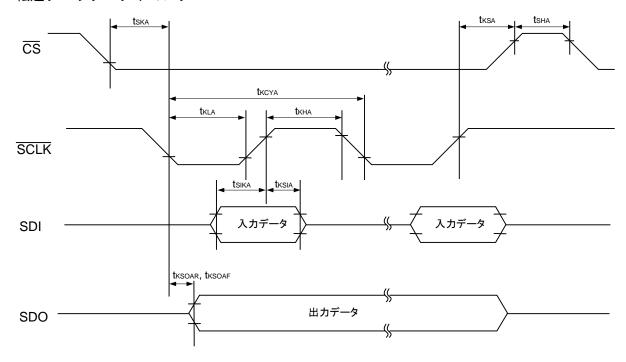

(6) SPI

$(-40^{\circ}C \leq T_{A} \leq 105^{\circ}C, AV_{DD1} = AV_{DD2} = AV_{DD3} = AV_{DD4} = AV_{DD5} = DV_{DD} = 5.0 \text{ V})$

|   | 項目                          | 略号            | 条件                                     |            | 規格               |                        | 単位 |

|---|-----------------------------|---------------|----------------------------------------|------------|------------------|------------------------|----|

|   |                             |               |                                        | MIN        | TYP              | MAX                    |    |

|   | ハイ・レベル入力電圧                  | VIH           | CS 端子,SDI 端子,SCLK 端子,<br>RESET 端子      | 2.0        | DV <sub>DD</sub> | DV <sub>DD</sub> + 0.1 | V  |

|   | ロウ・レベル入力電圧                  | VIL           | CS 端子,SDI 端子,SCLK 端子,<br>RESET 端子      | -0.1       | DGND             | 0.7                    | V  |

|   | ハイ・レベル                      | leak_Hi1      | CS 端子,SDI 端子,SCLK 端子                   | -1         | -                | 2                      | μΑ |

|   | 入力リーク電流                     | Ileak_Hi2     | RESET 端子                               | -1         | -                | 2                      | μΑ |

|   | ロウ・レベル                      | leak_Lo1      | CS 端子,SDI 端子,SCLK 端子                   | 50         | 100              | 200                    | μΑ |

|   | 入力リーク電流 <sup>注</sup>        | leak_Lo2      | RESET 端子                               | -1         | _                | 2                      | μΑ |

| * | SDO 端子<br>ロウ・レベル出力電圧        | VsDO_Lo       | Io = -5 mA                             | -          | 120              | 300                    | mV |

|   | SDO 端子<br>OFF 時リーク電流        | leak_SDO      |                                        | -1         | -                | 2                      | μА |

|   | プルアップ抵抗                     | Rspi          | CS 端子,SDI 端子,SCLK 端子                   | 32.5       | 50               | 67.5                   | kΩ |

|   | SCLK<br>サイクル・タイム            | <b>t</b> KCYA |                                        | 100        | -                | -                      | ns |

|   | SCLK<br>ハイ・レベル幅,<br>ロウ・レベル幅 | tkha,<br>tkla |                                        | 0.9tkcya/2 | -                | _                      | ns |

|   | SDI セットアップ時間<br>(対 SCLK↑)   | <b>t</b> sika |                                        | 40         | -                | _                      | ns |

| * | SDI ホールド時間<br>(対 SCLK↑)     | <b>t</b> ksia |                                        | 10         | -                | _                      | ns |

|   | SCLK ↓ →SDO 出力<br>遅延時間      | tksoar        | プルアップ抵抗 10 kΩ、CL = 5 pF、<br>VSDO = 5 V | -          | 250              | 300                    | ns |

|   |                             | tksoaf        | プルアップ抵抗 10kΩ、CL = 5 pF、<br>VSDO = 5 V  | -          | -                | 20                     | ns |

|   | CS ハイ・レベル幅                  | <b>t</b> sha  |                                        | 200        | -                | -                      | ns |

|   | <br>CS↓→SCLK↓<br>遅延時間       | <b>t</b> ska  |                                        | 200        | _                | _                      | ns |

|   | SCLK↑→CS↑<br>遅延時間           | <b>t</b> ksa  |                                        | 200        | -                | -                      | ns |

注 プルアップ抵抗に流れる電流を含みます。

# SPI 転送クロック・タイミング

RAA730502 8. PKG 外形図

# 8. PKG 外形図

RAA730502 特性曲線

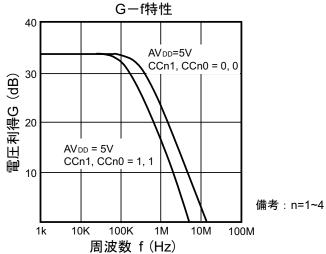

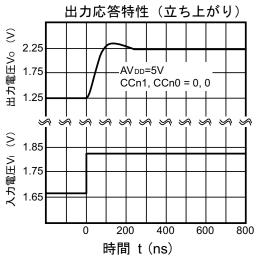

# 特性曲線 (TA = 25°C, TYP.) (参考值)

• コンパレータ内蔵高速計装アンプ (高速計装アンプ部)

RAA730502 特性曲線

RAA730502 特性曲線

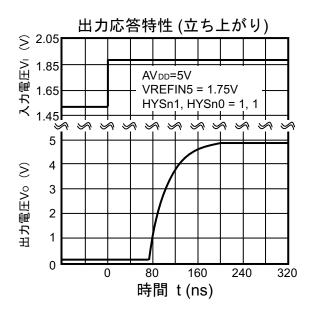

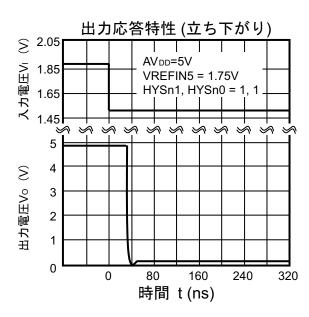

• コンパレータ内蔵高速計装アンプ (コンパレータ部)

備考:n=1~4

#### 温度センサ

改訂記録

RAA730502

モノリシック・プログラマブル・アナログ IC

| Rev. | 発行日        | ページ | ポイント                                                       |

|------|------------|-----|------------------------------------------------------------|

| 0.01 | 2011.09.05 | -   | 初版発行                                                       |

| 0.02 | 2012.02.24 | 8   | 表 1-2 未使用時の端子処理の端子を追加 (RESET)                              |

|      |            | 12  | 図 1-1 入出力回路タイプ (4/5) の等価回路を変更                              |

|      |            | 28  | 5. 2 SPI 通信動作の説明,図 5-2 SPI 通信タイミングを変更                      |

|      |            | 29  | 表 6-1 リセット期間中の動作状態を変更                                      |

|      |            | 30  | 表 6-3 リセット後の端子状態を追加                                        |

|      |            | 31  | 7.1 絶対最大定格の出力電流 IO1 の単位を変更                                 |

|      |            |     | 7.1 絶対最大定格の出力電流 IO3 を追加                                    |

|      |            | 32  | 7.2 電源電圧の条件 (AVDD1~AVDD5, DVDD) を追加                        |

|      |            | 34  | 7.4(1) 利得帯域幅の規格値を変更                                        |

|      |            | 35  | (1) コンバータ内蔵高速計装アンプ (高速計装アンプ) に入力換算オフセット電<br>圧温度係数 VOTC を追加 |

|      |            |     | (1) コンバータ内蔵高速計装アンプ (高速計装アンプ) の GAIN_Accu2 削除               |

|      |            | 38  | 7.4(3) セットリングタイムの単位、積分直線性誤差の規格値を訂正                         |

|      |            | 39  | 7. 4 (5) SPI インターフェースの Plieak_Hi2, lieak_Lo2 を追加           |

|      |            | 00  | 7. 4 (5) SPI インターフェースの tksoar の規格値を変更                      |

|      |            |     | 7. 4 (5) SPI インターフェースに注を追加                                 |

| 1.00 | 2012.08.30 | 2   | オーダ情報、型名を追加                                                |

|      |            | 14  | 図 1-1 入出力回路タイプ (5/5) の等価回路を変更                              |

|      |            | 31  | 表 6-3 リセット後の端子状態の I/O を削除                                  |

|      |            | 43  | 特性曲線(T <sub>A</sub> = 25℃, TYP.)(参考値)を追加                   |

| 1.01 | 2012.09.07 | 40  | 7. 4 (6) SPI インターフェースの規格値を変更                               |

| 1.10 | 2013.01.31 | 38  | 7.4(2) コンパレータ内蔵高速計装アンプ(コンパレータ部)の応答時間の規格値を変更                |

|      |            | 40  | 7. 4 (6) SPI の FSCLK を削除                                   |

|      |            |     | 7. 4 (6) SPI にプルアップ抵抗を追加                                   |

| 1.20 | 2014.05.31 | 15  | 2.1 コンパレータ内蔵高速計装アンプ 基準電圧に関する記述の変更。                         |

|      |            | 19  | 3.1 D/A コンバータ出力電圧値の算出式を訂正。                                 |

|      |            | 20  | 3. 3 (2) DAC 基準制御レジスタ(DACRC)に関する記述の変更。                     |

|      |            | 27  | 5 SPI 外部リセットに関する注意の追加。                                     |

|      |            | 29  | 6 リセット機能に関する記述の変更。                                         |

|      |            | 33  | 7.1 ジャンクション温度を削除。                                          |

|      |            | 34  | 7.2 「動作条件」に変更。                                             |

|      |            | 35  | 7.4(1) ゲイン設定誤差を追加。                                         |

|      |            | 40  | 7. 4 (6) SDO 端子ロウ・レベル出力電圧(TYP.)、SDI ホールド時間を訂正。             |

|      |            | 44  | 特性曲線(T <sub>A</sub> = 25℃, TYP.)(参考値)を変更                   |

すべての商標および登録商標は、それぞれの所有者に帰属します。

#### CMOSデバイスの一般的注意事項

- (1) 入力端子の印加波形:入力ノイズや反射波による波形歪みは誤動作の原因になりますので注意してください。 CMOSデバイスの入力がノイズなどに起因して、VL(MAX.)からVH(MIN.)までの領域にとどまるような 場合は、誤動作を引き起こす恐れがあります。入力レベルが固定な場合はもちろん、VL(MAX.)からVH(MIN.) までの領域を通過する遷移期間中にチャタリングノイズ等が入らないようご使用ください。

- (2) 未使用入力の処理: CMOSデバイスの未使用端子の入力レベルは固定してください。未使用端子入力については、CMOSデバイスの入力に何も接続しない状態で動作させるのではなく、プルアップかプルダウンによって入力レベルを固定してください。また、未使用の入出力端子が出力となる可能性(タイミングは規定しません)を考慮すると、個別に抵抗を介してVpoまたはGNDに接続することが有効です。資料中に「未使用端子の処理」について記載のある製品については、その内容を守ってください。

- (3) 静電気対策: MOSデバイス取り扱いの際は静電気防止を心がけてください。MOSデバイスは強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、当社が出荷梱包に使用している導電性のトレーやマガジン・ケース、または導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。また、MOSデバイスを実装したボードについても同様の扱いをしてください。

- (4) 初期化以前の状態 電源投入時、MOSデバイスの初期状態は不定です。電源投入時の端子の出力状態や入出力設定、レジスタ内容などは保証しておりません。ただし、リセット動作やモード設定で定義している項目については、これらの動作ののちに保証の対象となります。リセット機能を持つデバイスの電源投入後は、まずリセット動作を実行してください。

- (5) 電源投入切断順序 内部動作および外部インタフェースで異なる電源を使用するデバイスの場合,原則として内部電源を投入した後に外部電源を投入してください。切断の際には,原則として外部電源を切断した後に内部電源を切断してください。逆の電源投入切断順により,内部素子に過電圧が印加され,誤動作を引き起こしたり,異常電流が流れ内部素子を劣化させたりする場合があります。資料中に「電源投入切断シーケンス」についての記載のある製品については,その内容を守ってください。

- (6) 電源OFF時における入力信号 当該デバイスの電源がOFF状態の時に、入力信号や入出力プルアップ電源を入れないでください。入力信号や入出力プルアップ電源からの電流注入により、誤動作を引き起こしたり、 異常電流が流れ内部素子を劣化させたりする場合があります。資料中に「電源OFF時における入力信号」についての記載のある製品については、その内容を守ってください。

#### ご注意書き

- 1. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器・システムの設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因して、お客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 2. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報 の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 3. 本資料に記載された製品データ、図、表、プログラム、アルゴリズム、応用回路例等の情報の使用に起因して発生した第三者の特許権、著作権その他の知的財産権 に対する侵害に関し、当社は、何らの責任を負うものではありません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許 諾するものではありません。

- 4. 当社製品を改造、改変、複製等しないでください。かかる改造、改変、複製等により生じた損害に関し、当社は、一切その責任を負いません。

- 5. 当社は、当社製品の品質水準を「標準水準」および「高品質水準」に分類しており、

各品質水準は、以下に示す用途に製品が使用されることを意図しております。

標準水準: コンピュータ、OA機器、通信機器、計測機器、AV機器、

家電、工作機械、パーソナル機器、産業用ロボット等

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、

防災・防犯装置、各種安全装置等

当社製品は、直接生命・身体に危害を及ぼす可能性のある機器・システム(生命維持装置、人体に埋め込み使用するもの等)、もしくは多大な物的損害を発生させるおそれのある機器・システム(原子力制御システム、軍事機器等)に使用されることを意図しておらず、使用することはできません。 たとえ、意図しない用途に当社製品を使用したことによりお客様または第三者に損害が生じても、当社は一切その責任を負いません。 なお、ご不明点がある場合は、当社営業にお問い合わせください。

- 6. 当社製品をご使用の際は、当社が指定する最大定格、動作電源電圧範囲、放熱特性、実装条件その他の保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質および信頼性の向上に努めていますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害等を生じさせないよう、お客様の責任において、冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、お客様の機器・システムとしての出荷保証を行ってください。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様の機器・システムとしての安全検証をお客様の責任で行ってください。

- 8. 当社製品の環境適合性等の詳細につきましては、製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に 関して、当社は、一切その責任を負いません。

- 9. 本資料に記載されている当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器・システムに使用することはできません。また、当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途に使用しないでください。当社製品または技術を輸出する場合は、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。

- 10. お客様の転売等により、本ご注意書き記載の諸条件に抵触して当社製品が使用され、その使用から損害が生じた場合、当社は何らの責任も負わず、お客様にてご負担して頂きますのでご了承ください。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを禁じます。

- 注1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社がその総株主の議決権の過半数 を直接または間接に保有する会社をいいます。

- 注2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

ルネサスエレクトロニクス株式会社

■営業お問合せ窓口

http://www.renesas.com

※営業お問合せ窓口の住所は変更になることがあります。最新情報につきましては、弊社ホームページをご覧ください。

ルネサス エレクトロニクス株式会社 〒100-0004 千代田区大手町2-6-2 (日本ビル)

■技術的なお問合せおよび資料のご請求は下記へどうぞ。 総合お問合せ窓口: http://japan.renesas.com/contact/