# RAA458100GNP / RAA457100GBM

Low Power Wireless Charging System Configuration and Function

R19AN0041EJ0100 Rev.1.00 2017.03.31

APPLICATION NOTE

## Outline

RAA458100 / RAA457100 are power control IC for wireless charging. RAA458100 / RAA457100 are suitable for small capacity Li-ion secondary battery charging and various battery charging systems can be constructed by some function setting pins.

To adjust transmission power automatically, and to set battery charging parameters (RAA457100 register) from a transmitter system can be realized by bi-directional wireless communication function implemented in RAA458100 / RAA457100. Also, register accessing to a main device (RxMCU) in a receiver system can be performed from a main device (TxMCU) in a transmitter system. This document describes some wireless charging system configuration examples, the wireless communication function and the automatic transmission power control function.

## Contents

1. Battery charging system configuration

- 1.1 Overview of pin function

- 1.2 Battery charging system configuration, operation and pin settings

- 1.3 Power transmission start or stop timing

- 1.4 Data configuration of EEPROM(TxROM)

- WPT communication function (communication function on wireless power transfer carrier)

2.1 Packet configuration of WPT communication

- 2.2 Modulation and demodulation method, and detailed demodulation function

- 3. Automatic transmission power control function and WPT communication procedure

- 3.1 Overview of automatic transmission power control function

- 3.2 WPT communication packet in ATPC Mode, MCU Control Mode

- 3.3 Automatic transmission power control timing

- 3.4 Control error and RECT pin converged voltage

- 3.5 Update timing for ADC output codes storage registers

- 3.6 WPT communication procedure in each charging system configuration

- 4. Error detection function

- 4.1 Error detection items and post-processing

- 4.2 Error detection items in each charging system configuration

- 4.3 Over power detection of transmission power

- 5. Test registers

## Abbreviations and the meanings

The following table shows the abbreviations and the meanings used in this document.

| Term                    | Description                                                                                                                                        |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| TxIC                    | Wireless charging system transmitter IC RAA458100GNP.                                                                                              |

| RxIC                    | Wireless charging system receiver IC RAA457100GBM.                                                                                                 |

| TxROM, EEPROM           | EEPROM in transmitter system.                                                                                                                      |

| TxMCU                   | The device connected to TxIC by 2-wire interface. (mainly microcomputer)                                                                           |

| RxMCU                   | The device connected to RxIC by 2-wire interface. (mainly microcomputer)                                                                           |

| Tx system               | Wireless charging transmitter system. It is constructed by "TxIC only" or "TxIC and TxMCU" or "TxIC and EEPROM".                                   |

| Rx system               | Wireless charging receiver system. It is constructed by "RxIC only" or "RxIC and RxMCU".                                                           |

| WPT communication       | Communication on wireless power transmission carrier signal.                                                                                       |

| Tx2Rx WPT communication | WPT communication from TxIC to RxIC.                                                                                                               |

| Rx2Tx WPT communication | WPT communication from RxIC to TxIC.                                                                                                               |

| T_Header                | The header of Tx2Rx WPT communication packet.                                                                                                      |

| R_Header                | The header of Rx2Tx WPT communication packet                                                                                                       |

| T_0xXX D[X]             | Register address and data bit of TxIC<br>(Example : T_0x02 D[4:1] means that TxIC register address is 0x02, register data bits are D4, D3, D2, D1) |

| R_0xXX D[X]             | Register address and data bit of RxIC.<br>(Example : R_0x10 D[7:5] means that RxIC register address is 0x10, register data bits are D7, D6, D5)    |

Remark : The values described in this document are reference values, not guaranteed.

RENESAS

## 1. Battery charging system configuration

## 1.1 Overview of pin function

A battery charging system which adapt to an application can be provided by the function setting pins of TxIC and RxIC. Table 1.1 shows pin function which is important when a battery charging system is constructed.

| Pin setting |                         |   | Description                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|-------------|-------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| TxIC        | CLKSEL                  |   | -                                                                                                                                                                                                   | pin. Reference clock frequency is 8 [MHz] regardless of clock source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| -           |                         | н |                                                                                                                                                                                                     | 8[MHz]) is selected for reference clock. CLKI pin should be set to low, CLKO pin should be open.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|             |                         | L |                                                                                                                                                                                                     | m TxMCU, or clock signal is generated by ceramic resonator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|             |                         |   | Clock from TxMCU                                                                                                                                                                                    | Clock is inputted to CLKI pin and CLKO pin is set to open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|             |                         |   | Clock generation                                                                                                                                                                                    | Ceramic resonator is connected between CLKI pin and CLKO pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|             | BRGSEL                  |   | -                                                                                                                                                                                                   | I bridge circuit to drive transmitting coil.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|             |                         | н |                                                                                                                                                                                                     | ed. Gate drive pulse is outputted from GD1H and GD1L pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|             |                         | L |                                                                                                                                                                                                     | ed. Gate drive pulse is outputted from GD1H, GD1L, GD2H and GD2L pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|             | GAIN                    |   | Parameter (GAIN) selectio                                                                                                                                                                           | n for the automatic transmission power control. Refer to section 3.4 for GAIN description.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|             |                         | н | GAIN=0.250                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             |                         | L | GAIN=0.125                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             | MS                      |   | Master or slave device sele                                                                                                                                                                         | ection for 2-wire interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|             |                         | Н | TxIC is master device of 2 should be set to high.                                                                                                                                                   | 2-wire interface in Tx system. When the register of TxIC and RxIC from TxROM is set, MS pin                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|             |                         | L |                                                                                                                                                                                                     | wire interface in Tx system. When the register of TxIC and RxIC from TxMCU is set, or when ed, MS pin should be set to low.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|             | ATPC                    |   | nable automatic transmission power control.                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             |                         | Н | In order to enable the auto                                                                                                                                                                         | matic transmission power control, ATPC pin should be set to high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|             |                         | L | In order to disable the auto                                                                                                                                                                        | matic transmission power control, ATPC pin should be set to low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|             | DUTY6<br>DUTY7<br>DUTY8 |   | can be set by DUTY6, DL<br>D[2:0], T_0x04 D[7:0]. For<br>"0" when DUTY pin level is<br>Duty=(100 / F_DRIVE) x ( 1                                                                                   | selection of bridge driver output pulse duty. When the register of duty (T_0x07 D[1:0], T_0x06 D[7:0]) can not be se<br>an be set by DUTY6, DUTY7 and DUTY8 pins. Duty is defined as below formula. F_DRIVE is register value of `<br>0[2:0], T_0x04 D[7:0]. For the value of DUTY8, DUTY7, DUTY6 in this formula, it is "1" when DUTY pin level is high a<br>" when DUTY pin level is low.<br>Duty=(100 / F_DRIVE) x ( 256 x DUTY8 + 128 x DUTY7 + 64 x DUTY6 ) [%]<br>If the register of TxIC can be set, duty should be set by register.) |  |  |  |  |  |  |

| RxIC        | MS                      |   | Master or slave device sele                                                                                                                                                                         | ection for 2-wire interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|             |                         | Н | RxIC is master device of 2-wire interface in Rx system. When the automatic transmission power control is ava register of RxIC and RxMCU can be written or read from Tx system by WPT communication. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             |                         | L | RxIC is slave device of 2-<br>interface.                                                                                                                                                            | wire interface in Rx system. The register of RxIC can be written or read from RxMCU by 2-wire                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|             | ATPC                    |   | Enable automatic transmis                                                                                                                                                                           | sion power control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|             |                         | Н | To enable the automatic tra                                                                                                                                                                         | ansmission power control, ATPC pin should be set to high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|             |                         | L | To disable the automatic tr                                                                                                                                                                         | ansmission power control, ATPC pin should be set to low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|             | ATCHG                   |   | Enable automatic start of b                                                                                                                                                                         | battery charging.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|             |                         | н | Battery charging is automa                                                                                                                                                                          | tically started when battery charging is available condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|             |                         | L | Battery charging is not au<br>setting the register R_0x01                                                                                                                                           | tomatically started even if battery charging is available condition. Battery charging is started by D[0]=1.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|             | ATR                     |   | Enable automatic control o<br>VCC regulator).                                                                                                                                                       | of rectifier circuit. The parameter of rectifier circuit is adjusted with load current (output current of                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|             |                         | н | Enable automatic control o                                                                                                                                                                          | f rectifier circuit parameter when both of ATPC and ATR pin are set to high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|             |                         | L | Disable automatic control of                                                                                                                                                                        | of rectifier circuit parameter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             | WRC                     |   | Enable wired charging mod                                                                                                                                                                           | de. <sup>•1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|             |                         |   |                                                                                                                                                                                                     | hen wired charging is needed, WRC pin is set to high. The wired charging system is available by applying DC voltage                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|             |                         | н | RECT pin directly.                                                                                                                                                                                  | seded, WRC pin is set to high. The wired charging system is available by applying DC voltage to                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Table1.1        | TxIC. | RxIC  | nin | function | outline |

|-----------------|-------|-------|-----|----------|---------|

| 1 4 5 1 5 1 . 1 | 1,10, | 11110 | pin | runction | outime  |

$^{\ast}1$  Wired charging system can not be combined with wireless charging system.

## 1.2 Battery charging system configuration, operation and pin setting

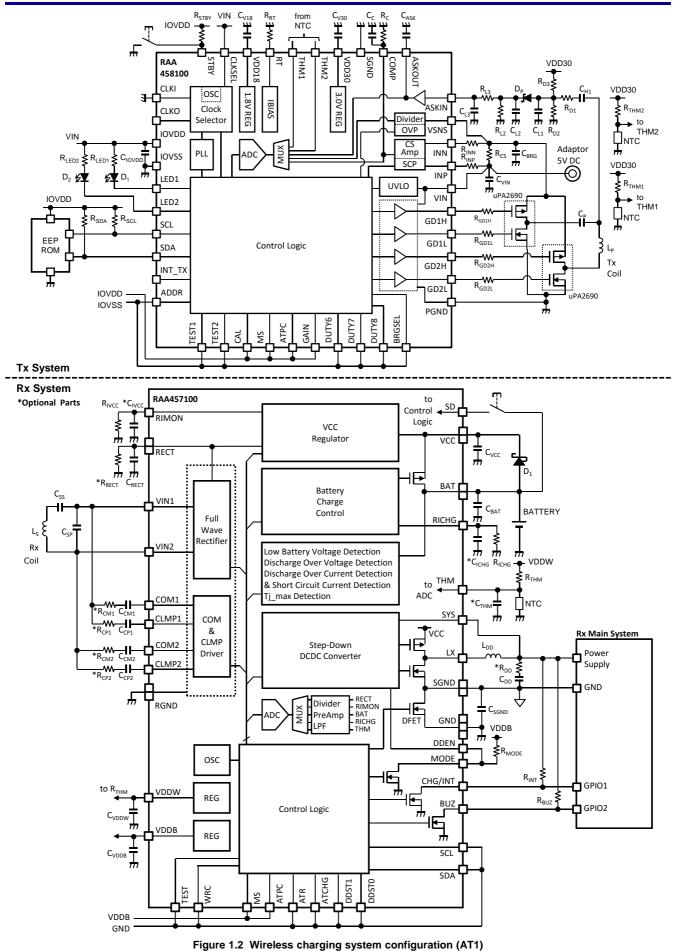

Table 1.2.1 and 1.2.2 show the battery charging system configuration and pin setting by using TxIC and RxIC. Figure 1.2 shows wireless charging system configuration (AT1). Depending on an application, an operation mode for a charging system is selected by the pin setting of TxIC and RxIC.

The control parameters such as bridge driver output pulse duty, thresholds of error detection, WPT communication parameters, charging control parameters can be set by TxIC registers and RxIC registers. Error conditions and ADC output codes can be monitored by reading the registers. The registers of TxIC can be written or read by 2-wire interface from external TxROM(EEPROM) or TxMCU in Tx system. The registers of RxIC can be written or read by WPT communication from Tx system (Tx2Rx WPT communication) or 2-wire interface from RxMCU. When RxIC is a master device of 2-wire interface, registers of RxIC can be written or read by Tx2Rx WPT communication from Tx system (AT1, AT2, AT3). When RxIC is a slave device of 2-wire interface, registers of RxIC can be written or read by 2-wire interface from RxMCU (AT4, MC1).

|               |     | n mode<br>method /      | Tx powe    | er control |                                                                                                                                                                                                                                                                                                                                                    | Descriptio                                                                                                                                                        | n                                                                                                                                |             |                              |                              |                                                                            |                                |                                   |

|---------------|-----|-------------------------|------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------|------------------------------|----------------------------------------------------------------------------|--------------------------------|-----------------------------------|

|               | Io. | Tx sys                  | stem *1    | Rx sy      | stem *1                                                                                                                                                                                                                                                                                                                                            | TxIC register         RxIC register           setting device         setting device                                                                               |                                                                                                                                  |             | Tx2Rx WPT                    | Rx2Tx WPT                    | Automatic transmission                                                     |                                |                                   |

|               |     | Master                  | Slave      | Master     | Slave                                                                                                                                                                                                                                                                                                                                              | TxROM                                                                                                                                                             | TxMCU                                                                                                                            | TxROM       | TxMCU                        | RxMCU                        | comm.                                                                      | comm.                          | power control                     |

|               |     | ne Mode<br>Fixed brid   | lge freque | ency and d | uty                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                   | The wireless power is transmitted in fixed frequency and duty of bridge driver output pulse. The TxIC can be set by TxROM (SA2). |             |                              |                              |                                                                            |                                |                                   |

| S             | A1  | -                       | TxIC       | RxIC       | -                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                 | -                                                                                                                                | -           | -                            | -                            | -                                                                          | -                              | -                                 |

| s             | A2  | TxIC                    | TxROM      | RxIC       | -                                                                                                                                                                                                                                                                                                                                                  | O *2                                                                                                                                                              | -                                                                                                                                | -           | -                            | -                            | -                                                                          | -                              | -                                 |

| ATP0<br>Wirel |     | de<br>Automatio         | c control  |            |                                                                                                                                                                                                                                                                                                                                                    | implement<br>system, the                                                                                                                                          | ed in TxIC a<br>e registers c                                                                                                    | nd RxIC. Th | ne registers<br>can be writt | of TxIC can<br>ten or read b | sion power is co<br>be written or rea<br>by Tx2Rx WPT c<br>T communication | ad from TxROM communication (A | or TxMCU in Tx<br>AT1, AT2, AT3). |

| A             | .T1 | TxIC                    | TxROM      | RxIC       | -                                                                                                                                                                                                                                                                                                                                                  | O *2                                                                                                                                                              | -                                                                                                                                | O *2        | -                            | -                            | 0                                                                          | 0                              | 0                                 |

| A             | T2  | TxMCU                   | TxIC       | RxIC       | -                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                 | 0                                                                                                                                | -           | 0                            | -                            | 0                                                                          | 0                              | 0                                 |

| A             | Т3  | TxMCU                   | TxIC       | RxIC       | RxMCU                                                                                                                                                                                                                                                                                                                                              | -                                                                                                                                                                 | 0                                                                                                                                | -           | 0                            | -                            | 0                                                                          | 0                              | 0                                 |

| A             | T4  | TxMCU                   | TxIC       | RxMCU      | RxIC                                                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                 | 0                                                                                                                                | -           | -                            | O *3                         | -                                                                          | 0                              | 0                                 |

|               |     | trol Mode<br>External I | MCU contr  | rol        | The registers of TxIC can be written and read from TxMCU by 2-wire interface. By using eac communication register of TxIC and RxIC, TxMCU and RxMCU can execute Tx2Rx and Rx2T communication for user original transmission power control and data communication. But the reg RxIC can't be written or read from TxMCU by Tx2Rx WPT communication. |                                                                                                                                                                   |                                                                                                                                  |             |                              |                              |                                                                            |                                | nd Rx2Tx WPT                      |

| N             | IC1 | TxMCU                   | TxIC       | RxMCU      | RxIC                                                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                 | 0                                                                                                                                | -           | 0                            | 0                            | -                                                                          |                                |                                   |

| Wire<br>Wire  |     | arging Moo              | de         |            |                                                                                                                                                                                                                                                                                                                                                    | The battery can be charged by DC voltage power like an AC adapter. DC voltage power is applied to RECT pin. The operation is limited in initial register setting. |                                                                                                                                  |             |                              |                              |                                                                            |                                | er is applied to                  |

| N             | /C1 | -                       | -          | RxIC       | -                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                 | -                                                                                                                                | -           | -                            | -                            | -                                                                          | -                              | -                                 |

#### Table 1.2.1 Battery charging system configuration and operation

\*1 Master means master device of 2-wire interface, and Slave means slave device of 2-wire interface.

\*2 TxROM needs to be set the register setting data of TxIC and RxIC previously. Refer to section 1.4.

\*3 The registers of RxIC can't be written or read from RxMCU in battery protection detection condition and maximum junction temperature detection condition, because SDA and SCL pin function of RxIC stops in that conditions. Also, R\_0x40 D[0] needs to be set "1" to write data in R\_0x00 to R\_0x0F.

#### Table 1.2.2 Battery charging system configuration and pin setting

| Operation mode |         |            |       |        |       | Тх | IC pin setti | ing     |             |          | Rx | IC pin sett | ng    |     |      |

|----------------|---------|------------|-------|--------|-------|----|--------------|---------|-------------|----------|----|-------------|-------|-----|------|

|                | No.     | Tx sy      | stem  | Rx sy  | /stem | MS | ATPC         | DUTY6   | DUTY7       | DUTY8    | MS | ATPC        | ATCHG | ATR | WRC  |

|                | NO.     | Master     | Slave | Master | Slave |    |              | Donto   | 20117       | Dorno    |    |             | Alono | AIN | WING |

| Sta            | and Alo | ne Mode    |       |        |       |    |              |         |             |          |    |             |       |     |      |

|                | SA1     | -          | TxIC  | RxIC   | -     | L  | L            | Set one | e or more p | ins to H | н  | L           | н     | L   | L    |

|                | SA2     | TxIC       | TxROM | RxIC   | -     | Н  | L            | Set one | e or more p | ins to H | н  | L           | н     | L   | L    |

| AT             | PC Mo   | de         |       |        |       |    |              |         |             |          |    |             |       |     |      |

|                | AT1     | TxIC       | TxROM | RxIC   | -     | Н  | н            | L       | L           | L        | Н  | н           | L     | х   | L    |

|                | AT2     | TxMCU      | TxIC  | RxIC   | -     | L  | н            | L       | L           | L        | Н  | н           | L     | х   | L    |

|                | AT3     | TxMCU      | TxIC  | RxIC   | RxMCU | L  | н            | L       | L           | L        | Н  | н           | L     | х   | L    |

|                | AT4     | TxMCU      | TxIC  | RxMCU  | RxIC  | L  | н            | L       | L           | L        | L  | н           | Н     | х   | L    |

| MC             | CU Con  | trol Mode  |       |        |       |    |              |         |             |          |    |             |       |     |      |

|                | MC1     | TxMCU      | TxIC  | RxMCU  | RxIC  | L  | L            | L       | L           | L        | L  | L           | н     | L   | L    |

| Wi             | red Cha | arging Mod | le    |        |       |    |              |         |             |          |    |             |       |     |      |

|                | WC1     | -          | -     | RxIC   | -     | -  | -            | -       | -           | -        | Н  | L           | Н     | L   | Н    |

X: Arbitrary value can be selected.

#### 1.3 Power transmission start / stop timing

Figure 1.3 shows the power transmission start and stop timing (GD1H, GD1L, GD2H, GD2L of bridge driver) of TxIC. In Stand Alone Mode, power transmission is started when Initial Mode (start processing) is finished. In ATPC Mode, power transmission is started when Initial Mode is finished, and the power is transferred intermittently until R\_Header 0x01 packet is received. In MCU Control Mode, power transmission can be started and stopped at any timing controlled by TxMCU.

Transmitter timer is started when operation state changes to Drive Mode. In Stand Alone Mode and ATPC Mode, power transmission is stopped when the timeout period of transmitter timer is detected. The timeout period can be set by register. Power transmission is stopped also when other error (refer to section 4.1) is detected, but transmitter timer is not reset.

TxIC continues power transmission even if battery charging is finished by RxIC, unless TxMCU stops power transmission in MCU Control Mode, or power transmission is stopped by transmitter timer or other error detection. While RxIC operates by transmission power in charging completion condition, RxIC consumes around 10[uA] current from battery for battery voltage monitor circuit in RxIC.

| Pin, Signal                                               |                            |        |             |                              |                                                          | TxIC operation state                                                                            |                           |                                      |  |

|-----------------------------------------------------------|----------------------------|--------|-------------|------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------|--------------------------------------|--|

| Pin, Signai                                               |                            | Pow    | er OFF      | Power On                     | Initial Mode                                             |                                                                                                 | Drive Mode                |                                      |  |

| VIN                                                       |                            |        |             |                              |                                                          |                                                                                                 |                           |                                      |  |

| IOVDD                                                     |                            |        |             |                              |                                                          |                                                                                                 |                           |                                      |  |

| STBY                                                      |                            |        |             |                              |                                                          |                                                                                                 |                           |                                      |  |

| VDD30<br>VDD18                                            |                            |        |             |                              |                                                          |                                                                                                 |                           |                                      |  |

| CLK<br>(System clock in                                   | ı TxIC)                    |        |             |                              |                                                          |                                                                                                 |                           |                                      |  |

| GD1H/GD1L/GD                                              | D2H/GD2                    | L      |             | <u>.</u>                     | <u>i</u>                                                 |                                                                                                 |                           |                                      |  |

| Stand Alone                                               | Mode                       |        |             |                              |                                                          |                                                                                                 |                           |                                      |  |

| ATPC Mode                                                 |                            |        | (Transitio  | T_<br>on from Initial Mode t | T <sub>TX_ID_TIMER</sub><br>0x00 D[1]=1<br>o Drive Mode) |                                                                                                 | R_Header_0x01 packet      | is received                          |  |

| MCU Contro                                                | l Mode                     |        | (Transitic  | T_<br>on from Initial Mode t | 0x00 D[1]=1<br>o Drive Mode)                             | T_0x00 D[0]=1<br>(Bridge driver ON)                                                             |                           | T_0x00 D[0]=0<br>(Bridge driver OFF) |  |

| Symbol                                                    | Registe                    | ers    | Descript    | ion                          |                                                          | :                                                                                               |                           |                                      |  |

| T <sub>TX_INIT</sub>                                      | -                          |        | set in this | s period. When T             | xROM is used, Tx                                         | than 520[ms] of period is ne<br>IC automatically loads the sto<br>xIC register in this period.  |                           |                                      |  |

| T <sub>TX_CHG_TIMER</sub>                                 | T_0x11<br>T_0x11<br>T_0x12 | D[7:6] | be set by   | / register T_0x11            | D[7:6] (198, 264, 3                                      | state of TxIC changes to Driv<br>330, 396[min]). Power transm<br>ssmission timer is unavailable | ission is stopped and T_0 | x12 D[5] is set to "1"               |  |

| T <sub>TX_ID_TIMER</sub> ,<br>T <sub>TX_ID_INTERVAL</sub> | T_0x35<br>T_0x4B           |        |             |                              |                                                          |                                                                                                 |                           |                                      |  |

Figure 1.3 Power transmission start / stop timing

RENESAS

#### 1.4 Data configuration of EEPROM(TxROM)

By applying EEPROM(TxROM) in Tx system, TxIC registers can be set. RxIC registers can be set by Tx2Rx WPT communication in ATPC Mode(AT1). TxIC reads the data from EEPROM in start process(Initial Mode), and set the data into the register of TxIC. For the RxIC register setting, TxIC reads the RxIC register data stored in EEPROM and it sends the data to RxIC by Tx2Rx WPT communication at proper timing. Tx2Rx WPT communication does not affect Rx2Tx WPT communication.

Table 1.4 shows the data configuration of EEPROM. Device slave address of EEPROM should be set 7'b1010000 or 7'b101001. TxIC reads the data which were stored in EEPROM in turn from word address "0" to the address that completion code was written. Read cycle is random read cycle. TxIC can not write data to the EEPROM.

#### Table 1.4 Slave address, read cycle, data configuration of EEPROM (TxROM)

|                           | Teau Cycle, data configurati    |                                                                                                                               |

|---------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Item                      | Description                     |                                                                                                                               |

| Communication method      | 2-wire serial communication (SC | CL frequency is fixed at 64[kHz].)                                                                                            |

| EEPROM                    | ADDR pin setting into low       | 7'b1010000                                                                                                                    |

| Device slave address      | ADDR pin setting into high      | 7'b1010001 (Evaluation board)                                                                                                 |

| EEPROM read cycle         | Random read cycle (Data readir  | ig is started from address "0" and increment word address by "1")                                                             |

| EEPROM word address       | Word address range is from "0"  | to "255". 2K bit EEPROM is available.                                                                                         |

| EEPROM data configuration | n                               |                                                                                                                               |

| EEPROM word address       | EEPROM data                     | Description                                                                                                                   |

| 0                         | TxIC register address           | TxIC register setting area.                                                                                                   |

| 1                         | TxIC register data              | "" Even address : TxIC register address     Odd address : TxIC register data                                                  |

| 2                         | TxIC register address           |                                                                                                                               |

| 3                         | TxIC register data              |                                                                                                                               |

|                           | :                               |                                                                                                                               |

| 2n-6                      | 0x48                            | When register of RxIC is set from TxIC by Tx2Rx WPT communication, it should be set                                           |

| 2n-5                      | 0x04                            | "" "T_0x48 D[7:0]=0x04" (Packet Header is specified).                                                                         |

| 2n-4                      | 0x00                            | After setting necessary register, T_0x00 D[1] should be set to "1".                                                           |

| 2n-3                      | 0x02                            | " (Operation state of TxIC changes from Initial Mode to Drive Mode.)                                                          |

| 2n-2                      | 0xFF                            | Completion code. Even address : 0xFF, odd address : 0x00                                                                      |

| 2n-1                      | 0x00                            | "TxIC register setting is finished.                                                                                           |

| 2n                        | 0xFE                            | Count setting of receiving packet in Rx2Tx WPT communication. Data "0xFE" is set in                                           |

| 2n+1                      | Count of receiving packet       | " even address, and count of receiving packet is set in odd address. (*1)                                                     |

| 2n+2                      | RxIC register address           | RxIC register setting area.                                                                                                   |

| 2n+3                      | RxIC register data              | "Even address : RxIC register address<br>odd address : RxIC register data                                                     |

| 2n+4                      | RxIC register address           | If register of RxIC does not need to be set, completion code should be set soon.<br>(Even address : 0xFF, odd address : 0x00) |

| 2n+5                      | RxIC register data              | (Even address . 0xFF, odd address . 0x00)                                                                                     |

| •                         | •                               |                                                                                                                               |

| •                         | •                               |                                                                                                                               |

| 2m-4                      | 0x01                            | After setting necessary register, R_0x01 D[0] should be set to "1" for starting battery charge.                               |

| 2m-3                      | 0x01                            |                                                                                                                               |

| 2m-2                      | 0xFF                            | Completion code. Even address : 0xFF, Odd address : 0x00<br>RxIC register setting is finished.                                |

| 2m-1                      | 0x00                            |                                                                                                                               |

\*1 When there is this setting, TxIC restarts to read from next word address after receiving Rx2Tx WPT communication packet "the setting value + 1" times. This operation is to perform over power detection of transmission power at power transmission start timing. If over power detection is not needed, this setting is not need.

## 2 WPT communication function (communication function on wireless power transfer carrier)

## 2.1 Packet configuration of WPT communication

WPT communication packet is fixed length (55bit) packet showed in Figure 2.1. The packet is configured with Preamble, Header, Message1, Message2, Checksum. Header and Message1 and Message2 have 1 bit of odd number parity bit each. The Checksum created by exclusive OR is added to the last of the packet.

| Preambl<br>(11bit) | St | Header<br>(8bit) | Pr | Sp | St | Message1<br>(8bit) | Pr | Sp | St | Message2<br>(8bit) | Pr | Sp | St | Checksum<br>(8bit) | Pr | Sp | ] |

|--------------------|----|------------------|----|----|----|--------------------|----|----|----|--------------------|----|----|----|--------------------|----|----|---|

|--------------------|----|------------------|----|----|----|--------------------|----|----|----|--------------------|----|----|----|--------------------|----|----|---|

St : Start bit(1bit), Pr : Parity bit(1bit), Sp : Stop bit(1bit)

Figure 2.1 WPT communication packet configuration

#### 2.2 Modulation and demodulation method, and detailed demodulation function

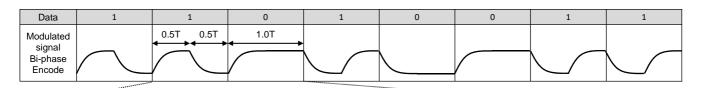

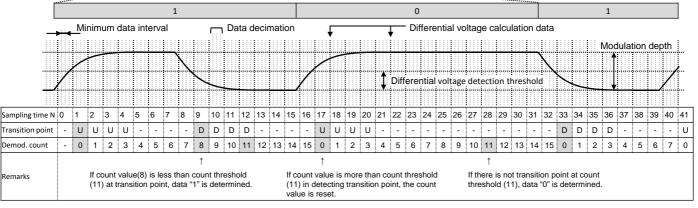

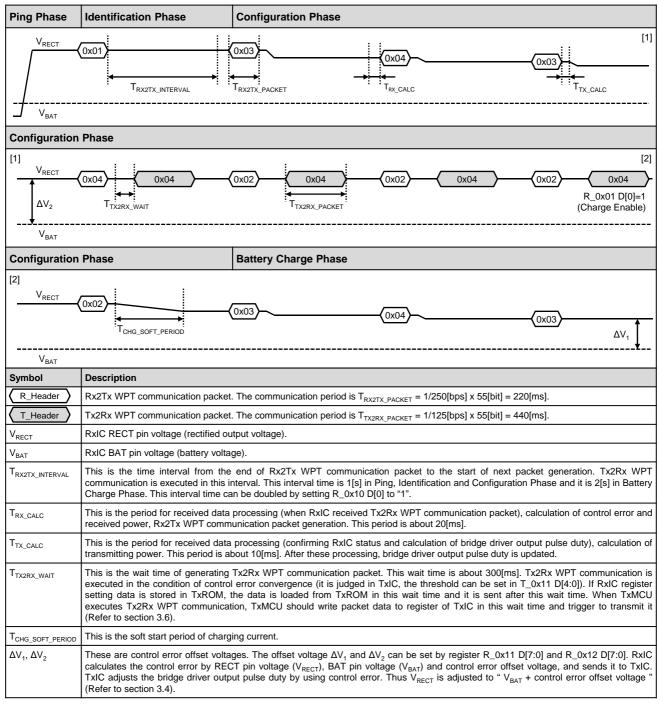

Tx2Rx and Rx2Tx WPT communication are performed by amplitude modulation and demodulation. Packet data is bi-phase encoded data. Table 2.2 shows the modulation and demodulation method of WPT communication and register parameters for demodulation. Figure 2.2 shows detailed demodulation method. The registers related to WPT communication should be set by TxMCU or TxROM for TxIC, and set by RxMCU for RxIC. The modulated signal of WPT communication (RECT pin voltage for Tx2Rx WPT communication and ASKOUT pin voltage for Rx2Tx WPT communication) is demodulated by ADC and demodulation logic circuit. Therefore modulated signal level including DC voltage needs to be within input dynamic range of ADC.

#### Table 2.2 Modulation and demodulation method of WPT communication and register parameters for demodulation

| Direction                                                              | Modulation a                                    | and demodula                                 | tion method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tx2Rx WPT<br>communication                                             | power becon                                     | nes the chang                                | nal by changing bridge driver output pulse duty depending on modulation signal. The change of the transmission<br>e of RECT pin voltage of RxIC. RECT pin voltage is converted to digital signal and demodulated by logic. The<br>quire the RECT pin voltage by ADC is 62.5[us].                                                                                                                                                                                                                                             |

| Rx2Tx WPT<br>communication                                             | switches CO<br>voltage is atte<br>through buffe | M driver (C <sub>CM</sub><br>enuated and its | gnal by load modulation depending on modulation signal. Power transmission line impedance changes when RxIC<br>) depending on modulation signal pattern. The transmitting coil voltage changes by the impedance shifting. The<br>s peak voltage is detected. The peak voltage is inputted to ASKIN pin. ASKIN pin voltage is outputted to ASKOUT pin<br>KOUT pin voltage is converted to digital signal and demodulated by logic. The minimum time interval to acquire the<br>C is 64[us].                                   |

| Parameters for demodulation                                            | TxIC<br>register                                | RxIC<br>register                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Modulation depth                                                       | T_0x0D<br>D[6:0]                                | -                                            | The changing range of bridge driver output pulse duty as modulation depth for Tx2Rx WPT communication is set by register T_0x0D D[6:0]. The register should be set so that the variation range of rectifier output voltage is higher than 200[mV] (recommended value). The C <sub>CM</sub> value should be set so that the variation range of ASKOUT pin voltage is higher than 100[mV] (recommended value) for Rx2Tx WPT communication.                                                                                     |

| Bit rate                                                               | T_0x0E<br>D[2:1]                                | R_0x27<br>D[1:0]                             | The bit rate in Tx2Rx WPT communication is 125[bps](1.0T=1/125=8[ms]) and the bit rate in Rx2Tx communication is 250[bps](1.0T=1/250=4[ms]). (Bit rate can be changed by register, but WPT communication parameters of RxIC should be set from RxMCU by 2-wire interface.)                                                                                                                                                                                                                                                   |

| Data decimation                                                        | T_0x30<br>D[3:0]                                | R_0x27<br>D[7:4]                             | Data decimation number can be set in range from 0 to 7 by register. The decimation number is 3 in Figure 2.2 for example.                                                                                                                                                                                                                                                                                                                                                                                                    |

| Differential voltage calculation data $(\Delta V_{DIFF})$              | T_0x30<br>D[5:4]                                | R_0x27<br>D[3:2]                             | Differential voltage $\Delta V_{\text{DIFF}}$ of modulated signal is calculated by formula V[N] - V[N - (m + 1)], where V is voltage of modulated signal, N is sampling time, m is integer. The m can be set in range from 0 to 3 by register. The m is 3 in Figure 2.2 for example.                                                                                                                                                                                                                                         |

| Differential voltage detection threshold $(\Delta V_{\text{DIFF}_TH})$ | T_0x31<br>D[7:0]                                | R_0x28<br>D[7:0]                             | This is the threshold to detect the voltage variation of modulated signal. The condition for increasing voltage is $\Delta V_{\text{DIFF}} > + \Delta V_{\text{DIFF}_TH}$ ("U" in Figure 2.2). The condition for decreasing voltage is $\Delta V_{\text{DIFF}} < - \Delta V_{\text{DIFF}_TH}$ ("U" in Figure 2.2). When these conditions are satisfied, change of the modulated signal is detected (transition point). The threshold voltage should be from 25% to 50% of modulation depth. (for example, 50% in Figure 2.2) |

| Demodulation count                                                     |                                                 |                                              | counted up when the modulated signal data is acquired. The data 0/1 detection (decode) is executed in relationship to point and the count threshold.                                                                                                                                                                                                                                                                                                                                                                         |

| Count threshold for data 0/1 decode                                    | T_0x33<br>D[7:0]                                | R_0x29<br>D[7:0]                             | Data "1" is decoded when count value is less than this threshold at transition point. Data "0" is decoded when the transition point is not detected before count value is counted up to this threshold. The count threshold should be set near 0.75T normally. (For example, counter threshold is 11 in Figure 2.2.)                                                                                                                                                                                                         |

| Count threshold for no data                                            | T_0x34<br>D[7:0]                                | R_0x2A<br>D[7:0]                             | No data is detected when count value is more than this threshold at transition point. When that is detected in the middle of the demodulation, it becomes packet reception error. The count threshold should be set near 1.25T normally.                                                                                                                                                                                                                                                                                     |

## 3. Automatic transmission power control function and WPT communication procedure

## 3.1 Overview of automatic transmission power control function