# AN-1144

**I2C IO Controllers 8-bit BUS**

*Author: Yu-Han Sun Date: September 19, 2016*

# Introduction

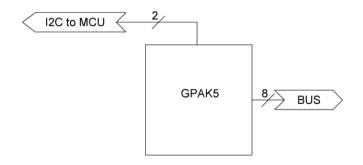

This app note is a corollary to another app note **AN-1090 Simple I2C IO Controllers with SLG46531V**. AN-1090 explains how to make I2C IO Controllers with separate input and output pins. However, this app note will explain how to setup an 8-bit bus controller which combines input pins with output pins. Refer to Figure 1 for the System Level View.

# **Digital Input/Output and OE**

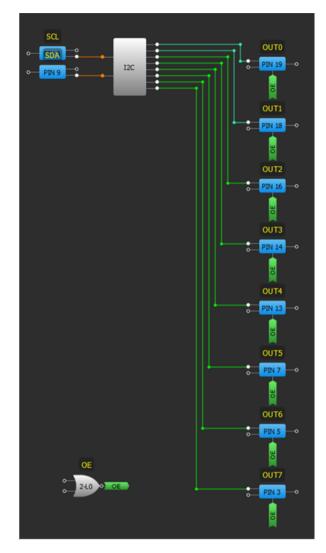

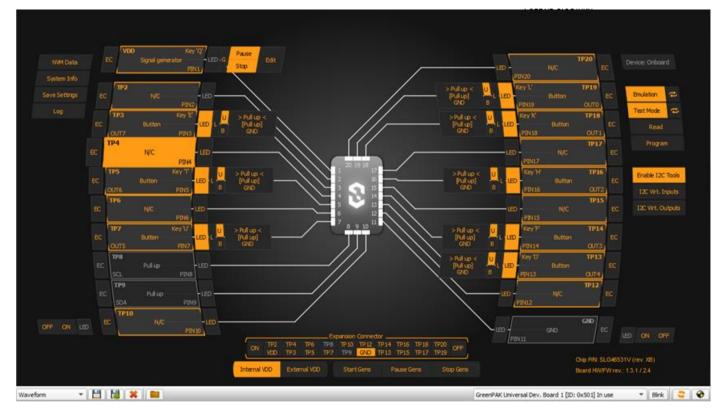

To combine inputs with outputs, each pin interfacing the bus is set to 'Digital Input/Output'. Only 9 GPIOs in the SLG46531V are 'Digital Input/Output' capable and we will be using 8 of those pins: PINs #19, 18, 16, 14, 13, 7, 5, 3. Each of these pins have an OE signal that toggles the mode. Set the properties as shown in Figure 3 and setup the matrix connections as shown in Figure 2.

Each output signal is controlled by an I2C Virtual Input. OE is controlled by 2-bit LUT0. The inputs to the 2-bit LUT0 are both gnd. Therefore, if the LUT is configured as in Figure 4a, then OE will be logic 1. If the LUT is configured as in Figure 4b, then OE will be logic 0. We will be using I2C to change the LUT configuration on the fly.

Figure 2. GreenPAK Design

Figure 1. System Level View

# **I2C IO Controllers 8-bit BUS**

| Properties             |                 |                         |                      | ×        |  |  |  |  |

|------------------------|-----------------|-------------------------|----------------------|----------|--|--|--|--|

|                        | P               | PIN                     | 19                   |          |  |  |  |  |

| I/O select             | ion:            | Digital input/output 💌  |                      |          |  |  |  |  |

| Input mod<br>OE = 0    | de:             | Digital in without Sd 💌 |                      |          |  |  |  |  |

| Output mode:<br>OE = 1 |                 |                         | 1x open drain NMO! 💌 |          |  |  |  |  |

| Resistor:              |                 | FI                      | oating               | Ŧ        |  |  |  |  |

| Resistor v             | value:          | F                       | oating               | -        |  |  |  |  |

|                        | Info            | rn                      | nation               |          |  |  |  |  |

| Electrical Spe         | ecificatio      | ns                      |                      |          |  |  |  |  |

|                        | 1.8 V<br>min/ma |                         | 5.0 V<br>min/max     |          |  |  |  |  |

| V_IH (V)               | 1.060/          | -                       | 1.810/-              | 2.680/-  |  |  |  |  |

| V_IL (V)               | -/0.760         | )                       | -/1.310              | -/1.960  |  |  |  |  |

| V_OL (V)               | -/0.009         | )                       | -/0.150              | -/0.160  |  |  |  |  |

| I_OL (mA)              | 1.380/          | -                       | 7.310/-              | 10.820/- |  |  |  |  |

| -                      | -/-             |                         | -/-                  | -/-      |  |  |  |  |

| -                      | -/-             |                         | -/-                  | -/-      |  |  |  |  |

| 0 1                    |                 | 6                       | Ap                   | ply      |  |  |  |  |

### **Figure 3. PIN Configuration**

| IN1 | IN0 | OUT |

|-----|-----|-----|

| 0   | 0   | 1   |

| 0   | 1   | 0   |

| 1   | 0   | 0   |

| 1   | 1   | 0   |

| IN1 | IN0 | OUT |

|-----|-----|-----|

| 0   | 0   | 0   |

| 0   | 1   | 0   |

| 1   | 0   | 0   |

| 1   | 1   | 0   |

Figure 4a. OE = 1

Figure 4b. OE =0

# **I2C Bus Write**

To write the bus, the MCU must send 2 commands: first write to the I2C Virtual Inputs, then set OE = 1 by re-configuring 2-bit LUTO:

i) **W: I2C Virtual Inputs**, write to address 0xF4. Each bit corresponds to an I2C Virtual Input. The order from left to right is PINs #19, 18, 16, 14, 13, 7, 5 and 3.

| 0xF4 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|------|---|---|---|---|---|---|---|---|

|      |   |   |   |   |   |   |   |   |

| 0xF4 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

ii) **W: 2-bit LUT0**, write to the second nibble of address 0x96 with the byte value 0x8. To mask the first nibble, read the byte and change only the latter four bits.

| 0x96 | Х | Х | Х | Х | 1 | 0 | 0 | 0 |

|------|---|---|---|---|---|---|---|---|

|------|---|---|---|---|---|---|---|---|

### **I2C Bus Read**

To read from the bus, the MCU must send 2 commands: first set OE = 0 by reconfiguring 2-bit LUT0, then read from the GPIO Input Levels.

i) **W: 2-bit LUT0**, write to the second nibble of address 0x96 with the byte value 0x0. To mask the first nibble, read the byte and change only the latter four bits.

| 0x96 | Х | Х | Х | Х | 0 | 0 | 0 | 0 |  |

|------|---|---|---|---|---|---|---|---|--|

|------|---|---|---|---|---|---|---|---|--|

ii) **R: Input levels**, read from address  $0 \times F0$  and  $0 \times F6$  the input levels of PIN#3, 5, 7 and PIN#13, 14, 16, 18, 19 respectively. Then parse the data based on bit location.

| 0XF0 X X | PIN3 | Х | PIN5 | Х | PIN7 | Х |

|----------|------|---|------|---|------|---|

|----------|------|---|------|---|------|---|

| 0XF6 | х | PIN13 | PIN14 | х | PIN16 | 0 | PIN18 | PIN19 |

|------|---|-------|-------|---|-------|---|-------|-------|

# Warning

The following warning can be ignored because 2bit LUT0 inputs are intentionally left static and the truth table will be re-configured through I2C.

# **Examples I2C Commands**

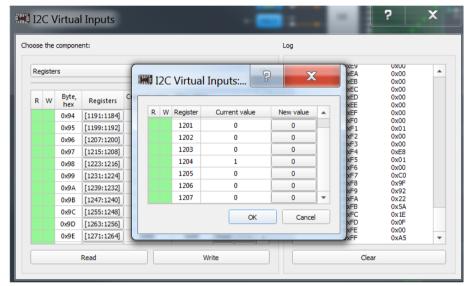

The output of each example is shown in Figure 7 through 10, which are screenshots from the I2C Tool.

| Time     | Event     | Rule                                                              | Note                                                                                                                                       |

|----------|-----------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 14:27:21 | 🕕 Fail    | 2-bit LUT0/DFF/LATCH0: The truth table is configured incorrectly. | The truth table is configured so that all combinations of the inputs that are connected to the blocks, do not cause changes on the output. |

| 14:27:21 | 🚸 Warning | 2-bit LUT0/DFF/LATCH0: No input connected.                        | 2-bit LUT0/DFF/LATCH0's input is not connected.                                                                                            |

### Figure 5. Warnings and Rules Checker

# **Emulation**

Each Digital IO pin has a pull-up active-low button. Enable I2C Tools after Emulation.

<u>Syntax</u>: [ is the start bit, ] is the stop bit, and **SA** is the slave address with a r/w bit.

Figure 6. Emulator Configuration

# **I2C IO Controllers 8-bit BUS**

i) I2C write to I2C Virtual Inputs the logic 0, 0, 0, 1, 0, 1, 1, 1.

**[ SA** 0xF4, 0xE8 **]**

ii) I2C write 2-bit LUT0 configuration to 1, 0, 0, 0:

**[ SA** 0x96 0x08 **]**

iii) I2C write 2-bit LUT0 configuration to 0, 0, 0, 0:

**[ SA** 0x96 0x00 **]**

iv) I2C Read the input levels from PINs #7, 5 and 3 and also #19, 18, 16, 14 and 13:

[ SA 0xF0 [ 0xSA read ]

| I2C Virt | tual Inputs |               | •         | [14:29:57]: Read (device: 0x00)<br>Address, hex Data, hex |

|----------|-------------|---------------|-----------|-----------------------------------------------------------|

|          | Outputs     | Current value | New value | 0xF4 0x00<br>[14:30:42]: Write (device: 0x00)             |

| 1        | OUTO        | 0             | 0         | Address, hex Data, hex<br>0xF4 0xE8                       |

| 2        | OUT1        | 0             | 0         |                                                           |

| 3        | OUT2        | 0             | 0         |                                                           |

| 4        | OUT3        | 1             | 1         |                                                           |

| 5        | OUT4        | 0             | 0         |                                                           |

| 6        | OUT5        | 1             | 1         |                                                           |

| 7        | OUT6        | 1             | 1         |                                                           |

| 8        | OUT7        | 1             | 1         |                                                           |

# Figure 7. Example i

| 120  |        | intua        | Inputs      |   |   |   |    |    |          |       |              | -   | -       |   |                   | ?                            |   |

|------|--------|--------------|-------------|---|---|---|----|----|----------|-------|--------------|-----|---------|---|-------------------|------------------------------|---|

| oose | the    | compone      | ent:        |   |   |   |    |    |          |       |              | Lo  | g       |   |                   |                              |   |

| Reg  | jister | s            |             | - |   |   | 12 | 2C | Virtua   | l Inp | uts: ?       | )   | X       | 2 | xE9<br>xEA<br>xEB | 0x00<br>0x00<br>0x00<br>0x00 | - |

| R    | w      | Byte,<br>hex | Registers   | c | Г | _ | _  | _  |          |       |              |     |         |   | xEC<br>xED<br>xEE | 0x00<br>0x00<br>0x00         |   |

|      |        | 0x94         | [1191:1184] |   |   | F | 2  | W  | Register | CL    | irrent value | Nev | v value |   | XEF               | 0x00                         |   |

|      |        | 0x95         | [1199:1192] |   |   |   |    |    | 1201     |       | 0            |     | 0       |   | xF0<br>xF1        | 0x00<br>0x01                 |   |

|      |        | 0x96         | [1207:1200] | 1 |   |   |    |    | 1202     |       | 0            |     | 0       |   | xF2               | 0x00                         |   |

|      |        | 0x97         | [1215:1208] |   |   |   |    |    | 1203     |       | 0            |     | 0       |   | xF3<br>xF4        | 0x00<br>0xE8                 |   |

|      |        | 0x98         | [1223:1216] |   |   |   |    |    | 1204     |       | 1            |     | 1       |   | xF5<br>xF6        | 0x01<br>0x00                 |   |

|      |        | 0x99         | [1231:1224] |   |   |   |    |    | 1205     |       | 0            |     | 0       |   | xF0<br>xF7        | 0x00                         |   |

|      |        | 0x9A         | [1239:1232] |   |   |   |    |    | 1206     |       | 0            |     | 0       |   | xF8<br>xF9        | 0x9F<br>0x92                 |   |

|      |        | 0x9B         | [1247:1240] | 1 |   |   |    |    | 1207     |       | 0            |     | 0       | - | xFA               | 0x22                         |   |

|      |        | 0x9C         | [1255:1248] |   |   |   |    |    |          |       |              |     |         |   | xFB<br>xFC        | 0x5A<br>0x1E                 |   |

|      |        | 0x9D         | [1263:1256] | 1 |   |   |    |    |          |       | OK           |     | Cancel  |   | xFD               | 0x0F                         |   |

|      |        | 0x9E         | [1271:1264] |   | L | - |    | _  | -        |       |              | _   | _       |   | xFE               | 0x00<br>0xA5                 | - |

|      | _      |              | Read        |   | _ |   | _  | _  |          | Write |              |     |         |   | Clear             | •                            |   |

v) I2C write 2-bit LUT0 configuration to 0, 0, 0, 0:

# **[ SA** 0x96 0x00 **]**

vi) I2C Read the input levels from PINs #7, 5 and 3 and also #19, 18, 16, 14 and 13:

[ SA 0xF0 [ 0xSA read ]

# [ **SA** 0xF6 [ 0xSA read ]

# Conclusion

By the end of this app note, you should be able to make a GreenPAK Design and the I2C Commands. Unlike AN-1090, this design uses less GPIOs at the expense of more I2C commands.

# Figure 9. Example iii

| er                         |          | ID     | Block           | Pin | Level |

|----------------------------|----------|--------|-----------------|-----|-------|

|                            |          | 2      | PIN 3           | OUT | 1     |

| PIN 16                     | <b>^</b> | 4      | PIN 5           | OUT | 1     |

| PIN 17                     |          | 6      | PIN 7           | OUT | 1     |

| Crystal OSC                |          | 49     | PIN 13          | OUT | 1     |

| V PIN 18                   |          | 50     | PIN 14          | OUT | 1     |

| <ul> <li>PIN 19</li> </ul> |          | 52     | PIN 16          | OUT | 1     |

| PIN 20                     |          | 54     | PIN 18          | OUT | 1     |

| A CMP0                     |          | 55     | PIN 19          | OUT | 1     |

| A CMP1                     |          |        |                 |     |       |

| A CMP2                     |          |        |                 |     |       |

| A CMP3                     |          |        |                 |     |       |

| P DLY                      |          |        |                 |     |       |

| POR                        |          |        |                 |     |       |

| VDD (PIN 1)                | -        | Last U | pdate: 14:56:47 |     |       |

Figure 10. Example iv

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.