# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                        |                | Document<br>No.         | TN-RX*-A0244A/E                                                      | Rev. | 1.00 |

|-----------------------|------------------------------------------------------------------------------------------------|----------------|-------------------------|----------------------------------------------------------------------|------|------|

| Title                 | Errata to the Section on Electrical Characteristics in the RX66N Group User's Manual: Hardware |                | Information<br>Category | Technical Notification                                               |      |      |

| Applicable<br>Product | RX66N Group                                                                                    | Lot No.<br>All | Reference<br>Document   | RX66N Group User's Manual:<br>Hardware Rev.1.00<br>(R01UH0825EJ0100) |      |      |

This document describes corrections to the section on Electrical Characteristics in the RX66N Group User's Manual: Hardware, Rev.1.00.

## • Page 2971 of 3050

The frequency of ICLK described in Conditions 2 of Table 61.26, Bus Timing is corrected as follows.

## Before correction

#### Table 61.26 **Bus Timing** Conditions 1: VCC = AVCC0 = AVCC1 = VCC\_USB = V<sub>BATT</sub> = 2.7 to 3.6 V, 2.7 V ≤ VREFH0 ≤ AVCC0, VSS = AVSS0 = AVSS1 = VREFL0 = VSS USB = 0 V, ICLK = PCLKA = 8 to 120 MHz, PCLKB = BCLK = SDCLK = 8 to 60 MHz, T<sub>a</sub> = T<sub>opr</sub>, Output load conditions: $V_{OH} = VCC \times 0.5$ , $V_{OL} = VCC \times 0.5$ , C = 30 pF, High-drive output is selected by the driving ability control register. Conditions 2: VCC = AVCC0 = AVCC1 = VCC USB = V<sub>BATT</sub> = 3.0 to 3.6 V, 3.0 V ≤ VREFH0 ≤ AVCC0, VSS = AVSS0 = AVSS1 = VREFL0 = VSS USB = 0 V, ICLK = PCLKA = 8 to 120 MHz, PCLKB = 8 to 60 MHz, 60 MHz < BCLK = SDCLK $\leq$ 80 MHz, T<sub>a</sub> = T<sub>opr</sub>, Output load conditions: $V_{OH} = VCC \times 0.5$ , $V_{OL} = VCC \times 0.5$ , C = 15 pF for the SDCLK pin, C = 30 pF for other pins. To control the drive capacity when using the SDRAM: set the PFBCR3.SDCLKDRV bit in external bus control register 1 to 1 to select the drive capacity of the SDCLK pin, and set the SDRAM pins other than the SDCLK pin as highspeed-interface driving outputs. After correction Table 61.26 **Bus Timing** Conditions 1: VCC = AVCC0 = AVCC1 = VCC\_USB = V<sub>BATT</sub> = 2.7 to 3.6 V, 2.7 V ≤ VREFH0 ≤ AVCC0, VSS = AVSS0 = AVSS1 = VREFL0 = VSS USB = 0 V, ICLK = PCLKA = 8 to 120 MHz, PCLKB = BCLK = SDCLK = 8 to 60 MHz, T<sub>a</sub> = T<sub>opr</sub>, Output load conditions: $V_{OH} = 0.5 \times VCC$ , $V_{OL} = 0.5 \times VCC$ , C = 30 pF, High-drive output is selected by the drive capacity control register. Conditions 2: VCC = AVCC0 = AVCC1 = VCC\_USB = V<sub>BATT</sub> = 3.0 to 3.6 V, 3.0 V ≤ VREFH0 ≤ AVCC0, VSS = AVSS0 = AVSS1 = VREFL0 = VSS USB = 0 V, ICLK = 60 to 120 MHz, PCLKA = 8 to 120 MHz, PCLKB = 8 to 60 MHz, 60 MHz < BCLK = SDCLK ≤ 80 MHz, $T_a = T_{opr}$ , Output load conditions: $V_{OH} = 0.5 \times VCC$ , $V_{OL} = 0.5 \times VCC$ , C = 15 pF for the SDCLK pin, C = 30 pF for other pins. To control the drive capacity when using the SDRAM: set the PFBCR3.SDCLKDRV bit in external bus control register 1 to 1 to select the drive capacity of the SDCLK pin, and set the SDRAM pins other than the SDCLK pin as highspeed-interface driving outputs.

#### • Page 2988 of 3050

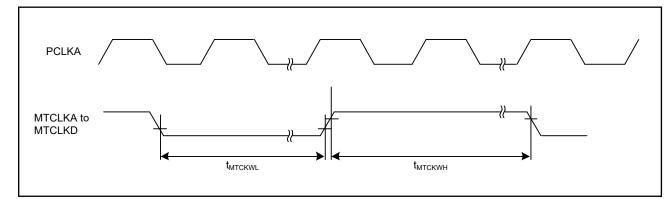

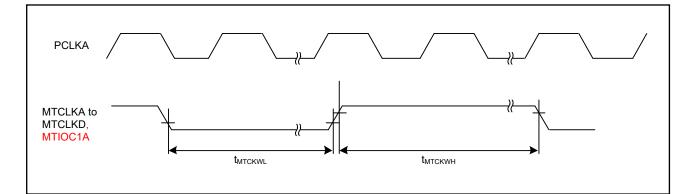

The MTIOC1A pin is added to Figure 61.41, MTU Clock Input Timing as follows.

### Before correction

## Figure 61.41 MTU Clock Input Timing

After correction

Figure 61.41 MTU Clock Input Timing

## • Page 2992 of 3050

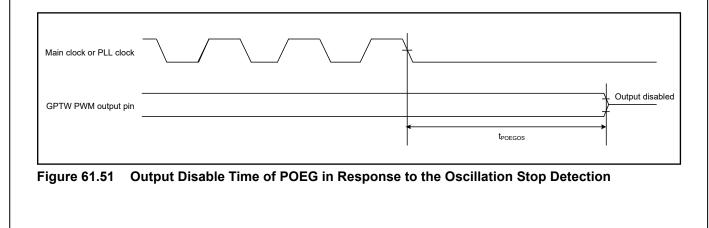

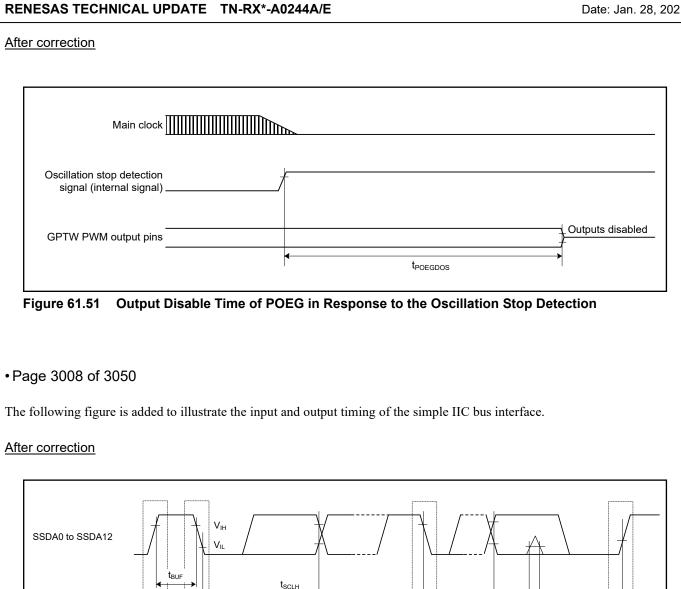

Figure 61.51, Output Disable Time of POEG in Response to the Oscillation Stop Detection is corrected as follows.

Before correction

t<sub>STAS</sub>

tspas

$V_{IH} = 0.7 \times VCC, V_{IL} = 0.3 \times VCC$

Test conditions

$V_{OL} = 0.6 \text{ V}, I_{OL} = 6 \text{ mA}$

Sı

t<sub>STAH</sub>

t<sub>SCLL</sub>

Note 1. S, P, and Sr indicate the following conditions. S: Start condition

t<sub>SCL</sub>

ts

I← t<sub>SDAH</sub>

S\*1

t<sub>Sf</sub>

P: Stop condition

Sr: Restart condition

SSCL0 to SSCL12

|←  $t_{\text{STOS}}$