発行日: 2016年6月29日

# **RENESAS TECHNICAL UPDATE**

〒135-0061 東京都江東区豊洲 3-2-24 豊洲フォレシア ルネサス エレクトロニクス株式会社

問合せ窓口 http://japan.renesas.com/contact/

E-mail: csc@renesas.com

| 製   | 品分類                                          | MPU & MCU | 発行番号   | TN-RL*-A062A/J                                                      |      | Rev. | 第1版 |

|-----|----------------------------------------------|-----------|--------|---------------------------------------------------------------------|------|------|-----|

| 題名  | 誤記訂正通知<br>RL78/G1G ユーザーズマニュアル Rev.1.20 の記載変更 |           |        | 情報分類                                                                | 技術情報 |      |     |

| 適   |                                              |           | 対象ロット等 |                                                                     |      |      |     |

| 用製品 | RL78/G1G グループ<br>: R5F11Exxx                 | 全ロット      | 関連資料   | RL78/G1G ユーザーズマニュス<br>ハードウェア編 Rev.1.20<br>R01UH0499JJ0120 (Jul.22.1 |      | 1.20 |     |

RL78/G1G ユーザーズマニュアル ハードウェア編 Rev.1.20 (R01UH0499JJ0120)において、下記訂正がございます。

#### 今回通知する訂正内容

| 訂正箇所                                                                                                      | 該当ページ | 内容   |

|-----------------------------------------------------------------------------------------------------------|-------|------|

| 4.2.1 ポート0 図4-1 P00のブロック図                                                                                 | p.71  | 注意追加 |

| 4.2.1 ポート0 図4-2 P01のブロック図                                                                                 | p.72  | 注意追加 |

| 4.2.2 ポート1 図4-3 P10のブロック図                                                                                 | p.75  | 注意追加 |

| 4.2.2 ポート1 図4-7 P14のブロック図                                                                                 | p.79  | 誤記訂正 |

| 4.2.2 ポート1 図4-8 P15のブロック図                                                                                 | p.80  | 注意追加 |

| 4.2.2 ポート1 図4-9 P16のブロック図                                                                                 | p.81  | 注意追加 |

| 4.2.2 ポート1 図4-10 P17のブロック図                                                                                | p.82  | 注意追加 |

| 4.2.4 ポート3 図4-12 P30のブロック図                                                                                | p.86  | 注意追加 |

| 4.2.4 ポート3 図4-13 P31のブロック図                                                                                | p.87  | 誤記訂正 |

| 4.2.6 ポート5 図4-16 P50のブロック図                                                                                | p.92  | 注意追加 |

| 4.2.6 ポート5 図4-17 P51のブロック図                                                                                | p.93  | 注意追加 |

| 8.3.9 タイマRD出力制御レジスタ(TRDOCR)<br>図8-12 タイマRD出力制御レジスタ(TRDOCR)のフォーマット<br>[リセット同期PWMモード,相補PWMモード]              | _     | 仕様追加 |

| 8.3.11 タイマRD出力制御レジスタ(TRDOCR)<br>図8-18タイマRD制御レジスタ0 (TRDOCR0)のフォーマット<br>[相補PWMモード]                          | p.313 | 誤記訂正 |

| 8.3.18 タイマRDカウンタi (TRDi)(i = 0, 1)<br>図8-31タイマRDカウンタi (TRDi)(i = 0, 1)のフォーマット<br>[リセット同期PWMモード, PWM3 モード] | p.328 | 誤記訂正 |

| 8.3.18 タイマRDカウンタi (TRDi)(i = 0, 1)<br>図 8-32 タイマRDカウンタi (TRDi)(i = 0, 1)のフォーマット<br>[相補PWMモード(TRD0)]       | p.328 | 誤記訂正 |

| 8.3.18 タイマRDカウンタi (TRDi)(i = 0, 1)<br>図 8-33 タイマRDカウンタi (TRDi)(i = 0, 1)のフォーマット<br>[相補PWMモード(TRD1)]       | p.329 | 誤記訂正 |

| 8.4.8 アウトプットコンペア機能<br>図8-50 アウトプットコンペア機能のブロック図                                                            | p.355 | 誤記訂正 |

| 8.4.9 PWM機能<br>図8-54 PWM機能のブロック図                                                                          | p.361 | 誤記訂正 |

| 8.4.10 リセット同期PWMモード<br>図8-57 リセット同期PWMモードのブロック図                                                           | p.366 | 誤記訂正 |

| 8.4.11 相補PWMモード<br>図8-59 相補PWMモードのブロック図                                                                   | p.370 | 誤記訂正 |

| 8.4.12 PWM3モード<br>図8-62 PWM3モードのブロック図                                                                     | p.375 | 誤記訂正 |

#### ドキュメント改善計画

本訂正内容については、次回ユーザーズマニュアル改版時に修正を行います。

#### ユーザーズマニュアルの訂正一覧

|    | 訂正内容と該当箇所                                                                                                   |                                              |              |                 | 本通知での |  |

|----|-------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------|-----------------|-------|--|

| No |                                                                                                             | ドキュメント<br>No.                                | 和文           | R01UH0499JJ0120 | 該当ページ |  |

| 1  | 4.2.1 ポート0 図4-                                                                                              | 1 P00のブロック図                                  |              | p.71            | p.3   |  |

| 2  | 4.2.1 ポート0 図4-                                                                                              | 2 P01のブロック図                                  |              | p.72            | p.4   |  |

| 3  | 4.2.2 ポート1 図4-3 P10のブロック図                                                                                   |                                              |              | p.75            | p.5   |  |

| 4  | 4.2.2 ポート1 図4-                                                                                              | 7 P14のブロック図                                  |              | p.79            | p.6   |  |

| 5  | 4.2.2 ポート1 図4-                                                                                              | -8 P15のブロック図                                 |              | p.80            | p.7   |  |

| 6  | 4.2.2 ポート1 図4-                                                                                              | ·9 P16のブロック図                                 |              | p.81            | p.8   |  |

| 7  | 4.2.2 ポート1 図4-10 P17のブロック図                                                                                  |                                              |              | p.82            | p.9   |  |

| 8  | 4.2.4 ポート3 図4-12 P30のブロック図                                                                                  |                                              |              | p.86            | p.10  |  |

| 9  | 4.2.4 ポート3 図4-13 P31のブロック図                                                                                  |                                              |              | p.87            | p.11  |  |

| 10 | 4.2.6 ポート5 図4-16 P50のブロック図                                                                                  |                                              |              | p.92            | p.12  |  |

| 11 | 4.2.6 ポート5 図4-                                                                                              | -17 P51のブロック図                                |              | p.93            | p.13  |  |

| 12 | 図8-12 タイマRD出                                                                                                | 力制御レジスタ(TRD0<br>ḋ力制御レジスタ(TRI<br>Iモード,相補PWMモ- | DOCR)のフォーマット | _               | p.14  |  |

| 13 | 図8-18タイマRD制<br>[相補PWMモード ]                                                                                  |                                              | CR0)のフォーマット  | p.313           | p.15  |  |

| 14 | 8.3.18 タイマRDカウンタi (TRDi) (i = 0, 1)<br>図8-31 タイマRDカウンタi (TRDi) (i = 0, 1)のフォーマット<br>[リセット同期PWMモード, PWM3モード] |                                              |              | p.328           | p.15  |  |

| 15 | 図8-32 タイマRDカ<br>[相補PWMモード(T                                                                                 |                                              | ), 1)のフォーマット | p.328           | p.16  |  |

| 16 | 図 8-33 タイマRD<br>[相補PWMモード(T                                                                                 |                                              |              | p.329           | p.16  |  |

| 17 |                                                                                                             | コンペア機能<br>トコンペア機能のブ                          | ロック図         | p.355           | p.17  |  |

| 18 | 8.4.9 PWM機能<br>図8-54 PWM機能の                                                                                 |                                              |              | p.361           | p.18  |  |

| 19 |                                                                                                             | 期PWMモードのブロ                                   | リック図         | p.366           | p.19  |  |

| 20 | 8.4.11 相補PWMモ<br>図8-59 相補PWMモ                                                                               | ードのブロック図                                     |              | p.370           | p.20  |  |

| 21 | 8.4.12 PWM3モー I<br>図8-62 PWM3モー                                                                             |                                              | ,            | p.375           | p.21  |  |

誤記訂正の該当箇所は、**誤)太字下線、**正)グレー・ハッチングで記載します。

記載変更・追加の該当箇所は、旧)太字下線、新)グレー・ハッチングで記載します。

#### 発行文書履歴

RL78/G1G ユーザーズマニュアル Rev.1.20 誤記訂正通知 発行文書履歴

| 文書番号           | 発行日        | 記事                                       |

|----------------|------------|------------------------------------------|

| TN-RL*-A062A/J | 2016年6月29日 | 初版発行<br>訂正一覧の No.1 ~ No.21 の誤記訂正(本通知です。) |

発行日: 2016年6月29日

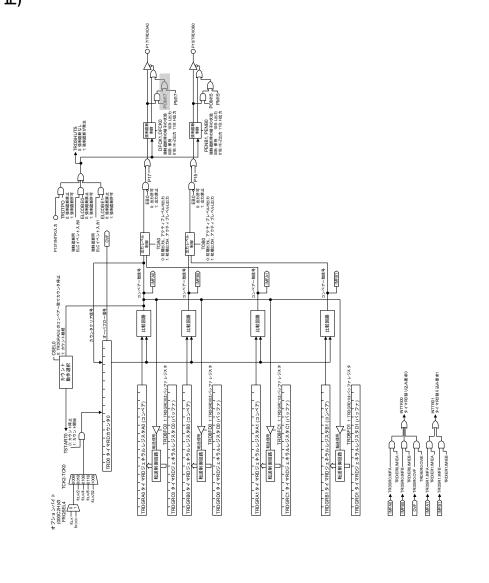

#### 1. <u>4.2.1 ポート 0 図 4-1 P00 のブロック図 (p.71)</u>

旧)

図 4 - 1 P00 のブロック図

新)

図 4 - 1 P00 のブロック図

注意. ポート出力モード・レジスタ(POMx)で N-ch オープン・ドレイン出力モード設定時は、 出力モード時においても、入力バッファがオンになっているため、中間電位となった 場合、貫通電流が流れることがあります。

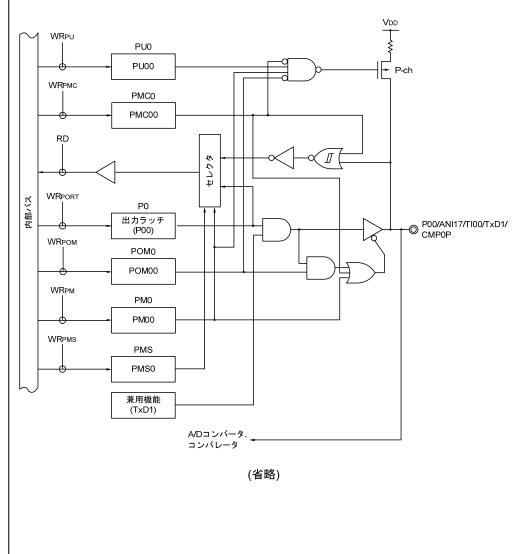

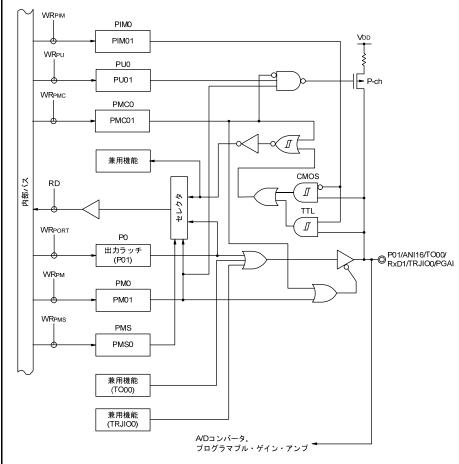

#### 2. <u>4.2.1 ポート 0 図 4-2 P01 のブロック図 (p.72)</u>

旧)

図 4 - 2 P01 のブロック図

#### 新)

図 4 - 2 P01 のブロック図

注意. ポート入力モード・レジスタ(PIMx)で TTL 入力バッファに設定し、ハイレベルを入力 している場合、TTL 入力バッファの構造により入力バッファで電力を消費することが あります。電力増加を防ぎたい場合は、ローレベルを入力してください。

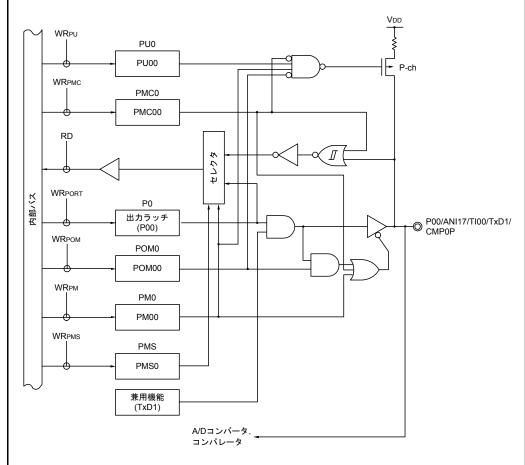

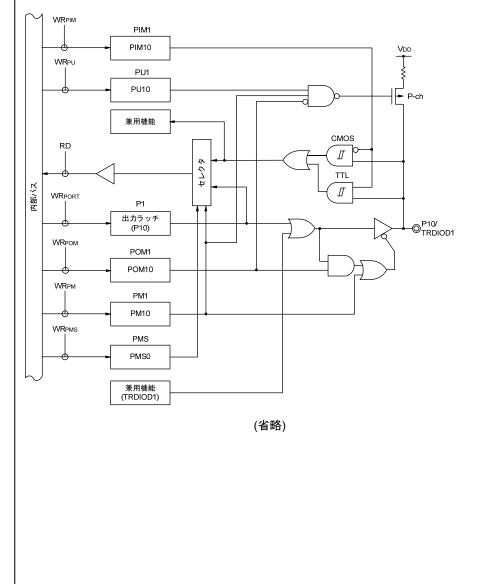

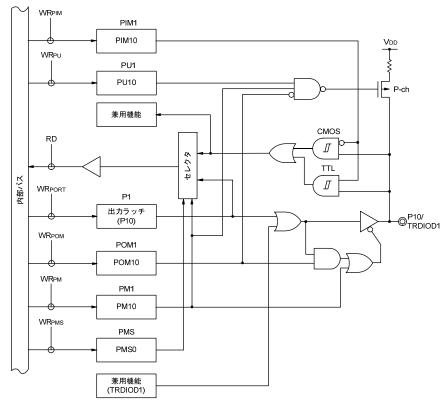

#### 3. 4.2.2 ポート1 図 4-3 P10 のブロック図 (p.75)

旧)

図 4 - 3 P10 のブロック図

#### 新)

図 4 - 3 P10 のブロック図

注意 1.ポート出力モード・レジスタ(POMx)で N-ch オープン・ドレイン出力モード設定時は、 出力モード時においても、入力バッファがオンになっているため、中間電位となった 場合、貫通電流が流れることがあります。

2.ポート入力モード・レジスタ(PIMx)で TTL 入力バッファに設定し、ハイレベルを入力している場合、TTL 入力バッファの構造により入力バッファで電力を消費することがあります。電力増加を防ぎたい場合は、ローレベルを入力してください。

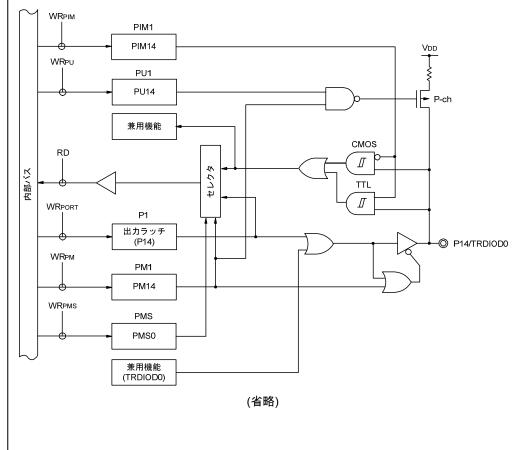

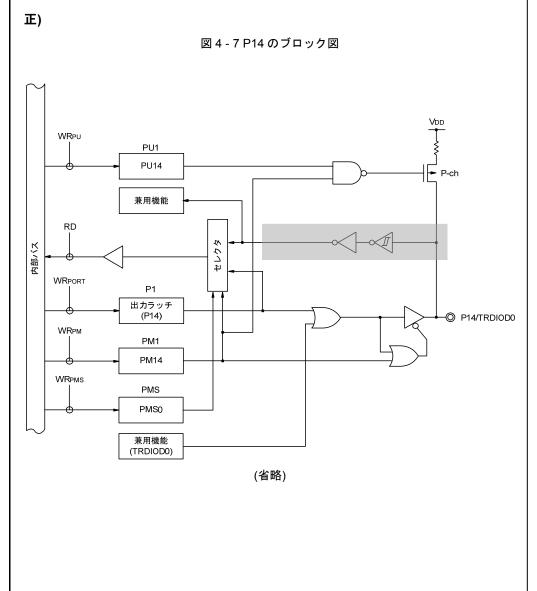

#### 4. <u>4.2.2 ポート1 図 4-7 P14 のブロック図 (p.79)</u>

誤)

図 4 - 7 P14 のブロック図

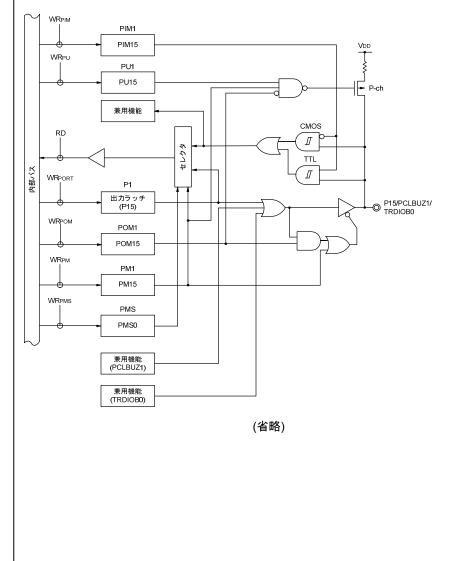

#### 5. 4.2.2 ポート1 図 4-8 P15 のブロック図 (p.80)

旧)

図 4 - 8 P15 のブロック図

新)

図 4 - 8 P15 のブロック図

注意 1.ポート出力モード・レジスタ(POMx)で N-ch オープン・ドレイン出力モード設定時は、 出力モード時においても、入力バッファがオンになっているため、中間電位となった 場合、貫通電流が流れることがあります。

2.ポート入力モード・レジスタ(PIMx)で TTL 入力バッファに設定し、ハイレベルを入力 している場合、TTL 入力バッファの構造により入力バッファで電力を消費することが あります。電力増加を防ぎたい場合は、ローレベルを入力してください。

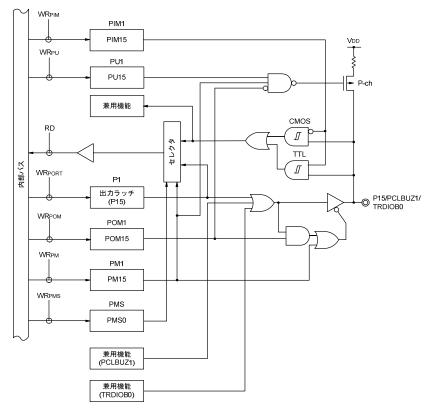

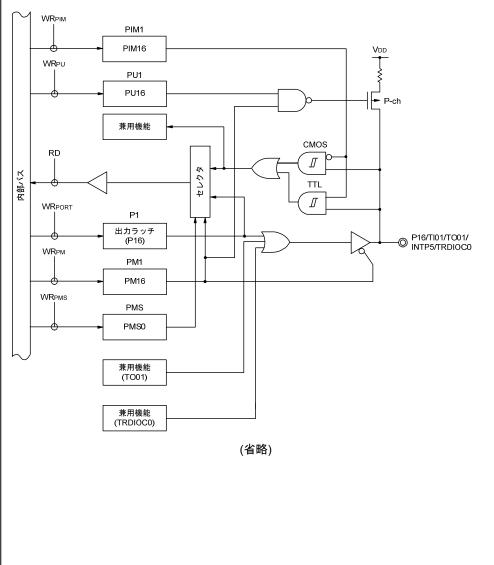

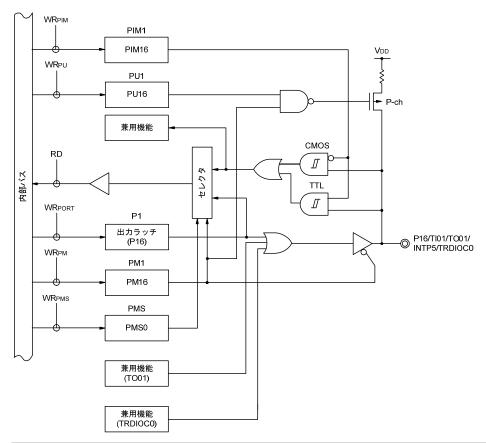

#### 6. <u>4.2.2 ポート1 図 4-9 P16 のブロック図 (p.81)</u>

旧)

図 4 - 9 P16 のブロック図

#### 新)

図 4 - 9 P16 のブロック図

注意. ポート入力モード・レジスタ(PIMx)で TTL 入力バッファに設定し、ハイレベルを入力 している場合、TTL 入力バッファの構造により入力バッファで電力を消費することが あります。電力増加を防ぎたい場合は、ローレベルを入力してください。 (省略)

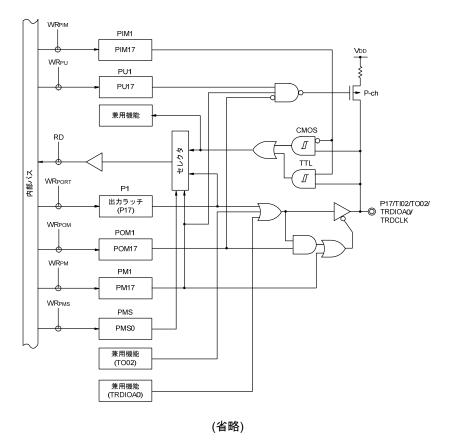

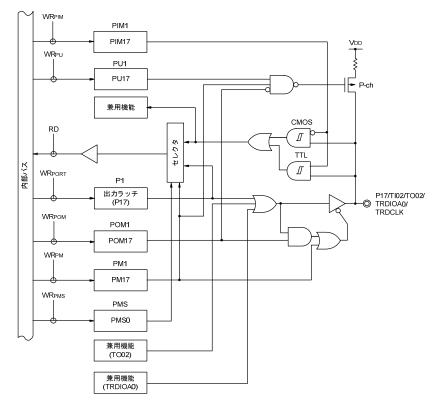

#### 7. 4.2.2 ポート1 図 4-10 P17 のブロック図 (p.82)

旧)

図 4 - 10 P17 のブロック図

新)

図 4 - 10 P17 のブロック図

- 注意 1.ポート出力モード・レジスタ(POMx)で N-ch オープン・ドレイン出力モード設定時は、 出力モード時においても、入力バッファがオンになっているため、中間電位となった 場合、貫通電流が流れることがあります。

- 2.ポート入力モード・レジスタ(PIMx)で TTL 入力バッファに設定し、ハイレベルを入力している場合、TTL 入力バッファの構造により入力バッファで電力を消費することがあります。電力増加を防ぎたい場合は、ローレベルを入力してください。

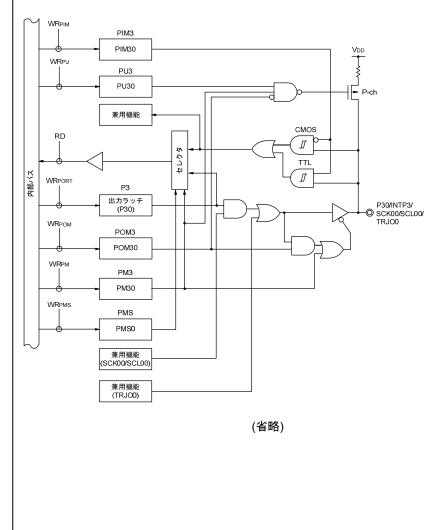

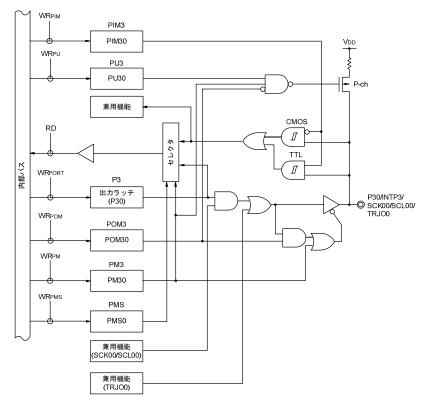

#### 8. 4.2.4 ポート 3 図 4-12 P30 のブロック図 (p.86)

旧)

図 4 - 12 P30 のブロック図

#### 新)

図 4 - 12 P30 のブロック図

注意 1.ポート出力モード・レジスタ (POMx)で N-ch オープン・ドレイン出力モード設定時は、 出力モード時においても、入力バッファがオンになっているため、中間電位となった 場合、貫通電流が流れることがあります。

2.ポート入力モード・レジスタ(PIMx)で TTL 入力バッファに設定し、ハイレベルを入力 している場合、TTL 入力バッファの構造により入力バッファで電力を消費することが あります。電力増加を防ぎたい場合は、ローレベルを入力してください。

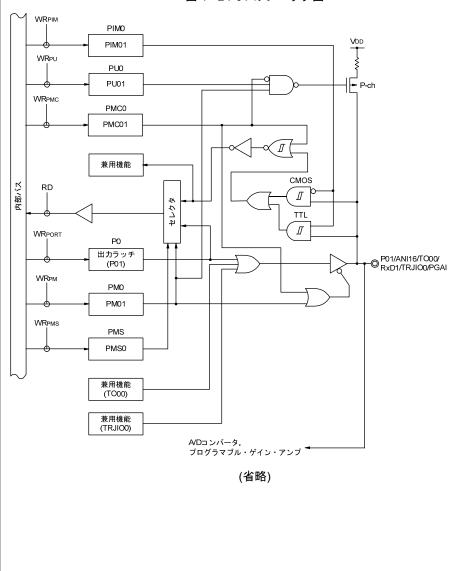

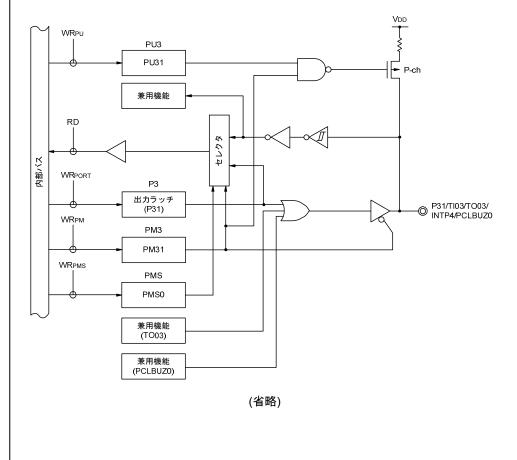

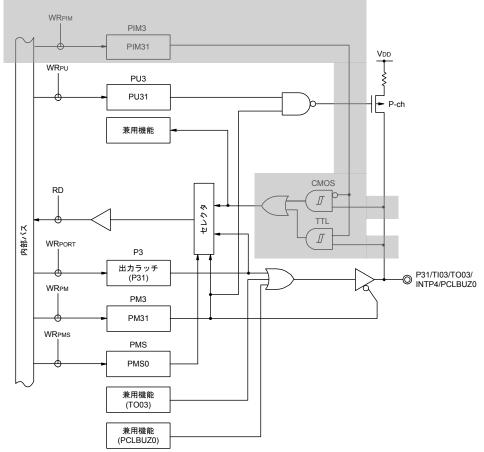

#### 9. 4.2.4 ポート 3 図 4-13 P31 のブロック図 (p.87)

誤)

図 4 - 13 P31 のブロック図

正)

図 4 - 13 P31 のブロック図

注意. ポート入力モード・レジスタ(PIMx)で TTL 入力バッファに設定し、ハイレベルを入力 している場合、TTL 入力バッファの構造により入力バッファで電力を消費することが あります。電力増加を防ぎたい場合は、ローレベルを入力してください。

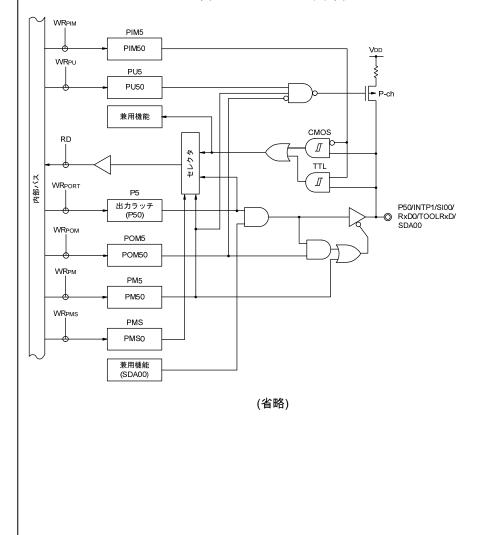

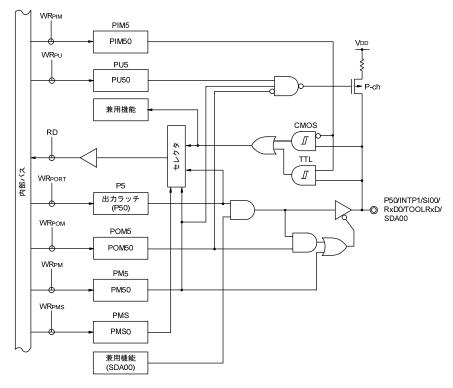

#### 10. <u>4.2.6 ポート 5 図 4-16 P50 のブロック図 (p.92)</u>

旧)

図 4 - 16 P50 のブロック図

新)

図 4 - 16 P50 のブロック図

注意 1.ポート出力モード・レジスタ(POMx)で N-ch オープン・ドレイン出力モード設定時は、 出力モード時においても、入力バッファがオンになっているため、中間電位となった 場合、貫通電流が流れることがあります。

2.ポート入力モード・レジスタ(PIMx)で TTL 入力バッファに設定し、ハイレベルを入力 している場合、TTL 入力バッファの構造により入力バッファで電力を消費することが あります。電力増加を防ぎたい場合は、ローレベルを入力してください。

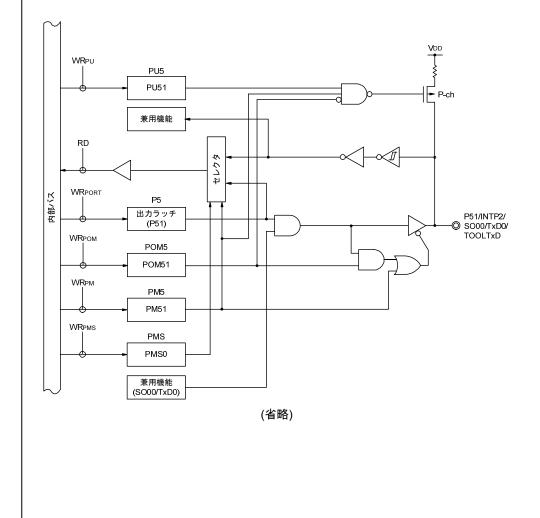

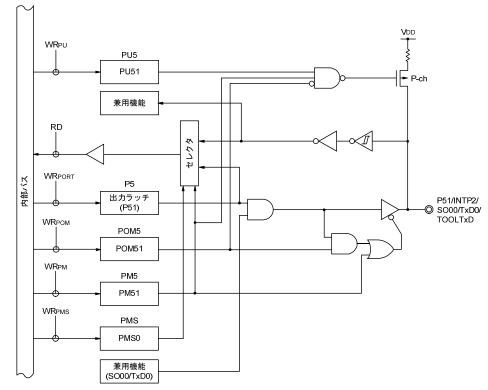

#### 11. <u>4.2.6 ポート 5 図 4-17 P51 のブロック図 (p.93)</u>

旧)

図 4 - 17 P51 のブロック図

新)

図 4 - 17 P51 のブロック図

注意. ポート出力モード・レジスタ(POMx)で N-ch オープン・ドレイン出力モード設定時は,

出力モード時においても、入力バッファがオンになっているため、中間電位となった

場合、貫通電流が流れることがあります。

12. <u>8.3.9 タイマ RD 出力制御レジスタ(TRDOCR)</u>

図 8-12 タイマ RD 出力制御レジスタ(TRDOCR) のフォーマット

[リセット同期 PWM モード, 相補 PWM モード]

旧)

なし

新)

図 8-12 タイマ RD 出力制御レジスタ (TRDOCR)のフォーマット

[リセット同期 PWM モード, 相補 PWM モード]

アドレス: F0269H リセット時: 00H 注1 R/W

略号

7

6

5

4

3

2

1

0

TRDOCR

TOD1

TOC1

TOB1

TOA1

TOD0

TOC0

TOB0

TOA0

TOD1,TOC1, TOB1,TOA1, TOD0,TOB0, TOA0 リセット同期 PWM モード時, 相補 PWM モードでは、設定は無効です。必ず、0 を設定してください。 リセット同期 PWM モード、相補 PWM モードの場合、本レジスタの設には依存せず、TRDFCR の OLS1、 OLS0 ビットの設定に従います。

| TOC0                                 | TRDIOC0 初期出カレベル選択 <sup>注2</sup> |  |  |  |

|--------------------------------------|---------------------------------|--|--|--|

| 0                                    | 初期出力 L                          |  |  |  |

| 1                                    | 初期出力H                           |  |  |  |

| リセット同期 PWM モードでは、PWM 周期ごとに出力反転します。   |                                 |  |  |  |

| 相補 PWM モードでは、PWM の 1/2 周期ごとに出力反転します。 |                                 |  |  |  |

- 注 1 ユーザ・オプション・バイト(000C2H)の FRQSEL4 = 1 かつ, PER1 レジスタの TRD0EN = 0 の場合, リセット時の値は不定となります。初期値を読み出す必要 がある場合は, fCLK を flH に設定し TRD0EN = 1 にセットしたあとに読み出して ください。

- 注 2. TRDOCR レジスタの端子機能が波形出力の場合, TRDOCR レジスタを設定したとき、初期出力レベルが出力されます。

### 13. 8.3.11 タイマ RD 制御レジスタ i (TRDCRi)(i = 0, 1) 図 8-18 タイマ RD 制御レジスタ 0 (TRDCR0)のフォーマット [相補 PWM モード] (p.313)

5

CCLR0

誤)

図 8 - 18 タイマ RD 制御レジスタ 0 (TRDCR0)のフォーマット[相補 PWM モード]

アドレス: F0270H (TRDCR0)

リセット時:00H<sup>注1</sup> R/W

略号 TRDCR0 CCLR2 CCLR1

3 CKEG1 CKEG0 TCK2 TCK1 TCK0

(省略)

14. <u>8.3.18 タイマ RD カウンタ i (TRDi) (i = 0, 1)</u>

図 8 - 31 タイマ RD カウンタ i (TRDi) (i = 0, 1)のフォーマット [リセット同期 PWM モード, PWM3 モード] (p.328)

誤)

図 8 - 31 タイマ RD カウンタ i (TRDi) (i = 0, 1)のフォーマット

[リセット同期 PWM モード, PWM3 モード]

アドレス: F0276H (TRD0), F0286H (TRD1) リセット時: 0000H 注 R/W

略号 15 14 13 12 11 10 9 8 7 **TRDi** (省略)

正)

図 8-19 タイマ RD 制御レジスタ i (TRDCRi) (i=0,1)のフォーマット[相補 PWM モード]

アドレス: F0270H(TRDCR0), F0280H(TRDCR1)

リセット時:00H<sup>注1</sup> R/W 2

略号 **TRDCRi**

CCLR2 CCLR1

CCLR0 CKEG1

CKEG0

TCK2

TCK1

TCK0

(省略)

正)

図 8 - 32 タイマ RD カウンタ 0 (TRD0)のフォーマット

[リセット同期 PWM モード、PWM3 モード]

アドレス: F0276H (TRD0) リセット時: 0000H 注 R/W

TRD0

略号 15 14 13 12 11 10 9 8

15. 8.3.18 タイマ RD カウンタ i (TRDi) (i = 0, 1)

図 8 - 32 タイマ RD カウンタ i (TRDi) (i = 0, 1)のフォーマット

[相補 PWM モード(TRD0)] (p.328)

誤)

図 8 - 32 タイマ RD カウンタ i (TRDi) (i = 0, 1)のフォーマット[相補 PWM モード(TRD0)]

アドレス: F0276H (TRD0), F0286H (TRD1) リセット時: 0000H <sup>注</sup>

略号 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TRDi (省略)

16. 8.3.18 タイマ RD カウンタ i (TRDi) (i = 0, 1)

図 8 - 33 タイマ RD カウンタ i (TRDi) (i = 0, 1)のフォーマット

<u>[相補 PWM モード(TRD1)] (p.329)</u>

誤)

図 8 - 33 タイマ RD カウンタ i (TRDi) (i = 0, 1)のフォーマット[相補 PWM モード(TRD1)]

アドレス: F0276H (TRD0), F0286H (TRD1) リセット時: 0000H<sup>注</sup>

略号 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 IRDi

(省略)

正)

図 8 - 33 タイマ RD カウンタ 0 (TRD0)のフォーマット[相補 PWM モード(TRD0)]

アドレス: F0276H (TRD0) リセット時: 0000H 注 R/W

略号 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 TRD0

(省略)

正)

図 8 - 34 タイマ RD カウンタ 1 (TRD1)のフォーマット[相補 PWM モード(TRD1)]

アドレス: F0286H (TRD1) リセット時: 0000H 注 R/W

略号 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 TRD1

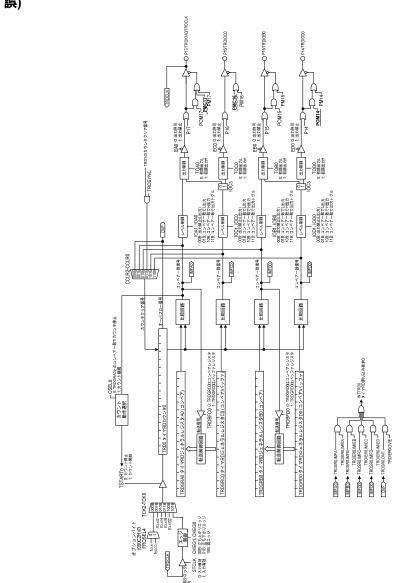

## 17. <u>8.4.8 アウトプットコンペア機能</u> 図 8-50 アウトプットコンペア機能のブロック図 (p.355)

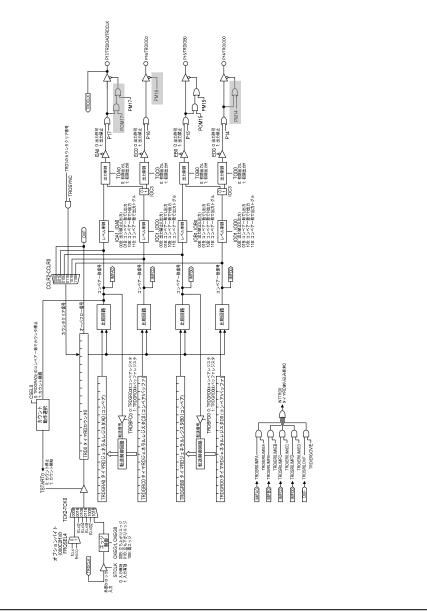

誤)

正)

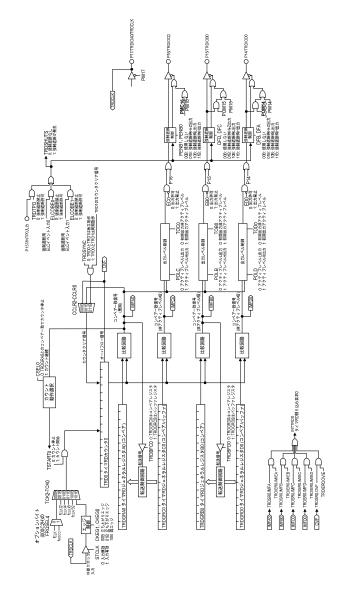

# 18. <u>8.4.9 PWM 機能</u> 図 8-54 PWM 機能のブロック図 (p.361) 誤)

正)

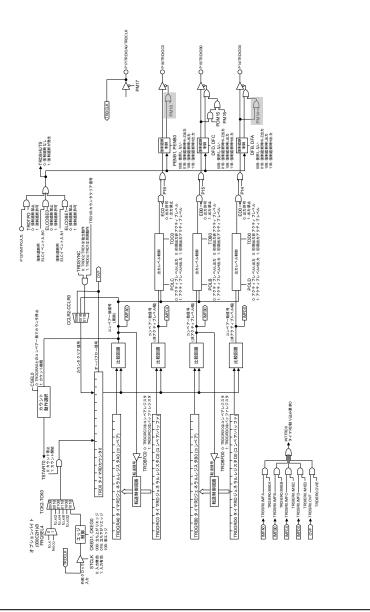

# 19. <u>8.4.10 リセット同期 PWM モード</u> 図 8-57 リセット同期 PWM モードのブロック図 (p.366) 誤) 正)

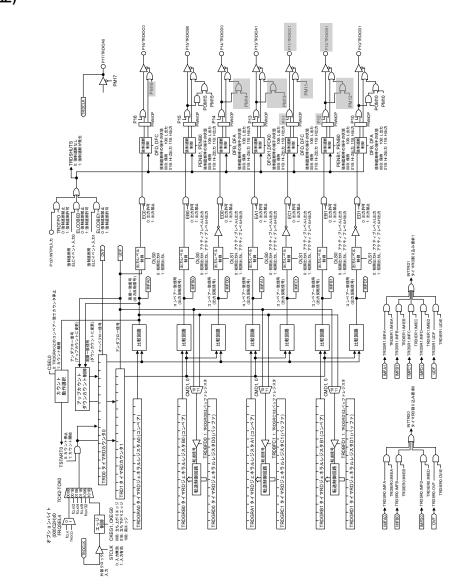

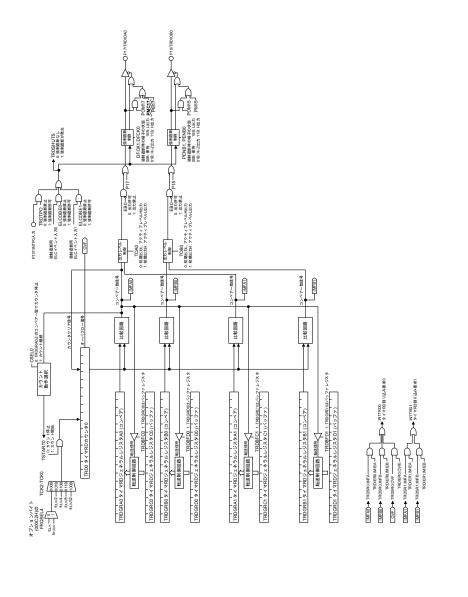

# RENESAS TECHNICAL UPDATE TN-RL\*-A062A/J 20. <u>8.4.11 相補 PWM モード</u> 図 8-59 相補 PWM モードのブロック図 (p.370) 誤)

正)

#### 21. <u>8.4.12 PWM3 モード</u> 図 8-62 PWM3 モードのブロック図 (p.375)

誤)

正)