# FemtoClock<sup>®</sup> NG Jitter Attenuator and Clock Synthesizer

### **Description**

The 8V19N492 is a fully integrated FemtoClock NG jitter attenuator and clock synthesizer designed as a high-performance clock solution for conditioning and frequency/phase management of wireless base station radio equipment boards. The device is optimized to deliver excellent phase noise performance as required in GSM, WCDMA, LTE, and LTE-A radio board implementations. The device supports JESD204B subclass 0 and 1 clocks.

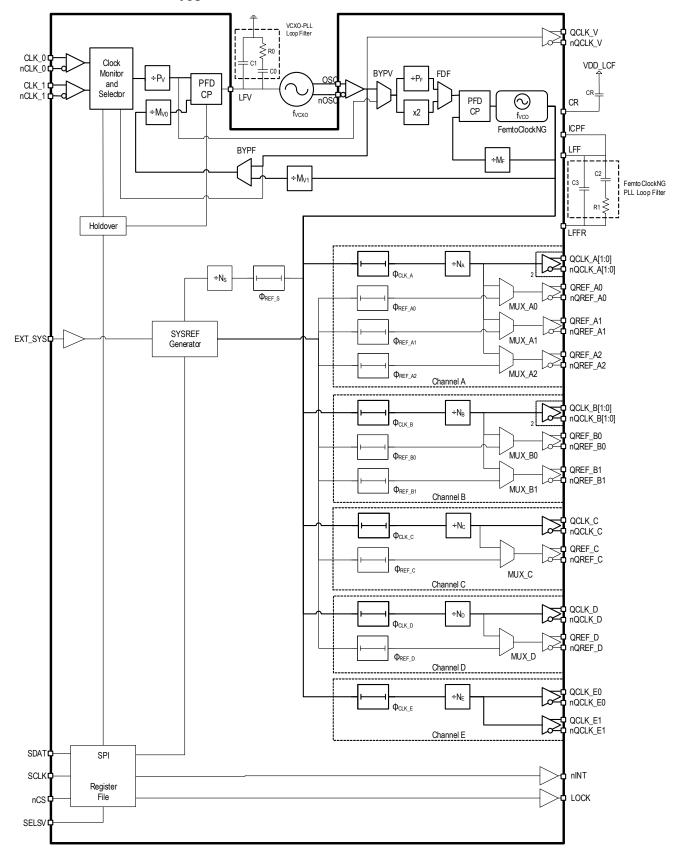

A two-stage PLL architecture supports both jitter attenuation and frequency multiplication. The first stage PLL is the jitter attenuator and uses an external VCXO for best possible phase noise characteristics. The second stage PLL locks on the VCXO-PLL output signal and synthesizes the target frequency.

The device supports the clock generation of high-frequency clocks from the selected VCO and low-frequency synchronization signals (SYSREF). SYSREF signals are internally synchronized to the clock signals. Delay functions exist for achieving alignment and controlled phase delay between system reference and clock signals and to align/delay individual output signals. The four redundant inputs are monitored for activity. Four selectable clock switching modes are provided to handle clock input failure scenarios. Auto-lock, individually programmable output frequency dividers, and phase adjustment capabilities are added for flexibility.

The device is configured through a three-wire SPI interface and reports lock and signal loss status in internal registers and via a lock detect (LOCK) output. Internal status bit changes can also be reported via the nINT output. The 8V19N492 is ideal for driving converter circuits in wireless infrastructure, radar/imaging, and instrumentation/medical applications. The device is a member of the high-performance clock family from IDT.

### **Typical Applications**

- Wireless infrastructure applications: GSM, WCDMA, LTE, and LTE-A

- Ideal clock driver for jitter-sensitive ADC and DAC circuits

- Low phase noise clock generation

- Ethernet line cards

- Radar and imaging

- Instrumentation and medical

### **Features**

- High-performance clock RF-PLL with support for JESD204B

- Optimized for low phase noise: -150dBc/Hz (800kHz offset; 245.76MHz clock)

- Integrated phase noise of 80fs RMS typical (12k-20MHz).

- Dual-PLL architecture

- 1st-PLL stage with external VCXO for clock jitter attenuation

- 2nd-PLL with internal FemtoClockNG PLL: 2949.12MHz

- Six output channels with a total of 16 outputs, organized in:

- Four JESD204B channels (device clock and SYSREF output) with two, four and five outputs

- One clock channel with two outputs

- One VCXO output

- Configurable integer clock frequency dividers

- Supported clock output frequencies include: 2949.12, 1474.56, 983.04, 491.52, 245.76, and 122.88MHz

- Low-power LVPECL/LVDS outputs support configurable signal amplitude, DC and AC coupling and LVPECL, LVDS line terminations techniques

- Phase delay circuits

- Clock phase delay with 256 steps of 339ps and a range of 0 to 86.466ns

- Individual SYSREF phase delay with 8 steps of 169ps

- Additional individual SYSREF fine phase delay with 25ps steps

- Global SYSREF signal delay with 256 steps of 339ps and a range of 0 to 86.466 ns

- Redundant input clock architecture with two inputs and

- · Input activity monitoring

- Manual and automatic, fault-triggered clock selection modes

- · Priority controlled clock selection

- · Digital holdover and hitless switching

- Differential inputs accept LVDS and LVPECL signals

- SYSREF generation modes include internal and external trigger mode for JESD204B

- Supply voltage: 3.3V

- SPI and control I/O voltage: 1.8V/3.3V (Selectable)

- Package: 10 × 10 mm 88-VFQFPN

- Temperature range: -40°C to +105°C (Case)

## **Block Diagram**

Figure 1. Block Diagram (f<sub>VCO</sub> = 2949.12MHz)

### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.