## PL 3120<sup>®</sup>/PL 3150<sup>®</sup>/PL 3170 Power Line Smart Transceiver Data Book

Echelon, LON, LonWORKS, i.LON, LonBuilder, NodeBuilder, LNS, LonTalk, Neuron, 3120, 3150, LonMaker, ShortStack, and the Echelon logo are trademarks of Echelon Corporation registered in the United States and other countries.

Other brand and product names are trademarks or registered trademarks of their respective holders.

Smart Transceivers, Neuron Chips, and other OEM Products were not designed for use in equipment or systems which involve danger to human health or safety or a risk of property damage and Echelon assumes no responsibility or liability for use of the Smart Transceivers or Neuron Chips in such applications.

Echelon Corporation has developed and patented certain methods of implementing circuitry external to the PL 3120®, PL 3150®, and PL 3170<sup>TM</sup> Power Line Smart Transceiver chips. These patents are licensed pursuant to the Echelon PL 3120 / PL 3150/PL 3170 Power Line Smart Transceiver Development Support Kit License Agreement.

Parts manufactured by vendors other than Echelon and referenced in this document have been described for illustrative purposes only, and may not have been tested by Echelon. It is the responsibility of the customer to determine the suitability of these parts for each application.

ECHELON MAKES AND YOU RECEIVE NO WARRANTIES OR CONDITIONS, EXPRESS, IMPLIED, STATUTORY OR IN ANY COMMUNICATION WITH YOU, AND ECHELON SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE.

Except as expressly permitted herein, no part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Echelon Corporation.

Printed in the United States of America. Copyright ©1996-2011 by Echelon Corporation.

Echelon Corporation www.echelon.com

## **Table of Contents**

| napter 1 -Introduction                                       |    |

|--------------------------------------------------------------|----|

| Overview                                                     |    |

| Product Overview                                             | 2  |

| LONWORKS Networks                                            | 2  |

| Three Product Families.                                      |    |

| Power Line Signaling                                         | 3  |

| Dual Carrier Frequency Operation                             | 4  |

| Forward Error Correction                                     | 5  |

| Powerful Output Amplifier                                    | 5  |

| Wide Dynamic Range                                           | 5  |

| Low Current Consumption                                      | 5  |

| Compliant with Regulations Worldwide                         | 5  |

| Integrated, Low-Cost and Small Form Factor Design            | 6  |

| Electric Utility vs. Home/Commercial/Industrial Applications | 7  |

| Extensive Development Resources                              |    |

| Audience                                                     | 7  |

| Content                                                      | 7  |

| Related Documentation                                        | 7  |

|                                                              |    |

| apter 2 -Hardware Resources                                  | 9  |

| Overview                                                     | 10 |

| Neuron Processor Architecture                                | 10 |

| Memory                                                       | 16 |

| Memory Allocation Overview                                   | 16 |

| PL 3150 Smart Transceiver Memory Allocation                  |    |

| PL 3120/PL 3170 Smart Transceiver Memory Allocation          |    |

| EEPROM                                                       |    |

| Static RAM                                                   | 19 |

| Pre-programmed ROM                                           | 19 |

| PL 3150 Smart Transceiver External Memory Interface          |    |

| Input/Output                                                 |    |

| Twelve Bidirectional I/O Pins                                |    |

| Two 16-Bit Timer/Counters                                    |    |

| Clock Input                                                  |    |

| Band-In-Use (BIU) and Packet Detect (PKD) LED Connections    |    |

| TXON Output Signal                                           |    |

| Additional Functions                                         |    |

| Reset Function                                               | 24 |

| RESET Pin                                                    |    |

| Power Up Sequence                                            |    |

| Software Controlled Reset                                    |    |

| Watchdog Timer                                               |    |

| ITCMode Pin                                                  |    |

| Reset Processes and Timing                                   | 27 |

| SERVICE Pin                                          | 32 |

|------------------------------------------------------|----|

| Integrity Mechanisms                                 |    |

| Memory Integrity Using Checksums                     | 34 |

| Reboot and Integrity Options Word                    | 35 |

| Reset Processing                                     | 36 |

| Signatures                                           | 36 |

| Chapter 3 - Input/Output Interfaces                  | 37 |

| Introduction                                         |    |

| Hardware Considerations                              |    |

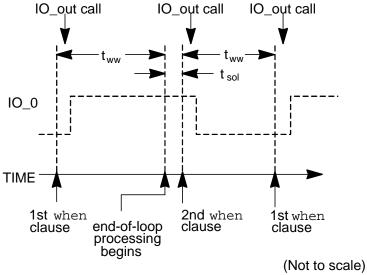

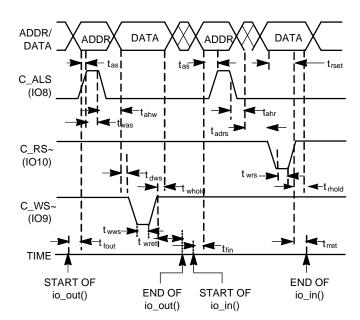

| I/O Timing Issues                                    |    |

| Scheduler-Related I/O Timing Information             |    |

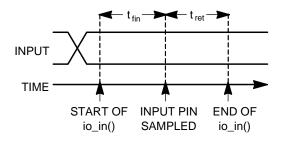

| Firmware and Hardware Related I/O Timing Information |    |

| Direct I/O Objects                                   |    |

| Bit Input/Output                                     | 46 |

| Byte Input/Output                                    | 48 |

| Leveldetect Input                                    | 49 |

| Nibble Input/Output                                  | 50 |

| Parallel I/O Objects                                 | 51 |

| Muxbus Input/Output                                  | 51 |

| Parallel Input/Output                                |    |

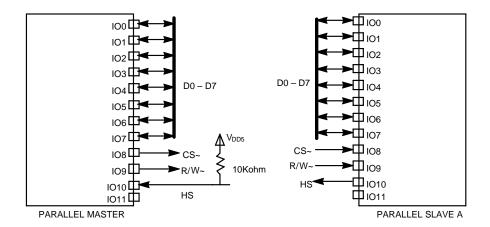

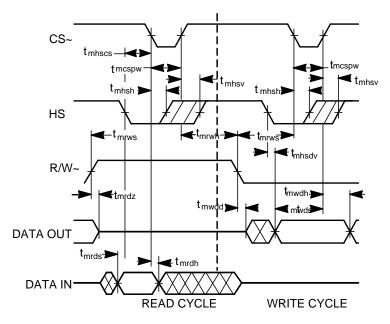

| Master/Slave A Mode                                  |    |

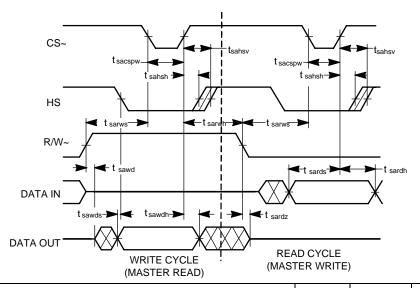

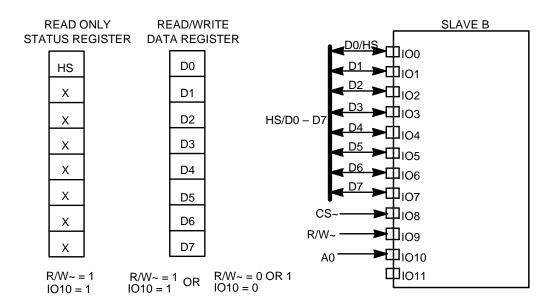

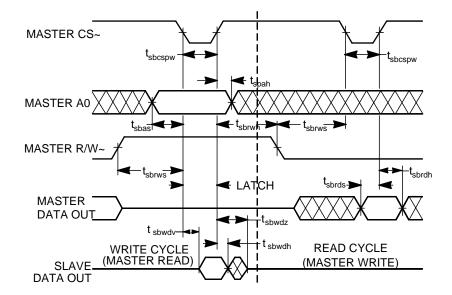

| Slave B Mode                                         |    |

| Serial I/O Objects                                   |    |

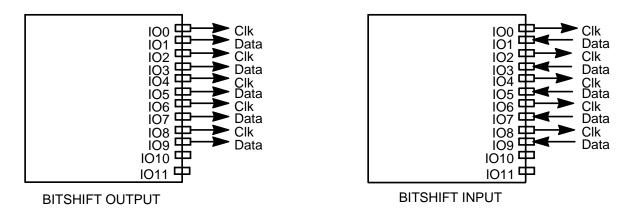

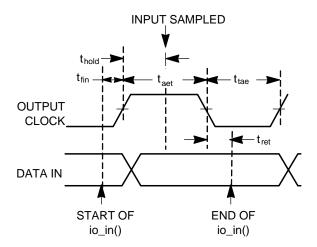

| Bitshift Input/Output                                |    |

| I <sup>2</sup> C Input/Output                        |    |

| Magcard Input                                        |    |

| Magtrack1 Input                                      |    |

| Magcard Bitstream Input                              |    |

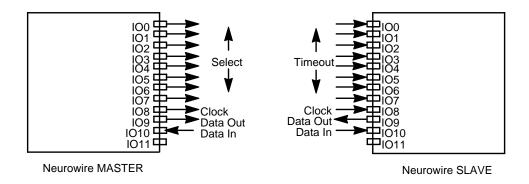

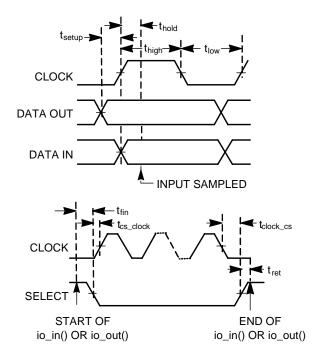

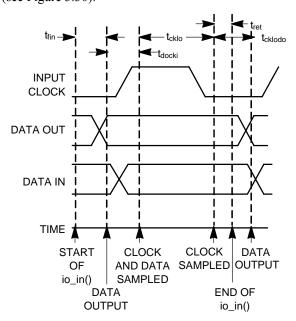

| Neurowire Input/Output Object                        |    |

| Neurowire Master Mode                                |    |

| Serial Input/Output                                  |    |

| Touch Input/Output                                   |    |

| Wiegand Input                                        |    |

| SCI (UART) Input/Output                              |    |

| SPI Input/Output                                     |    |

| Timer/Counter Input Objects                          |    |

| Dualslope Input                                      |    |

| Edgelog Input                                        |    |

| Infrared Input                                       |    |

| Ontime Input                                         |    |

| Period Input                                         |    |

| Pulsecount Input                                     |    |

| Quadrature Input                                     |    |

| Totalcount Input                                     | 92 |

| Timer/Counter Output Objects                         | 93 |

| Edgedivide Output                                                  | 93  |

|--------------------------------------------------------------------|-----|

| Frequency Output                                                   |     |

| Infrared Pattern Output                                            |     |

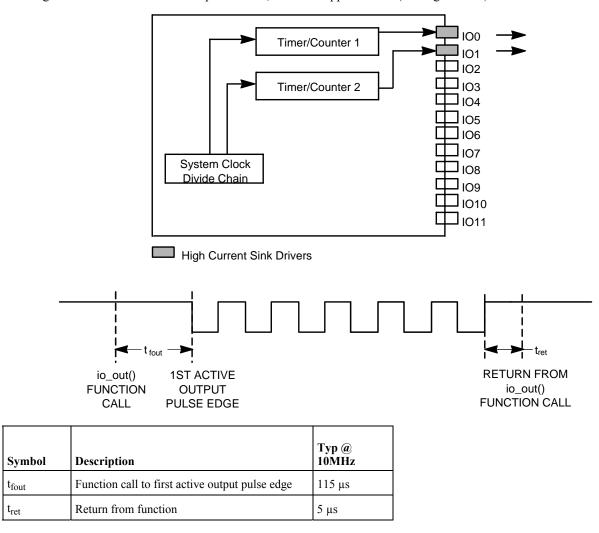

| Oneshot Output                                                     | 97  |

| Pulsecount Output                                                  |     |

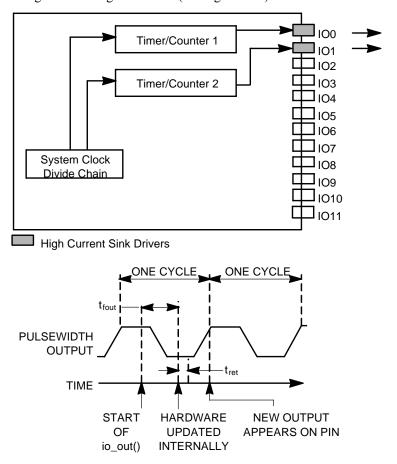

| Pulsewidth Output                                                  |     |

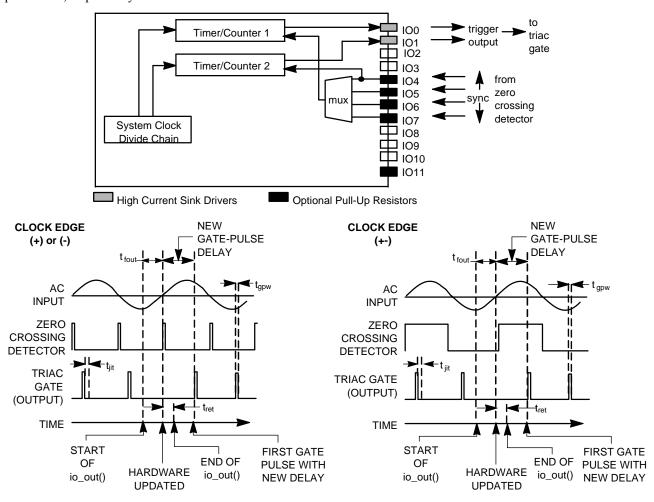

| Triac Output                                                       |     |

| Triggered Count Output                                             |     |

| Notes                                                              |     |

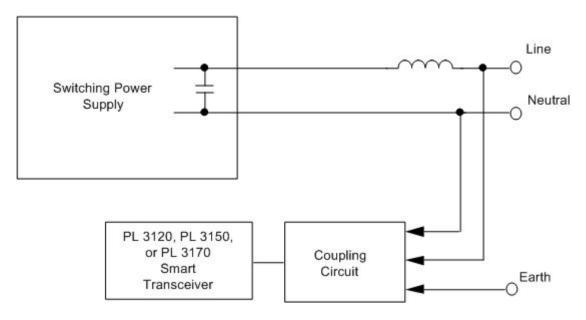

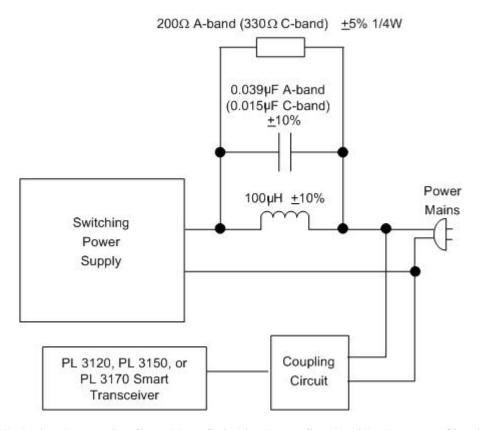

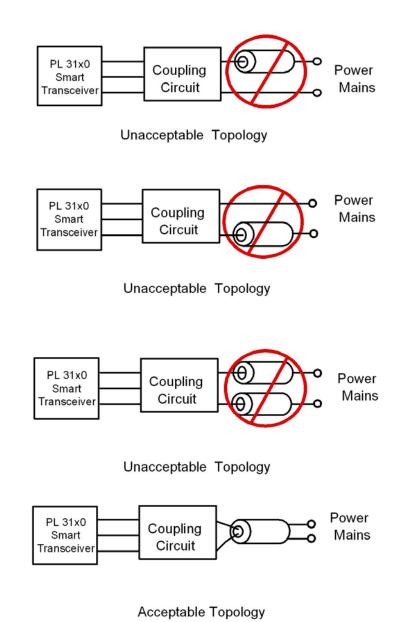

| Chapter 4 -Coupling Circuits                                       | 105 |

| Introduction                                                       | 106 |

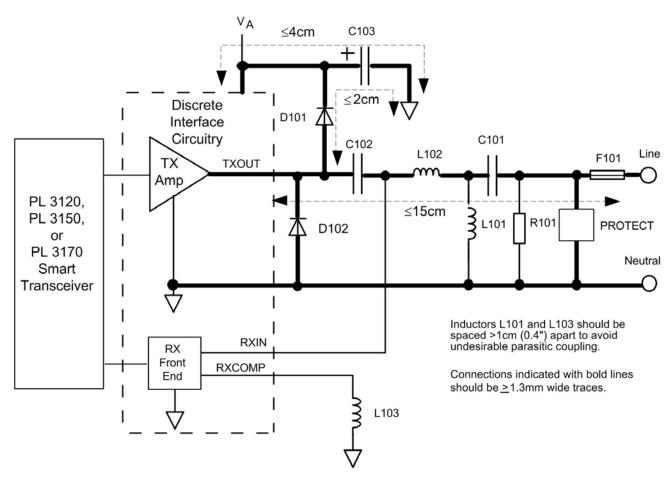

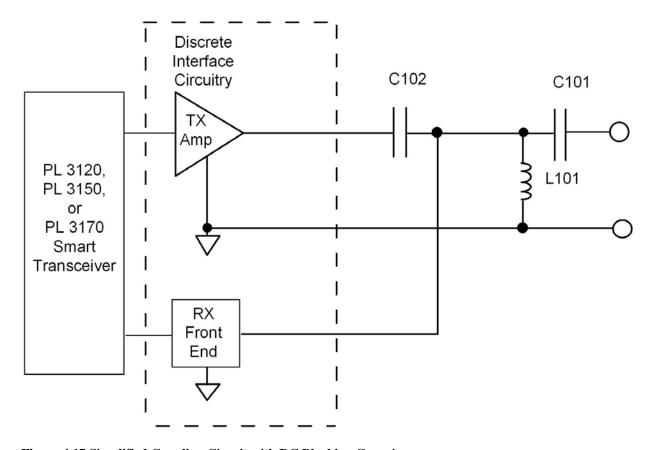

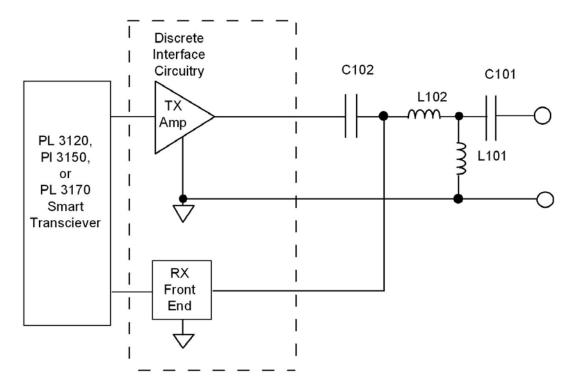

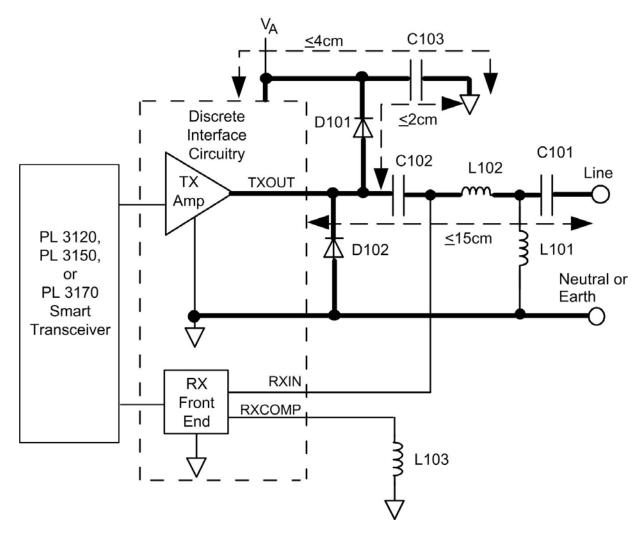

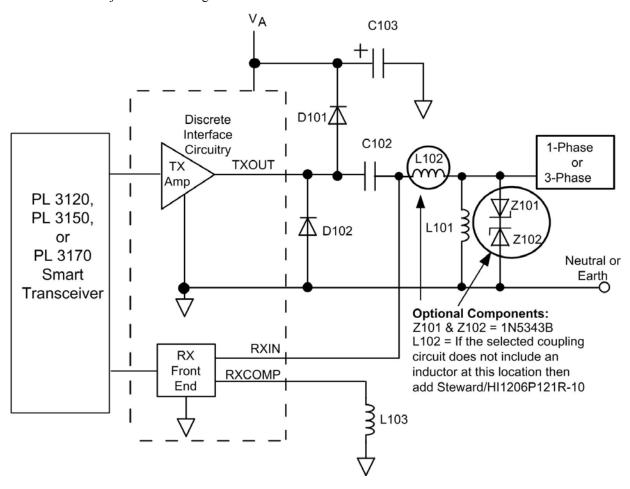

| Recommended Coupling Circuit                                       | 106 |

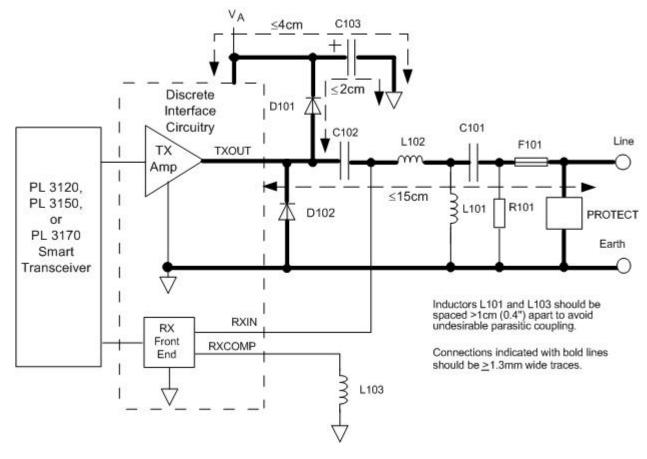

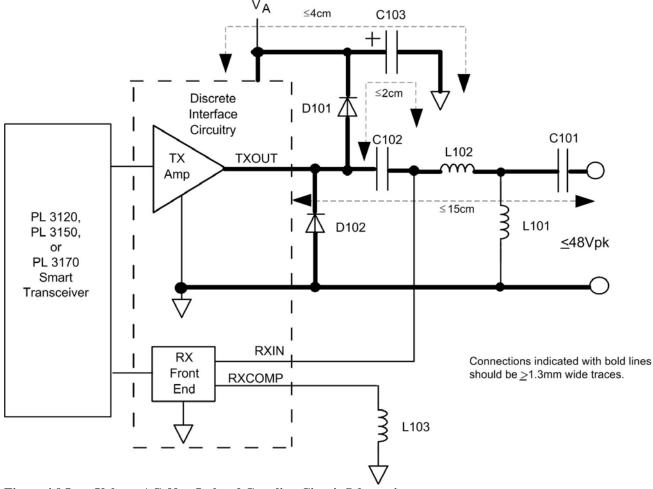

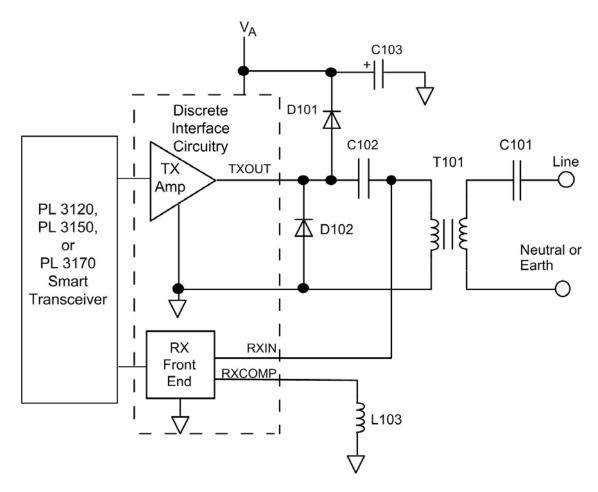

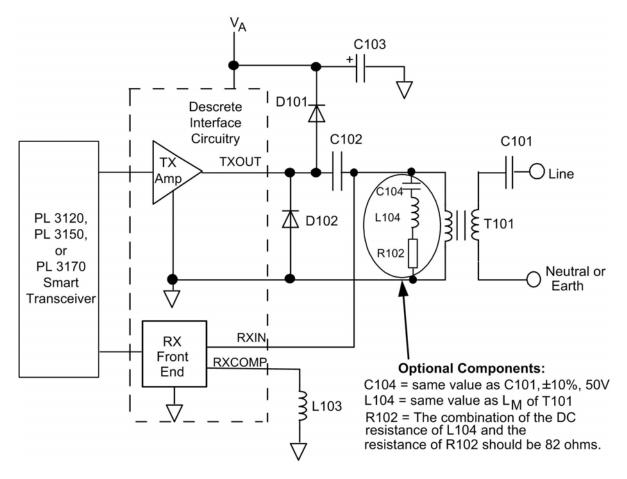

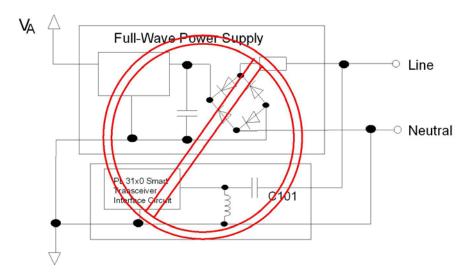

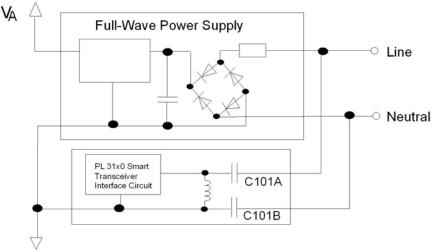

| Example 1. Line-to-Neutral, Non-Isolated Coupling Circuit          | 108 |

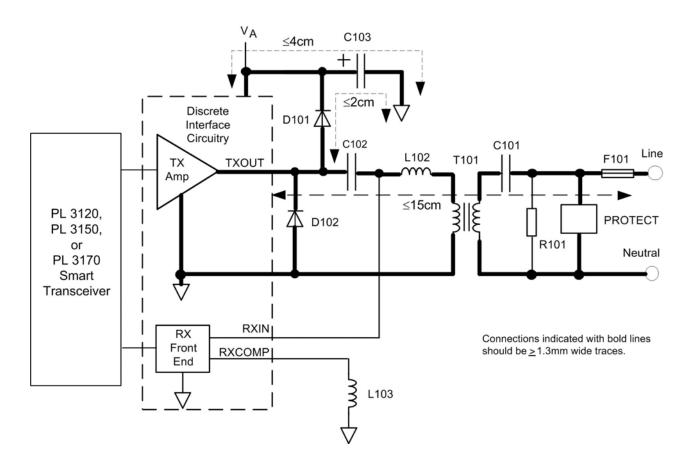

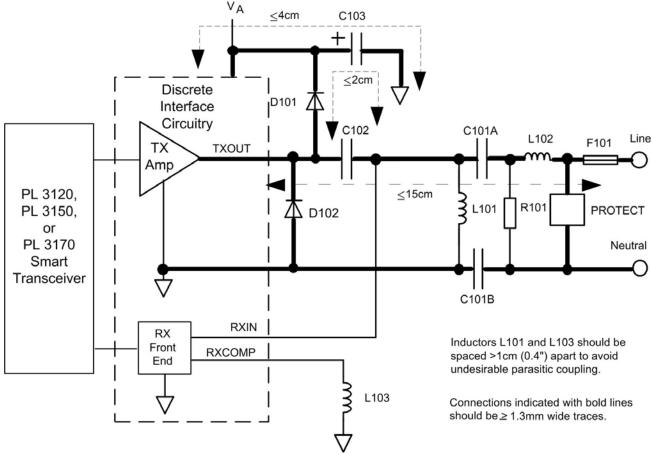

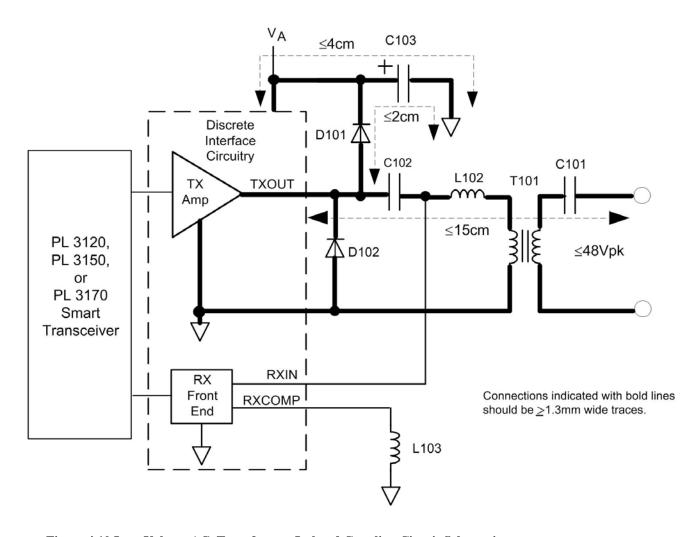

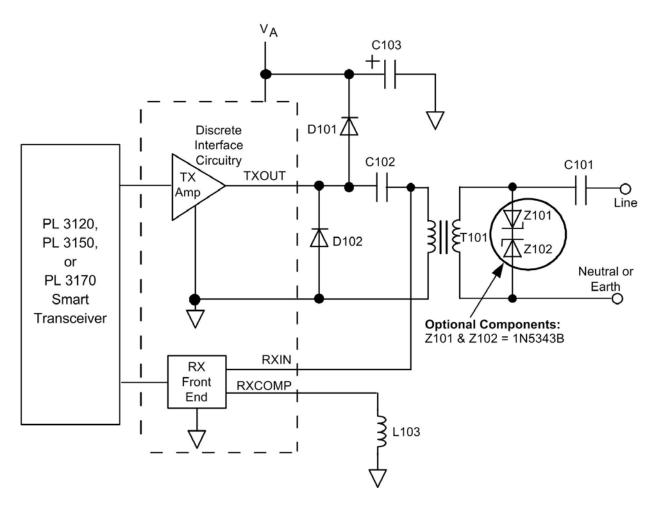

| Example 2. Line-to-Neutral, Transformer-Isolated Coupling Circuit  | 110 |

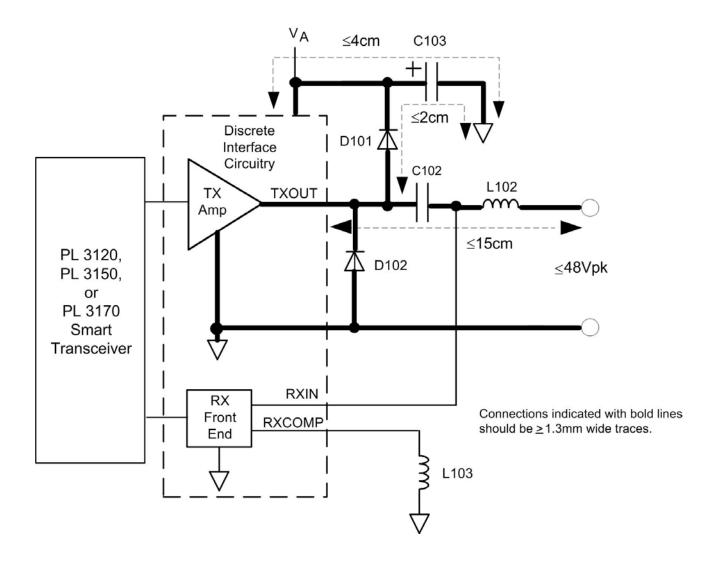

| Example 3. Line-to-Earth, Non-Isolated Coupling Circuit            | 112 |

| Example 4. Line-to-Earth, Transformer-Isolated Coupling Circuit    | 114 |

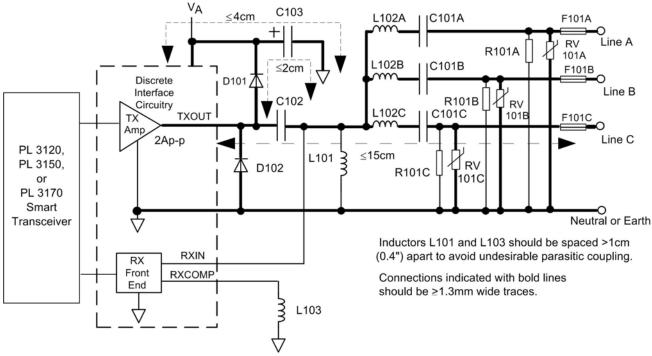

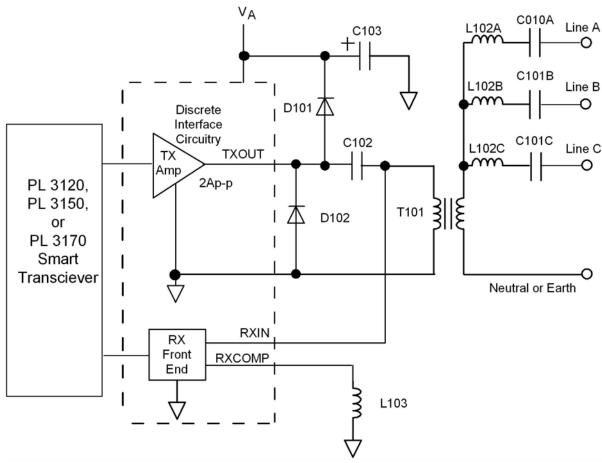

| Example 5. 3-Phase, Non-Isolated Coupling Circuit.                 | 116 |

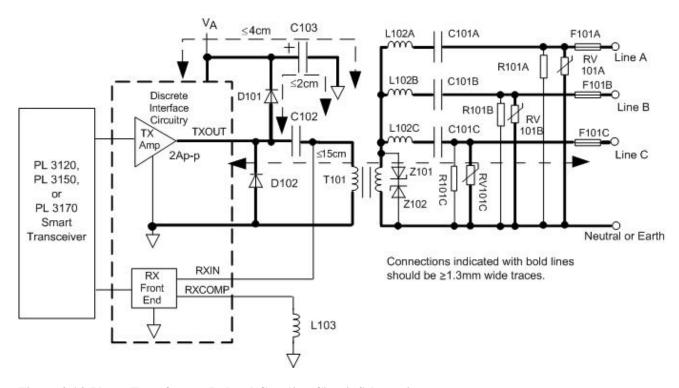

| Example 6. 3-Phase, Transformer-Isolated Coupling Circuit          | 118 |

| Example 7. Line-to-Neutral, Non-Isolated Floating Coupling Circuit |     |

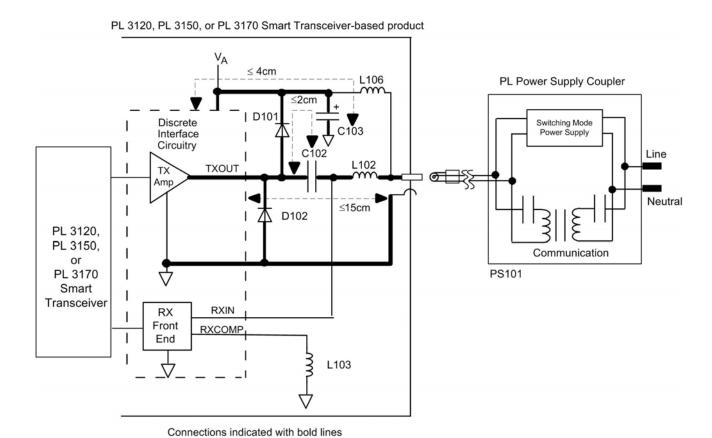

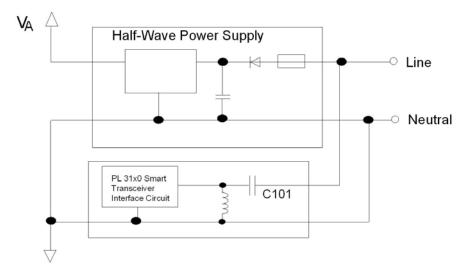

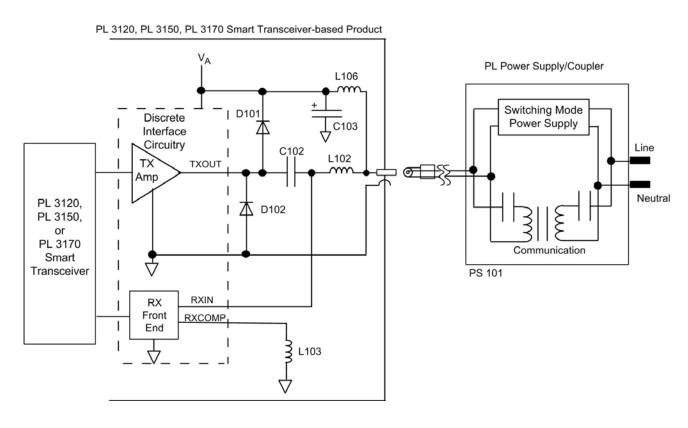

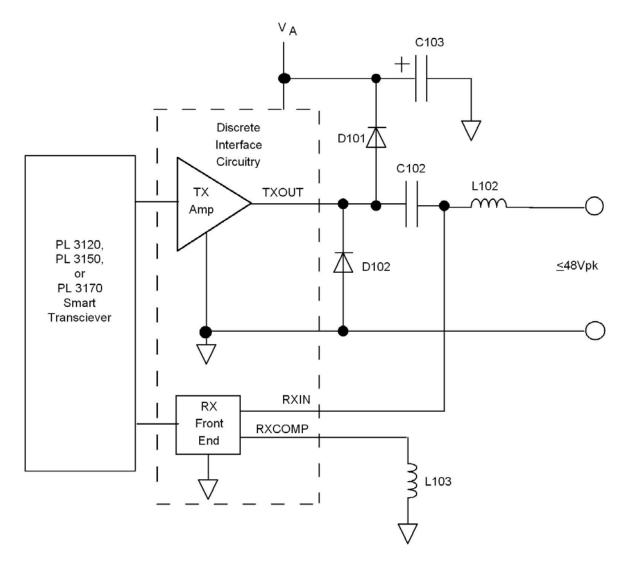

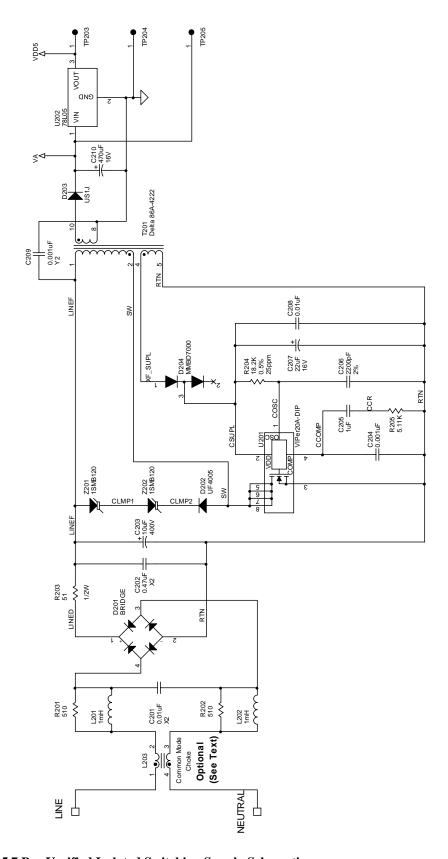

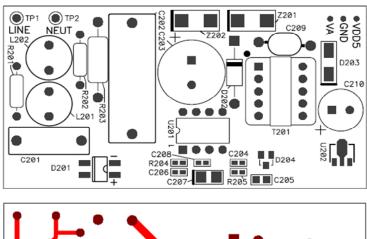

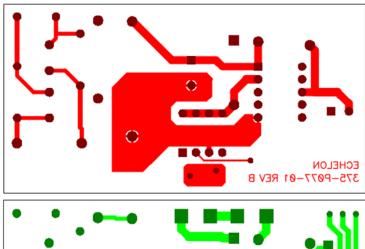

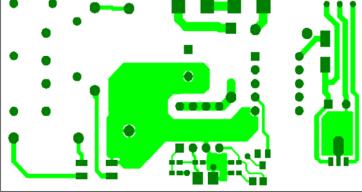

| Example 8. Line-to-Neutral, Power Line Power Supply Plus Coupler   |     |

| Example 9. Low-Voltage AC, Non-Isolated Coupling Circuit           |     |

| Example 10. Low-Voltage AC, Transformer-Isolated Coupling Circuit  | 126 |

| Example 11. Low-Voltage DC, Non-Isolated Coupling Circuit          |     |

| Coupling Circuit Tutorial                                          |     |

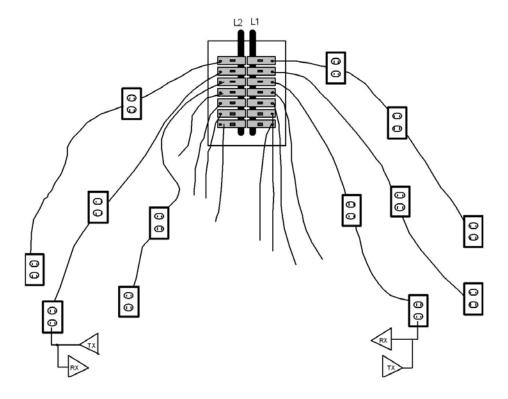

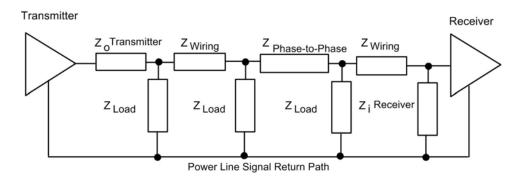

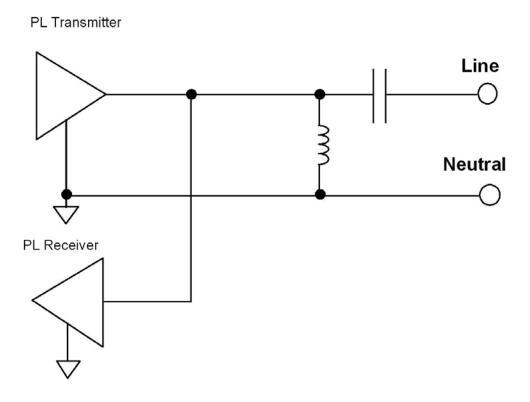

| Power Line Communications Background                               | 130 |

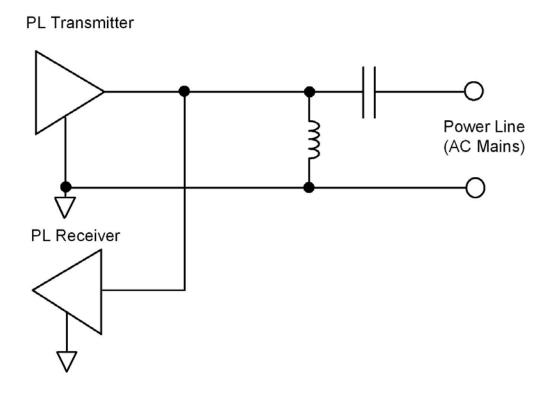

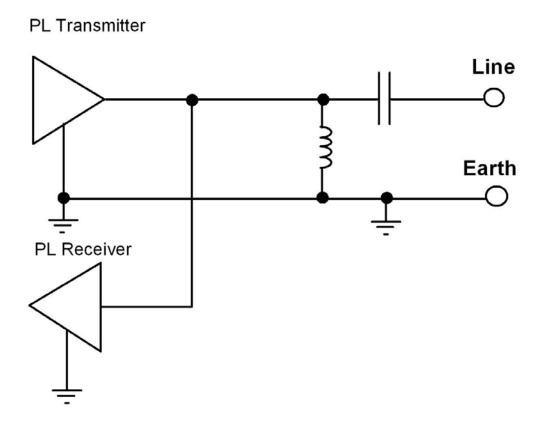

| Power Line Coupling Basics                                         | 132 |

| Power Line Coupling Details                                        | 134 |

| Coupling Circuit Receive Impedance                                 | 139 |

| Safety Issues                                                      | 139 |

| Safety Isolation Considerations                                    | 139 |

| Ground Leakage Currents                                            | 141 |

| Capacitor Charge Storage                                           | 142 |

| Fuse Selection                                                     | 142 |

| 3-Phase Coupling Circuits                                          | 142 |

| Non-isolated Floating Coupling Circuits                            | 143 |

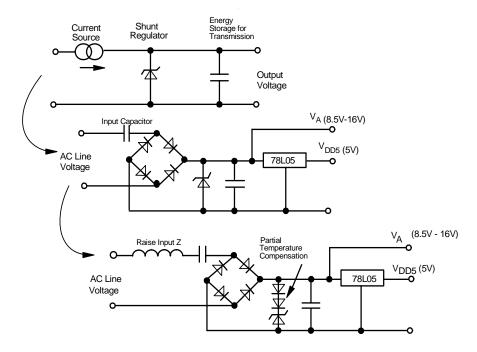

| Power Line Power Supply Plus Coupler                               | 145 |

| Low-Voltage Coupling Circuits                                      | 146 |

| Low-Voltage AC Coupling Circuits                                   | 146 |

| Low-Voltage DC Coupling Circuits                                   | 147 |

| Line Surge Protection                                              | 148 |

| Surge Immunity of Example Circuits                                 | 149 |

| Chapter 5 -Power Supplies for PL Smart Transceivers                |     |

| Introduction                                                       |     |

| Power Supply Design Options                                        |     |

| Energy Storage Power Supplies                                      | 156 |

|          | Energy Storage Capacitor-Input Power Supplies                | 158 |

|----------|--------------------------------------------------------------|-----|

|          | Energy Storage Linear Supplies                               | 161 |

|          | Traditional Linear Power Supplies                            | 162 |

|          | Pre-Verified Switching Power Supplies                        | 162 |

|          | Pre-Verified Energy Storage Switching Supply                 | 162 |

|          | A Pre-Verified Isolated Switching Supply                     |     |

|          | 5W and 10W Echelon Power Supply Plus Couplers                |     |

|          | Off-the-Shelf and Custom Switching Power Supplies            | 168 |

|          | Off-the-Shelf Switching Supplies                             |     |

|          | Full Custom Switching Supplies                               |     |

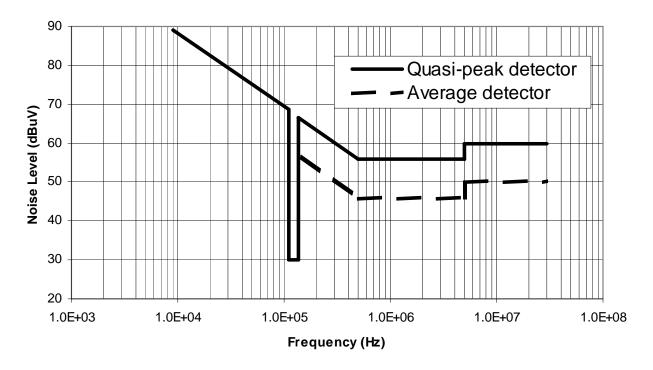

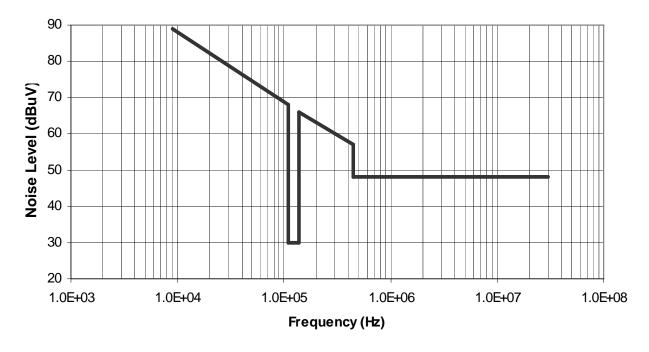

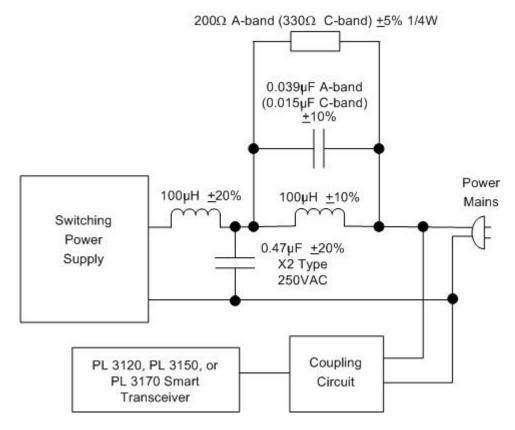

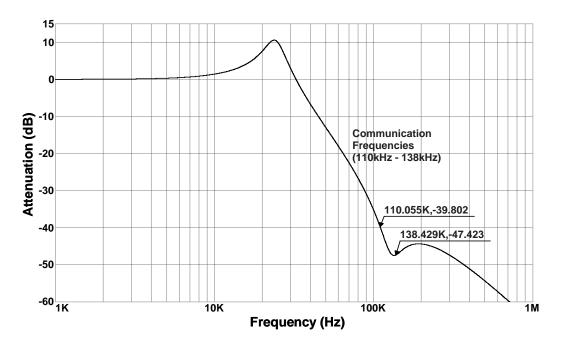

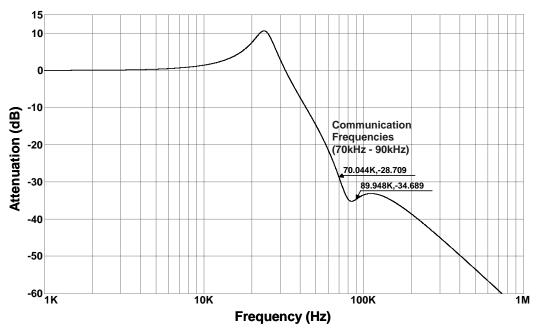

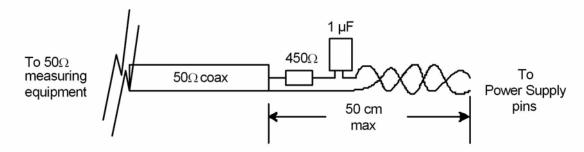

|          | Power Supply Impedance and Noise Requirements                | 170 |

|          | Power Supply-Induced Attenuation                             | 170 |

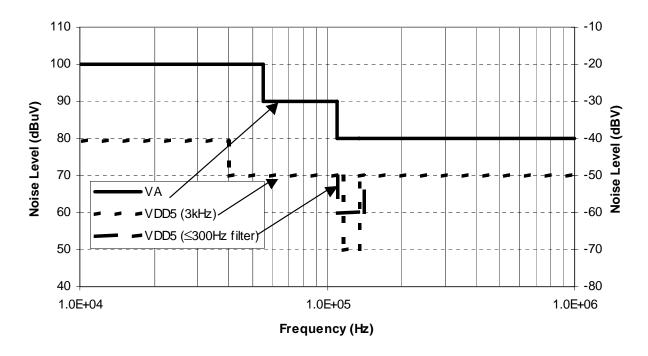

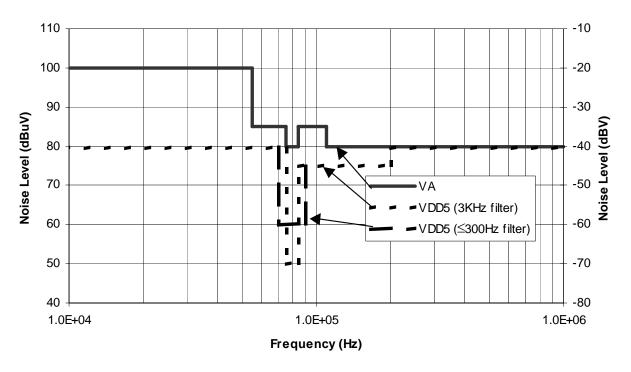

|          | Noise at the Power Supply Input                              | 173 |

|          | Switching Power Supply Input Noise Masks                     | 173 |

|          | Power Supply Output Noise Masks                              |     |

| C        | Chapter 6 -Design and Test for Electromagnetic Compatibility | 185 |

| <u> </u> | Introduction                                                 |     |

|          | Electromagnetic Interference (EMI) Compliance                | 186 |

|          | Conducted Emissions Testing                                  | 187 |

|          | EMI Remedies                                                 | 188 |

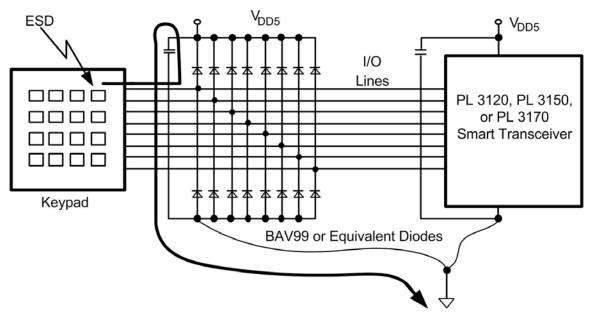

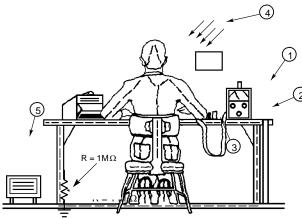

|          | Design for Electrostatic Discharge (ESD) Compliance          | 191 |

|          |                                                              |     |

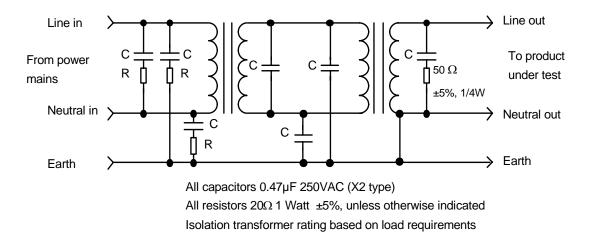

| C        | Chapter 7 -Communication Performance Verification            | 193 |

|          | Introduction                                                 |     |

|          | Reasons for Verifying Communication Performance              | 194 |

|          | Verification Procedure                                       |     |

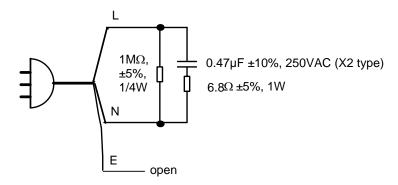

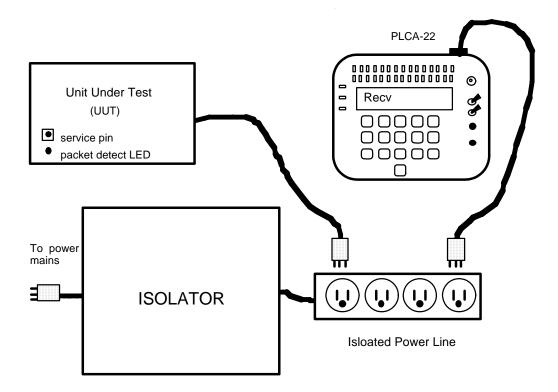

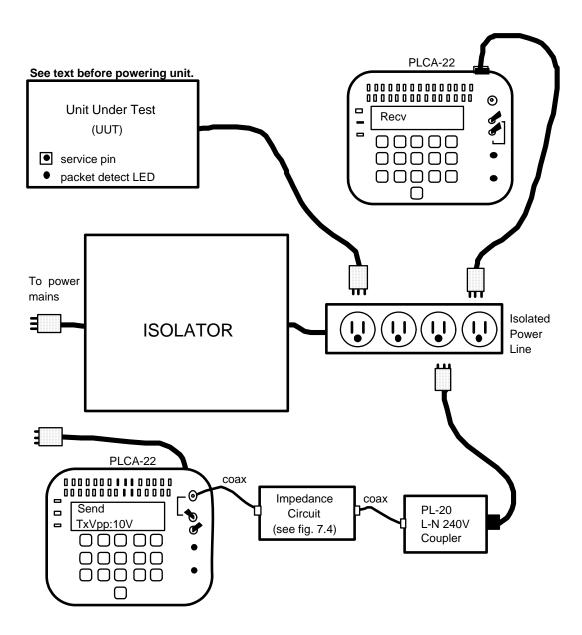

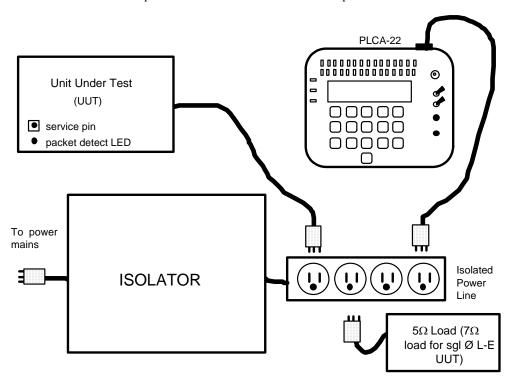

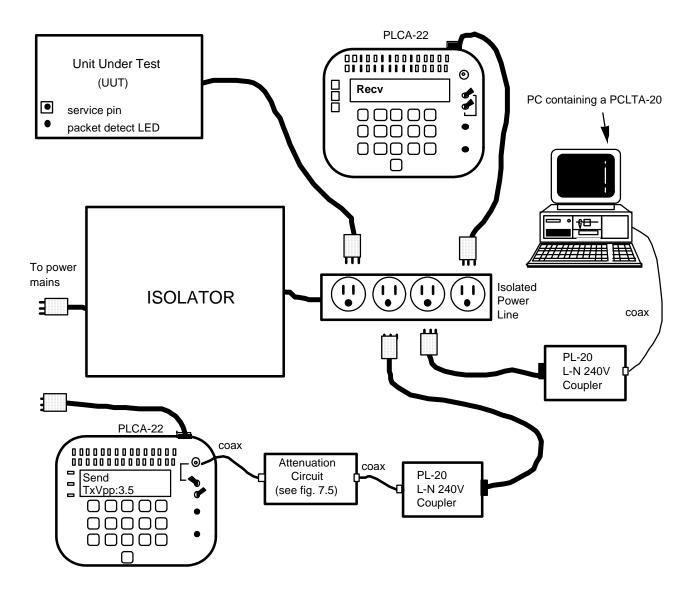

|          | Power Line Test Isolator                                     | 195 |

|          | Test Equipment.                                              |     |

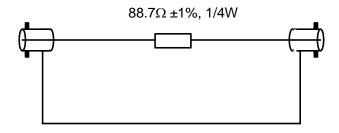

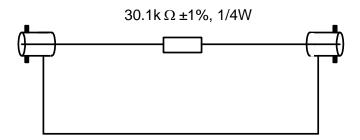

|          | Test Equipment to be Constructed                             |     |

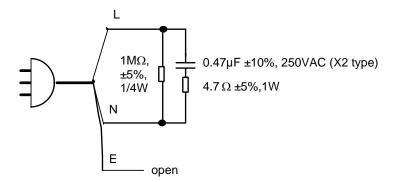

|          | "5 Ohm Load" Circuit                                         |     |

|          | "7 Ohm Load" Circuit                                         |     |

|          | Impedance Circuit                                            |     |

|          | Attenuation Circuit                                          | 197 |

|          | Good Citizen Verification                                    | 198 |

|          | Unintentional Output Noise Verification                      | 198 |

|          | Excessive Loading Verification                               | 199 |

|          | Transmit Performance Verification                            | 201 |

|          | Receive Performance Verification                             | 202 |

|          | Packet Error Measurement with NodeUtil                       | 202 |

|          | Receive Performance Verification Procedure                   |     |

| C        | Chapter 8 -PL Smart Transceiver Programming                  | 207 |

| <u> </u> | Introduction                                                 |     |

|          | Dual Carrier Frequency Mode                                  |     |

|          | CENELEC Access Protocol                                      |     |

|          | Power Management                                             | 209 |

|          |                                                              |     |

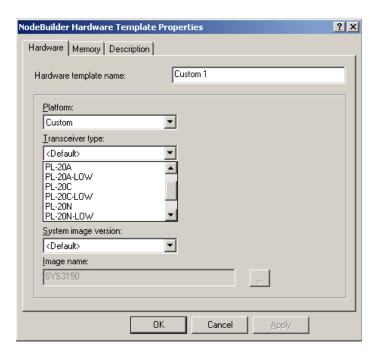

| Standard Transceiver Types                                              | 210 |

|-------------------------------------------------------------------------|-----|

| Development Tools Support                                               |     |

| Mini EVK Evaluation Kit                                                 |     |

| NodeBuilder Development Tool                                            |     |

| PL Smart Transceiver Channel Definitions                                |     |

| PL Smart Transceiver Clock Speed Selection                              | 212 |

| ShortStack Developer's Kit                                              |     |

| Downloading Application and Transceiver Type Parameters                 | 213 |

| Appendix A -PL Smart Transceiver Reference Designs                      | 215 |

| Introduction                                                            | 216 |

| Development Support Kit Contents                                        |     |

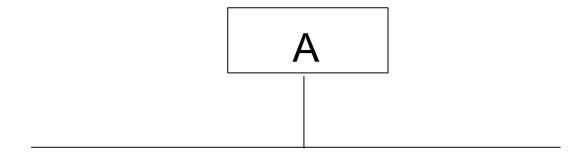

| Reference Design Files                                                  |     |

| Reference Design Specifications                                         |     |

| The Importance of Using Development Support Kit (DSK) Reference Designs |     |

| Appendix B -PL Smart Transceiver-Based Device Checklist                 | 223 |

|                                                                         |     |

| Introduction                                                            |     |

| Device Checklist                                                        | 225 |

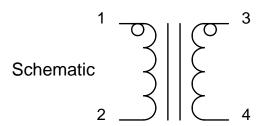

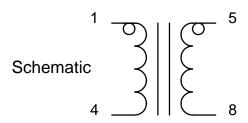

| Appendix C -Isolation Transformer Specifications                        | 231 |

| 12µH-Leakage Transformer Specifications                                 | 232 |

| Low-Leakage Transformer Specifications                                  | 233 |

| Appendix D -Manufacturing Test and Handling Guidelines                  | 235 |

|                                                                         |     |

| Production Test Guidelines                                              |     |

| Physical Layer Production Test                                          |     |

| Production Test Strategy                                                |     |

| Transmitter Performance Verification                                    |     |

| Receiver Performance Verification                                       |     |

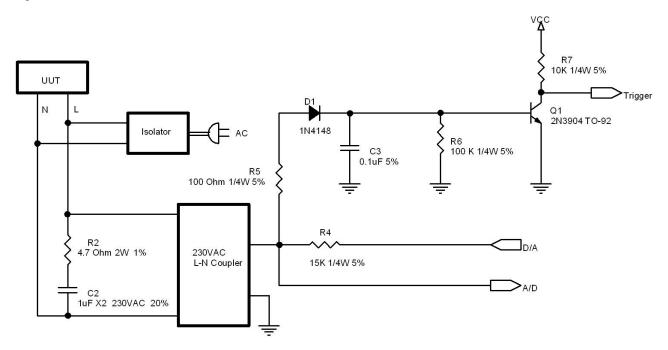

| A/D, D/A- based Test System                                             |     |

| Hardware Description                                                    |     |

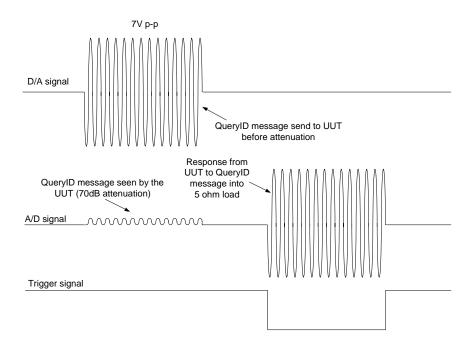

| Software Description                                                    |     |

| Test System Verification                                                |     |

| Verification of Background Noise                                        |     |

| Verification of Query ID Message Amplitude                              |     |

| Manufacturing Handling Guidelines                                       |     |

| Board Soldering Considerations                                          |     |

| Handling Precautions and Electrostatic Discharge                        |     |

| Wave-solder Operations                                                  |     |

| Board Cleaning Operations                                               |     |

|                                                                         |     |

| Appendix E -References                                                  | 245 |

Chapter 1

Introduction

#### **Overview**

This data book provides detailed technical specifications on the electrical interfaces, mechanical interfaces, and operating environment characteristics for the PL 3120®, PL 3150® and PL 3170 Power Line Smart Transceivers. This data book also provides guidelines for migrating applications to the PL Smart Transceiver using the NodeBuilder® Development Tool, the Mini EVK Evaluation Kit, or the ShortStack® Developer's Kit.

In some cases, vendor sources are included in this data book to simplify the task of integrating the PL Smart Transceivers with application electronics. A list of related documentation is provided in section 1.5, Related Documentation, at the end of this chapter. The documents listed in this section can be found on the Echelon Web site at www.echelon.com unless otherwise noted.

#### **Product Overview**

The PL Smart Transceivers provide a simple, cost-effective method of adding LonWorks® power line signaling and networking to everyday devices. Compliant with the open ANSI/EIA standards, the smart transceivers are ideal for networked appliance, audio/video, lighting, heating/cooling, security, metering, and irrigation applications.

Representing a breakthrough in price, performance and packaging size, the PL Smart Transceivers integrate a Neuron® processor core with a power line transceiver that is fully compatible with the LonMark® PL-20 channel type. Essentially a system-on-a-chip, the smart transceivers feature a highly reliable ANSI/EIA-709.2 compliant, narrow-band power line transceiver, an ANSI/EIA-709.1 compliant Neuron processor core for running applications and managing network communications, a choice of on-board or external memory, and an extremely small form factor. A wide variety of pre-designed, low-cost coupling circuit designs enable the PL Smart Transceivers to communicate over virtually any AC or DC power mains, as well as over an unpowered twisted pair.

#### LonWorks Networks

In almost every industry today, there is a trend away from proprietary control schemes and centralized systems. The migration towards open, distributed, peer-to-peer Lonworks networks is being driven by the interoperability, robust technology, faster development time, and scale economies afforded by Lonworks based solutions. All of the everyday devices in a Lonworks network communicate using the ANSI/EIA-709.1 protocol standard. This seven-layer OSI protocol provides a set of services that allow the application program in a device to send and receive messages from other devices in the network without needing to know the topology of the network or the functions of the other devices.

LONWORKS networks provide a complete suite of messaging services, including end-to-end acknowledgement, authentication, and priority message delivery. Network management services allow network tools to interact with devices over the network, including local or remote reconfiguration of network addresses and parameters, downloading of application programs, reporting of network problems, and start/stop/reset of device application programs.

Neuron Chips, a family of microprocessors originally designed by Echelon and licensed to third party semiconductor manufacturers, combine an ANSI/EIA-709.1 compliant processor core for running applications and managing the network communications, with a media-independent communication port, memory, I/O, and a 48-bit identification number (Neuron ID) that is unique to every device. The communication port permits short distance Neuron Chip-to-Neuron Chip communications, and can also be used with external line drivers and transceivers of almost any type.

The Neuron 3120 Chip family includes self-contained application program memory (no external memory bus) and the real-time operating system (RTOS) and application libraries pre-programmed in ROM. The Neuron 3150 Chip family includes both internal memory and an external memory bus.

The PL Smart Transceivers integrate a Neuron processor core with an ANSI/EIA-709.2 compliant power line transceiver within a single IC, eliminating the need for an external transceiver. Three variants of PL Smart Transceivers are available:

- The PL 3120 chip includes self-contained application program memory, RTOS, and application library preprogrammed in ROM.

- The PL 3150 chip includes both internal memory and an external memory bus.

- The **PL 3170** chip includes self-contained application program memory, Interoperable Self Installation (ISI) protocol, RTOS, and application library pre-programmed in ROM. With the ISI protocol, LonWorks devices can interoperate automatically or at the push of a button, without requiring the use of an installation tool.

#### **Three Product Families**

The following table describes the three PL Smart Transceivers.

| Product Name   | Model<br>Number | Maximum<br>Input<br>Clock | EEPROM     | RAM      | ROM       | External<br>Memory<br>Interface | IC Package |

|----------------|-----------------|---------------------------|------------|----------|-----------|---------------------------------|------------|

| PL 3120- E4T10 | 15311R-1000     | 10 MHz                    | 4 Kbytes   | 2 Kbytes | 24 Kbytes | No                              | 38 TSSOP   |

| PL 3170- E4T10 | 15331R-1000     | 10 MHz                    | 4 Kbytes   | 2 Kbytes | 24 Kbytes | No                              | 38 TSSOP   |

| PL 3150-L10    | 15321R-960      | 10 MHz                    | 0.5 Kbytes | 2 Kbytes | N/A       | Yes                             | 64 LQFP    |

The PL 3120 Smart Transceivers are targeted at small form factor designs that require up to 4KB of application code. The PL 3120 operates at either 6.5536MHz (A-band) or 10.0MHz (C-band), and includes 4KB of EEPROM and 2KB of RAM. Neuron system firmware (RTOS) along with application libraries is contained in on-chip ROM. The PL 3170 Smart Transceiver is targeted for the home control and automation market. The PL 3170 operates at 10.0MHz (C-band) only because this is the only band available for this market.

For applications that require more memory, the PL 3150 Smart Transceivers operate at either 6.5536MHz (A-band) or 10.0MHz (C-band), provide 0.5KB of EEPROM and 2KB of RAM, and use a 64 LQFP package. Through an external memory bus, the PL 3150 Smart Transceiver can address up to 58KB of external memory, of which 16KB is dedicated to Neuron system firmware.

The embedded EEPROM in both the PL Smart Transceivers can be written up to 10,000 times with no data loss. Data stored in the EEPROM will be retained for at least 10 years.

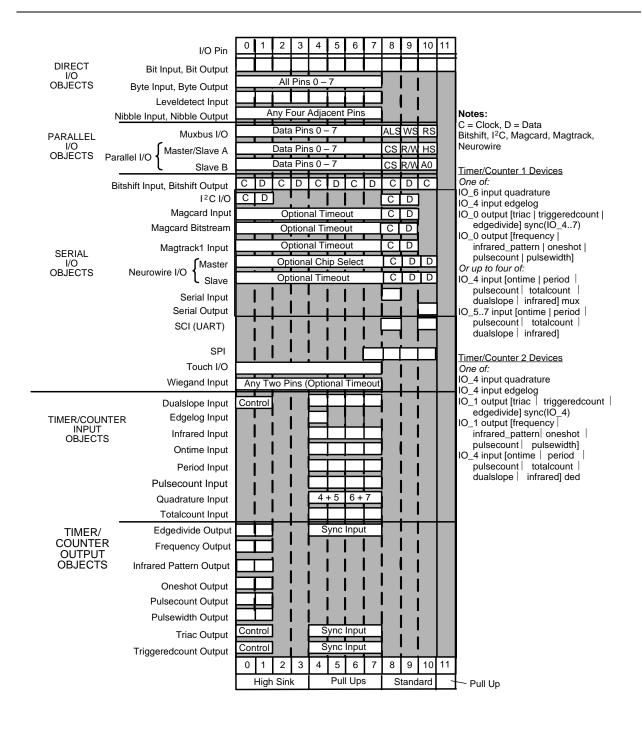

All three PL Smart Transceivers have 12 I/O pins which can be configured to operate in one or more of 38 predefined standard input/output modes. Combining a wide range of I/O models with two on-board timer/counters and hardware SCI/SPI UART enables the PL Smart Transceivers to interface to application circuits with minimal external logic or software development.

## **Power Line Signaling**

The underlying signaling technology used in the PL Smart Transceivers was developed and optimized through more than ten years of field-testing. Over 30 million of the Echelon narrow-band transceivers have been deployed in a wide range of consumer, utility, building, industrial, and transportation applications worldwide. Features such as narrow-band BPSK signaling, dual-carrier frequency operation, adaptive carrier and data correlation, impulse noise cancellation, tone rejection and low-overhead error correction provide superior reliability in the face of interfering noise sources.

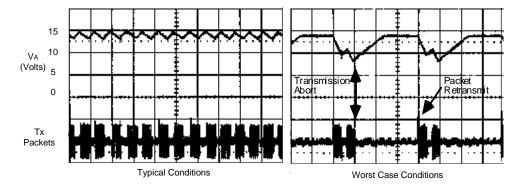

#### **Dual-Carrier Frequency Operation**

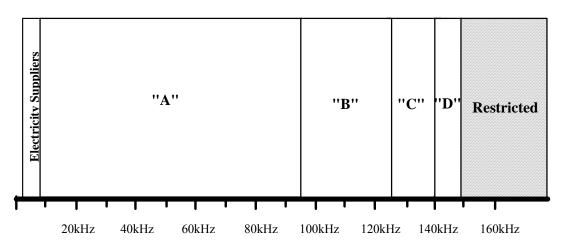

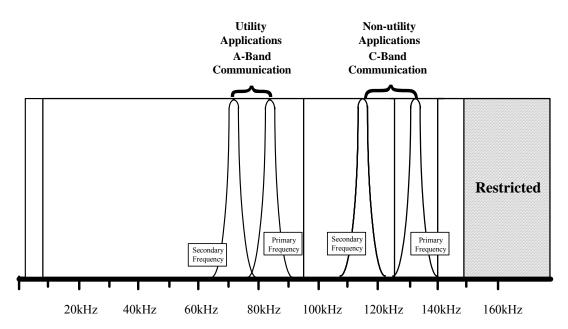

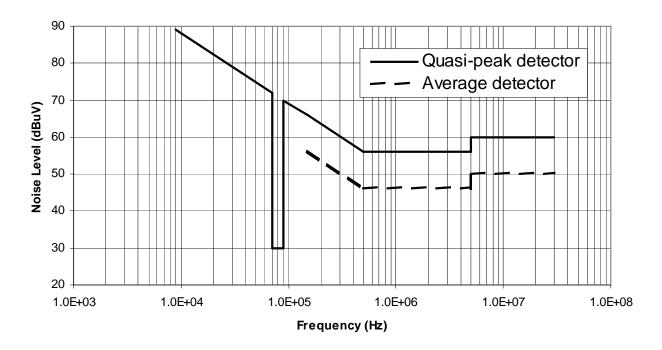

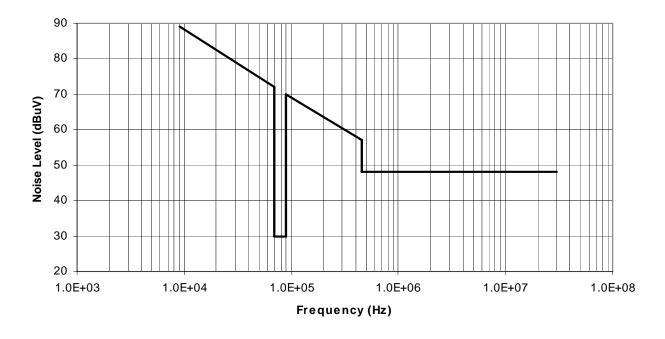

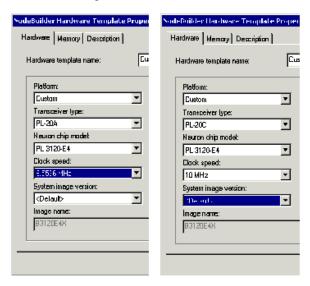

The PL Smart Transceivers utilize a dual-carrier frequency signaling technology to provide superior communication reliability in the face of interfering noise sources. In the case of acknowledged messaging, packets are initially transmitted on the primary frequency and if an acknowledgement is not received the packet is retransmitted on the secondary frequency. In the case of repeated messaging, packets are alternately transmitted on the primary and secondary frequencies. In utility applications the primary and secondary communication frequencies lie within the A-band shown in Figure 1.1. In non-utility applications, the primary communication frequency lies in the C-band shown in Figure 1.1 while the secondary frequency actually lies in what is called the B-band in CENELEC nomenclature. Figure 1.2 illustrates how the primary and secondary communications fit into the various frequency bands.

#### **Band Designations**

**Figure 1.1 CENELEC Frequency Band Designations**

Figure 1.2 Dual-Carrier Frequency Operation

#### **Forward Error Correction**

Many noise sources interfere with power line signaling by corrupting data packets. The PL Smart Transceivers use a highly efficient, low-overhead forward error correction (FEC) algorithm in addition to a cyclical redundancy check (CRC) to overcome packet errors.

#### **Powerful Output Amplifier**

The external, high performance amplifier design developed for use with the PL Smart Transceivers provides a 1 ohm output impedance and 1Ap-p current capability to drive high output levels into low impedance circuits, while maintaining the extremely low signal distortion levels necessary to meet stringent international EMC regulations. For applications requiring even more output power an optional higher power design is available that provides up to 2Ap-p of output current.

#### Wide Dynamic Range

Dynamic range relates to the sensitivity of the receiver. The PL Smart Transceivers have a dynamic range of > 80dB. On a quiet line the Power Line Smart Transceivers can receive signals that have been attenuated by a factor of more than 10,000.

#### **Low Current Consumption**

The PL Smart Transceivers and their associated power amplifier circuitry are powered by user-supplied +8.5 to +18VDC ( $V_A$ ) and +5VDC ( $V_{DD5}$ ) power supplies. Built-in power management features, combined with a wide supply range, are key benefits when designing inexpensive power supplies. Power management is especially useful for high volume, low cost consumer products such as electrical switches, outlets, and incandescent light dimmers.

Very low receive mode current consumption of just  $350\mu A$  typical from the  $V_A$  supply and 9mA typical from the  $V_{DDS}$  supply reduces power supply size and cost.

The PL Smart Transceivers communicate at a raw bit rate of 5.4kbps (C-band) or 3.6kbps (A-band), corresponding to the following maximum packet rates.

| Band   | Packets<br>Per<br>Second | Collisions | Minimum<br>Input Clock | Priority<br>Slots | Oscillator<br>Accuracy | Average<br>Packet<br>Size | Minimum<br>Backlog |

|--------|--------------------------|------------|------------------------|-------------------|------------------------|---------------------------|--------------------|

| C-band | 15                       | None       | 10MHz                  | 4                 | 200 PPM                | 15 bytes                  | 1                  |

| A-band | 10                       | None       | 6.5536MHz              | 4                 | 200 PPM                | 15 bytes                  | 1                  |

This high throughput makes the transceivers well suited for residential, commercial, and industrial automation applications.

## Compliant with Regulations Worldwide

The PL Smart Transceivers are designed to comply with FCC [1], Industry Canada, Japan MPT, China, and European CENELEC EN50065-1 regulations [2], allowing them to be used in applications worldwide. The CENELEC communications protocol is fully implemented by the PL Smart Transceivers, eliminating the need for users to develop the complex timing and access algorithms mandated under CENELEC EN50065-1. Additionally, the PL 3120 and 3150 Smart Transceivers can operate in either the CENELEC utility (A-band) or consumer (C-band) bands.

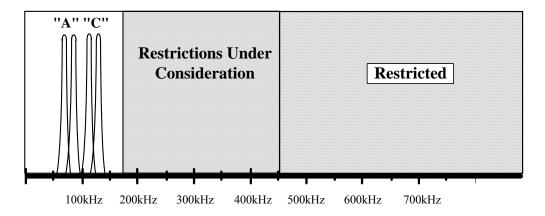

Figure 1.1 shows the CENELEC frequency restrictions that are mandatory in EU countries and are observed in many non-EU countries as well. FCC, Industry Canada and the Japan MPT regulations are less strict than the CENELEC requirements. The frequency allocations for these countries are summarized in Figure 1.3.

Figure 1.3 FCC, Industry Canada, Japan MPT Power-line Signaling

## Integrated, Low-Cost and Small Form Factor Design

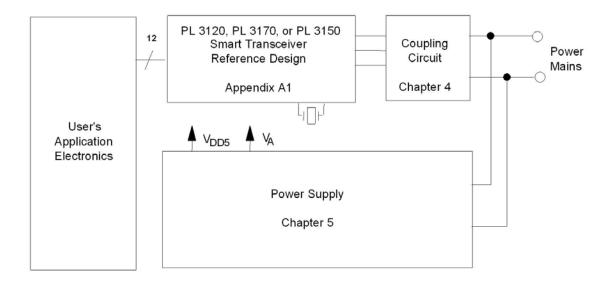

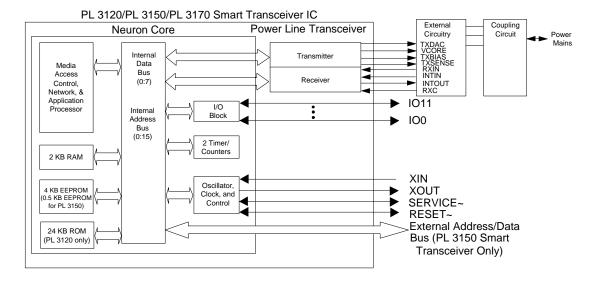

A small number of inexpensive external components are required to create a complete PL Smart Transceiver-based device. Figure 1.4 illustrates the block diagram of a PL Smart Transceiver based device. Acomprehensive Development Support Kit (DSK) is available from Echelon that includes sample PL Smart Transceivers, schematics, printed circuit board (PCB) layouts, bills of materials, and technology evaluation hardware with sample application code that customers can use to implement this interface circuitry.

LonWorks Node - Chapters 6,7,8

Figure 1.4 LONWORKS Device Block Diagram

# Electric Utility vs. Home/Commercial/Industrial Applications

The PL 3120 and PL 3150 Smart Transceivers are designed to operate in one of two frequency ranges depending on the end application. However, the PL 3170 Smart Transceiver is designed to operate in one frequency range for the home control and automation market. When configured for use in electric utility applications, the Smart Transceivers communicate in the A-band frequency range. In home/commercial/industrial applications, they communicate in the C-band frequency range. The use of separate operating frequency bands for utility and non-utility applications originated in Europe and has because become a de facto standard because of the numerous benefits it provides in terms of bandwidth management, security, and privacy.

## **Extensive Development Resources**

A wide assortment of technical documentation, diagnostic tools, support programs, and training courses are available to assist customers with their projects. Additionally, Echelon offers fee-based pre-production design reviews of customer's products, schematics, PCB layouts, and bills of material to verify that they comply with published guidelines. Communication performance-verification testing is provided to customers who submit working devices.

#### **Audience**

The PL 3120/PL 3150/ PL 3170 Power Line Smart Transceiver Data Book provides specifications and user instructions for PL Smart Transceiver customers.

#### Content

This data book describes the use of the PL Smart Transceivers in both utility (A-band) and home/commercial/industrial (C-band) applications.

### **Related Documentation**

The following documents are suggested reading and are available at Echelon's Web site:

PL 3120/PL 3150 Power Line Smart Transceiver Data Sheet (003-0378-01)

PL 3170 Power Line Smart Transceiver Data Sheet (003-0431-01)

Neuron C Programmer's Guide (078-0002-02)

Neuron C Reference Guide (078-0140-02)

Neuron 3150 Chip External Memory Interface Engineering Bulletin (005-0013-01)

ShortStack User's Guide (078-0189-01)

ShortStack 2 Nios II Example Port User's Guide (078-0354-01)

LONWORKS Microprocessor Interface Program User's Guide (078-0017-01)

NodeBuilder User's Guide (078-0141-01)

Mini EVK User's Guide (078-0302-01)

Parallel I/O Interface to the Neuron Chip Engineering Bulletin (005-0021-01)

### Chapter 1 - Introduction

PLCA-22 Power Line Communication Analyzer User's Guide (078-0147-01)

LONWORKS PCLTA-20 PCI Interface User's Guide (078-0179-01)

LONWORKS USB Network Interface User's Guide (078-0296-01)

Neuron Chip Quadrature Input Function Interface Engineering Bulletin (005-0003-01)

Chapter 2

Hardware Resources

#### **Overview**

The PL 3120 Smart Transceiver is a complete SoC (system-on-a-chip) for designs that require up to 4KB of memory. The PL 3170 Smart Transceiver includes self-contained application program memory, Interoperable Self-Installation (ISI) library and engine, RTOS, and an application library pre-programmed in ROM. The PL 3150 Smart Transceiver supports external memory for more complex applications. The major hardware blocks of the processors are the same, except where noted; see Table 2.1 and Figure 2.1.

| <b>Table 2.1</b> ( | Comparison | of PL Smart | Transceivers |

|--------------------|------------|-------------|--------------|

|--------------------|------------|-------------|--------------|

| Tubic III Comparison of   |                              | - ~                          |                              |

|---------------------------|------------------------------|------------------------------|------------------------------|

| Characteristic            | PL 3150 Smart<br>Transceiver | PL 3120 Smart<br>Transceiver | PL 3170 Smart<br>Transceiver |

| RAM Bytes                 | 2,048                        | 2,048                        | 2,048                        |

| ROM Bytes                 | _                            | 24,576                       | 24,576                       |

| ROM Version               | N/A                          | V 14                         | V 17                         |

| EEPROM Bytes              | 512                          | 4,096                        | 4,096                        |

| General purpose I/O pins  | 12                           | 12                           | 12                           |

| 16-Bit Timer/Counters     | 2                            | 2                            | 2                            |

| External Memory Interface | Yes                          | No                           | No                           |

| Package                   | 64 pin LQFP                  | 38 pin TSSOP                 | 38 pin TSSOP                 |

Figure 2.1 PL Smart Transceiver Block Diagram

## **Neuron Processor Architecture**

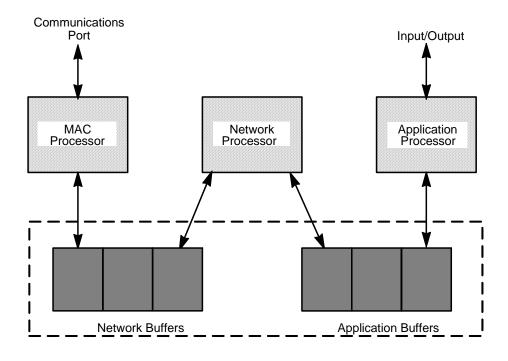

The Neuron core is composed of three processors. These processors are assigned to the following functions by the Neuron firmware.

Processor 1 is the MAC layer processor that handles layers 1 and 2 of the 7-layer LonTalk<sup>®</sup> protocol stack. This includes driving the communications subsystem hardware and executing the media access control algorithm. Processor 1 communicates with Processor 2 using network buffers located in shared RAM memory.

Processor 2 is the network processor that implements layers 3 through 6 of the LonTalk protocol stack. It handles network variable processing, addressing, transaction processing, authentication, background diagnostics, software timers, network management, and routing functions. Processor 2 uses network buffers in shared memory to communicate with Processor 1, and application buffers to communicate with Processor 3. These buffers are also located in shared RAM memory. Access to them is mediated with hardware semaphores to resolve contention when updating shared data.

Shared

**Figure 2.2 Processor Shared Memory Allocation**

Processor 3 is the application processor. It executes the code written by the user, together with the operating system services called by user code. The primary programming language used by applications is Neuron C, a derivative of the ANSI C language optimized and enhanced for Lonworks distributed control applications. The major enhancements are the following (see the *Neuron C Programmer's Guide* for details):

- A network communication model, based on *functional blocks* and *network variables*, that simplifies and promotes data sharing between like and disparate devices.

- A network configuration model, *based on functional blocks and configuration properties*, that facilitates interoperable network configuration tools.

- A type model based on standard and user *resource files* that expands the market for interoperable devices by simplifying the integration of devices from multiple manufacturers.

- An extensive set of I/O drivers that support the I/O capabilities of the Neuron core.

- Powerful event driven programming extensions that provide easy handling of network, I/O, and timer events.

The support for all these capabilities is part of the Neuron firmware, and does not need to be written by the programmer.

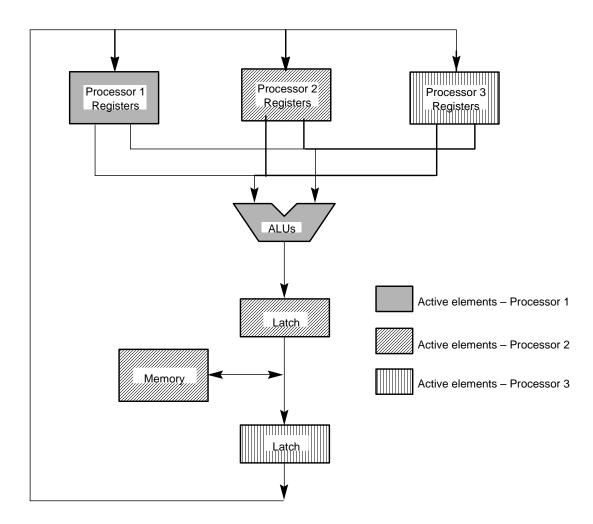

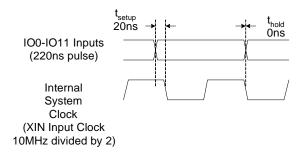

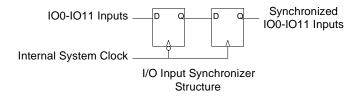

Each of the three identical processors has its own register set (Table 2.2), but all three processors share data, ALUs (arithmetic logic units) and memory access circuitry (Figure 2.3). On the PL 3150 Smart Transceiver, the internal address, data, and R/W~ signals are reflected on the corresponding external lines when utilized by any of the internal processors. Each CPU *minor* cycle consists of *three system clock* cycles, or phases; each system clock cycle is two input clock cycles. The minor cycles of the three processors are offset from one another by one system clock cycle, so that each processor can access memory and ALUs once during each instruction cycle. Figure 2.3 shows the active elements for each processor during one of the three phases of a minor cycle. Therefore, the system pipelines the three processors, reducing hardware requirements without affecting performance. This allows the execution of three processes in parallel without time-consuming interrupts and context switching.

**Table 2.2 Register Set**

| Mnemonic | Bits | Contents                                   |  |

|----------|------|--------------------------------------------|--|

| FLAGS    | 8    | CPU Number, Fast I/O Select, and Carry Bit |  |

| IP       | 16   | Next Instruction Pointer                   |  |

| BP       | 8    | Address of 256-byte Base Page              |  |

| DSP      | 8    | Data Stack Pointer within Base Page        |  |

| RSP      | 8    | Return Stack Pointer within Base Page      |  |

| TOS      | 8    | Top of Data Stack, ALU Input               |  |

Figure 2.3 Processor/Memory Activity During One of the Three System Clock Cycles of a Minor Cycle

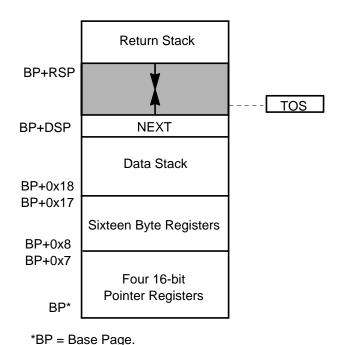

The architecture is stack-oriented; one 8-bit wide stack is used for data references, and the ALU operates on the TOS (Top of Stack) register and the next entry in the data stack which is in RAM. A second stack stores the return addresses for CALL instructions, and can also be used for temporary data storage. This stack architecture leads to very compact code. Tables 2.3, 2.4, and 2.5 outline the instruction set.

Figure 2.4 shows the layout of a base page, which can be up to 256 bytes long. Each of the three processors uses a different base page, whose address is given by the contents of the BP register of that processor. The top of the data stack is in the 8-bit TOS register, and the next element in the data stack is at the location within the base page at the offset given by the contents of the DSP register. The data stack grows from low memory towards high memory. The assembler shorthand symbol NEXT refers to the contents of the location (BP+DSP) in memory, which is not an actual processor register.

Pushing a byte of data onto the data stack involves the following steps: incrementing the DSP register, storing the current contents of TOS at the address (BP+DSP) in memory, and moving the byte of data to TOS.

Popping a byte of data from the data stack involves the following steps: moving TOS to the destination, moving the contents of the address (BP+DSP) in memory to TOS, and decrementing the DSP register.

The return stack grows from high memory towards low memory. Executing a subroutine call involves the following steps: storing the high byte of the instruction pointer register IP at the address (BP+RSP) in memory, decrementing RSP, storing the low byte of IP at the address (BP+RSP) in memory, decrementing RSP, and moving the destination address to the IP register.

Similarly, returning from a subroutine involves the following steps: incrementing RSP, moving the contents of (BP+RSP) to the low byte of the IP register, incrementing RSP, and moving the contents of (BP+RSP) to the high byte of IP.

ŭ

Figure 2.4 Base Page Memory Layout

#### Chapter 2 – Hardware Resources

A processor instruction cycle is three system clock cycles, or six input clock (XIN) cycles. Most instruction take between one and seven processor instruction cycles. At an input clock rate of 10MHz, instruction times vary between 0.6 µs and 4.2 µs. Execution time scales inversely with the input clock rate. The formula for instruction time is:

(Instruction Time) = (# Cycles) x 6 / (Input Clock)

Tables 2.3, 2.4, and 2.5 list the processor instructions, their timings (in cycles) and sizes (in bytes). This is provided for purposes of calculating the execution time and size of code sequences. All programming of the PL Smart Transceiver is typically done with Neuron C using the NodeBuilder development tool or the Mini EVK Evaluation Kit. The Neuron C compiler can optionally produce an assembly listing, and examining this listing can help the programmer to optimize the Neuron C source code.

**Table 2.3 Program Control Instructions**

| Mnemonic        | Cycles | Size<br>(bytes) | Description                               | Comments                                                            |

|-----------------|--------|-----------------|-------------------------------------------|---------------------------------------------------------------------|

| NOP             | 1      | 1               | No operation                              |                                                                     |

| SBR             | 1      | 1               | Short unconditional branch                | Offset 0 to 15                                                      |

| BR/BRC/BRN<br>C | 2      | 2               | Branch, branch on (not) carry             | Offset -128 to +127                                                 |

| SBRZ/SBRNZ      | 3      | 1               | Short branch on TOS (not) zero            | Offset 0 to 15. Drops TOS                                           |

| BRF             | 4      | 3               | Unconditional branch far                  | Absolute address                                                    |

| BRZ/BRNZ        | 4      | 2               | Branch on TOS (not) zero                  | Offset -128 to +127. Drops TOS                                      |

| RET             | 4      | 1               | Return from subroutine                    | Drops two bytes from return stack                                   |

| BRNEQ           | 4/6    | 3               | Branch if TOS not equal (taken/not taken) | Offset -128 to +127. Drops TOS if equal                             |

| DBRNZ           | 5      | 2               | Decrement [RSP] and branch if not zero    | Offset -128 to +127. If not taken, drops one byte from return stack |

| CALLR           | 5      | 2               | Call subroutine relative                  | Offset -128 to +127. Pushes two bytes to return stack               |

| CALL            | 6      | 2               | Call subroutine                           | Address in low 8KB. Pushes two bytes to return stack                |

| CALLF           | 7      | 3               | Call subroutine far                       | Absolute address. Pushes two bytes to return stack                  |

**Table 2.4 Memory/Stack Instructions**

| Mnemonic                     | Cycles | Size (bytes) | Comments / Effective Address (EA)                 |

|------------------------------|--------|--------------|---------------------------------------------------|

| PUSH TOS                     | 3      | 1            | Increment DSP, duplicate TOS into NEXT            |

| DROP TOS                     | 3      | 1            | Move NEXT to TOS, decrement DSP                   |

| DROP_R TOS                   | 6      | 1            | Move NEXT to TOS, decrement DSP, return from call |

| PUSH (NEXT, DSP, RSP, FLAGS) | 4      | 1            | Push processor register                           |

| POP (DSP, RSP, FLAGS)        | 4      | 1            | Pop processor register                            |

| DROP NEXT                    | 2      | 1            | Decrement DSP                                     |

| DROP_R NEXT                  | 5      | 1            | Decrement DSP and return from call                |

| PUSH/POP !D         | 4      | 1 | Byte register [8 to 23]                             |

|---------------------|--------|---|-----------------------------------------------------|

| PUSH !TOS           | 4      | 1 | EA = BP + TOS, push byte to NEXT                    |

| POP !TOS            | 4      | 1 | EA = BP + TOS, pop byte from NEXT                   |

| PUSH [RSP]          | 4      | 1 | Push from return stack to data stack, RSP unchanged |

| DROP [RSP]          | 2      | 1 | Increment RSP                                       |

| PUSHS #literal      | 4      | 1 | Push short literal value [0 to 7]                   |

| PUSH #literal       | 4      | 2 | Push 8-bit literal value [0 to 255]                 |

| PUSHPOP             | 5      | 1 | Pop from return stack, push to data stack           |

| POPPUSH             | 5      | 1 | Pop from data stack, push to return stack           |

| LDBP address        | 5      | 3 | Load base page pointer with 16-bit value            |

| PUSH/POP [DSP][-D]  | 5      | 1 | EA = BP + DSP - displacement [1 to 8]               |

| PUSHD #literal      | 6      | 3 | 16-bit literal value (high byte first)              |

| PUSHD [PTR]         | 6      | 1 | Push from 16-bit pointer [0 to 3], high byte first  |

| POPD [PTR]          | 6      | 1 | Pop to 16-bit pointer [0 to 3], low byte first      |

| PUSH/POP [PTR][TOS] | 6      | 1 | EA = (16-bit pointer) + TOS                         |

| PUSH/POP [PTR][D]   | 7      | 2 | EA = (16-bit pointer) + displacement [0 to 255]     |

| PUSH/POP absolute   | 7      | 3 | Absolute memory address                             |

| IN/OUT              | 7 + 4n | 1 | Fast I/O instruction, transfer <i>n</i> bytes       |

**Table 2.5 ALU Instructions**

| Mnemonic                | Cycles | Size (bytes) | Operation                                            |

|-------------------------|--------|--------------|------------------------------------------------------|

| INC/DEC/NOT             | 2      | 1            | Increment/decrement/negate TOS                       |

| ROLC/RORC               | 2      | 1            | Rotate left/right TOS through carry                  |

| SHL/SHR                 | 2      | 1            | Unsigned left/right shift TOS, clear carry           |

| SHLA/SHRA               | 2      | 1            | Signed left/right shift TOS into carry               |

| ADD/AND/OR/XOR/ADC      | 4      | 1            | Operate with NEXT on TOS, drop NEXT                  |

| ADD/AND/OR/XOR #literal | 3      | 2            | Operate with literal on TOS                          |

| (ADD/AND/OR/XOR)_R      | 7      | 1            | Operate with NEXT on TOS, drop NEXT and return       |

| ALLOC #literal          | 3      | 1            | Add [1 to 8] to data stack pointer                   |

| DEALLOC_R #literal      | 6      | 1            | Subtract [1 to 8] from data stack pointer and return |

| SUB NEXT,TOS            | 4      | 1            | TOS = NEXT - TOS, drop NEXT                          |

| SBC NEXT, TOS           | 4      | 1            | TOS = NEXT - TOS - carry, drop NEXT                  |

| SUB TOS,NEXT            | 4      | 1            | TOS = TOS - NEXT, drop NEXT                          |

| ХСН                     | 4      | 1            | Exchange TOS and NEXT                                |

| INC [PTR]               | 6      | 1            | Increment 16-bit pointer [0 to 3]                    |

## **Memory**

#### **Memory Allocation Overview**

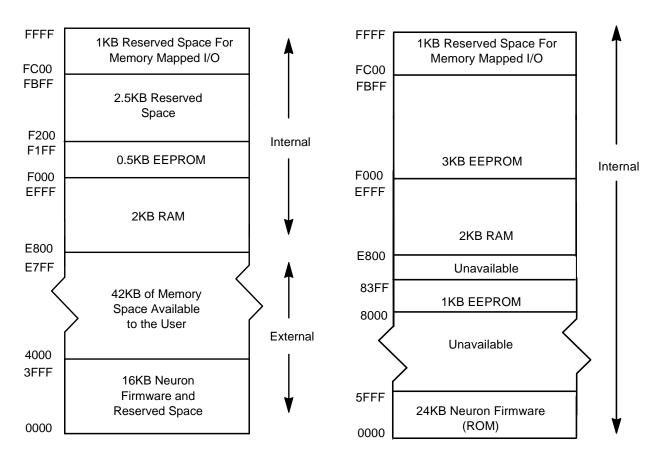

#### PL 3150 Smart Transceiver Memory Allocation

See Figure 2.5 for a memory map of the PL 3150 Smart Transceiver.

- 512 bytes of in-circuit programmable EEPROM that store the following:

- Network configuration and addressing information.

- Unique 48-bit Neuron ID written at the factory.

- User-written application code and read-mostly data. See Table 2.6 for available EEPROM space.

- 2,048 bytes of static RAM that store the following:

- Stack segment, application, and system data.

- Network and application buffers.

- The processor can access 59,392 bytes of the available 65,536 bytes of memory address space via the external memory interface. The remaining 6,144 bytes of the memory address space are mapped internally.

- 16,384 bytes of the external memory (59,392 bytes total) are required to store the following:

- The Neuron firmware, including the system firmware executed by the MAC and Network processors, and the executive supporting the application program.

- The rest of the external memory (43,008 bytes) is available for:

- User-written application code.

- Additional application read/write and non-volatile data.

- Additional network buffers and application buffers.

#### PL 3120/PL 3170 Smart Transceiver Memory Allocation

See Figure 2.6 for a memory map of the PL 3120 and PL 3170 Smart Transceivers.

- 4,096 bytes of in-circuit programmable EEPROM that store:

- Network configuration and addressing information.

- Unique 48-bit Neuron ID written at the factory.

- User-written application code and read-mostly data.

- 2,048 bytes of static RAM that store the following:

- Stack segment, application, and system data.

- Network buffers and application buffers.

- 24,576 bytes of ROM that store the following:

- The Neuron firmware, including the system firmware executed by the MAC and network processors, the executive supporting the application program, ISI library (PL 3170 only), and application libraries.

Figure 2.5 PL 3150 Smart Transceiver Memory Map

Figure 2.6 PL 3120/PL 3170 Smart Transceiver Memory Map

#### **EEPROM**

All three versions of the PL Smart Transceiver have internal EEPROM containing:

- Network configuration and addressing information.

- Unique 48-bit Neuron ID.

- Optional user-written application code and data tables.

All but 8 bytes of the EEPROM can be written under program control using an on-chip charge pump to generate the required programming voltage. The charge pump operation is transparent to the user. The remaining 8 bytes are written during manufacture, and contain a unique 48-bit identifier for each part called the *Neuron ID*, plus 16 bits for the chip manufacturer's device code. Each byte in the EEPROM region can be written up to 10,000 times. For all PL Smart Transceivers, the EEPROM stores the installation-specific information such as network addresses and communications parameters. For the PL 3120 and PL 3170 Smart Transceivers, the EEPROM also stores the application program generated by the NodeBuilder or Mini EVK tool. The application code for the PL 3150 Smart Transceiver can be stored either on-chip in the EEPROM memory or off-chip in external memory depending on the size of the application code. See Table 2.6 for available EEPROM space.

For all write operations to the internal EEPROM, the Neuron firmware automatically compares the value in the EEPROM location with the value to be written. If the two are the same, the write operation is not performed. This prevents unnecessary write cycles to the EEPROM, and reduces the average EEPROM write cycle latency.

#### Chapter 2 - Hardware Resources

When the PL Smart Transceiver is not within the specified power supply voltage range, a pending or on-going EEPROM write is not guaranteed. The PL Smart Transceiver contains a built-in low-voltage interruption (LVI) circuit that holds the chip in reset when V<sub>DD5</sub> is below a certain voltage. See the *PL 3120/ PL 3150 or PL 3170 Smart Transceiver Datasheets* for LVI trip points. This reduces the risk of EEPROM data corruption. For PL 3150 Smart Transceiver devices with external flash memory an external pulse stretching LVI is required. See *RESET Pin* for more information on LVI circuitry.

In the event of a fault, the on-chip EEPROM of the PL 3150 Smart Transceiver can be reset to its factory default state by executing the EEBLANK program. To do so, program the appropriate EEBLANK file into an external memory device, temporarily replace the application's external ROM or flash with the chip that has EEBLANK loaded, and power up the device. The EEBLANK files are named eeb<n>.nri where <n> is the Neuron input clock rate in kHz and is one of the following: 20000, 10000, 05000, 02500, 01250, or 00625. If you are using an input clock between two of these speeds, select the next slower version of EEBLANK.

After around 20 seconds (or less depending on clock speed), the device's service LED should come on solid, indicating that the EEPROM has been blanked. Then replace the original application ROM or flash. The EEBLANK files are distributed with NodeBuilder 3.1 and Mini EVK Evaluation Kit software. Versions of EEBLANK distributed with prior releases of the LonBuilder<sup>®</sup> and NodeBuilder tools should not be used with the PL 3150 Smart Transceiver.

The  $set\_eeprom\_lock()$  function can also be used for additional protection against accidental EEPROM data corruption. This function allows the application program to set the state of the lock on the checksummed portion of the EEPROM. Refer to the *Neuron C Reference Guide* for more information.

The internal EEPROM of a PL Smart Transceiver will contain a fixed amount of overhead and a network image (configuration), in addition to user code and user data. The following table shows the maximum amount of EEPROM space available for user code and user data assuming a minimally-sized network image. Also shown is the minimum segment size for user data. Constant data is assumed to be part of the code space.

**Table 2.6 Memory Usage**

| Tuble 210 Michief Chage   |                  |                         |                         |  |  |

|---------------------------|------------------|-------------------------|-------------------------|--|--|

| Device                    | Firmware Version | EEPROM Space<br>(Bytes) | Segment Size<br>(Bytes) |  |  |

| PL 3120 Smart Transceiver | 14               | 3969                    | 8                       |  |  |

| PL 3170 Smart Transceiver | 17               | 3964                    | 8                       |  |  |

| PL 3150 Smart Transceiver | 14 or newer      | 384                     | 2                       |  |  |

EEPROM must be allocated in increments of the device's segment size, the smallest unit of EEPROM that can be allocated for variable space. For example, if there are three 3-byte variables used, there must be 9 bytes of variable space. For a PL 3120 or PL 3170 Smart Transceivers, this would result in the allocation of 16 bytes for variable space, as 16 bytes is the lowest increment of the device segment size (8 bytes) that can store the three 3-byte variables. For a PL 3150 Smart Transceiver, this would result in the allocation of 10 bytes for variable space, as 10 bytes is the lowest increment of the device segment size (2 bytes) that can store the three 3-byte variables.

#### Static RAM

The PL Smart Transceivers contain 2048 bytes of static RAM.

The RAM is used to store the following:

- Stack segment, application, and system data

- Network buffers and application buffers

The RAM state is retained as long as power is applied to the device. After reset, releasing the PL Smart Transceiver initialization sequence will clear the RAM (see the section *Reset Processes and Timing* for more information).

#### **Pre-programmed ROM**

The PL 3120 and PL 3170 Smart Transceivers contain 24,576 bytes of pre-programmed ROM. This memory contains the Neuron firmware, including the LonTalk protocol stack, real time task scheduler, and system function libraries. The Neuron firmware for the PL 3150 Smart Transceiver is stored in external memory. The Neuron firmware is supplied with the NodeBuilder and Mini EVK tools.

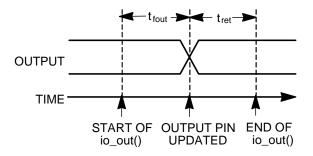

#### PL 3150 Smart Transceiver External Memory Interface

The external memory interface of the PL 3150 Smart Transceiver (the PL 3120 and PL 3170 Smart Transceivers have no external memory interface) supports up to 42K Bytes of external memory for additional user program and data. The total address space is 64K Bytes. However, the upper 6k of address space is reserved for internal RAM, EEPROM, and memory-mapped I/O (see Figures 2.5 and 2.6), leaving 58K Bytes of external address space. Of this space, 16K Bytes is used by the Neuron firmware. The external memory space can be populated with RAM, ROM, PROM, EPROM, EEPROM, or flash memory in increments of 256 bytes. The memory map for the PL 3150 Smart Transceiver is shown in Figure 2.5. The bus has 8 bidirectional data lines and 16 address lines driven by the processor. Two interface lines (R/W~ and E~) are used for external memory access. Refer to the *PL 3150 Smart Transceiver Datasheet* for the required access times for the external memory used. The input clock rates supported by the PL 3150 Smart Transceiver are 10MHz and 6.5536MHz. The Enable Clock (E~) runs at the system clock rate, which is one-half the input clock rate. All memory, both internal and external, can be accessed by any of the three processors at the appropriate phase of the instruction cycle. Because the instruction cycles of the three processors are offset by one-third of a cycle with respect to each other, the memory bus is used by only one processor at a time.

The Neuron 3150 Chip External Memory Interface engineering bulletin provides guidelines for interfacing the PL 3150 Smart Transceiver to different types of memory. A minimum hardware configuration would use one external ROM (PROM or EPROM), containing both the Neuron firmware and user application code. This configuration would **not** allow the system engineer to change the application code over the network after installation. The network image (network address and connection information) however, could be altered because this information resides in internal EE-PROM. If application downloads over the network are a requirement for maintenance or upgrade and the application code will not fit into the internal EE-PROM, then external EE-PROM or flash will be necessary. Refer to the Neuron C Programmer's Guide for guidelines to reduce code size.

The pins used to interface with external memory are listed in Table 2.7. The  $E\sim$  clock signal is used to generate read (or write) signals to external memory. The A15 (address line 15) or a programmable array logic (PAL) decoded signal gated with R/W $\sim$  can be used to generate read signals to external memory.

**Table 2.7 External Memory Interface Pins**

| Pin<br>Designation | Direction    | Function              |

|--------------------|--------------|-----------------------|

| A0 - A15           | Output       | Address Pins          |

| D0 - D7            | Input/Output | Data Pins             |

| Е                  | Output       | Enable Clock          |

| R/W                | output       | Read/Write Select Low |

The PL Smart Transceiver can be interfaced to another MPU through the 12 I/O pins using a serial or parallel connection, or through a dual-ported RAM device such as the Cypress CY7C144, CY7C138, or CY7C1342. There are pre-defined serial and parallel I/O models for this purpose which are easily implemented. Use the Neuron C programming language, ShortStack firmware, or MIP firmware to simplify the interface. For more details of dual-ported RAM interfacing, see Appendix B of the *LonWorks Microprocessor Interface Program User's Guide* (Echelon 078-0017-01).

## Input/Output

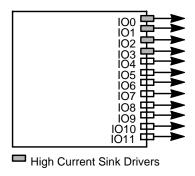

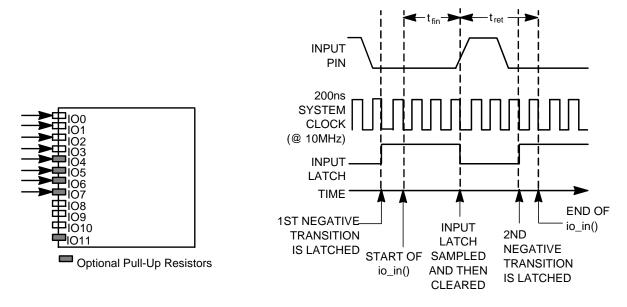

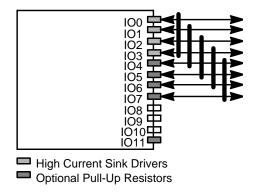

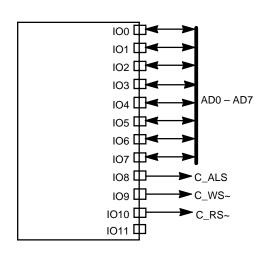

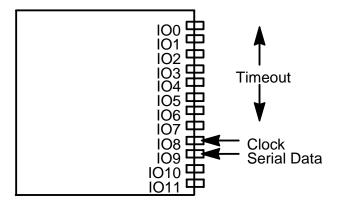

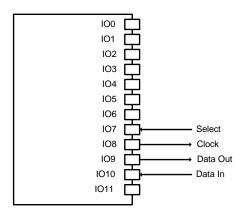

#### Twelve Bidirectional I/O Pins

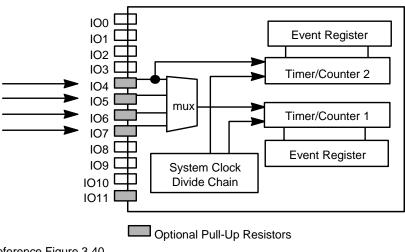

These pins are usable in several different configurations to provide flexible interfacing to external hardware and access to the internal timer/counters. The logic level of the output pins can be read back by the application processor.

Pins IO4 – IO7 and IO11 have programmable pull-up current sources. They are enabled or disabled with a compiler directive (see the *Neuron C Reference Guide*). Pins IO0 – IO3 have high current sink capability (20 mA @ 0.8 V). The others have sink capability of 1.4 mA @ 0.5 V. All pins (IO0 – IO11) have TTL level inputs with hysteresis. Pins IO0 – IO7 also have low level detect latches.

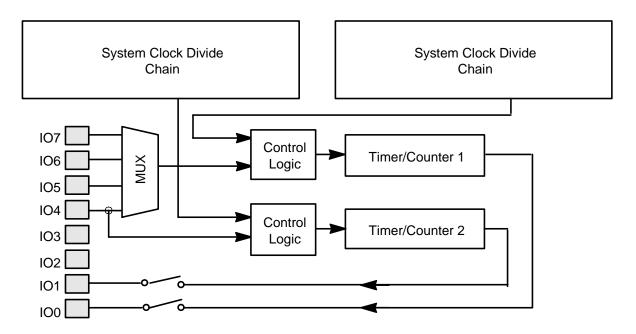

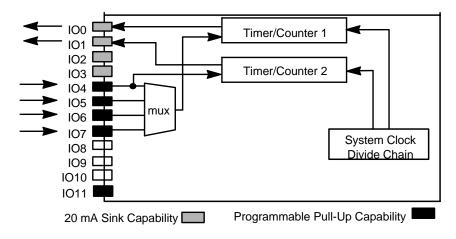

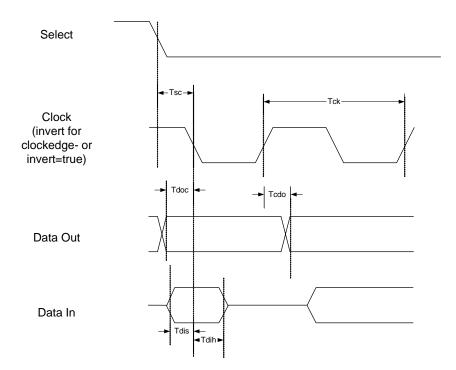

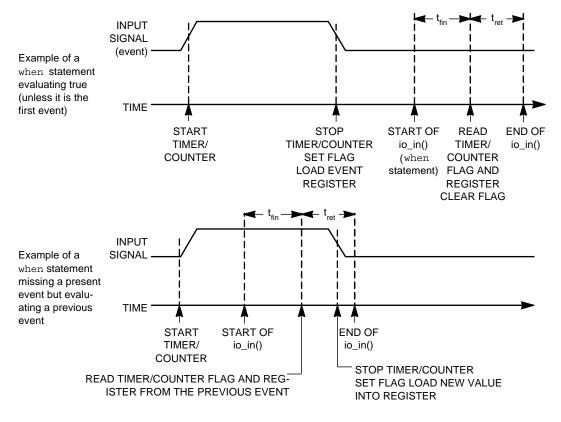

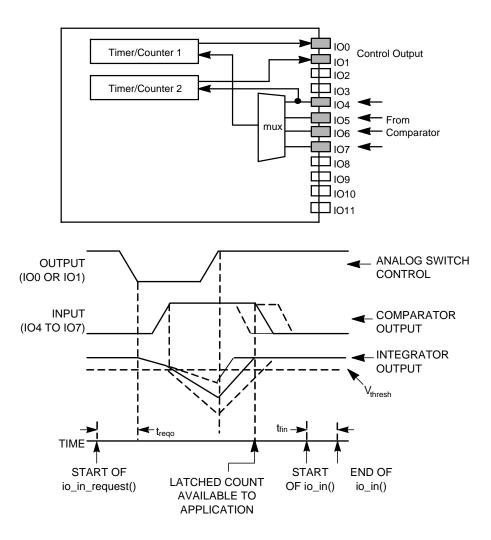

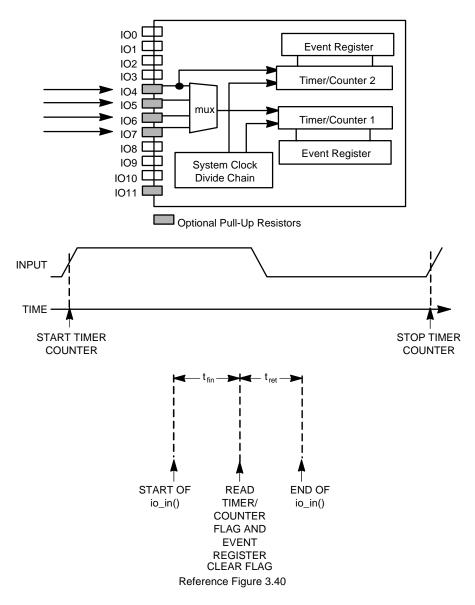

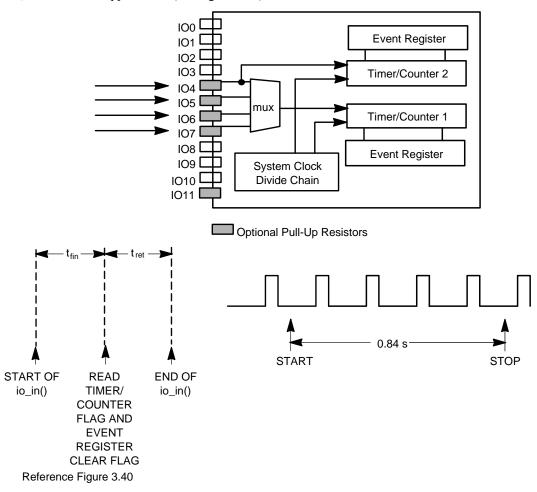

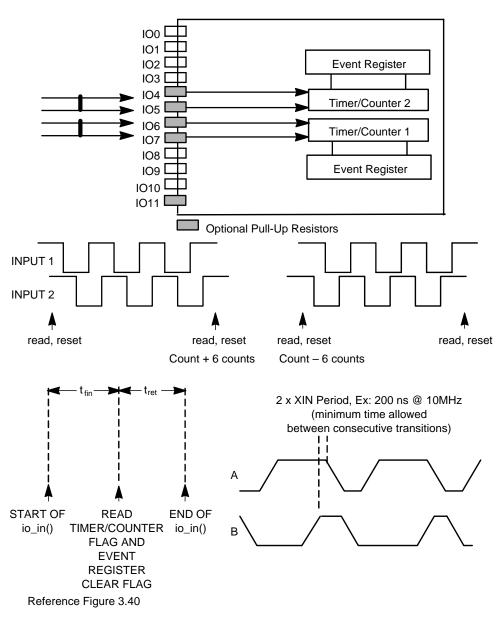

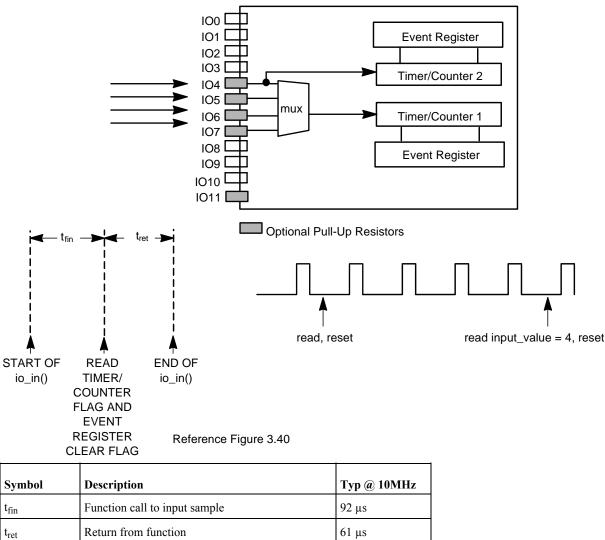

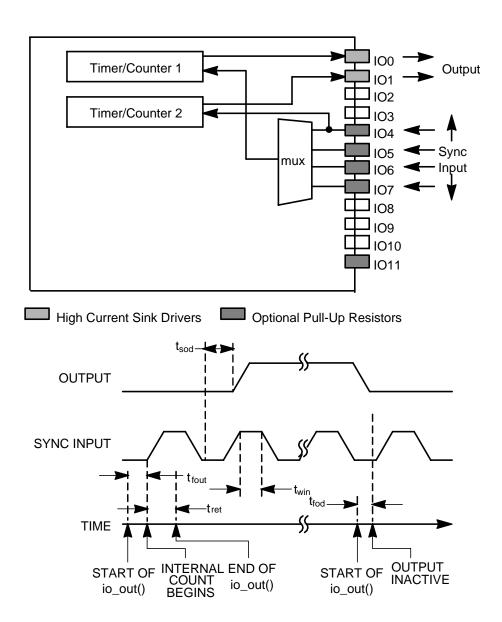

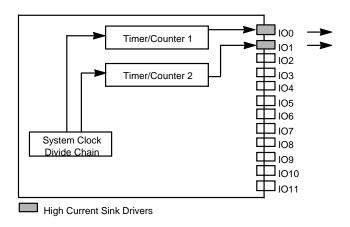

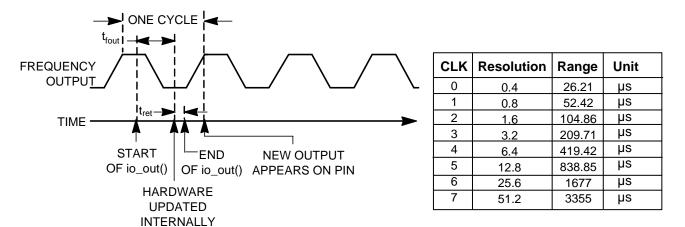

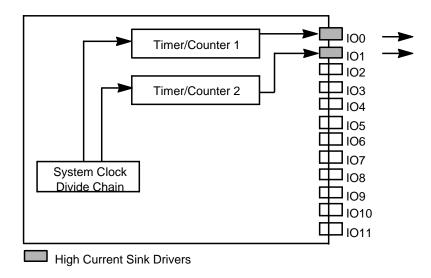

#### **Two 16-Bit Timer/Counters**

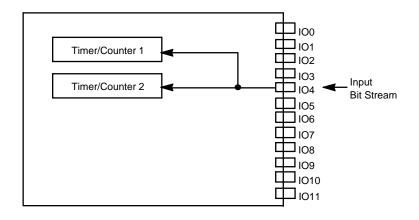

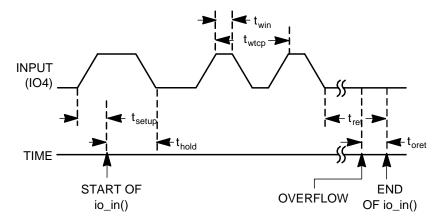

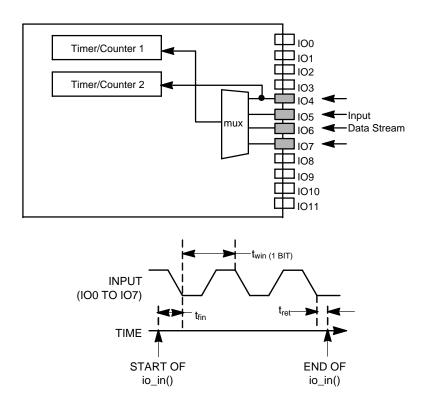

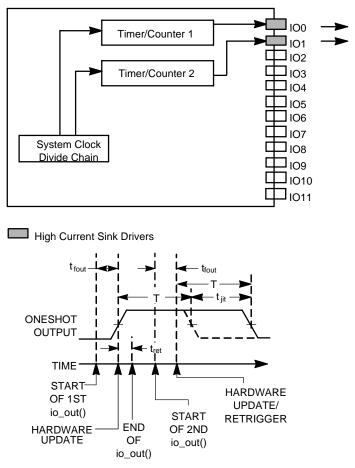

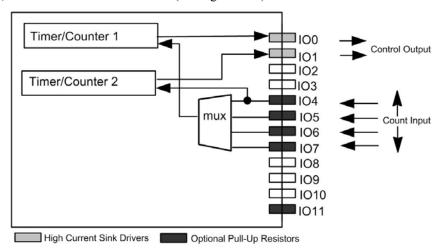

The timer/counters are implemented as a load register writable by the processor, a 16-bit counter, and a latch readable by the processor. The 16-bit registers are accessed 1 byte at a time. The PL Smart Transceivers have one timer/counter whose input is selectable among pins IO4 – IO7, and whose output is pin IO0, and a second timer/counter with input from pin IO4 and output to pin IO1 (Figure 2.7). No I/O pins are dedicated to timer/counter functions. If, for example, Timer/Counter 1 is used for input signals only, then IO0 is available for other input or output functions. Timer/counter clock and enable inputs can be from external pins, or from scaled clocks derived from the system clock; the clock rates of the two timer/counters are independent of each other. External clock actions occur optionally on the rising edge, the falling edge, or both rising and falling edges of the input.

Figure 2.7 Timer/Counter Circuits

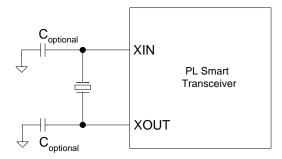

## **Clock Input**

The PL Smart Transceiver requires a 10.0000MHz clock signal for C-band operation and a 6.5536MHz signal for A-band operation. This clock can be provided by connecting an appropriate parallel resonant crystal to the XIN and XOUT pins of the PL Smart Transceiver as shown in Figure 2.8.

The Smart Transceiver IC includes on-chip crystal load capacitors. If a crystal is chosen with a load capacitance rating that matches the capacitance provided by the combination of the PL Smart Transceiver IC and the XIN and XOUT circuit traces, then off-chip load capacitors are not needed. If the developer prefers to use a crystal with a different load capacitance rating, then each reference layout for the PL smart Transceiver includes provision for optional off-chip capacitors to tune the design to match different crystals (see Appendix A for a list of reference designs). The schematic for each reference design includes a table listing crystal and load capacitance options. These tables cover crystal load capacitance values ranging from 15 to 20pF.

Crystals with load capacitance ratings greater than 20pF should not be used with PL Smart Transceiver chips. Even though the optional off-chip capacitors would allow centering the frequency of oscillation, using more than 20pF of load capacitance could prevent the oscillator from starting under worst-case conditions. To further ensure proper oscillator startup, the ESR specification for the crystal should be  $\leq 60\Omega$  for C-band operation and  $\leq 100\Omega$  for A-band use.

Figure 2.8 PL 3120, PL 3150, PL 3170 Smart Transceiver crystal clock connections

The PL Smart Transceiver requires a clock frequency accuracy of ±200ppm over the full range of component tolerances and operating conditions. Variation within the PL Smart Transceiver IC uses a portion of the overall ±200ppm budget. The remaining portion of the error budget allocated for *total crystal uncertainty* is ±85ppm (assuming that the selected crystal has a load capacitance specification which matches the circuit loading as described above). *Total crystal uncertainty* is the combination of the crystal's initial frequency tolerance plus its temperature and aging tolerances. Note that a typical crystal aging specification is 5ppm/yr but, since the aging effect tends to follow a logarithmic curve, aging over a 10 year span is commonly in the range of 10 to 15ppm (contact individual crystal vendors for detailed specifications regarding their particular products).

If the load capacitance specification of the crystal is not matched to the circuit design then the nominal frequency will not match the design center and the error budget for the crystal will be reduced. For example, using a 20pF crystal in a circuit designed to provide 18pF of loading results in about a 40ppm upward shift in the nominal frequency of oscillation. Thus a 2pF mismatch consumes nearly half of one side of the error budget. The resulting error budget for the crystal in this particular example would be +45/-125ppm. This example points out the importance of directly copying the selected reference layout so that differences in trace capacitance do not pull the nominal frequency away from the design center.

If a 10.0000MHz clock signal is already available elsewhere on a C-band circuit board (6.5536MHz for an A-band board) then it can be used as a clock source for the PL Smart Transceiver as long as the clock signal meets several requirements. First the clock must have an accuracy of  $\pm 200$ ppm over all operating conditions. Its duty cycle symmetry must be no worse than 60/40% when connected to a 33pF load and measured using a 0.9V threshold. In addition the voltage swing of the clock signal must be within the GND and  $V_{DDS}$  supply rails of the PL Smart Transceiver. To use this clock option, the appropriate clock signal should be connected to the XIN pin of the PL Smart Transceiver and the XOUT pin of the PL Smart Transceiver should be left open. Note also that appropriate high frequency clock distribution techniques must be used to ensure that a clean clock signal is present at the XIN pin of the PL Smart Transceiver.

The accuracy of any clock oscillator should be checked during the design verification phase of every PL Smart Transceiver based product. This measurement must be made without adding any capacitance to either the XIN or XOUT pins of the PL Smart Transceiver. Holding a probe near but not touching the clock lines and then connecting this probe to a spectrum analyzer with an accurate time-base provides one way to make this measurement without affecting the frequency of oscillation.

# Band-In-Use (BIU) and Packet Detect (PKD) LED Connections

The PL Smart Transceiver supplies two output signals, PKD and BIU, that are intended to drive low-current light-emitting diodes (LEDs). Both signals are active-high and must be connected to separate LEDs, with series current-limiting resistors added between the LEDs and ground. The PKD and BIU pins are rated to source up to 12mA.

A Band-In-Use detector, as defined under CENELEC EN 50065-1, must be active whenever a signal that exceeds  $86dB\mu V_{RMS}$  anywhere in the frequency range 131.5kHz to 133.5kHz is present for at least 4ms. The Band-In-Use detector is defined by CENELEC EN 50065-1 as part of the CENELEC access protocol. The Smart Transceiver incorporates the CENELEC access protocol, and the PL Smart Transceiver can be programmed to enable or disable its operation (See the *CENELEC Access Protocol* section in Chapter 8). When the PL Smart Transceiver is programmed to enable the CENELEC access protocol the state of the Band-in-Use signal regulates the flow of packet transmissions in accordance with CENECLEC-defined conditions. When the CENELEC access protocol is disabled, an active BIU signal has no affect on PL Smart Transceiver transmissions

The Band-In-Use function is defined for use in the CENELEC C-band and is not required for A-band operation. When the PL Smart Transceiver is programmed with proper A-band transceiver parameters, as described in Chapter 8, an active BIU signal does not prevent the PL Smart Transceiver from transmitting.

The PKD signal is active whenever a LonTalk packet addressed to any device is being received by the PL Smart Transceiver. The receive sensitivity of the transceiver is considerably greater than that of the BIU indicator. The PKD signal will go active when the PL Smart Transceiver receives packets whose signal level is as small as  $36dB\mu V_{RMS}$ . Thus it is not uncommon for the PKD indicator to signal that a packet is present without the BIU indicator turning on; this occurs in cases where the signal strength of a received packet is less than the BIU threshold.

ESD protection diodes should be connected to the BIU and PKD lines in applications where BIU and PKD drive LEDs that could be subject to ESD exceeding 2kV. Refer to the *Design for Electrostatic Discharge Compliance* section of Chapter 6 for recommendations regarding ESD protection.

## **TXON Output Signal**

TXON is a buffered version of the internal signal used to control the transceiver's transmit amplifier. The TXON output pin is active high while the PL Smart Transceiver is transmitting packets. This pin is rated to source up to 12mA. TXON can be used to drive a low-current LED to indicate transmit activity. A series current-limiting resistor is required between the LED and ground. ESD protection diodes should be connected to this pin in applications where the TXON signal line could be subjected to ESD exceeding 2kV.

#### **Additional Functions**

#### **Reset Function**

The reset function is a critical operation in any embedded microcontroller. In the case of the PL Smart Transceiver, the reset function plays a key role in the following conditions:

- Initial V<sub>DD5</sub> power up (reset ensures proper initialization of the PL Smart Transceiver during power up).

- V<sub>DD5</sub> power down (reset ensures proper shut down of the PL Smart Transceiver).

- Fluctuations in the V<sub>DD5</sub> supply voltage (reset manages proper recovery of PL Smart Transceiver state after V<sub>DD5</sub> stabilizes).

- Program recovery (if an application gets lost due to corruption of address or data the Smart Transceiver's watchdog timer initiates a watchdog reset event).

- Protecting the internal EEPROM of a PL 3120 or PL 3170 Smart Transceiver from corruption (an internal LVI insures that the transceiver is held in reset when the  $V_{DD5}$  supply is below a level that is safe for the EE activity).

The PL Smart Transceivers have four mechanisms to initiate a reset:

- RESET~ pin pulled low and then returned high.

- Software command either from the application program or from the network.

- Low-Voltage Indicator (LVI) detects a drop in the power supply below a set level.

- Watchdog timeout occurs during application execution (the timeout period is 840ms at 10MHz; this figure scales inversely with clock frequency).

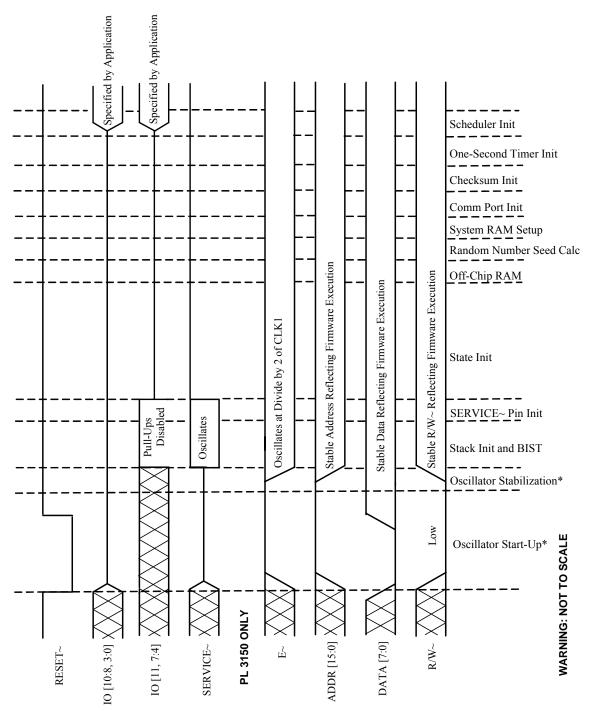

When in reset, the pins of the PL Smart Transceiver go to the states described in the list below. Figure 2.10 shows the state of the pins during reset and the initialization sequence just after reset.

- Oscillator continues to run

- All processor functions stop

- SERVICE~ pin goes to high impedance (except for pull-up current source)

- I/O pins go to high impedance

- Address pins go to 0xFFFF (PL 3150 Smart Transceiver only)

- All data pins become outputs with low states (PL 3150 Smart Transceiver only)

- E~ clock goes high (PL 3150 Smart Transceiver only)

- R/W~ goes low (PL 3150 Smart Transceiver only)

When the RESET~ pin is released back to a high state, the PL Smart Transceiver begins its initialization procedure starting at address 0x0001. The time it takes the PL Smart Transceiver to complete its initialization differs between PL Smart Transceivers, the different firmware versions that are being run, and the memory space used by the application (code and data). This will be discussed later in this section.

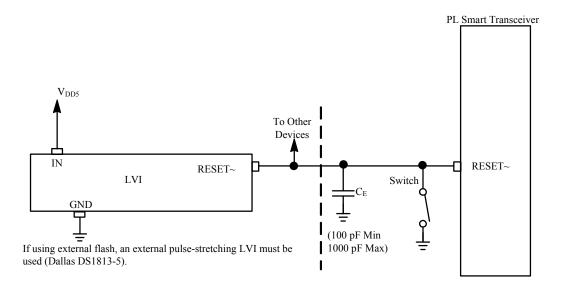

#### **RESET~ Pin**

The RESET~ pin is both an input and an output. The RESET~ pin includes an internal current source that acts as a pull-up resistor. The RESET~ pin acts an output when any of the following events occur:

- The Smart Transceiver's internal low-voltage indicator (LVI) detects a low voltage condition

- The Smart Transceiver's software program initiates a reset event

- The Smart Transceiver's Watchdog Timer times out

In some cases it is desirable to use the input capability of RESET~ pin to allow other devices to reset the Smart Transceiver. Examples of external devices that may be used for this purpose include push button switches, microcontrollers, and external low-voltage detectors.

**WARNING:** If the proper external reset circuitry is not used, the PL Smart Transceiver can go "applicationless" or unconfigured. The applicationless or unconfigured state occurs when the checksum error verification routine detects corruption in memory which could have falsely been detected due to an improper reset sequence.

The following guidelines must be followed in order for the transceiver's reset functions to operate reliably:

- Any device connected to the RESET~ pin must have an open-drain (or equivalent) output. If an external device were to actively drive the RESET~ pin high, contention between that device and the Smart Transceiver's internal circuitry could result in anomalous behavior ranging from "applicationless" errors to device failure.

- If any external devices are connected to the RESET~ pin of the Smart Transceiver then a capacitor should be connected between RESET~ and ground in order to provide noise immunity. The value of this capacitor should be at least 100pF and must not exceed 1000pF. For even greater noise immunity, two capacitors (totaling ≤1000pF) can be used with one connected from the RESET~ pin to ground and the other from RESET~ to V<sub>DD5</sub>. These capacitors should be located within 15mm of the Smart Transceiver's RESET~ pin.

- During board level in-circuit testing (ICT) the RESET~ pin should be hard wired to ground via a "pogo pin". The PL Smart Transceiver is sensitive to disruptions in on the RESET~ pin during the time it is performing its initial (one time) boot initialization sequence. For in-circuit test purposes a single test point with a trace of ≤2cm to the RESET~ pin is recommended.

- When using an external oscillator to drive the XIN pin of the PL Smart Transceiver, a power-on-pulsestretching LVI with a delay ≥10ms is recommended in order to ensure that the external oscillator has stabilized before the PL Smart Transceiver is released from reset.

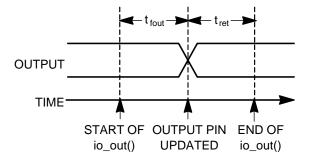

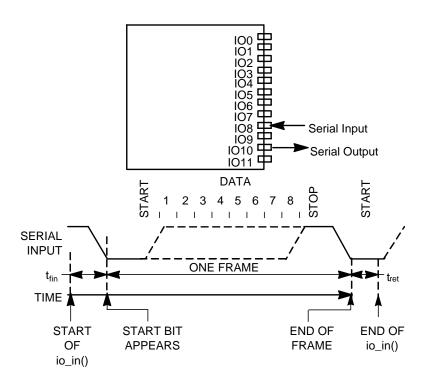

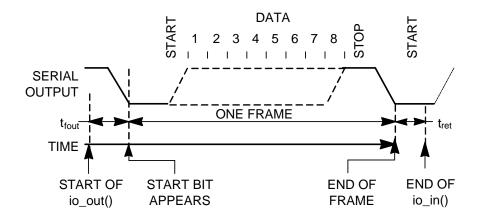

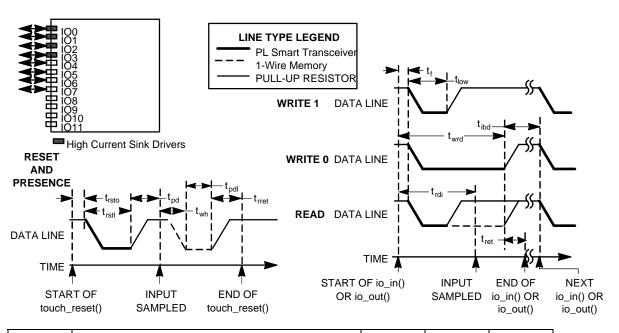

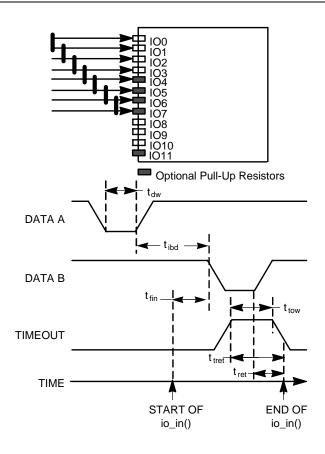

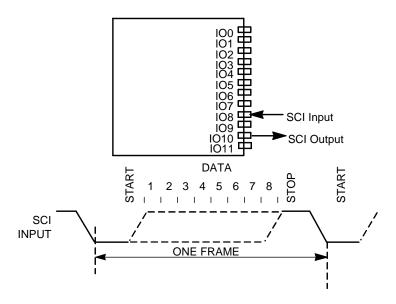

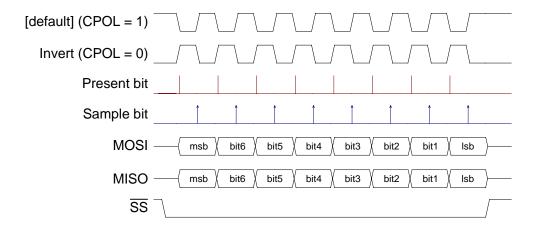

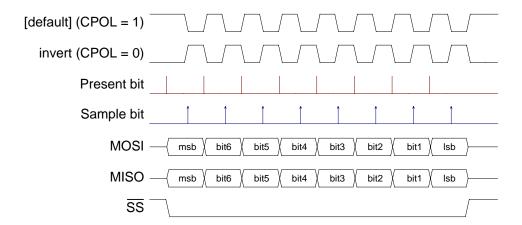

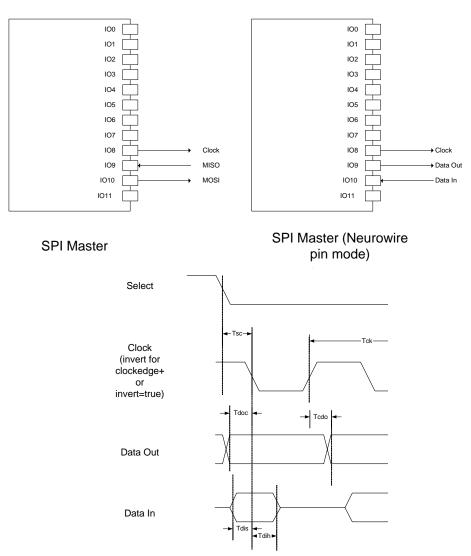

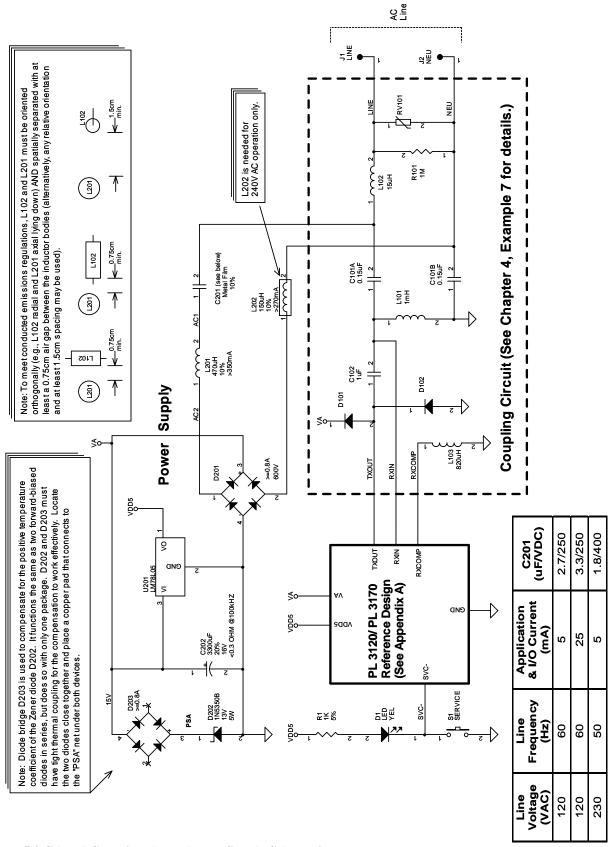

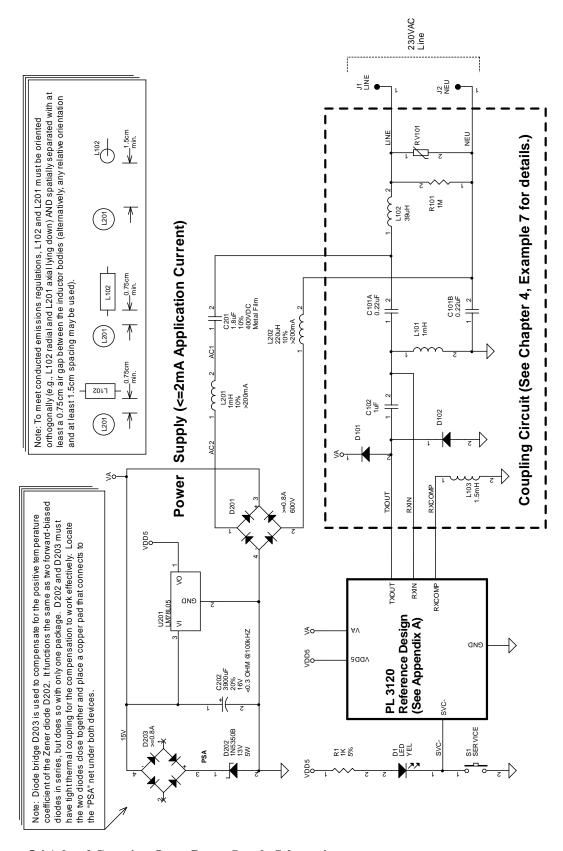

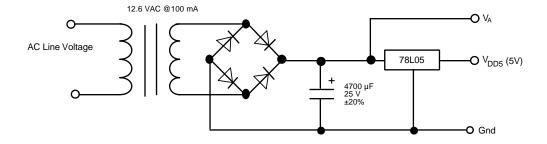

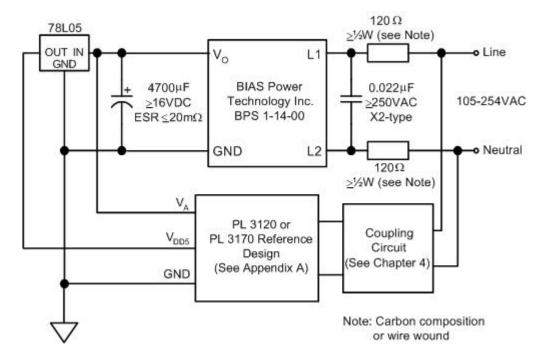

- A PL 3150 Smart Transceiver-based device must use an external pulse stretching LVI. This device must not