# USB3.1 Gen1 Peripheral Controller IP Core SUPERSPEED uu3pcss/uu3pcssaxi

## **Overview**

The Renesas USB3.1 Gen1 Peripheral Controller IP is compliant with the Universal Serial Bus (USB) 3.1 Specification and enables connectivity to USB3.1 system with proven design experiences.

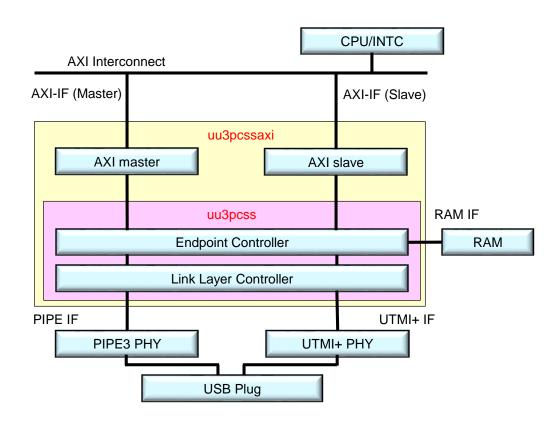

This core contains Endpoint Controller and has AXI bus bridge. This IP supports Super Speed (5 Gbps), High Speed (480 Mbps) and Full Speed (12Mbps).

## **Key Features**

## General

- Compliant with Universal Serial Bus 3.1 Specification Revision 1.0

- Compliant with PIPE3(PHY Interface for the PCI Express and USB3.0 Super Speed Architectures) Version 3.0

- Compliant with AMBA® AXI Protocol v1.0 Specification

## **USB3.1 function**

- 5Gbps USB3.1 Super Speed transfer

- Compliant with PIPE3 (PHY Interface for the PCI Express and USB3.0 Super Speed) architecture (32bit@125MHz)

- Maximum of 30 PIPE (PIPE0 not included) can be used (configurable)

- Configurations provided below can be set for each PIPE

Endpoint Number: between0 and 15

Transfer Type: control (only PIPE0)/bulk/interrupt (\*isochronous is not supported) Max Burst Size: fixed to 1 for PIPE0 (control), between 1 and 16 (bulk) and between 1 and 3 (interrupt)

- Max Sequence Number: fixed to 31

- Stream ID control supported (UASP can be supported)

- Suspend/Resume function

- Power Management by sending/receiving of link commands is supported

- Remote Wakeup request can be transmitted

#### **AXI Master I/F**

Address Bus width :32 bit :64 bit Data Bus width Maximum Burst Length :16 burst Burst Size :1/2/4/8 byte

### **AXI Slave I/F**

Address Bus width :32 bit (valid address bus width: 10bit)

Data Bus width :64 bit Maximum Burst length :16 burst Burst Size :1/2/4 byte

## **Product Details**

#### **IP Core**

uu3pcss provides EPC (endpoint controller) function which supports USB3.1/USB2.0. uu3pcssaxi contains AXI-bridge function (as both of master and slave) and uu3pcss.

## uu3pcssaxi interface

uu3pcssaxi has AXI Master interface and Slave interface. The master interface is for transaction data handling, and the slave interface is for register interface. The master interface supports 32-bit address, 64-bit data bus width, 16bursts. The slave interface supports 32-bit address, 64-bit data bus width, 16bursts.

## PIPE interface

Supports 32-bit 125MHz PIPE3 interface for Super Speed PHY interface.

#### **UTMI+** interface

Supports UTMI+ level-3 interface for High / Full / Low speed interface.

#### **Related Products**

•uPD720230,uPD720231A: USB3.0 SATA Bridge