# RZ/T1 Group

Serial Flash Sample Program (SPIBSC)

R01AN3010EJ0140 Rev.1.40 Jun. 07, 2018

# Summary

This application note describes how to make settings for the SPI multi-I/O bus controller of an RZ/T1 group microcontroller.

## **Restrictions**

The following restriction applies to the sample program.

(1) Since this program is for the area in the serial flash memory, the other areas cannot be programmed or erased by this program.

# **Applicable Devices**

RZ/T1 Group

When applying the program covered in this application note to another microcontroller, modify the program according to the specifications for the target microcontroller and extensively evaluate the modified program.

# Table of Contents

| 1. | Speci                       | Specifications                                                                |    |  |  |

|----|-----------------------------|-------------------------------------------------------------------------------|----|--|--|

| 2. | Opera                       | ting Environment                                                              | 5  |  |  |

| 3. | . Related Application Notes |                                                                               |    |  |  |

| 4. | Description of Hardware     |                                                                               |    |  |  |

|    | 4.1                         | List of Pins                                                                  | 7  |  |  |

|    | 4.2                         | Reference Circuit                                                             | 8  |  |  |

| 5. | Descr                       | iption of Software                                                            | 9  |  |  |

|    | 5.1                         | Outline of Operation                                                          |    |  |  |

|    | 5.1.1                       | Project Settings                                                              | 10 |  |  |

|    | 5.1.2                       | Preparing to Run the Program                                                  | 11 |  |  |

|    | 5.2                         | Fixed-Width Integers                                                          | 12 |  |  |

|    | 5.3                         | Structures and Unions                                                         | 13 |  |  |

|    | 5.4                         | Constants                                                                     | 20 |  |  |

|    | 5.5                         | Variables                                                                     | 23 |  |  |

|    | 5.6                         | Functions                                                                     | 23 |  |  |

|    | 5.7                         | Details of Functions                                                          | 25 |  |  |

|    | 5.8                         | Flowcharts of the Sample Program Functions                                    | 32 |  |  |

|    | 5.8.1                       | SPIBSC Initial Settings Function                                              | 32 |  |  |

|    | 5.8.2                       | Main Function                                                                 | 33 |  |  |

|    | 5.9                         | Operation of the Sample Program                                               | 34 |  |  |

|    | 5.9.1                       | Demonstration Program                                                         | 34 |  |  |

|    | 5.9.2                       | Reading the Serial Flash Memory                                               | 35 |  |  |

|    | 5.9.3                       | Programming the Serial Flash Memory                                           | 36 |  |  |

|    | 5.9.4                       | Erasing the Serial Flash Memory                                               | 36 |  |  |

| 6. | Proce                       | Procedure for Switching SPIBSC Mode                                           |    |  |  |

|    | 6.1                         | Problems which May Arise Due to Branch Prediction and Speculative Execution   | 37 |  |  |

|    | 6.1.1                       | Access to ROM/RAM in Cortex-R4                                                | 37 |  |  |

|    | 6.1.2                       | Modes of the SPI Multi-I/O Bus Controller                                     | 37 |  |  |

|    | 6.2                         | Outline of Mode Switching                                                     | 37 |  |  |

|    | 6.2.1                       | Switching between Modes                                                       | 37 |  |  |

|    | 6.2.2                       | Outline of Procedure for Making Changes                                       | 37 |  |  |

| 7. | Applic                      | ation Examples                                                                | 38 |  |  |

|    | 7.1                         | Conditions for the Sample Program                                             | 38 |  |  |

|    | 7.2                         | Changing the Sample Program when the Serial Flash Memory is Not to be Changed | 38 |  |  |

|    | 7.3                         | Changing the Sample Program when the Serial Flash Memory is to be Changed     | 39 |  |  |

|    | 7.3.1                       | Changing the Read Command Waveforms                                           | 40 |  |  |

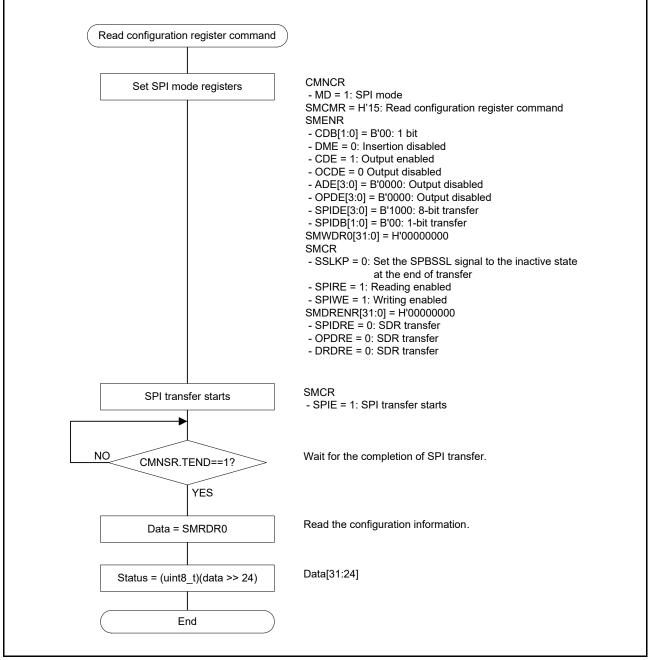

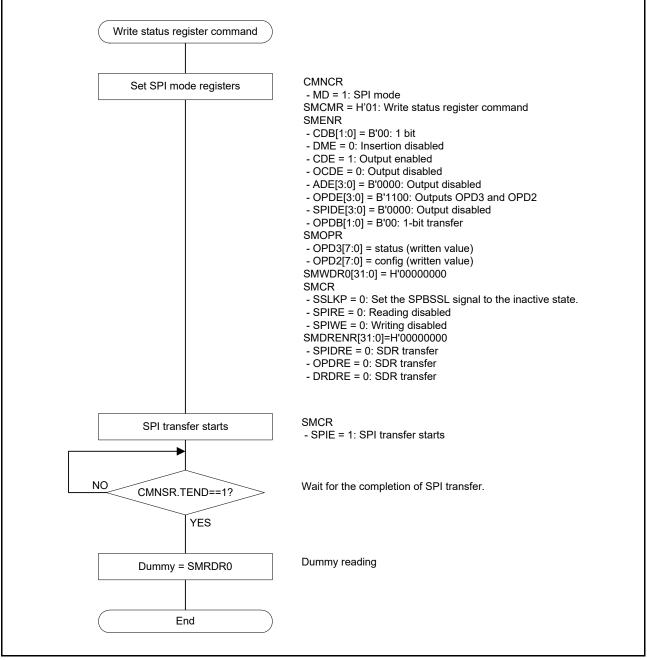

|    | 7.3.2                       | Setting Registers in the Serial Flash Memory                                  | 42 |  |  |

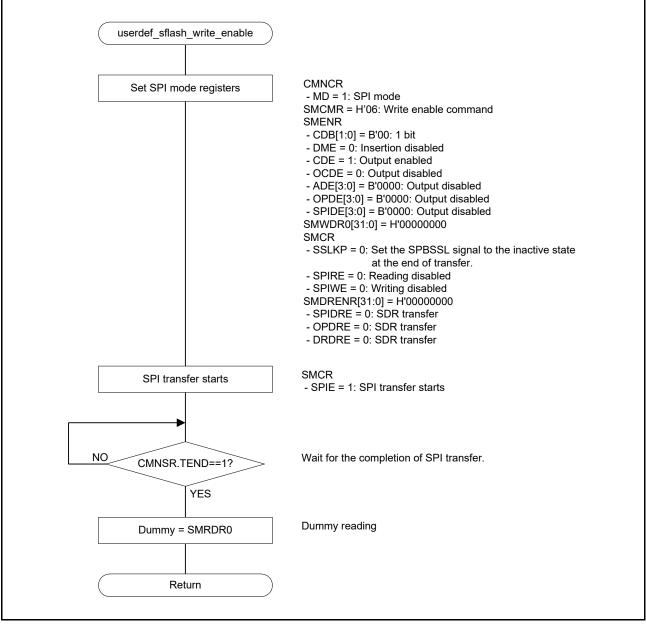

|    | 7.3.3                       | Enabling Writing to the Serial Flash Memory                                   | 47 |  |  |

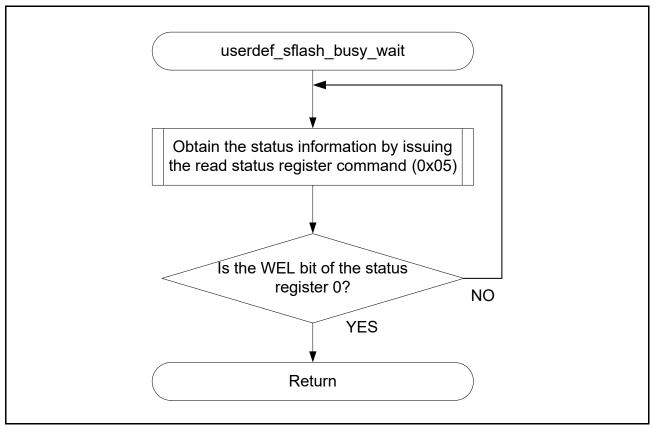

|    | 7.3.4                       | Waiting for the Serial Flash Memory to be Ready                               | 48 |  |  |

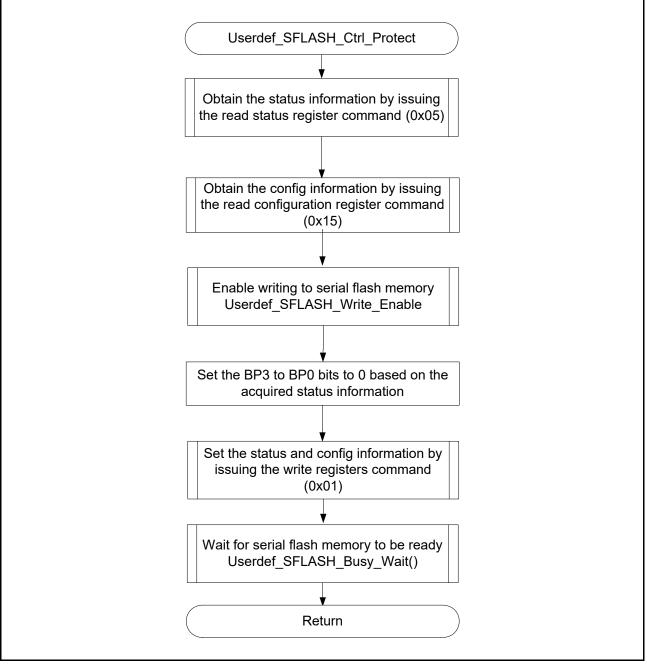

|    | 7.3.5                       | Reference: Releasing the Serial Flash Memory from Protection                  | 49 |  |  |

| 8. | Sample Program          | . 50 |

|----|-------------------------|------|

| 9. | Documents for Reference | . 51 |

# 1. Specifications

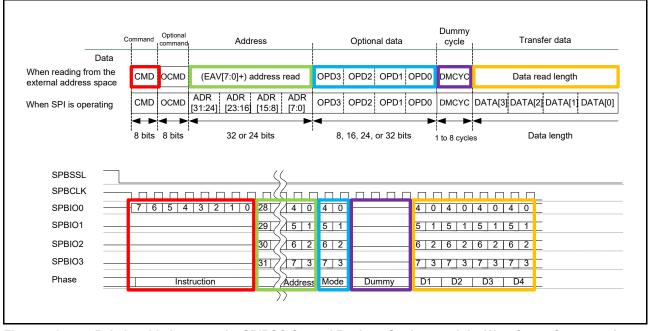

The SPI multi-I/O bus controller (SPIBSC) is a bus controller for the output of control signals to a serial flash memory connected to the SPI multi-I/O bus space (SPIBSC space). Making settings for the SPIBSC allows direct reading of the serial flash memory connected to the SPIBSC space and data transfer in SPI mode.

This application note describes how to make settings for the SPIBSC to read data directly from the SPIBSC space and how, in SPI mode, to make the settings for the registers of the serial flash memory which are required for access to the serial flash memory with a width of 4 bits.

Table 1.1 lists the peripheral modules used and their applications.

| Table 1.1 | Peripheral Modules and Their Applications |

|-----------|-------------------------------------------|

|-----------|-------------------------------------------|

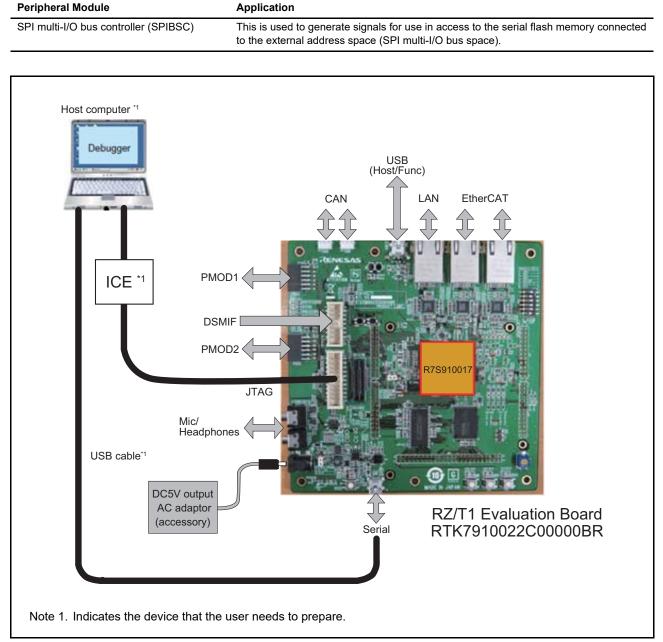

# 2. Operating Environment

The sample program covered in this application note is for the environment below.

## Table 2.1 Operating Environment

| Item                                                | Description                                                                                                                                                                                                                                                     |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MCU used                                            | RZ/T1 Group                                                                                                                                                                                                                                                     |  |

| Operating frequency                                 | CPU clock (CPUCLK): 450 MHz                                                                                                                                                                                                                                     |  |

| Operating voltage                                   | Power supply voltage (I/O): 3.3 V                                                                                                                                                                                                                               |  |

| Integrated development environment                  | <ul> <li>Embedded Workbench<sup>®</sup> for Arm Version 8.20.2 from IAR Systems</li> <li>Arm<sup>®</sup> Integrated Development Environment<br/>Arm Development Studio 5 (DS-5<sup>TM</sup>) Version 5.26.2</li> <li>Renesas e2studio Version: 6.1.0</li> </ul> |  |

| Operating mode                                      | SPI boot mode (serial flash memory)<br>16-bit bus boot mode (NOR flash memory)                                                                                                                                                                                  |  |

| Board used                                          | RZ/T1 evaluation board (RTK7910022C00000BR)                                                                                                                                                                                                                     |  |

| Devices used<br>(functions to be used on the board) | <ul> <li>Serial flash memory allocated to the SPI multi-I/O bus space (1- or 4-bit bus width)</li> <li>Manufacturer: Macronix International Co., Ltd.</li> <li>Product type name: MX25L51245G</li> </ul>                                                        |  |

# 3. Related Application Notes

The application note related to the descriptions in this application note is listed below. Also consult the following document along with this application note.

- RZ/T1 Group Initial Settings (R01AN2554EJ)

- Note: For registers not covered in this application note, the values set in the RZ/T1 Group Initial Settings application note are used without change.

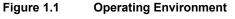

# 4. Description of Hardware

# 4.1 List of Pins

Table 4.1 lists the pins used and their functions.

## Table 4.1 Pins Used and Their Functions

| Pin Name            | I/O    | Description                                                                                      |  |

|---------------------|--------|--------------------------------------------------------------------------------------------------|--|

| SPBCLK              | Output | Clock output                                                                                     |  |

| SPBSSL              | Output | Slave select                                                                                     |  |

| SPBMO/SPBIO0        | I/O    | Master send data: data 0                                                                         |  |

| SPBMI/SPBIO1        | I/O    | Master input data: data 1                                                                        |  |

| SPBIO2              | I/O    | Data 2                                                                                           |  |

| SPBIO3              | I/O    | Data 3                                                                                           |  |

| MD2,<br>MD1,<br>MD0 | Input  | Selection of boot mode (set to SPI boot mode)<br>MD_BOOT2: "L"<br>MD_BOOT1: "L"<br>MD_BOOT0: "L" |  |

| RES#                | Input  | System reset signal                                                                              |  |

Note: The symbol # represents negative logic (or active low).

# 4.2 Reference Circuit

Figure 4.1 is a connection example.

# 5. Description of Software

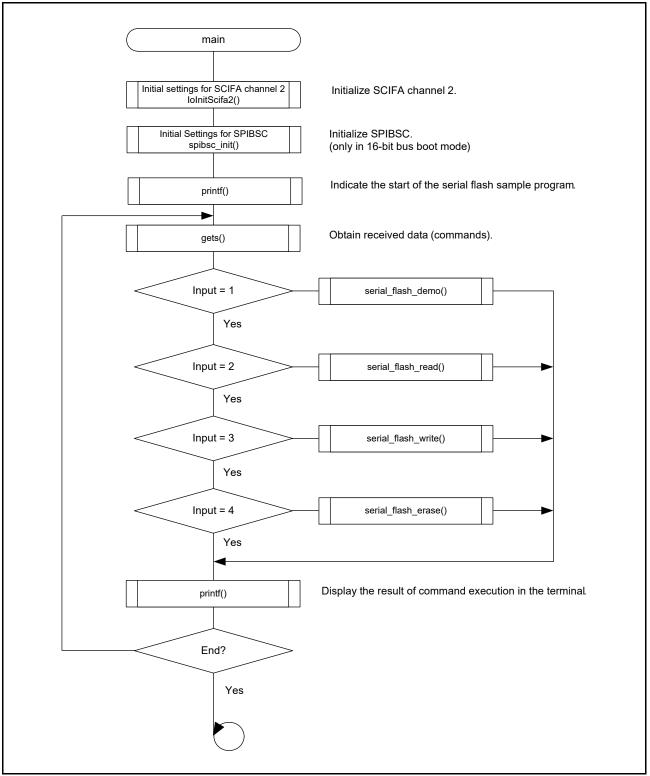

# 5.1 Outline of Operation

This section presents an outline of operation of the sample program.

When an RZ/T1 group microcontroller is booted up in SPI boot mode, it transfers the loader program in the serial flash memory connected to the SPIBSC space to the "B" tightly-coupled memory (BTCM) of the RZ/T1 group microcontroller and branches to the transferred loader program. Once execution branches to the loader program, the microcontroller can read data directly from the SPIBSC space. However, since the settings made for the SPIBSC are common to serial flash memory in general, you must make optimum settings for the SPIBSC to suit the given serial flash memory. For example, to read data at a high speed, you will need to make settings such as the setting for the read command to use 4 data pins. This sample program makes SPIBSC settings optimized for use with a Macronix serial flash memory (product type name: MX25L51245G).9

# 5.1.1 Project Settings

Project settings for use in the EWARM, DS-5, or e2studio as the development environment are described in the RZ/T1 Group Initial Settings application note.

Note: Since the sample program of the SPI boot version for the EWARM environment (RZ\_T1\_serialflash\_serial\_boot.eww) does not update the contents of rodata section when the serial flash memory is modified, the rodata section is placed in the "A" tightly-coupled memory (ATCM). When placing, "RZ\_T1\_init\_serial\_boot.icf" is changed as shown below (bold indicates added text, whereas double-strikethrough indicates deleted text).

| nitialize manua | lly { ro code object loader_init.o,    |

|-----------------|----------------------------------------|

|                 | ro code object loader_init2.o,         |

|                 | ro code object r_atcm_init.o,          |

|                 | ro code object r_cpg.o,                |

|                 | ro code object r_ram_init.o,           |

|                 | ro code object r_mpc.o,                |

|                 | ro code object bus_init_serial_boot.o, |

|                 | ro code object r_reset.o,              |

|                 | ro code object vector.o,               |

|                 | ro code object spibsc_flash_api.o,     |

|                 | ro code object spibsc_flash_userdef.o, |

|                 | ro code object spibsc_ioset_api.o,     |

|                 | ro code object spibsc_ioset_drv.o,     |

|                 | ro code object spibsc_ioset_userdef.o, |

|                 | ro code,                               |

|                 | section .rodata                        |

|                 | };                                     |

# 5.1.2 Preparing to Run the Program

This sample program handles processing for transfer to and from the PC and the following describes the preparation for running the program.

(1) Start the terminal software on the host PC and make settings for the serial port as follows (the following is the case for Tera Term on COM3).

| Tera Term: Serial port                                                                                             | t setup                                         |

|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| <u>P</u> ort:<br><u>B</u> aud rate:<br><u>D</u> ata:<br>P <u>a</u> rity:<br><u>S</u> top:<br><u>E</u> low control: | COM3  COM3 COM3 COK Cancel Rone Libit Help Rone |

| Transmit del                                                                                                       | ay<br>ec/ <u>c</u> har 0 msec/ <u>l</u> ine     |

Figure 5.1Settings for the Serial Port

Г

(2) When the sample program is run and ready to handle transfer, the data received form the sample program are displayed in the terminal software as shown below.

| COM3:115200baud - Tera T<br><u>File Edit Setup Control</u> |       |

|------------------------------------------------------------|-------|

| Serial Flash example program F                             |       |

|                                                            | <br>A |

| [1] Demo<br>[2] Read Serial Flash                          |       |

| [3] Write Serial Flash                                     |       |

| [4] Erase Serial Flash                                     |       |

| [9] Exit                                                   |       |

|                                                            |       |

| Í                                                          |       |

|                                                            |       |

|                                                            |       |

|                                                            |       |

|                                                            |       |

|                                                            |       |

|                                                            |       |

|                                                            |       |

|                                                            |       |

|                                                            |       |

|                                                            | -     |

Figure 5.2 Display in the Terminal Software after the Sample Program is Run

# 5.2 Fixed-Width Integers

Table 5.1 lists fixed-width integers used in the sample program.

#### Table 5.1 Fixed-Width Integers Used in the Sample Program

| Symbol   | Description             |

|----------|-------------------------|

| char_t   | 8-bit signed integer    |

| int_t    | Signed integer          |

| int32_t  | 32-bit signed integer   |

| uint8_t  | 8-bit unsigned integer  |

| uint16_t | 16-bit unsigned integer |

| uint32_t | 32-bit unsigned integer |

# 5.3 Structures and Unions

Table 5.2 to Table 5.8 list the structures used in the sample program.

| Table 5.2 | Structure of SPIBSC External Address Read Settings (st_spibsc_cfg_t) (1) |

|-----------|--------------------------------------------------------------------------|

|-----------|--------------------------------------------------------------------------|

| Member                                                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uint8_t udef_cmd                                                                 | <ul> <li>Read command</li> <li>Sets the read command output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications.</li> <li>The value of this member is set in the CMD[7:0] bits of the data read command setting register (DRCMR).</li> </ul>                                                                                                                                                                                                                 |

| uint8_t udef_cmd_wid                                                             | <ul> <li>Read command bit width</li> <li>Sets the bit width for issuing read commands.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the CDB[1:0] bits of the data read enable register<br/>(DRENR).</li> </ul>                                                                                                                                                                                                                      |

| uint8_t udef_opd3<br>uint8_t udef_opd2<br>uint8_t udef_opd1<br>uint8_t udef_opd0 | <ul> <li>Optional data</li> <li>Set the optional data output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications.</li> <li>The values of these members are set in the OPD3[7:0], OPD2[7:0], OPD1[7:0], and OPD0[7:0] bits of the data read option setting register (DROPR).</li> </ul>                                                                                                                                                                       |

| uint8_t udef_opd_ena                                                             | <ul> <li>Optional data enable</li> <li>Selects whether the optional data is to be issued.</li> <li>Available settings:<br/>SPIBSC_OUTPUT_DISABLE: No data are output.<br/>SPIBSC_OUTPUT_OPD_3: OPD3 is output.<br/>SPIBSC_OUTPUT_OPD_32: OPD3 and OPD2 are output.<br/>SPIBSC_OUTPUT_OPD_321: OPD3, OPD2, and OPD1 are output.<br/>SPIBSC_OUTPUT_OPD_3210: OPD3, OPD2, OPD1, and OPD0 are output.</li> <li>The value of this member is set in the OPDE[3:0] bits of the data read enable register<br/>(DRENR).</li> </ul> |

| uint8_t udef_opd_widt                                                            | <ul> <li>h Optional data bit width</li> <li>Sets the bit width for issuing the optional data.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the OPDB[1:0] bits of the data read enable register<br/>(DRENR).</li> </ul>                                                                                                                                                                                                              |

| Member                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| uint8_t udef_dmycyc_num   | <ul> <li>Number of dummy cycles</li> <li>Sets the number of dummy cycles output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications.</li> <li>Available settings:<br/>SPIBSC_DUMMY_1CYC: 1 cycle<br/>SPIBSC_DUMMY_2CYC: 2 cycles<br/>SPIBSC_DUMMY_3CYC: 3 cycles<br/>SPIBSC_DUMMY_4CYC: 4 cycles<br/>SPIBSC_DUMMY_4CYC: 5 cycles<br/>SPIBSC_DUMMY_5CYC: 5 cycles<br/>SPIBSC_DUMMY_6CYC: 6 cycles<br/>SPIBSC_DUMMY_7CYC: 7 cycles<br/>SPIBSC_DUMMY_8CYC: 8 cycles</li> <li>The value of this member is set in the DMCYC[2:0] bits of the data read dummy cycle setting register (DRDMCR).</li> </ul> |  |  |

| uint8_t udef_dmycyc_enabl | <ul> <li>Dummy cycle enable</li> <li>Selects whether dummy cycles are to be inserted.</li> <li>Available settings:<br/>SPIBSC_DUMMY_CYC_DISABLE: Dummy cycles are not inserted.<br/>SPIBSC_DUMMY_CYC_ENABLE: Dummy cycles are inserted.</li> <li>The value of this member is set in the DME bit of the data read enable register (DRENR).</li> </ul>                                                                                                                                                                                                                                                                                                             |  |  |

| uint8_t udef_dmycyc_width | <ul> <li>Dummy cycle bit width</li> <li>Sets the bit width for issuing dummy cycles.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the DMDB[1:0] bits of the data read dummy cycle<br/>setting register (DRDMCR).</li> </ul>                                                                                                                                                                                                                                                                                                                                                |  |  |

| uint8_t udef_data_width   | <ul> <li>Data read bit width</li> <li>Sets the bit width for reading data from the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the DRDB[1:0] bits of the data read enable register (DRENR).</li> </ul>                                                                                                                                                                                                                                                         |  |  |

# Table 5.3 Structure of SPIBSC External Address Read Settings (st\_spibsc\_cfg\_t) (2)

| Member                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| uint8_t udef_spbr       | <ul> <li>Bit rate</li> <li>Sets the bit rate of the serial clock (SPBCLK) output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications.</li> <li>Available settings:<br/>Make settings to match the bit-rate division setting (udef_brdv).</li> <li>The value of this member is set in the SPBR[7:0] bits of the bit rate setting register (SPBCR).</li> </ul>                  |  |  |  |

| uint8_t udef_brdv       | <ul> <li>Bit-rate division setting</li> <li>Sets the bit rate of the serial clock (SPBCLK) output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications.</li> <li>Available settings:<br/>Make settings to match the bit-rate division setting (udef_brdv).</li> <li>The value of this member is set in the BRDV[1:0] bits of the bit-rate setting register (SPBCR).</li> </ul> |  |  |  |

| uint8_t udef_addr_width | <ul> <li>Address bit width</li> <li>Sets the width in bits of the address line or lines for output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communication</li> <li>Available settings:</li> <li>SPIBSC_1BIT: 1-bit width</li> <li>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the ADB[1:0] bits of the data read enable register (DRENR).</li> </ul>     |  |  |  |

| uint8_t udef_addr_mode  | <ul> <li>Address enable</li> <li>Sets the address for output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications.</li> <li>Available settings:<br/>SPIBSC_OUTPUT_ADDR_24: 24-bit address output<br/>SPIBSC_OUTPUT_ADDR_32: 32-bit address output</li> <li>The value of this member is set in the ADE[3:0] bits of the data read enable register (DRENR).</li> </ul>           |  |  |  |

# Table 5.4 Structure of SPIBSC External Address Read Settings (st\_spibsc\_cfg\_t) (3)

| Member         | Description                                                                                                                                                                                                                                                                                                                      |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uint32_t cdb   | Command bit width <ul> <li>Sets the command bit width in SPI operation mode.</li> <li>Available settings: <ul> <li>SPIBSC_1BIT: 1-bit width</li> <li>SPIBSC_4BIT: 4-bit width</li> </ul> </li> <li>The value of this member is set in the CDB[1:0 bits of the SPI mode enable register (SMENR).</li> </ul>                       |

| uint32_t ocdb  | <ul> <li>Optional command bit width</li> <li>Specifies the optional command bit width in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the OCDB[1:0] bits of the SPI mode enable register<br/>(SMENR).</li> </ul>       |

| uint32_t adb   | <ul> <li>Address bit width</li> <li>Specifies the width in bits of the address line or lines in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the ADB[1:0] bits of the SPI mode enable register<br/>(SMENR).</li> </ul> |

| uint32_t opdb  | <ul> <li>Optional data bit width</li> <li>Specifies the optional data bit width in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the OPDB[1:0] bits of the SPI mode enable register<br/>(SMENR).</li> </ul>             |

| uint32_t spidb | <ul> <li>Transfer data bit width</li> <li>Specifies the transfer data bit width in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the SPIDB[1:0] bits of the SPI mode enable register<br/>(SMENR).</li> </ul>            |

| uint32_t cde   | <ul> <li>Sets whether commands are to be output in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_OUTPUT_DISABLE: Output is disabled.<br/>SPIBSC_OUTPUT_ENABLE: Output is enabled.</li> <li>The value of this member is set in the CDE bit of the SPI mode enable register (SMENR).</li> </ul>                      |

# Table 5.5 Structure of SPIBSC SPI Mode Settings (st\_spibsc\_spimd\_reg\_t) (1)

| Member   |       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uint32_t | ocde  | <ul> <li>Optional command enable</li> <li>Sets whether the optional command is to be output in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_OUTPUT_DISABLE: Output is disabled.<br/>SPIBSC_OUTPUT_ENABLE: Output is enabled.</li> <li>The value of this member is set in the OCDE bit of the SPI mode enable register<br/>(SMENR).</li> </ul>                                                                                                                                                                                    |

| uint32_t | ade   | <ul> <li>Address enable</li> <li>Sets whether the address is to be output in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_OUTPUT_DISABLE: Output is disabled.<br/>SPIBSC_OUTPUT_ADDR_24: ADR[23:0] are output.<br/>SPIBSC_OUTPUT_ADDR_32: ADR[31:0] are output.</li> <li>The value of this member is set in the ADE[3:0] bits of the SPI mode enable register<br/>(SMENR).</li> </ul>                                                                                                                                            |

| uint32_t | opde  | <ul> <li>Optional data enable</li> <li>Sets whether the optional data is to be issued in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_OUTPUT_DISABLE: Output is disabled.<br/>SPIBSC_OUTPUT_OPD_3: OPD3 is output.<br/>SPIBSC_OUTPUT_OPD_32: OPD3 and OPD2 are output.<br/>SPIBSC_OUTPUT_OPD_321: OPD3, OPD2, and OPD1 are output.<br/>SPIBSC_OUTPUT_OPD_3210: OPD3, OPD2, OPD1, and OPD0 are output.</li> <li>The value of this member is set in the OPDE[3:0] bits of the SPI mode enable setting register (SMENR).</li> </ul> |

| uint32_t | spide | <ul> <li>Transfer data enable</li> <li>Sets whether data transfer is to proceed in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_OUTPUT_DISABLE: Output is disabled.<br/>SPIBSC_OUTPUT_SPID_8: 8- (or 16-) bit transfer<br/>SPIBSC_OUTPUT_SPID_16: 16- (or 32-) bit transfer<br/>SPIBSC_OUTPUT_SPID_32: 32- (or 64-) bit transfer</li> <li>The value of this member is set in the SPIDE[3:0] bits of the SPI mode enable register<br/>(SMENR).</li> </ul>                                                                         |

| uint32_t | sslkp | <ul> <li>SPBSSL signal level retention</li> <li>Sets the state of the SPBSSL signal after the end of transfer in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_SPISSL_NEGATE: The signal is negated at the end of transfer.<br/>SPIBSC_SPISSL_KEEP: The level of the SPBSSL signal is retained from the end of transfer to the start of next access.</li> <li>The value of this member is set in the SSLKP bit of the SPI mode control register (SMCR).</li> </ul>                                                                |

# Table 5.6 Structure of SPIBSC SPI Mode Settings (st\_spibsc\_spimd\_reg\_t) (2)

| Member         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| uint32_t spire | <ul> <li>Data read enable</li> <li>Enables or disables reading of data in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_SPIDATA_DISABLE: Reading of data is disabled.<br/>SPIBSC_SPIDATA_ENABLE: Reading of data is enabled.</li> <li>The value of this member is set in the SPIRE bit of the SPI mode control register<br/>(SMCR).</li> </ul>                                                                                                                                                                      |  |  |  |

| uint32_t spiwe | <ul> <li>Data write enable</li> <li>Enables or disables writing of data in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_SPIDATA_DISABLE: Writing of data is disabled.<br/>SPIBSC_SPIDATA_ENABLE: Writing of data is enabled.</li> <li>The value of this member is set in the SPIWE bit of the SPI mode control register<br/>(SMCR).</li> </ul>                                                                                                                                                                     |  |  |  |

| uint32_t dme   | <ul> <li>Dummy cycle enable</li> <li>Sets whether dummy cycles are to be inserted in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_DUMMY_CYC_DISABLE: Dummy cycles are not inserted.<br/>SPIBSC_DUMMY_CYC_ENABLE: Dummy cycles are inserted.</li> <li>The value of this member is set in the DME bit of the SPI mode enable register (SMENR).</li> </ul>                                                                                                                                                            |  |  |  |

| uint8_t dmdb   | <ul> <li>Dummy cycle bit width</li> <li>Sets the bit width of dummy cycles in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the DMDB[1:0] bits of the SPI mode dummy cycle<br/>setting register (SMDMCR).</li> </ul>                                                                                                                                                                                                     |  |  |  |

| uint8_t dmcyc  | <ul> <li>Number of dummy cycles</li> <li>Sets the number of dummy cycles in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_DUMMY_1CYC: 1 cycle<br/>SPIBSC_DUMMY_2CYC: 2 cycles<br/>SPIBSC_DUMMY_3CYC: 3 cycles<br/>SPIBSC_DUMMY_4CYC: 4 cycles<br/>SPIBSC_DUMMY_5CYC: 5 cycles<br/>SPIBSC_DUMMY_6CYC: 6 cycles<br/>SPIBSC_DUMMY_7CYC: 7 cycles<br/>SPIBSC_DUMMY_7CYC: 8 cycles</li> <li>The value of this member is set in the DMCYC[2:0] bits of the SPI mode dummy cycle<br/>setting register (SMDMCR).</li> </ul> |  |  |  |

# Table 5.7 Structure of SPIBSC SPI Mode Settings (st\_spibsc\_spimd\_reg\_t) (3)

| Member         | Description                                                                                                                                                                                                                                                                                                                        |  |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| uint8_t cmd    | <ul> <li>Command</li> <li>Sets the command for output in SPI operation mode.</li> <li>The value of this member is set in the CMD[7:0] bits of the SPI mode command setting register (SMCMR).</li> </ul>                                                                                                                            |  |  |  |

| uint8_t ocmd   | <ul> <li>Optional command</li> <li>Sets the optional command for output in SPI operation mode.</li> <li>The value of this member is set in the OCMD[7:0] bits of the SPI mode command setting register (SMCMR).</li> </ul>                                                                                                         |  |  |  |

| uint32_t addr  | <ul> <li>Address</li> <li>Sets the address for output in SPI operation mode.</li> <li>The value of this member is set in the ADR[23:0] bits of the SPI mode address sett register (SMADR).</li> <li>Set the ADRE[7:0] bits for output in 32 bits.</li> <li>This setting is effective when the ADE[3] bit of SMENR is 1.</li> </ul> |  |  |  |

| uint8_t opd[4] | Optional data<br>• Sets the optional data for output in SPI operation mode.<br>• The value of this member is set in the OPDn[7:0] bits of the SPI mode option setting<br>register (SMOPR) as follows.<br>OPD3[7:0] ← opd[0]<br>OPD2[7:0] ← opd[1]<br>OPD1[7:0] ← opd[2]<br>OPD0[7:0] ← opd[3]                                      |  |  |  |

| uint32_t smrdr | <ul> <li>Read data storage buffer</li> <li>Holds the data read in SPI operation mode (the value of the SPI mode read data registe 0 (SMRDR0)) as follows.</li> <li>SMRDR0 → smrdr</li> </ul>                                                                                                                                       |  |  |  |

| uint32_t smwdr | <ul> <li>Write data storage buffer</li> <li>Holds the data for writing in SPI operation mode (the value of the SPI mode write register 0 (SMWDR0)) as follows.</li> <li>SMWDR0 ← swrdr</li> </ul>                                                                                                                                  |  |  |  |

# Table 5.8 Structure of SPIBSC SPI Mode Settings (st\_spibsc\_spimd\_reg\_t) (4)

# 5.4 Constants

Table 5.9 to Table 5.12 list the constants used in the sample program.

| Constant                    | Setting | Description                                        |

|-----------------------------|---------|----------------------------------------------------|

| SFLASHCMD_SECTOR_ERASE      | (0xD8)  | Sector erase (3-byte address) command*1            |

| SFLASHCMD_BYTE_PROGRAM      | (0x02)  | Page programming (3-byte address) command          |

| SFLASHCMD_FAST_READ         | (0x0B)  | Read fast (3-byte address) command                 |

| SFLASHCMD_QUAD_FAST_READ    | (0x6B)  | Quad read fast (3-byte address) command            |

| SFLASHCMD_QUAD_IO_READ      | (0xEB)  | Quad I/O read (3-byte address) command             |

| SFLASHCMD_WRITE_ENABLE      | (0x06)  | Write enable command                               |

| SFLASHCMD_READ_STATUS       | (0x05)  | Read status register-1 command                     |

| SFLASHCMD_READ_CONFIG       | (0x15)  | Read configuration register-1 command              |

| SFLASHCMD_WRITE_STATUS      | (0x01)  | Write register (status-1, configuration-1) command |

| SFLASHCMD_SECTOR_ERASE_4B   | (0xDC)  | Sector erase (4-byte address) command*1            |

| SFLASHCMD_BYTE_PROGRAM_4B   | (0x12)  | Page programming (4-byte address) command          |

| SFLASHCMD_FAST_READ_4B      | (0x0C)  | Read fast (4-byte address) command                 |

| SFLASHCMD_QUAD_FAST_READ_4B | (0x6C)  | Quad read fast (4-byte address) command            |

| SFLASHCMD_QUAD_IO_READ_4B   | (0xEC)  | Quad I/O read (4-byte address) command             |

Note 1. A Macronix serial flash memory (product type name: MX25L51245G) for use by this sample program is erased in 64-Kbyte block units.

#### Table 5.10 Constants Used in the Sample Program (2)

| Constant           | Setting | Description                                        |

|--------------------|---------|----------------------------------------------------|

| STREG_SRWD_BIT     | (0x80)  | Status register/SRWD bit mask value                |

| STREG_QUAD_BIT     | (0x40)  | Status register/QUAD bit mask value                |

| STREG_BPROTECT_BIT | (0x3C)  | Status register/block protection bit mask value    |

| STREG_WEL_BIT      | (0x02)  | Status register/write enable latch bit mask value  |

| STREG_WIP_BIT      | (0x01)  | Status register/write in progress bit mask value   |

| CFREG_LC_BIT       | (0xC0)  | Configuration register/latency code bit mask value |

| CFREG_4BYTE_BIT    | (0x20)  | Configuration register/4-byte bit mask value       |

| Constant                 | Setting      | Description                                                                                         |

|--------------------------|--------------|-----------------------------------------------------------------------------------------------------|

| SPIBSC_CMNCR_BSZ_SINGLE  | (0)          | One serial flash memory is connected to the SPIBSC data bus.                                        |

| SPIBSC_CMNCR_MD_EXTRD    | (0)          | Sets mode of the SPIBSC to external address space read mode.                                        |

| SPIBSC_CMNCR_MD_SPI      | (1)          | Sets mode of the SPIBSC to SPI operation mode.                                                      |

| SPIBSC_OUTPUT_LOW        | (0)          | Sets the pin output value to 0.                                                                     |

| SPIBSC_OUTPUT_HIGH       | (1)          | Sets the pin output value to 1.                                                                     |

| SPIBSC_OUTPUT_LAST       | (2)          | Sets the pin output value as the value of the last bit from the previous transfer.                  |

| SPIBSC_OUTPUT_HiZ        | (3)          | Sets the pin output value to HI-Z.                                                                  |

| SPIBSC_CMNCR_CPHAT_EVEN  | (0)          | Sets the edge of the SPBCLK signal for received data to odd edges.                                  |

| SPIBSC_CMNCR_CPHAT_ODD   | (1)          | Sets the edge of the SPBCLK signal for received data to even edges.                                 |

| SPIBSC_CMNCR_CPHAR_ODD   | (0)          | Sets the edge of the SPBCLK signal for received data to even edges.                                 |

| SPIBSC_CMNCR_CPHAR_EVEN  | (1)          | Sets the edge of the SPBCLK signal for received data to odd edges.                                  |

| SPIBSC_CMNCR_SSLP_LOW    | (0)          | Sets the sense of the SPBSSL signal to active low.                                                  |

| SPIBSC_CMNCR_SSLP_HIGH   | (1)          | Sets the sense of the SPBSSL signal to active high.                                                 |

| SPIBSC_CMNCR_CPOL_LOW    | (0)          | Sets the output level of the SPBCLK pin for the period while the SPBSSL signal is inactive to 0.    |

| SPIBSC_CMNCR_CPOL_HIGH   | (1)          | Sets the output level of the SPBCLK pin for the period while the SPBSSL signal<br>is inactive to 1. |

| SPIBSC_DELAY_1SPBCLK     | (0)          | Sets B'000 to each symbol of the SSL delay register.                                                |

| SPIBSC_DELAY_2SPBCLK     | (1)          | Sets B'001 to each symbol of the SSL delay register.                                                |

| SPIBSC_DELAY_3SPBCLK     | (2)          | Sets B'010 to each symbol of the SSL delay register.                                                |

| SPIBSC_DELAY_4SPBCLK     | (3)          | Sets B'011 to each symbol of the SSL delay register.                                                |

| SPIBSC_DELAY_5SPBCLK     | (4)          | Sets B'100 to each symbol of the SSL delay register.                                                |

| SPIBSC_DELAY_6SPBCLK     | (5)          | Sets B'101 to each symbol of the SSL delay register.                                                |

| SPIBSC_DELAY_7SPBCLK     | (6)          | Sets B'110 to each symbol of the SSL delay register.                                                |

| SPIBSC_DELAY_8SPBCLK     | (7)          | Sets B'111 to each symbol of the SSL delay register.                                                |

| SPIBSC_BURST_1           | (0x00)       | Burst length for reading:                                                                           |

| to<br>SPIBSC BURST 16    | to<br>(0x0f) | 1 to 16 data-length bits                                                                            |

| <br>SPIBSC_BURST_DISABLE | (0)          | Disables the read cache.                                                                            |

| SPIBSC_BURST_ENABLE      | (1)          | Enables the read cache.                                                                             |

| SPIBSC_DRCR_RCF_EXE      | (1)          | Clears all entries in the read cache.                                                               |

| SPIBSC_SSL_NEGATE        | (0)          | The SPBSSL pin is inactive.                                                                         |

| SPIBSC_TRANS_END         | (1)          | Indicates the completion of data transfer.                                                          |

| SPIBSC_1BIT              | (0)          | Sets the bit width for issuing read commands to 1 bit.                                              |

| SPIBSC_4BIT              | (2)          | Sets the bit width for issuing read commands to 4 bits.                                             |

| SPIBSC_OUTPUT_DISABLE    | (0)          | Specifies that no command is output when a read command is issued.                                  |

| SPIBSC_OUTPUT_ENABLE     | (1)          | Specifies that a command is output when a read command is issued.                                   |

| SPIBSC_OUTPUT_ADDR_24    | (0x07)       | Outputs 24-bit addresses.                                                                           |

| SPIBSC_OUTPUT_ADDR_32    | (0x0f)       | Outputs 32-bit addresses.                                                                           |

| SPIBSC_OUTPUT_OPD_3      | (0x08)       | Outputs the optional data OPD3 when a read command is issued.                                       |

| SPIBSC_OUTPUT_OPD_32     | (0x0c)       | Outputs the optional data OPD3 and OPD2 when a read command is issued.                              |

| SPIBSC_OUTPUT_OPD_321    | (0x0e)       | Outputs the optional data OPD3, OPD2, and OPD1 when a read command is issued.                       |

| SPIBSC_OUTPUT_OPD_3210   | (0x0f)       | Outputs the optional data OPD3, OPD2, OPD1, and OPD0 when a read command is issued.                 |

|                          |              |                                                                                                     |

Table 5.11

Constants Used in the Sample Program (3)

| Constant                 | Setting | Description                                                                                                                                                       |

|--------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPIBSC_OUTPUT_SPID_16    | (0x0c)  | Enables 16- (or 32-) bit transfer in SPI operation mode.                                                                                                          |

| SPIBSC_OUTPUT_SPID_32    | (0x0f)  | Enables 32- (or 64-) bit transfer in SPI operation mode.                                                                                                          |

| SPIBSC_SPISSL_NEGATE     | (0)     | Sets the state of SPBSSL signal after the end of transfer to the negated state in SPI operation mode.                                                             |

| SPIBSC_SPISSL_KEEP       | (1)     | Specifies that the level of the SPBSSL signal is retained from the end of transfer to the start of next access in SPI operation mode.                             |

| SPIBSC_SPIDATA_DISABLE   | (0)     | Disables reading of data in SPI operation mode.                                                                                                                   |

| SPIBSC_SPIDATA_ENABLE    | (1)     | Enables reading of data in SPI operation mode.                                                                                                                    |

| SPIBSC_SPI_ENABLE        | (1)     | Starts transfer of SPI data.                                                                                                                                      |

| SPIBSC_DUMMY_CYC_DISABLE | (0)     | Disables insertion of dummy cycles.                                                                                                                               |

| SPIBSC_DUMMY_CYC_ENABLE  | (1)     | Enables insertion of dummy cycles.                                                                                                                                |

| SPIBSC_DUMMY_1CYC        | (0)     | Sets the number of dummy cycles for output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications to 1. |

| SPIBSC_DUMMY_2CYC        | (1)     | Sets the number of dummy cycles for output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications to 2. |

| SPIBSC_DUMMY_3CYC        | (2)     | Sets the number of dummy cycles for output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications to 3. |

| SPIBSC_DUMMY_4CYC        | (3)     | Sets the number of dummy cycles for output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications to 4. |

| SPIBSC_DUMMY_5CYC        | (4)     | Sets the number of dummy cycles for output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications to 5. |

| SPIBSC_DUMMY_6CYC        | (5)     | Sets the number of dummy cycles for output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications to 6. |

| SPIBSC_DUMMY_7CYC        | (6)     | Sets the number of dummy cycles for output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications to 7. |

| SPIBSC_DUMMY_8CYC        | (7)     | Sets the number of dummy cycles for output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications to 8. |

| Table 5.11 | Constants Used in the Sample Program (3) |

|------------|------------------------------------------|

|------------|------------------------------------------|

| Table 5.12 | Constants Used in the Sample Program (4) |

|------------|------------------------------------------|

|------------|------------------------------------------|

| Constant                  | Setting                         | Description                                                        |

|---------------------------|---------------------------------|--------------------------------------------------------------------|

| R_SERIAL_FLASH_TOP        | (0x1000000U)                    | Address where the installed serial flash memory starts             |

| R_SERIAL_FLASH_END        | (0x13FFFFFCU)                   | Address where the installed serial flash memory ends               |

| R_SERIAL_FLASH_ADDR_LIMIT | 0x14000000U                     | Boundary value of the address of the installed serial flash memory |

| R_SERIAL_FLASH_READ_SIZE  | (64U)                           | Maximum value of the amount of data to be read                     |

| R_SERIAL_FLASH_CNT_ADDR   | (0x13FF0000U)                   | Counter variable area                                              |

| R_SERIAL_FLASH_DATA_WIDTH | SPIBSC_4BIT<br>(2)              | Data read bit width                                                |

| R_SERIAL_FLASH_ADDR_MODE  | SPIBSC_OUTPUT_ADDR_32<br>(0x0f) | Number of address bytes                                            |

| R_SERIAL_FLASH_WRITE_BYTE | (4)                             | Amount of bytes to be written                                      |

| R_SERIAL_FLASH_READ_BYTE  | (4)                             | Amount of bytes to be read                                         |

#### 5.5 Variables

Table 5.13 and Table 5.14 list the static and global constants, respectively.

#### Table 5.13 Static Variables

| Туре            | Variable Name | Description                                                                                                 |

|-----------------|---------------|-------------------------------------------------------------------------------------------------------------|

| static char     | gbuff[16]     | Data received from the terminal software                                                                    |

| st_spibsc_cfg_t | spibsc_cfg    | SPIBSC external address read settings storage variable<br>Stores the SPIBSC external address read settings. |

#### Table 5.14Global Variables

| Туре                  | Variable Name      | Description                                                                                                                                                                                                                                                                                                                   |

|-----------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| st_spibsc_spimd_reg_t | g_spibsc_spimd_reg | <ul> <li>SPIBSC SPI mode operation settings storage variable</li> <li>Stores the SPIBSC settings when the SPIBSC is used in SPI mode<br/>In the sample program, these settings are also used as arguments<br/>when running serial flash control functions within the API functions<br/>and user-defined functions.</li> </ul> |

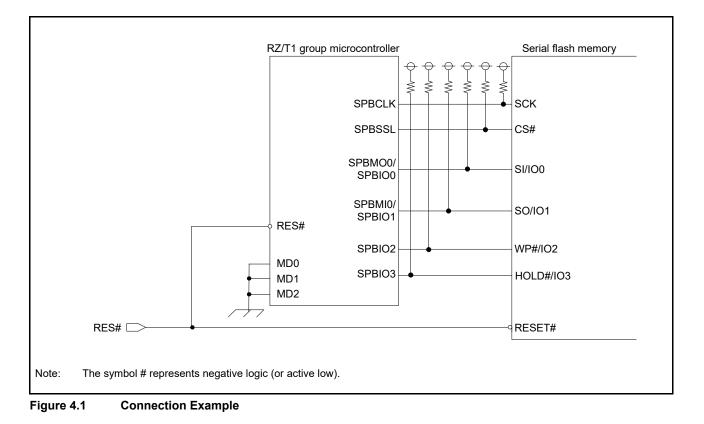

#### 5.6 Functions

The sample code consists of the following functions: the interface functions for using peripheral modules (API functions); the user-defined functions that must be prepared by the user to suit the application of the user system (function called by the API functions); and the sample functions required to operate the sample code.

Table 5.15 to Table 5.17 list the functions to be used.

| Table 5.15 | List of Functions | (1) |

|------------|-------------------|-----|

|------------|-------------------|-----|

| Function           | Description                                                                                                                                                 |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| spibsc_init        | SPIBSC initial settings function<br>Makes settings optimized for use with a Macronix flash memory (product type name:<br>MX25L51245G) within this function. |

| serial_flash_demo  | Function for executing the demonstration program                                                                                                            |

| serial_flash_read  | Function for executing the serial flash read program                                                                                                        |

| serial_flash_write | Function for executing the serial flash write program                                                                                                       |

| serial_flash_erase | Function for executing the serial flash erasure program                                                                                                     |

| main               | Main function of the sample program                                                                                                                         |

| Table 5.16 List of Funct | ions (2) |

|--------------------------|----------|

|--------------------------|----------|

| Function                | Description                                                                                                                                                                                                                                                                                                                                            |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R_SPIBSC_ExmodeSetting  | SPIBSC initial settings function<br>Makes initial settings required for controlling the serial flash memory and for using the SPIBSC in<br>external address read mode. This function also makes register settings in the flash memory to suit<br>the initial settings. After the initial settings, it places the SPIBSC in external address read mode. |

| R_SPIBSC_WaitTend       | SPIBSC data transfer end wait function<br>Waits for the completion of data transfer from the SPIBSC.                                                                                                                                                                                                                                                   |

| R_SPIBSC_Exmode         | SPIBSC external address mode setting function<br>Places the SPIBSC in external address read mode.                                                                                                                                                                                                                                                      |

| R_SPIBSC_SetConfig      | SPIBSC external address read settings function<br>Makes initial settings required for using the SPIBSC in external address read mode.                                                                                                                                                                                                                  |

| R_SPIBSC_Spimode        | SPIBSC SPI mode setting function<br>Places the SPIBSC in SPI mode.                                                                                                                                                                                                                                                                                     |

| R_SPIBSC_ExmodeInit     | SPIBSC external address mode initial settings function<br>Makes initial settings for using the SPIBSC in external address read mode. After the initial<br>settings, it places the SPIBSC in external address read mode.                                                                                                                                |

| R_SPIBSC_EraseSector    | Serial flash memory erasure function<br>Uses SPI mode of the SPIBSC to erase the serial flash memory.                                                                                                                                                                                                                                                  |

| R_SPIBSC_ByteProgram    | Serial flash memory programming function<br>Uses SPI mode of the SPIBSC to write data to the serial flash memory.                                                                                                                                                                                                                                      |

| R_SPIBSC_ByteRead       | Serial flash memory read function<br>Uses SPI mode of the SPIBSC to read data from the serial flash memory.                                                                                                                                                                                                                                            |

| R_SPIBSC_SpibscTransfer | Serial flash memory control function<br>Issues commands to the serial flash memory according to arguments.                                                                                                                                                                                                                                             |

| Function                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

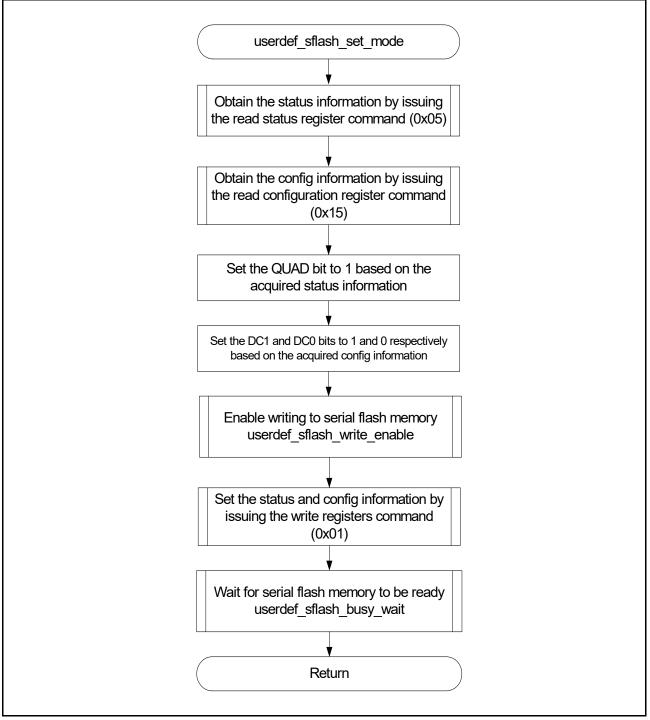

| userdef_spibsc_set_config   | SPIBSC external address read settings function<br>Determines the SPIBSC external address read mode settings to suit the serial flash memory in<br>use. The sample program makes initial settings required for using the SPIBSC in external address<br>read mode on the basis of the settings made by this function.<br>The sample program makes initial settings for the SPIBSC for use with a Macronix serial flash<br>memory (product type name: MX25L51245G). |

| userdef_sflash_set_mode     | Serial flash memory internal register settings function<br>Makes settings for the registers in the serial flash memory required when using the SPIBSC in<br>external address read mode, to suit the serial flash memory in use.<br>The sample program makes initial settings for the registers in the Macronix serial flash memory<br>(product type name: MX25L51245G).                                                                                          |

| userdef_sflash_write_enable | Serial flash memory write enable function<br>Makes settings for the registers in the serial flash memory to enable writing, to suit the serial flash<br>memory in use.<br>The sample program makes settings for the registers in the Macronix serial flash memory (product<br>type name: MX25L51245G).                                                                                                                                                           |

| userdef_sflash_busy_wait    | Serial flash memory ready wait function<br>Reads the registers in the serial flash memory and waits for the serial flash memory to enter the<br>ready state, over a period that suits the serial flash memory in use.<br>The sample program waits for the Macronix serial flash memory (product type name:<br>MX25L51245G) to enter the ready state.                                                                                                             |

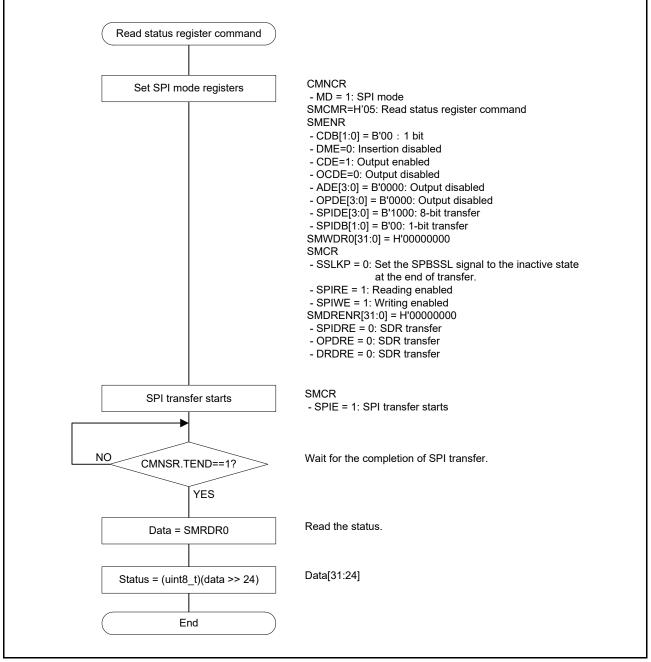

# 5.7 Details of Functions

The following tables list the details of the functions.

| spibsc_init  |                                                                                                                                                                                                                                                                                                                                                         |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Synopsis     | SPIBSC initial settings function                                                                                                                                                                                                                                                                                                                        |

| Declaration  | static void spibsc_init(void);                                                                                                                                                                                                                                                                                                                          |

| Description  | This function makes settings optimized for use with a Macronix serial flash memory (product type name: MX25L51245G) within this function.                                                                                                                                                                                                               |

| Arguments    | None                                                                                                                                                                                                                                                                                                                                                    |

| Return value | None                                                                                                                                                                                                                                                                                                                                                    |

| Note         | This function is used when the MCU is booted in 16-bit bus boot mode.<br>This function is not used when the MCU is booted in SPI boot mode, since the initial settings for<br>the SPIBSC are made within the settings for bus connection during booting up. For details, check<br>with the RZ/T1 Group Initial Settings application note (R01AN2554EJ). |

| serial_flash_demo |                                                                                                         |

|-------------------|---------------------------------------------------------------------------------------------------------|

| Synopsis          | Function for executing the demonstration program                                                        |

| Declaration       | static void serial_flash_demo (void)                                                                    |

| Description       | This function executes the demonstration program by handling the issuing of user commands by key input. |

| Arguments         | None                                                                                                    |

| Return value      | None                                                                                                    |

| serial_flash_read |                                                                                                             |

|-------------------|-------------------------------------------------------------------------------------------------------------|

| Synopsis          | Function for executing the serial flash read program                                                        |

| Declaration       | static void serial_flash_read (void)                                                                        |

| Description       | This function executes the serial flash read program by handling the issuing of user commands by key input. |

| Arguments         | None                                                                                                        |

| Return value      | None                                                                                                        |

#### serial\_flash\_write

| Synopsis     | Function for executing the serial flash write program                                                          |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------|--|--|

| Declaration  | n static void serial_flash_write (void)                                                                        |  |  |

| Description  | n This function executes the serial flash write program by handling the issuing of user commands by key input. |  |  |

| Arguments    | None                                                                                                           |  |  |

| Return value | None                                                                                                           |  |  |

#### serial\_flash\_erase

| _ | _            |                                                                                                                     |  |  |

|---|--------------|---------------------------------------------------------------------------------------------------------------------|--|--|

|   | Synopsis     | Function for executing the serial flash erasure program                                                             |  |  |

|   | Declaration  | on static void serial_flash_erase (void)                                                                            |  |  |

|   | Description  | n This function executes the serial flash erasure program by handling the issuing of user commands<br>by key input. |  |  |

|   | Arguments    | None                                                                                                                |  |  |

|   | Return value | None                                                                                                                |  |  |

|   |              |                                                                                                                     |  |  |

#### main

| Synopsis     | Main function of the sample program   |

|--------------|---------------------------------------|

| Declaration  | void main (void)                      |

| Description  | Main processing of the sample program |

| Arguments    | None                                  |

| Return value | None                                  |

|              |                                       |

| R_SPIBSC_ExmodeSetting |                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                   |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|