# Interfacing the Tsi384 and the Tsi148: Clocking and Reset Considerations

80E1000\_AN006\_04

September 22, 2009

6024 Silver Creek Valley Road San Jose, California 95138

Telephone: (408) 284-8200 • FAX: (408) 284-3572

Printed in U.S.A.

©2009 Integrated Device Technology, Inc.

#### GENERAL DISCLAIMER

GENERAL DISCLAIMER

Integrated Device Technology, Inc. ("IDT") reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance. IDT does not assume responsibility for use of any circuitry described herein other than the circuitry embodied in an IDT product. Disclosure of the information herein does not convey a license or any other right, by implication or otherwise, in any patent, trademark, or other intellectual property right of IDT. IDT products may contain errata which can affect product performance to a minor or immaterial degree. Current characterized errata will be made available upon request. Items identified herein as "reserved" or "undefined" are reserved for future definition. IDT does not assume responsibility for conflicts or incompatibilities arising from the future definition of such items. IDT products have not been designed, tested, or manufactured for use in, and thus are not warranted for, applications where the failure, malfunction, or any inaccuracy in the application carries a risk of death, serious bodily injury, or damage to tangible property. Code examples provided herein by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of such code examples shall be at the user's sole risk.

Copyright  $^{\odot}$  2009 Integrated Device Technology, Inc. All Rights Reserved.

The IDT logo is registered to Integrated Device Technology, Inc. IDT is a trademark of Integrated Device Technology, Inc.

# 1. Interfacing the Tsi384 and the Tsi148: Clocking and Reset Considerations

This application note details the hardware requirements specific to clocking and reset when designing a board that interfaces the IDT Tsi384 and Tsi148 devices on the PCI/X bus. The following topics are discussed:

- "Overview" on page 3

- "Tsi148 Power-on Reset Requirements" on page 4

- "Tsi384 Clocking Modes" on page 5

# **Revision History**

# 80E1000\_AN006\_04, Formal, September 2009

This document was rebranded as IDT. It does not include any technical changes.

# 80E1000\_AN006\_03, Formal, October 2008

The "Slave Mode Clocking" section has been updated to show that this mode is the preferred mode of operation.

## 80E1000\_AN006\_02, Formal, February 2008

This document includes a slight correction in the units for "Reset Timing".

#### 80E1000\_AN006\_01, Formal, September 2007

This was the first version of this document.

# 1.1 Overview

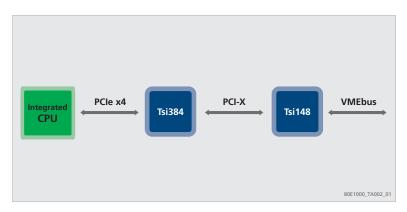

The Tsi384 is a PCI Express-to-PCI/PCI-X Bridge designed for forward bridging applications. The Tsi148 is a PCI/X-to-VMEbus Bridge used in applications that require PCI/X access to the VMEbus. The Tsi384 and Tsi148 can be combined and used in designs that require access to the VMEbus when only a PCIe port is available (see Figure 1).

Figure 1: Tsi384 and Tsi148 Typical Application

This document addresses the clocking and reset timing requirements in the following cases:

- Slave Mode Clocking

- In this mode, an external clock buffer is added to the design and both PCI/X clock inputs to the Tsi384 and Tsi148 are provided externally.

- This mode is the preferred mode because it allows for flexibility in performing local PCI resets

- Master Mode Clocking

- In this mode, the Tsi384 provides PCI/X clock outputs to source the PCI/X clock inputs for both the Tsi384 and Tsi148

# 1.2 Tsi148 Power-on Reset Requirements

The Tsi148 has some specific requirements for power-on reset that must be followed for proper device operation.

At power-up, there are three reset inputs to the Tsi148 that must meet specific timing requirements. The Tsi148 PLL\_RSTI\_, PURSTI\_ and LRSTI\_ inputs must be asserted and negated as follows:

- PLL\_RSTI\_

- The Tsi148 PLL reset input (PLL\_RSTI\_) is required to reset the internal PLL and must be held asserted until both power and the PCI/X reference clock (PCLK) are stable

- PURSTI

- The Tsi148 power-up reset input (PURSTI\_) is a full device reset. The PURSTI\_ reset must be held a minimum of 150 us after the de-assertion of PLL\_RSTI\_ so that the internal PLLs within the Tsi148 can lock.

- LRSTI

- At power-up, the Tsi148's local reset (PCI/X reset) input must be held asserted until the PCI/X initialization pattern is stable. Once the pattern is stable, the LRSTI\_input can be negated.

The Tsi384's initialization pattern is stable at a very specific time (see Figure 3 and Figure 2). For more information about timing values, see the *Tsi384 User Manual*.

# 1.3 Tsi384 Clocking Modes

The system requirements dictate which clocking mode, master or slave, to use in a Tsi384 and Tsi148 application. How the PCI/X clocks are provided dictates the system functionality and the reset requirements between the Tsi384 and Tsi148.

The Tsi148 has a very flexible reset architecture that allows for the PCI/X and VMEbus interfaces to be reset completely asynchronously from each other. However, when the Tsi384 is configured in master mode clocking, the Tsi148 effects VMEbus resources because the Tsi148 must be completely reset when the Tsi384 is reset (see "Master Mode Clocking" on page 6). When the Tsi384 is configured in slave mode clocking, the Tsi148's local bus (PCI/X) can be independently reset when the Tsi384 is reset (see "Slave Mode Clocking" on page 5).

# 1.3.1 Slave Mode Clocking

When the Tsi384 is configured to use slave mode clocking, an external clock buffer is required to supply the PCI/X clock inputs to the Tsi384 and the Tsi148. Since the PCI/X clock remains stable through local bus reset (PCI/X), the Tsi148 does not require a complete power-on reset. Operating the Tsi384 with slave mode clocking allows complete flexibility in resetting the Tsi148 after the initial power-on reset.

The Tsi384 inputs reset from upstream devices and drive reset to downstream devices. In the event of a PCIe reset (Cold, Warm, or Hot) the Tsi384 drives its PCI reset output signal (PCI\_RSTn). After the initial power-on reset, the PCI\_RSTn output can be used to reset the Tsi148 local resources (PCI/X) without effecting the VMEbus resources.

The Tsi148 requires a full power-on reset at initial power-up in order to sample the PCI/X initialization pattern and its internal PLLs can lock to the incoming PCI/X clock (once stable). After the initial power-up reset, the Tsi148's local reset (PCI/X) input (LRSTI\_) can be driven to reset Tsi148 local resources (PCI/X).

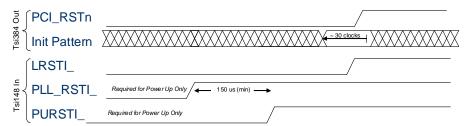

Figure 2 describes the required reset timing between the Tsi384 and Tsi148 when operating in clock slave mode. In addition to the external clock buffer, the reset timing requires the use of on-board logic to properly generate the reset inputs to the Tsi148.

Figure 2: Slave Mode Clocking Reset Timing

#### Figure 2 notes:

1. PLL\_RSTI\_ is de-asserted when the power and clocks are stable

The assertion of PLL\_RSTI is only required during power-up reset.

- 2. PURSTI\_ is de-asserted 150 us (minimum after PLL\_RSTI is de-asserted

- This satisfies the timing requirement between PLL\_RST\_ and PURSTI\_.

The assertion of PURSTI\_ is only required during power-up reset.

- 3. LRSTI\_ is de-asserted with PCI\_RSTn

- a. This latches the Initialization Pattern within the Tsi148.

- Initialization Pattern is stable approximately 30 clock cycles prior to the de-assertion of PCI RSTn

- Initialization Pattern is held for two additional PCI/X clock cycles following PCI\_RSTn de-assertion

## 1.3.2 Master Mode Clocking

When the Tsi384 is configured to operate in master mode clocking, the Tsi384 can provide up to five PCI/X clock outputs (PCI\_CLKO[4:0]). In a Tsi384 and Tsi148 application, the Tsi384 provides the PCI/X clock source for the Tsi148. When the Tsi384 provides the PCI/X system clocks, the Tsi148 requires a full power-on reset when the is Tsi384 reset. When the Tsi148 receives a full power-on reset the entire device is reset, including both local (PCI/X) and VMEbus resources.

The Tsi148 drives the SRSTO signal to reset the VME bus backplane. Since SRSTO feeds back into the Tsi148's SRSTI input this causes the Tsi148's local reset output (LRSTO) to be asserted. Additional external reset gating logic may be required to ensure the desired system behavior.

#### 1.3.2.1 PCIe Reset

The Tsi384 receives reset notification from upstream devices and drive reset to downstream devices. In the event of a PCIe reset (Cold, Warm, or Hot), the Tsi384 drives its PCI reset output signal (PCI\_RSTn). When the Tsi384 is configured to operate in master mode clocking and it receives a PCIe reset, the internal clock logic is reset. This causes the clock generator to go into bypass mode, which generates a 25 MHz output on all its external PCI/X clocks.

#### Tsi148 and PCIe Reset

Operating the Tsi384 in master mode clocking limits the reset capabilities of the Tsi148 because the Tsi148 must receive a full power-on reset in the event of a Tsi384 reset. When the Tsi384 receives a PCIe reset, the Tsi148's PCLK input changes from its normal operating frequency to 25 MHz. When the operating frequency is reduced to 25 MHz, the Tsi148's internal PLL loses lock and the entire device must be reset. When the internal PLL loses lock, the Tsi148 requires a full power-on reset so that it can re-sample the PCI/X initialization pattern and its internal PLLs can lock to the incoming PCI/X clock (once stable).

The Tsi148 uses its PCI/X clock input (PCLK) as the reference clock for the entire device. All Tsi148 logic is clocked from the output of an internal PLL that uses PCLK as its reference.

A full, power-on reset means the Tsi148's local resources (PCI/X), as well as VMEbus resources are reset. If the intended application requires that VME resources remain stable during local bus (PCI/X) resets, then slave mode clocking must be used (see "Slave Mode Clocking" on page 5).

#### 1.3.2.2 Reset Timing

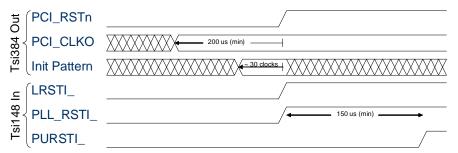

Figure 3 describes the required reset timing between the Tsi384 and Tsi148 when operating in master mode clocking. The reset timing requires the use of on board logic to properly generate the reset inputs to the Tsi148.

Figure 3: Master Mode Clocking Reset Timing

#### Figure 3 notes:

- Both PCI\_CLKO and the Initialization Pattern are stable when PCI\_RSTn is de-asserted and the following occurred:

- PCI\_CLKO is stable approximately 200 microseconds prior to the de-assertion of PCI\_RSTn

- Initialization Pattern is stable approximately 30 clock cycles prior to the de-assertion of PCI\_RSTn

- The Initialization Pattern is held for two additional PCI/X clock cycles following PCI\_RSTn de-assertion

- LRSTI\_ is de-asserted with PCI\_RSTn

- This latches the Initialization Pattern within the Tsi148.

- PLL\_RSTI\_ is de-asserted with PCI\_RSTn

- This guarantees that both clock and Initialization Pattern are stable.

- PURSTI\_ is de-asserted for a minimum of 150 us after PCI\_RSTn is de-asserted.

- This satisfies the timing requirement between PLL\_RST\_ and PURSTI\_.

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

# **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.