# RENESAS

## APPLICATION NOTE

Thermal Characterization and Board Level Modeling of the RSLIC18 in the MLFP Package

AN9922 Rev 0.00 Oct 10, 2001

## Introduction

In most circuit designs, realestate is a premium. This is especially true for the new generation of Home Gateway and Remote

Terminal voice circuits, where some solutions allocate less than one square inch for the SLIC and its components. With the development of Quad and Octal CODECS the SLIC now has a larger share of the solutions real-estate and a larger impact on area reduction. Small packaging has been around for some time, but there has not been a reliable, cost effective solution to significantly reduce the SLIC's area until now. The most significant hurdle has been the power dissipation capability of the package, which has been addressed with a new "Micro Lead Frame" Package technology. The improved thermal dissipation performance comes from the exposed lead frame that is used to help pull heat out of the die with the aid of thermal vias that tie directly to a heat sink plane. With this new technology Designers can take advantage of a 65% reduction in the RSLIC18's footprint (7mm x 7mm) and realize a significant improvement in thermal performance.

The Micro Lead Frame Plastic Package (MLFP) is a JEDEC standard package outline (EIA/JEDEC Publication 95, MO-220) and has several aliases. For example, depending on the manufacturer it may be referred to as a "Micro Lead Frame (MLF), a "Quad Flat No Lead Package" (QFN), or a "Lead Frame Chip Scale Package" (LFCSP).

Figure 1 illustrates a section view of a 16-Lead MLFPpackage. The die pad and perimeter I/O pads are fabricated from a planar copper leadframe substrate. This is encapsulated in plastic with the bottom of the die attach and I/O pads exposed to create a very small footprint "exposed pad" package, ideal for today's dense high power Ringing SLIC solutions.

FIGURE 1. SECTION VIEW OF A 16-LEAD MICRO LEAD FRAME PACKAGE

## The Concept of Thermal Resistance

The term "thermal resistance", denoted by the greek letter "theta" is frequently used to quantify the thermal performance of a packaged integrated circuit. For a semiconductor device the thermal resistance indicates the steady state temperature rise of the die junction above a given reference for each watt of power dissipated at the die surface (degrees centigrade/watt). A component manufacturer typically determines the junction to ambient thermal resistance (Theta-ja) by making physical measurements in a controlled laboratory environment and/or by computer simulation. The data includes the chips junction temperature ( $T_J$ ), the ambient air temperature ( $T_A$ ) in close proximity to the package, and the power dissipated by the IC ( $P_D$ ). The theta-ja is calculated as follows;

Theta-ja  $(\theta_{,IA}) = (Tj - Ta) / Pd$ , in Deg C/W (EQ. 1)

Given the  $\theta_{JA}$  and the power consumed by the die, a system level end user can estimate the die junction temperature from the equation below:

| $Tj = Ta + (\theta_{1A})$ | * Pd) | (EC | Q. 2) |

|---------------------------|-------|-----|-------|

| $I = Ia + (\theta_{IA})$  | FU)   |     | x.    |

## Standardized Test Methods for Thermal Resistance Characterization

Theta-ja has historically been characterized in the laboratory with the device mounted on a variety of standardized printed circuit boards. Performing tests in a standardized way enables the circuit designer to easily compare the thermal performance of one package vs another for a given IC. If a component/package type combination performs better than another in a standardized test it will do so in the real application.

Many companies including Intersil follow the JEDEC EIA/JESD 51-X series standards, which define test methods, conditions and board design criteria. They are available at <u>www.jedec.org</u> under "Free Standards" area. Intersil's TB379 Tech Brief, Thermal Characterization of Packages for ICs provides additional information and references the applicable JEDEC specifications. It is available at <u>www.intersil.com</u> under the Design Support/Packaging Information section.

JEDEC focuses on two types of standard test boards for thermal resistance characterization. The first is the JESD51-3 low effective thermal conductivity test board with 2 ounce (0.070mm thick) surface copper I/O traces. It is commonly called "1S" or "1S0P" for one signal, 0 ground/power planes. The second board type is the JESD51-7 "high effective thermal conductivity" board, and is more applicable for today's

multi layer PCBs. It adds two continuous, one ounce (0.035mm) buried copper planes, and is usually called 1S2P indicating 1 signal (top) and two buried planes. JEDEC has recently added the JESD51-5 "extension" standard for packages with direct thermal attachment mechanisms. This spec provides for surface attachment pads and copper plated thermal vias that connect directly to the upper buried plane of the 1S2P board. This new board type is called the 1S2P-DA where the "DA" stands for "direct attach". It applies to exposed pad packages such as SOIC, TSSOP, TQFP, and the MLFP.

## Power Estimates for Worst Case Conditions

It is important to understand the maximum power the SLIC is expected to dissipate in a given application to ensure safe and reliable operating conditions are met. As noted in the HC5518X data sheets the maximum recommended operating temperature is 150°C. The device also has a temperature sensing circuit on board that will power down the SLIC when the junction temperature exceeds 170°C. A Power Spread sheet is available on the Intersil Web site to assist the designer with this estimate. It can be accessed at <u>www.intersil.com</u> under VoIP Applications.

The worst case scenarios for power consumption are short loop applications. Off-hook operation also referred to as the "Talk Mode" (Forward Active), and Ringing (multiple phones) should be considered. When quantifying the power consumption during ringing, one must factor in the ring cadence which is typically (two seconds ringing, four seconds idle). For example, when ringing 5 phones continuously with a maximum peak-to-peak waveform (190V) the power consumed by the SLIC can exceed 1.25W, however with a ringing cadence of two seconds ringing, four seconds idle the power is reduced to 0.6W. When the transient power pulse (2sec) and the period (6sec) are relatively short as is the case for ringing the phone, the average power and the  $\theta_{IA}$  can be used to accurately predict the Die's junction temperature. Typically the off hook talk mode is the worst case, and under short loop conditions the SLIC will consume 400 to 500mW.

# Thermal Characterization in the MLFP Package

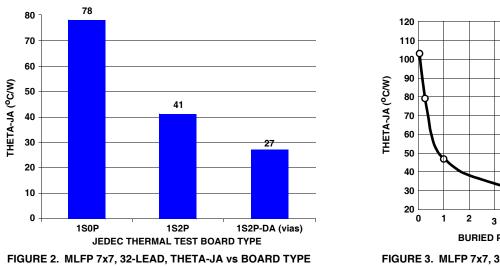

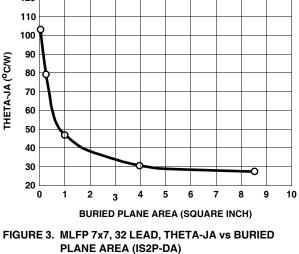

Advancements in thermal modeling have made simulation the preferred method for thermal characterization. With the development and use of Finite Element Analysis (FEA) software, correlation to within 4-8% is routinely achieved between the simulator and laboratory data. Once this very good level of correlation is obtained with the standard JEDEC test boards multiple simulations are performed to generate the data shown in Figures 2 and 3.

Figure 2 summarizes the  $\theta$ ja of the 32 pin MLFP package for the three JEDEC standard test boards for the RSLIC18. Note that without buried planes or thermal vias the package can't dissipate heat effectively (78°C/W, 1SOP) which would significantly limit the application. Adding the buried planes and connecting to the upper plane with conductive vias (1S2P-DA) significantly reduces the  $\theta$ ja to less than 30°C/W (1S2P-DA). Keep in mind that the area of each internal buried plan is 2.92 x 2.92 inches on the test boards and essentially represents an infinite heat sink.

Figure 3 illustrates the effect of various heat sink areas on the  $\theta_{JA}$  of the HC55185 using the 1S2P-DA test board with thermal vias. This data-set is more applicable for the designer as one can probably assume the MLFP package is being used to realize a dense line circuit solution and the heat sink area will be restricted. The data shows that  $\theta_{JA}$ 's of less than  $50^{\circ}$ C/W can be expected with less than one square inch of heat sink area dedicated to the SLIC.

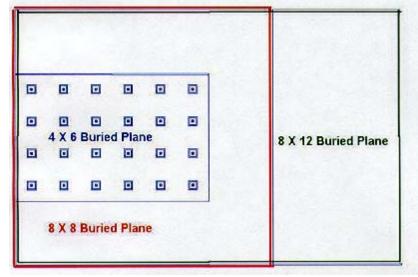

The question that now comes to mind is how do adjacent SLICs interact thermally and what effect does the heat sink plane have on the overall board temperature in a dense line card application? We can simulate these interactions and predict the maximum die and circuit board temperatures with a relatively simple board level model. Figure 4 illustrates the board layout and defines the conditions for the thermal simulations depicted in Figures 5, 6 and 7. For each simulation the SLICs were spaced one inch apart (center to center) in a 4 by 6 array resulting in a packing density of one square inch per device. All units are dissipating 500mW in the Forward Active loop feed mode (talk mode). Note that the only variable changed in the simulations was the area of the heat sink plane. To keep the simulations manageable the model was set up without any top level interconnects representing a worse case condition for thermal conductivity.

#### NOTES:

- 1. Assumes natural convection, board horizontal.

- 2. "DA" board includes "Direct Attach" thermal vias (16 at 0.3mm drill diameter) per JESD 51-5.

- 3. In all cases, the package die pad is soldered to the matching board pad.

- 4. Board metal thickness 100% thick 2 ounce signal, and 95% thick 1 ounce buried copper planes).

### MLFP Package Details

7x7mm-32-pin, 5.3mm pad top, 5.1mm pad bottom.

### **Board Details:**

A 3x4.5" 1S2P-DA ("direct attach") board type with two 1 ounce Cu buried planes and 16 vias connecting to the upper plane only (per JEDEC). On the board surface, traces fan out radially from the surface. As the plane size is decreased, the 2 ounce surface trace lengths are also decreased so that the traces end slightly inside of the plane size. For the  $1/4 \times 1/4$  inch plane, trace lengths are the same as for the  $1/2 \times 1/2$  inch plane (otherwise there would be no traces, they would be too short).

- Units spaced 1 inch apart (center to center)

- Heat sink area = 1 sq inch per device

- All devices active and dissipating 500mW

- Board thickness = 1.6mm

- Buried planes = 1oz copper

- Copper thickness = 0.035mm

- FR4 thickness = 0.375mm top/bottom to buried plane

- FR4 thickness = 0.78mm between buried planes

- 16 conductive thermal vias tied to the upper buried plane

FIGURE 4. BOARD SIZE = 8 INCHES x 12 INCHES WITH VARIOUS HEAT SINK PLANES

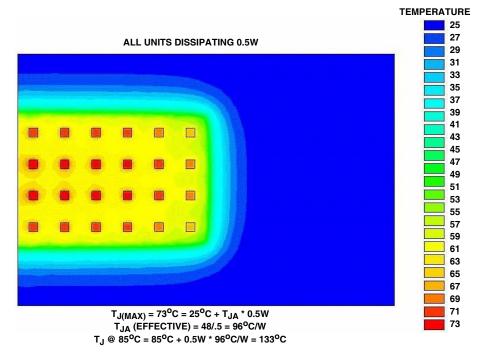

Simulation #1 (Figure 5) restricts to heat sink plan to the area directly under the 4 x 6 array of SLICs creating an effective heat sink area of 1 square inch/device. With an ambient temperature of  $25^{\circ}$ C the maximum die temperature reaches  $73^{\circ}$ C for most units and the board temperature in close proximity to the hottest units reaches approximately  $65^{\circ}$ C. In this instance the heat sink plane is saturated resulting in an effective  $\theta_{JA}$  of  $96^{\circ}$ C/W. Increasing the ambient temperature to  $85^{\circ}$ C would result in a maximum die temperature of  $133^{\circ}$ C which is well within the safe operating temperature range of the SLIC (Max =  $150^{\circ}$ C). Note that the FR4 material is an excellent thermal barrier which could be beneficial for heat sensitive components.

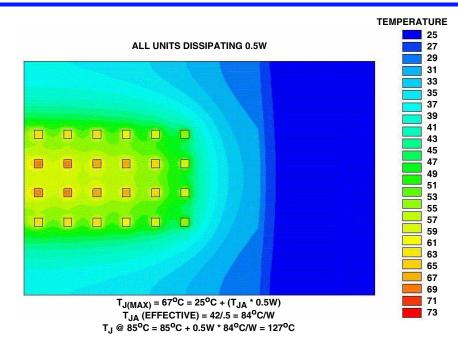

Simulation #2 (Figure 6) increases the heat sink plane to 8 inches x 8 inches providing additional heat sink area to the units on the perimeter of the array. At  $25^{\circ}$ C ambient, the maximum die temperature of  $67^{\circ}$ C is observed on the units in

the two center rows. The additional heat sink area reduces the effective  $\theta_{JA}$  on these devices to 84°C/W. Increasing the ambient temperature to 85°C would result in a maximum die temperature of 127°C.

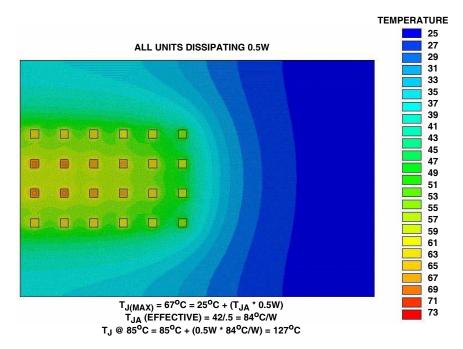

Simulation #3 (Figure 7) shows the effect of increasing the heat sink plane to match the total board area of 8 inches x 12 inches. In this case the additional heat sink area provides little if any improvement in thermal conductivity for the units in the center rows. This suggests that the packing density of one square inch per unit limits the effective  $\theta_{JA}$  to approximately  $84^{\circ}$ C/W for units in the center of the array.

These simulations indicate the heat sink plane can saturate when packing densities are pushed to the extreme, however the resulting  $\theta_{JA}$ 's are more than adequate to keep the device well under the maximum die temperature of 150°C when operating at 85°C ambient.

FIGURE 5. HC55185 BOARD LEVEL THERMAL ANALYSIS WITH TOW 4 X 6 INCH BURIED PLANES

#### Thermal Characterization and Board Level Modeling of the RSLIC18 in the MLFP Package

FIGURE 7. HC55185 BOARD LEVEL THERMAL ANALYSIS WITH TWO 8 x 12 INCH BURIED PLANES

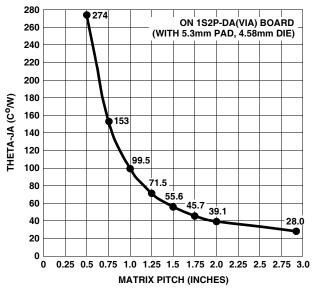

Figure 8 further illustrates the impact of device spacing (pitch) on the effective theta-ja. This graph summarizes the results of 8 simulations where the pitch on an infinite matrix of RSLIC18's is varied from .5 inches to 2.92 inches in .25 inch increments. Note the substantial reduction in effective theta-ja that is obtained with only slight increases in device pitch.

FIGURE 8. THETA-JA vs MATRIX PITCH FOR LARGE SQUARE MATRIX OF 32 PIN 7x7mm MLFPs

## Requirements and Recommendations for Circuit Board Layout

- The lead-frame must be electrically tied to V<sub>BH</sub>. No current flows through the substrate so a current limiting resistor in the order of 100K can be implemented to address any safety issues.

- The electrical connection of the heat sink plane to  $\rm V_{BH}$  should be made on the cathode side of the  $\rm V_{BH}$  protection diode.

- Dedicate an internal power plane to spread the heat and optimize thermal dissipation.

- Make the heat sink plane as large as possible to minimize board and die temperature. Effective heat sink areas of 1 sq inch/device are acceptable.

- Use conductive copper plated vias to make the electrical and thermal tie to the heat sink plane.

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard" Computers: office equipment: communications equipment: test and measurement equipment: audio and visual equipment: home electronic appliances; machine tools; personal electronic equipment: industrial robots: etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc. Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics oroducts outside of such specified ranges

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Plea e contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

#### **Renesas Electronics Corporation**

http://www.renesas.com

SALES OFFICES Refer to "http://www.renesas.com/" for the latest and detailed information Renesas Electronics America Inc. 1001 Murphy Ranch Road, Milpitas, CA 95035, U.S.A. Tel: +1-408-432-8888, Fax: +1-408-434-5351 Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004 Renesas Electronics Europe Limited Dukes Meadow, Miliboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tei: +44-1628-651-700, Fax: +44-1628-651-804 Renesas Electronics Europe GmbH Arcadiastrasse 10, 40472 Düsseldorf, Germar Tel: +49-211-6503-0, Fax: +49-211-6503-1327 Renesas Electronics (China) Co., Ltd. Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679 Renesas Electronics (Shanghai) Co., Ltd. Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0888, Fax: +86-21-2226-0999 Renesas Electronics Hong Kong Limited Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +852-2265-6688, Fax: +852 2886-9022 Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670 Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300 Renesas Electronics Malaysia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amco Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Unit 1207, Block B, Menara Amcorp, Amcorp Tel: +60-3-7955-9390, Fax: +60-3-7955-9510 Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777 Renesas Electronics Korea Co., Ltd. 17F, KAMCO Yangjae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tei: +822-558-3737, Fax: +822-558-5338