Author: Mujammil Ali A S Date: November 26, 2016

### Introduction

Programmable Electronic based controls typically incorporate capability to accomplish safety functions. In the EU for example, compliance to IEC 60730 and IEC 61508 functional safety standards are mandatory. It even covers possible hazards caused by the malfunction of the safety mechanism itself.

Though many MCUs in the market have class B category software mandated by IEC 60730 (to monitor failure of the MCU), there is a need for some use cases to have a double check mechanism for more reliablility.

For instance, consider the opening and closing operation of the gas valve actuator in a boiler. If the MCU controlling it fails, things could be catastrophic.

This App note demonstrates the capability of the SLG46531V to safely drive five output pins on which critical actuators are connected. The SLG46531V monitors a "heartbeat" signal to decide the stability of the MCU.

The MCU sends commands via I2C to switch ON/OFF the output pins.

These Outputs run only during a stable state, and the actuator will always be OFF in any other state.

The advantages of employing this double check mechanism over class B software-only routine running in MCU are as follows:

- The software can crash due to coding oversights in the initial design phase, or software update phase (When adding the new device driver for a new component or existing component in this case).

- Re-certification is required for each software update (in the hardware layer). In contrast, this certification is needed only once if this critical actuator is interfaced directly by an ASIC.

- Though some MCU manufacturers provide digital IO peripheral test as recommended by Annex H of the IEC 60730-1 standard, the end application of a particular digital IO is usually customized, and then differs behaviorally compared to testing time.

## HARDWARE BASED STATE MODEL DRIVEN ACTUATOR

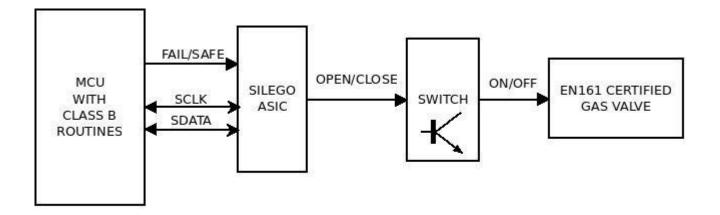

### Figure 1. Typical Application

## Application

In this system, the MCU and the Gas valve driving circuit are isolated by a GreenPAK.

The MCU sends a command to switch ON/OFF the particular IO pin through I2C commands. MCU runs class B self-test periodically to check its stable condition and sends a pulse of frequency (heartbeat signal) less than 23mSec. If Self-test is not OK, MCU stops sending the heartbeat signal.

GreenPAK monitors the heartbeat signal for any unexpected behavior such as no signal or fluctuating signal, and if detected it switches OFF all the output pins. It obeys the I2C command and the output pins allow an OK state only when GreenPAK receives good and stable heartbeat signal. All these operations are driven by the hardware-based ASM (asynchronous state machine) in GreenPAK.

# Auto Lockout Output Driver with safe Reset

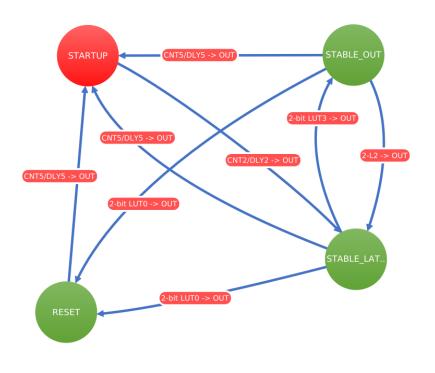

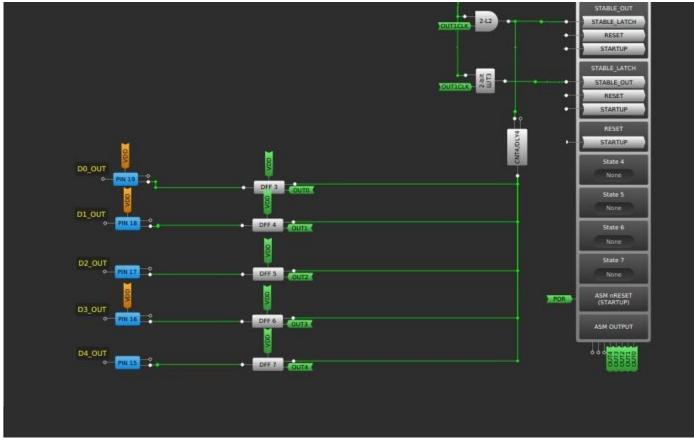

This ASM design drives all five output pins based on the stability indication of MCU. It utilizes four states to accomplish the task. Five ASM RAM bits are connected to D0\_OUT, D1\_OUT, D2\_OUT, D3\_OUT, and D4\_OUT pins to out the commanded value corresponding to STABLE\_OUT state by I2C. Upon start, ASM enters into STARTUP state in which it monitors for the steady pulse with the time period less than 23mSec.

When there is a good healthy pulse, it triggers the STABLE\_LATCH state and then toggles between STABLE\_LATCH and STABLE\_OUT state. This toggling is necessary to reflect the internal ASM RAM table changes made by I2C command to the register address D1.

Figure 2. ASM State Machine

This Register is the only one among all that shall be modified by I2C command. All five output pins are latched using DFF3, DFF4 to DFF7 in STABLE\_OUT and blocked in STABLE\_LATCH state. Once the ASM identifies about non-stability indication either by not receiving the pulse or fluctuation in pulse, it triggers the RESET state in which all output pins are OFF.

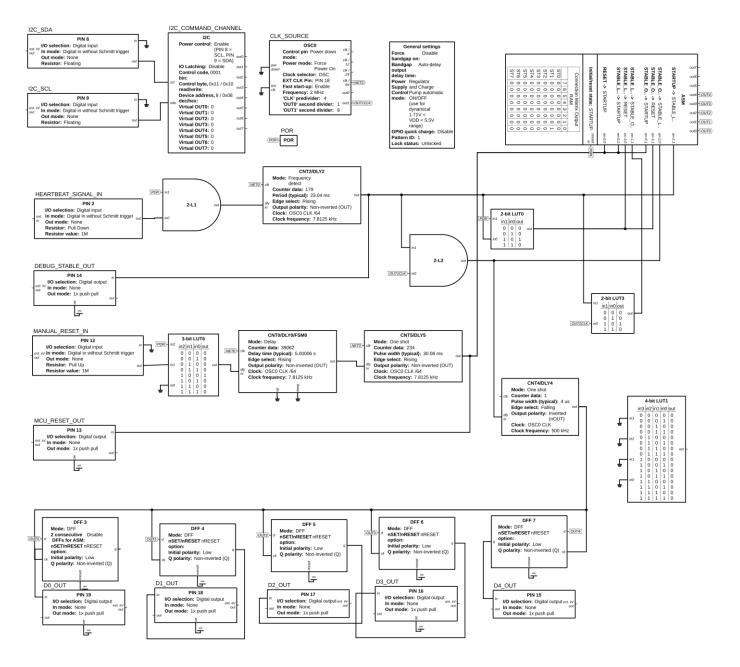

Figure 3. GreenPAK Schematic Overview

|                           | F        | PIN 2                  |            | 3-bit I                | LUT5/    | 8-bit CN            | T2/D                | LY2                 |       | 2      | -bit LU | T2/DFF | LATCH | 12  |     |     |

|---------------------------|----------|------------------------|------------|------------------------|----------|---------------------|---------------------|---------------------|-------|--------|---------|--------|-------|-----|-----|-----|

| I/O selec                 | tion:    | Digital inp            | ut 💌       | Type:                  |          | CNT/DLY             |                     | •                   |       | Туре:  |         | LUT    |       |     |     |     |

| Input mo<br>OE = 0        | ode:     | Digital in without S 💌 |            | Digital in without 5 💌 |          | Mode:               |                     | Frequen             | cy de | tect 💌 |         | IN3    | IN2   | IN1 | INO | OUT |

| Output r                  | node:    |                        |            | -                      |          |                     |                     |                     | 0     | 0      | 0       | 0      | 0     |     |     |     |

| DE = 1                    |          | None                   |            | Counter da             | ata:     | 179                 |                     | \$                  |       | 0      | 0       | 0      | 1     | 0   |     |     |

|                           |          | -                      |            |                        |          | (Range:             | 1 - 25              | and a second second |       | 0      | 0       | 1      | 0     | 0   |     |     |

| Resistor                  | :        | Pull Down              | · · ·      | Period (ty             | pical):  | 23.04 ms            |                     | Formula             |       | 0      | 0       | 1      | 1     | 1   |     |     |

| Resistor                  | value:   | 1M                     | •          |                        |          |                     |                     | Sector Contractor   | -     |        | 1       | 0      | 0     | 0   |     |     |

|                           |          | Edge selec             | ct:        | Rising                 |          | •                   |                     | 0                   | 1     | 0      | 1       | 0      |       |     |     |     |

| Information               |          |                        | Output po  | Output polarity:       |          |                     | Non-inverted (OUT - |                     |       | 1      | 1       | 0      | 0     |     |     |     |

| Electrical Specifications |          | output po              | iancy.     | Homenity               | ateu     | (001 -              |                     | 0                   | 1     | 1      | 1       | 0      |       |     |     |     |

| 1.8 V 3.3 V 5.0 V         |          |                        | Q mode:    |                        | None     |                     |                     |                     | 1     | 0      | 0       | 0      | 0     |     |     |     |

|                           | min/max  |                        |            | Stop and               |          | None                |                     |                     |       | 1      | 0       | 0      | 1     | 0   |     |     |

| _IH (V)                   | 1.060/-  | 1.810/-                |            | restart:               | restart: |                     |                     |                     |       | 1      | 0       | 1      | 0     | 0   |     |     |

| _IL (V)                   | -/0.760  | -/1.310                | 1000000000 |                        | Con      | nection             | 5                   |                     |       | 1      | 0       | 1      | 1     | 0   |     |     |

|                           | -/-      | -/-                    | -/-        |                        |          | 0500.01             |                     |                     |       | 1      | 1       | 0      | 0     | 0   |     |     |

|                           | -/-      | -/-                    | -/-        | Clock:                 |          | OSC0 CLK /64 👻      |                     |                     |       | 1      | 1       | 0      | 1     | 0   |     |     |

|                           | - -      | -/-                    | -/-        | Clock source:          |          | RC OSC Freq. /4 /64 |                     |                     | 1     | 1      | 1       | 0      | 0     |     |     |     |

|                           | -/-      | -/-                    | -/-        | Clock                  |          | 7.8125 kHz          |                     |                     |       | 1      | 1       | 1      | 1     | 0   |     |     |

| 2-                        | bit LUT1 | /DFF/LA                | ICH1       |                        |          | DFF/LA              | тсн                 | 0                   |       |        | 2-bit   | LUT3/F | GEN   |     |     |     |

| Type:                     |          | LUT -                  |            | Type:                  |          | LUT                 |                     |                     | Type: | LUT 👻  |         |        |       |     |     |     |

| IN3                       | IN2      | IN1 II                 | IO OUT     | IN3 11                 | N2       | IN1 II              | NO                  | OUT                 |       | IN3    | IN2     | IN1    | INO   | OUT |     |     |

| 0                         | 0        | 0                      | 0 0        |                        | 0        |                     | 0                   | 001                 |       | 0      | 0       | 0      | 0     | 0   |     |     |

| .0                        | 0        | 0                      | LO         |                        | 0        | 8 1 4               | 1                   | 0                   |       | 0      | 0       | 0      | 1     | 0   |     |     |

| 0                         | 0        | 1                      | 0 0        |                        | 0        | -                   | 0                   | 1                   |       | 0      | 0       | 1      | 0     | 1   |     |     |

| 0                         | 0        | 1                      | 1          |                        | 0        | 8                   | 1                   | 0                   |       | 0      | 0.08    | 1      | 1     | 0   |     |     |

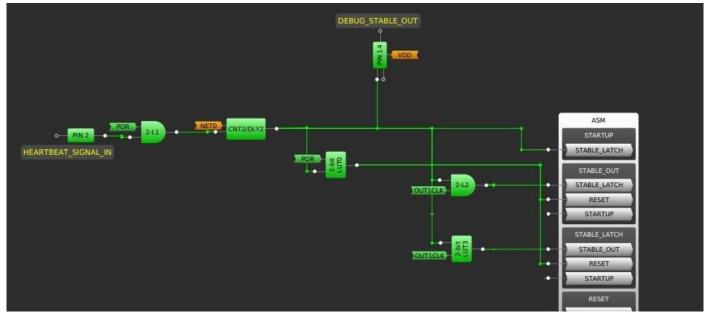

### Figure 4. Configuration of Heartbeat signal monitoring circuit

It never returns to the (STARTUP) normal state until the manual reset operation is carried out by passing LOW signal (by pressing the manual reset button) to MANUAL\_RESET\_IN pin. The manual reset operation is functional as well in all states, and will immediately force the STARTUP state when enabled.

### **Heartbeat Signal Monitor**

Stability of the heartbeat signal of MCU is inferred by measuring the period of the signal at PIN2 which is less than 23mSec. CNT2/DLY2 block is configured in frequency mode with rising edge. The Counter value is set as 179 to capture the signal with the period of 23mSec or less.

The Output of this block is active high when the time period is less than or equal to the said period. It is then complemented with the help of programmed LUT0 block as a NOT gate, acting as a transition signal for RESET state.

The direct non-inverted output is carried to 2-L2 and LUT3 block which is responsible for creating toggling transition signal with the help of clock from STABLE\_LATCH to STABLE\_OUT and vice versa.

Figure 6. Output Latch

# Extended IO Peripheral with Lockout using ASM

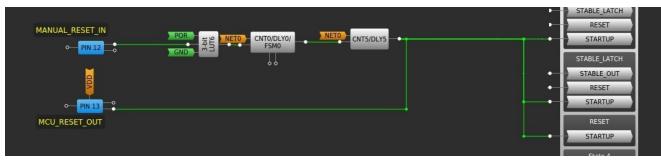

PIN15 to PIN19 are connected with Connection Matrix Output RAM of ASM using DFF7 to DFF3 respectively. Each DFF latches the data during STABLE\_OUT state by the one-shot inverted pulse signal generated from CNT/DLY4. This CNT/DLY4 is configured as one-shot generator upon reception of falling edge from 2-L2. PIN12 is connected to pull down button and looks for pressing the button for more than or equal to 5 Seconds. CNTO/DLYO/FSM0 is configured in delay mode with detection of rising edge for 5 sec. Once the button is pressed, as the Pin is in pull-up mode and LUT6 is in inverted logic, the pin receives low to high transition. If the signal is at the high level for 5 seconds, it triggers the CNT5/DLY5 block that in turn activates the single pulse with a width of 30mSec. This Single pulse is used as a transition signal for STARTUP and routed to MCU through output pin 13.

### Safe Manual Reset

In case an unstable condition arises due to no heartbeat or fluctuating pulse, GreenPAK shuts down the five output pins by making all the corresponding pins as LOW, and requires manual reset to unlock the Output interface and safe reset.

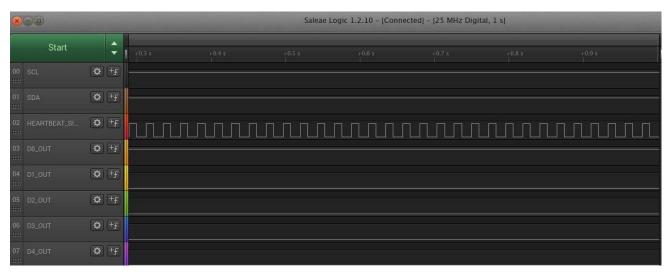

# Monitoring of Stable heartbeat signal at system startup

At System Startup, the heartbeat signal is received as if from the MCU which is emulated using GreenPAK Designer.

| RAM             |       |        |           |         |                |      |      | ×    | L                          |                                  | 3-bit LUT                        | T3/DFF/LATCH6 /  | 3/4 |

|-----------------|-------|--------|-----------|---------|----------------|------|------|------|----------------------------|----------------------------------|----------------------------------|------------------|-----|

| State<br>name   | OUT7  | OUT6 0 | OUTS OUTS | OUT4 Ma | trix O<br>ELDO | OUT2 | TTUO | OUTO |                            |                                  | Туре:                            | DFF / LATCH      | ×   |

| STARTUP         | 0     | 0      | 0         | 0       | 0              | 0    | 0    | 0    | 3-bit LUT7/                | 8-bit CNT4/DLY4                  | Mode:                            | DFF              | •   |

| STABLE_OUT      | 0     | 0      | 0         | 0       | 0              | 0    | 0    | 1    | Type:                      | CNT/DLY -                        | nSET/nRESET<br>option:           | nRESET           | •   |

| STABLE_LAT      | 0     | 0      | 0         | 0       | 0              | 0    | 0    | 0    |                            |                                  | Initial polarity:                | Low              | •   |

| RESET           | 0     | 0      | 0         | 0       | 0              | 0    | 0    | 0    | Mode:                      | One shot 💌                       | Q output<br>polarity:            | Non-inverted (Q) | •   |

| State 4         | 0     | 0      | 0         | 0       | 0              | 0    | 0    | 0    | Counter data:              | 1                                | 3-bit LUT                        | 4/DFF/LATCH7     |     |

| State 5         | 0     | 0      | 0         | 0       | 0              | 0    | 0    | 0    | Pulse width                | (Range: 1 - 255)<br>4 us Formula | Туре:                            | DFF / LATCH      | •   |

| State 6         | 0     | 0      | 0         | 0       | 0              | 0    | 0    | 0    | (typical):<br>Edge select: | Falling 👻                        | Mode:                            | LATCH            | •   |

| Bulk operation: | -     | 0      | 0         | 0       | 0              | 0    | 0    | 0    | Output polarity:           | Inverted (nOUT) 💌                | nSET/nRESET                      | nRESET           | •   |

| All to 0        |       |        |           |         |                | Ŧ    | S    | et   | Q mode:                    | None -                           | Initial polarity:                | Low              | •   |

|                 |       |        | State     | 25      |                |      |      |      | Stop and restart:          | None 🔫                           | Q output<br>polarity:            | Non-inverted (Q) | •   |

|                 |       | ARTU   |           |         |                |      |      |      | Cor                        | nnections                        |                                  | PIN 15/16/17/1   | 8/  |

| ✓ State         | 2 (51 | ABLE   |           |         |                |      |      |      | Clock:                     | OSC0 CLK 👻                       | I/O selection:                   | Digital output   | *   |

| State           | 5     | :SEI)  |           |         |                |      |      |      | Clock source:              | RC OSC Freq. /4                  | Input mode:<br>OE = 0            | None             | -   |

| State           |       |        |           |         |                |      |      |      | frequency:                 | 500 kHz                          | OE = 0<br>Output mode:<br>OE = 1 | 1x push pull     | •   |

|                 |       |        |           |         |                |      |      |      |                            |                                  | Resistor:                        | Floating         |     |

|                 |       |        |           |         |                |      |      |      |                            |                                  | Resistor value:                  | Floating         |     |

Figure 7. Output Pin and ASM Configuration

|                           | F                | PIN 12                   |               |                  |                   |                   |      | 3-bit LUT8/            | 8-bit CNT5/DL          | Y5    |  |

|---------------------------|------------------|--------------------------|---------------|------------------|-------------------|-------------------|------|------------------------|------------------------|-------|--|

| I/O selec                 | tion:            | Digita                   | al input      | · •              |                   |                   |      | Туре:                  | CNT/DLY                | •     |  |

| Input mo<br>OE = 0        | ode:             | Digital in without 5 💌   |               | thout 5 💌        | 4-bit LUT0/WS     | Ctrl/16-bit CN    | то/  | Mode:                  | One shot               | *     |  |

| Output r<br>OE = 1        | mode:            | None -                   |               | -                | Туре:             | CNT/DLY           | •    |                        | Teres a                |       |  |

| Resistor                  | :                | Pull L                   | Jp            | •                | Mode:             | Delay 👻           |      | Counter data:          | 234<br>(Range: 1 - 255 | )     |  |

| Resistor                  | value            | 1M                       |               | •                |                   |                   |      | (typical):             | 30.08 ms               | ormul |  |

| RESISLOI                  | value.           | Tiel                     |               | <u> </u>         | Counter data:     | 39062             | •    | Edge select:           | Rising                 | -     |  |

|                           | Info             | ormati                   | ion           |                  |                   | (Range: 1 - 6553  | 35)  |                        |                        |       |  |

| Electrical Specifications |                  | Delay time<br>(typical): | 5.00006 s     | ormula           | Output polarity:  | Non-inverted (C   |      |                        |                        |       |  |

|                           | 1.8 V<br>min/max |                          | .3 V<br>n/max | 5.0 V<br>min/max | Edge select:      | Rising            | •    | Q mode:                | None                   |       |  |

| V_IH (V)                  | 1.060/-          |                          | B10/-         | 2.680/-          | Output polarity:  | Non-inverted (O   | UT T | Stop and<br>restart:   | None                   |       |  |

| V_IL (V)                  | -/0.760          | -/1                      | .310          | -/1.960          | output polarity.  | inon inverted (o  |      | Connections            |                        |       |  |

| - 1                       | -/-              |                          | -/-           | -/-              | Q mode:           | Reset             |      | COL                    | mecuons                | -     |  |

| 3-bi                      | t LUT6/8         | B-bit C                  | CNT3/I        | DLY3             | Stop and restart: | Disable           | -    | Clock:                 | OSC0 CLK /64           | •     |  |

| Type:                     |                  | LUT                      |               | •                | Cor               | Connections       |      |                        | RC OSC Freq. /4 /64    |       |  |

| IN3                       | IN2              | IN1                      | INO           | OUT              | Clock:            | OSC0 CLK /64      | •    | Clock<br>frequency:    | 7.8125 kHz             |       |  |

| 0                         | 0                | 0                        | 0             | 0                | cioca.            | OSCO CERTON       |      | 1                      | PIN 13                 |       |  |

| 0                         | 0                | 0                        | 1             | 0                | Clock source:     | RC OSC Freq. /4 / | /64  |                        | 1                      |       |  |

| 0                         | 0                | 1                        | 0             | 0                | Clock             | 7.8125 kHz        |      | I/O selection:         | Digital output         |       |  |

| 0                         | 0                | 1                        | 1             | 0                | frequency:        |                   |      | Input mode:            | -                      |       |  |

| 0                         | 1                | 0                        | 0             | 1                |                   |                   |      | OE = 0                 | None                   |       |  |

| 0                         | 1                | 0                        | 1             | 0                |                   |                   |      | Output mode:<br>OE = 1 | 1x push pull           |       |  |

| 0                         | 1                | 1                        | 0             | 0                |                   |                   |      | 02 = 1                 | [                      |       |  |

| 0                         | 1                | 1                        | 1             | 0                |                   |                   |      | Resistor:              | Floating               |       |  |

Figure 8. Manual Reset Circuit Configuration

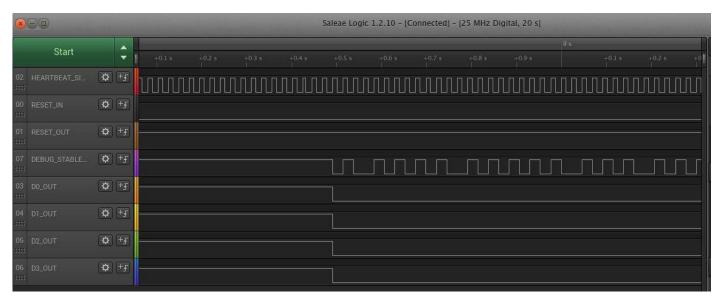

SCL and SDA signals are for the I2C channel. HEARTBEAT\_SIGNAL is a pulse signal that is stable upon start up. D0\_OUT to D4\_OUT refers to the output driver pins among which D0\_OUT is ON. This ON status is due to the initial value present in the ASM output RAM matrix table.

The emulator is configured as follows: TP2 is acting as a signal generator that is used for creating stable and unstable heartbeat signal. TP15, TP16, TP17, TP18, and TP19 are used as output ON/OFF interface.

This design supports five output drivers. TP12 is set as pull down button.

TP13 is the one-shot reset signal for MCU, and unlocks the ASM.

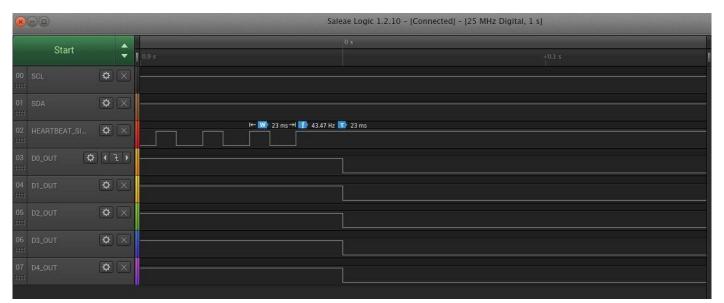

# I2C based Control of Output Interface

The Output matrix of ASM RAM table with address 0xD1 holds the value of all five output drivers from the 0th bit to 5th bit in this byte. I2C command to switch on all output pins is [0x08 0xD1 0x1F]. D0\_OUT to D4\_OUT are switched ON after the I2C command is received. [Device Address: 0x08 Register Address: 0xD1 Value: 0x1F].

### Figure 9. Manual Safe Reset

Figure 10. Waveform of Heartbeat and output signal at system startup

| 800                             | in the second |         | Saleae Lo                         | gic 1.2.10 - [Connected] - [25 MHz | Digital, 1 sj    | -       |

|---------------------------------|---------------|---------|-----------------------------------|------------------------------------|------------------|---------|

| Start                           | ÷             | +0.9 ms | 0 s : 0 ms                        | +0.1 ms                            | +0.2 ms          | +0.3 ms |

| 00 SCL                          | ¢ ( 5 )       | ė_      | Setup Write to ('8' (0x08)] + ACK | 209' (0xD1) + ACK                  | 31' (0x1F) + ACK |         |

| 01 SDA                          | ¢ ×           |         |                                   | _กุรกรุกรารกรุกรา                  | _กากกากกากกา     |         |

| 02 HEARTBEAT_SI.                |               |         |                                   |                                    |                  |         |

| 03 D0_OUT                       |               |         |                                   |                                    |                  |         |

| 04 D1_OUT                       | ð X<br>ð X    |         |                                   |                                    |                  |         |

| 05 D2_OUT<br>;;;;;<br>06 D3_OUT | ¢ ×           |         |                                   |                                    |                  |         |

| 07 D4_OUT                       |               |         |                                   |                                    |                  |         |

|                                 |               |         |                                   |                                    |                  |         |

### **Auto Lockout**

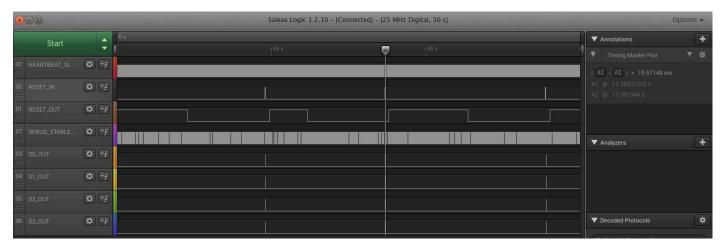

All Output pins are automatically switched to the OFF state when either there is no heartbeat signal or varying unstable heartbeat signal from MCU. The Following Figure 12.A shows that D0\_OUT to D4\_OUT are switched OFF when MCU stops sending the heartbeat signal.

It is understood that when there is a fluctuation in heartbeat signal (in Figure 12.B) shown by DEBUG\_STABLE\_OUT pin, ASM locks into RESET state upon first detection itself. DEBUG\_STABLE\_OUT is the output of frequency detection unit.

Figure 12(a). Auto lockout of Output pins when no or fluctuating heartbeat signal (No Signal)

### Unlocking the System safely using Manual Reset

Once the ASM is in RESET state, it requires manual reset by pressing the button connected in pull-down mode. RESET\_OUT is the signal in the waveform that is generated by the switch; RESET\_IN is the signal name for the signal going to MCU reset pin. Manual reset is the safe operation and avoids automatic triggering of output drivers. Figure 13.A shows that the reset is triggered by a one-shot pulse in RESET\_IN signal when there is a button press for more than 5 Seconds, indicated by RESET\_OUT under the availability of unstable heartbeat signal.

Figure 13(a). Manual Reset in case of unstable situation (During)

| Start |                           | 20 s   |  |  |  |             |  |  |      |  |         | ▼ Annotations       | +  |  |

|-------|---------------------------|--------|--|--|--|-------------|--|--|------|--|---------|---------------------|----|--|

|       | -                         | s +2 s |  |  |  | +7 s 🐼 +8 s |  |  | +2 5 |  | +5 s +6 |                     |    |  |

|       | 🔅 +4                      |        |  |  |  |             |  |  |      |  |         |                     |    |  |

|       | ¢ +f                      |        |  |  |  |             |  |  |      |  |         |                     |    |  |

|       | <b>(¢</b> ) [+ <b>f</b> ] |        |  |  |  |             |  |  |      |  |         |                     |    |  |

|       | ¢ +5                      |        |  |  |  |             |  |  |      |  |         | ▼ Analyzers         | 19 |  |

|       | <b>\$</b>                 |        |  |  |  |             |  |  |      |  |         | · Antiy2013         |    |  |

|       | <b>\$</b> +f              |        |  |  |  |             |  |  |      |  |         |                     |    |  |

|       | ¢ +5                      | 7      |  |  |  |             |  |  |      |  |         |                     |    |  |

|       | <b>⇔</b> + <sub>5</sub>   |        |  |  |  |             |  |  |      |  |         | V Decoded Protocols | \$ |  |

(D4\_OUT waveform is not shown but it was expressly tested).

Figure 13.B shows the manual reset operation after receiving the stable heartbeat signal. In this case, all output pins will reflect the last value sent through I2C channel.

### **MCU Reset**

Once the reset button is pressed more than 5 Seconds, it sends the One-shot pulse (Refer signal named RESET\_IN in the below waveform) to unlock the ASM from RESET state. This same signal is used for host MCU reset. When there is a need to reset the MCU regardless of any lockout error, it is possible to use this signal to do so.

### Conclusion

Functional safety is a primary concern in some of the use cases necessitated by the oil and gas industry, the machinery sector and so on. There is a safety advantage of hardware based GreenPAK ASM over a software approach. In this case, it is an ON/OFF driver driven by SLG46531V IC. The SLG46531V IC catches the undesired situation when pulse period approaches 23 mSec and safely lock out the output driver without fail. The GreenPAK IC helps in isolating the actuator, minimizes hazards, and occupies very little PCB board area.

| 800   |                   |      | Sale | ae Logic 1.2.10 - [0 | Connected] - [25 Mi | Hz Digital, 15 sj |      |      | 0                        | ptions - |

|-------|-------------------|------|------|----------------------|---------------------|-------------------|------|------|--------------------------|----------|

| Start |                   |      | <br> |                      |                     |                   |      | 10 s | Annotations              | C        |

|       |                   | +3 s |      |                      |                     | +8 5              | +9 s |      | Y Timing Marker Pair     |          |

|       | <b>\$</b> +f      |      |      |                      |                     |                   |      |      | AT - A2   = 4.99937284 s |          |

|       | <b>\$</b> +5      |      |      |                      |                     |                   |      |      |                          |          |

|       | <b>₽</b> +        |      |      | 🚻 5.317 s            |                     |                   | └×   |      |                          |          |

|       | ( <b>¢</b> ) [+5] |      |      |                      |                     |                   |      |      |                          |          |

|       |                   |      |      |                      |                     |                   |      |      | ▼ Analyzers              |          |

|       | 🌣 +f              |      |      |                      |                     |                   |      |      |                          |          |

|       | 🗘 +ł              |      |      |                      |                     |                   |      |      |                          |          |

|       | <b>♦</b> +F       |      |      |                      |                     |                   |      |      |                          |          |

|       |                   |      |      |                      |                     |                   |      |      |                          |          |

|       | <b>₽</b> +        |      |      |                      |                     |                   |      |      | Decoded Protocols        | Ŀ        |

Figure 14. RESET signal for host MCU

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.