# RENESAS

### Contents

| Introduction                                        | 2 |

|-----------------------------------------------------|---|

| Method 1: Input Phase Delay Adjustment              | 3 |

| Method 2: Input-to-Output Phase delay Adjustment    |   |

| Method 3: Output Phase Delay Adjustment             | 6 |

| Method 4: Frequency Snap and Phase Snap – 1PPS Snap |   |

| Summary                                             |   |

| References                                          |   |

| Revision History                                    | 9 |

# List of Figures

| Functional Blocks where a Phase Adjustment Can be Made                                   | 2                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output Phase Adjustment by Configuring Input Phase Delay                                 |                                                                                                                                                                                                                                                                                                                              |

| Phase Adjustment by Using Only the Register DPLLx_PHASE_OFFSET                           | 4                                                                                                                                                                                                                                                                                                                            |

| Phase Adjustment by Using both DPLL0_PHASE_OFFSET_CFG and DPLL0_FINE_PHASE_ADV Registers | 5                                                                                                                                                                                                                                                                                                                            |

| Phase Adjustment by Configuring OUT0_PHASE_ADJ                                           | 6                                                                                                                                                                                                                                                                                                                            |

| Enabling Frequency and Phase Snap for DPLL0 to Fast Lock to 1PPS Input                   | 7                                                                                                                                                                                                                                                                                                                            |

| Configuring 1PPS External Feedback                                                       | 8                                                                                                                                                                                                                                                                                                                            |

| DPLL Configurations to Enable 1PPS External Feedback and INPUT9 is Selected              | 8                                                                                                                                                                                                                                                                                                                            |

|                                                                                          | Phase Adjustment by Using Only the Register DPLLx_PHASE_OFFSET<br>Phase Adjustment by Using both DPLL0_PHASE_OFFSET_CFG and DPLL0_FINE_PHASE_ADV Registers<br>Phase Adjustment by Configuring OUT0_PHASE_ADJ<br>Enabling Frequency and Phase Snap for DPLL0 to Fast Lock to 1PPS Input<br>Configuring 1PPS External Feedback |

### List of Tables

### Introduction

The ClockMatrix (CM) family is a new generation of IDT's advanced timing devices. It has built in a rich and powerful set of features to meet the evolving requirements of modern timing and synchronization systems, including Sync-E and IEEE 1588 applications.

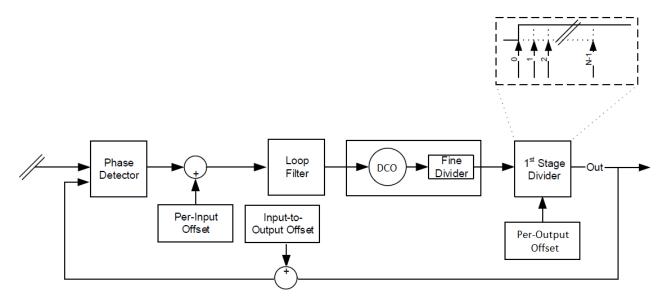

ClockMatrix implements clock phase adjustment at three different locations in the clock path, as shown in Figure 1. The phase adjustment methods include:

- Input clock phase adjustment

- Input-to-output phase adjustment

- Output clock adjustment

### Figure 1. Functional Blocks where a Phase Adjustment Can be Made

In IEEE 1588/PTP applications, 1PPS is used as a basic time reference. In order to align the edge of the local 1PPS and other higher frequency clocks to the network Grandmaster (GM), a "snap" is used to achieve the alignment quickly, instead of adjusting a possible ±500ms phase skew by small increments. Therefore, on top of the three phase adjustment methods, there is a fourth method of phase adjustment in ClockMatrix: 1PPS snap.

The remainder of this document describes how each phase adjustment method works. Table 1 lists the range and the step size of each phase adjustment method.

| Table 1. | Range and Resolution for | Input/Input-to-Output/0 | Output Phase Adjustments |

|----------|--------------------------|-------------------------|--------------------------|

|----------|--------------------------|-------------------------|--------------------------|

| Phase Adjustment at | Range               | Resolution          |

|---------------------|---------------------|---------------------|

| Input               | ±1.6834ms           | 50ps                |

| Input-to-Output     | ±1717.9ms           | 0.391ps             |

| Output              | 1UI of output clock | 1ns (FoD = 1000MHz) |

| 1PPS Snap           | ±500ms              | 50ps                |

# Method 1: Input Phase Delay Adjustment

Input phase adjustment is intended to support clean switchovers. In a system that accepts multiple inputs, phase skew may exist among these input clocks due to different trace lengths or other reasons. When the DPLL is switching from one input clock to another, there will be output phase upsets due to the phase skew of different input clocks. By adjusting these phase skews using input phase delays, the output phase hit is minimized.

A phase adjustment can be made on each of the eight differential inputs (or configured as 16 LVCMOS) independently. The register used to configure the input phase adjustment is INx PHASE, where x = 0...15. The register holds a signed 16-bit value, which means it can be negative or positive. For offset addresses of these registers, search by the register name under the BITS SET tab in Timing Commander GUI.

In Timing Commander, the input phase offset value is configured in the configuration window for the input clock (click at the triangle following each input frequency entry box) (see Figure 2 for the CLK0 configuration window). Hovering the mouse at the "Phase Offset" field will display the address of this input's phase offset register.

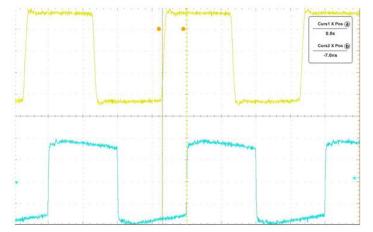

As shown in Figure 2 and the following figures, a negative phase adjustment will move the targeted clock edge to the left on a scope screen, while a positive phase adjustment to the right.

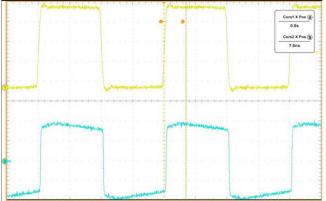

#### **Output Phase Adjustment by Configuring Input Phase Delay** Figure 2.

Phase skew between input and output clocks without any adjustment Phase aligned by adjusting input clock phase delay (INO\_PHASE)

Input clock (yellow trace) leading output clock (blue trace) by 7ns

By setting INO PHASE = -7ns, input clock (yellow trace) and output clock (blue trace) are aligned

The input phase adjustment register is a signed 16-bit register. It can be set with a positive value (the result is the clock edge will move to the right on the scope) or a negative value (the result is that the clock edge will move to the left on the scope).

Inx PHASE register contains a signed 16-bit phase offset value indicating the number of ITDC UIs to adjust the input by. One ITDC UI = (Period of Input TDC frequency)/32. By default, Input TDC frequency is 625MHz. Using this default frequency, the resolution of input clock phase adjustment is (1/625MHz)/32 = 1.6ns/32 = 50ps. The range of this phase adjustment can be calculated by  $\pm 2^{15} \times 50ps = \pm 1.6834ms$ (see Table 1).

The maximum input TDC frequency can be up to 1GHz for differential input clocks.

### Method 2: Input-to-Output Phase delay Adjustment

Input-to-output phase adjustment can be implemented on a per DPLL channel basis. It provides flexible phase adjustments both in wide ranges and in fine resolutions. The limit is that it is per-channel shared. Two outputs driven from the same channel will share the same adjustment value.

Input-to-Output phase offset is implemented by a phase offset on the feedback path from the FoD applied to the phase detector (PD). The phase offset is represented by two registers:

- DPLLx\_PHASE\_OFFSET\_CFG (x = 0...7) This is a signed 36-bit value to define the phase adjustment in either direction: MSB of 1 defines a negative phase delay and MSB of 0 defines a positive phase delay. Since it is a signed register, both negative and positive values can be configured to this register. A negative phase adjustment will move the targeted clock edge to the left as shown in a scope screen, while a positive value to the right.

- DPLLx\_FINE\_PHASE\_ADVANCE (x = 0...7) This is an unsigned 13-bit register to define the fine phase adjustment resolution as input TDC period/4096. For a TDC input TDC clock of 500MHz, this resolution will be 1/500MHz/4096 = 0.4883ps. Please note that this register will take effect only when the DPLL feedback divider is an integer. This register can only hold a positive value.

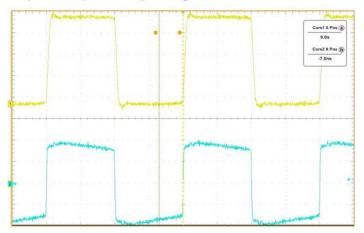

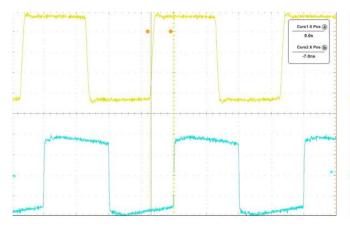

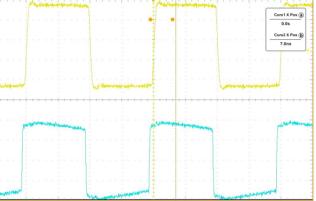

### Figure 3. Phase Adjustment by Using Only the Register DPLLx\_PHASE\_OFFSET

No input-to-output phase adjustment is configured, Input clock leads output clock by 7ns

No phase adjustment is configured. Input clock (yellow trace) is leading the output clock (blue trace) by 7ns

By configuring only DPLL0\_Phase\_Offset, the output clock (blue trace) is not quite aligned with the input clock (yellow trace)

DPLL0\_PHASE\_OFFSET = -128, DPLL0\_FINE\_PHASE\_ADVANCE = 0

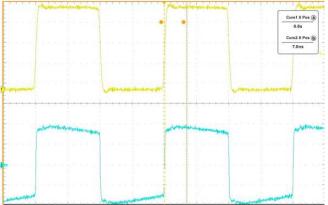

### Figure 4. Phase Adjustment by Using both DPLL0\_PHASE\_OFFSET\_CFG and DPLL0\_FINE\_PHASE\_ADV Registers

No input-to-output phase adjustment is configured, Input clock leads output clock by 7ns

No phase adjustment is configured. Input clock (yellow trace) is leading the output clock (blue trace) by 7ns

By configuring both "coarse" and "fine" phase adjustment registers, input and output clocks are perfectly aligned

By configuring both DPLL0\_Phase\_Offset = -128 and DPLL0\_Fine\_Phase\_Advance = 2048 , the output clock (blue trace) is aligned with the input clock (yellow trace)

On the right-hand side of Figure 4, "coarse" phase adjustment register – DPLL0\_PHASE\_OFFSET\_CFG and "fine" phase adjustment register – DPLL0\_FINE\_PHASE\_ADV are given a value of -128 and 2048, respectively.

DPLL0\_PHASE\_OFFSET defines the phase adjustment equal to the number of ITDC\_UI. ITDC\_UI = 1/(32 input TDC frequency). It can be configured with a negative or positive number. A negative number will move the phase to the left, while a positive number will move the phase to the right. In this example, input TDC frequency is 500MHz. Thus, each ITDC\_UI = 1/(32 500MHz) = 0.0625 ns. As a result, setting DPLL0\_PHASE\_OFFSET\_CFG = -128 will cause a negative phase of -128 \* 0.0625 = -8 ns.

DPLL0\_FINE\_PHASE\_ADV can be set only as a positive number. It defines a phase adjustment in units of input TDC period divided by 4096. From above, input TDC period is 2ns (Input TDC frequency = 500MHz). Thus, a value of 2048 will move the phase by 2048 \* 2ns/4096 = 1ns. Both "coarse" and "fine" registers configured above will have an effect on the phase by -8ns + 1ns = -7ns, compensating the output phase lagging the input phase by the same amount (shown in the left-hand side of Figure 4). After the adjustment, the output and input are phase aligned.

Default input TDC frequency is 625MHz. According to the description above, the DPLLx\_PHASE\_OFFSET\_CFG register can define a phase adjustment resolution of  $\pm 1/(32 * 625MHz) = \pm 50ps$ ; DPLLx\_FINE\_PHASE\_ADVANCE can define a positive phase move in a step size of 1/(4096 \* 625MHz) = 0.391ps.

The maximum input TDC frequency can be up to 1GHz. The resolution as calculated above can get even finer.

# Method 3: Output Phase Delay Adjustment

Output phase adjustment is managed at the integer divider using periods of the FoD clock, and therefore is quite coarse (1~2ns). The upside is that it can be done on a per-output basis.

A phase offset can be adjusted on any of the output clocks, differential or single-ended. The difference from the above two phase adjustment methods is that the output phase adjustment occurs at the integer output dividers after DPLL's FoD (see Figure 1). The register for the output phase offset adjustment is called OUTx\_PHASE\_ADJ, where x = 0...11. It is a signed 32-bit value in units of the FoD period (1nsec – 2nsec depending on FoD configuration) for the FoD driving this divider (for information on which FoD drives which output, see the device block diagram and Output Stages section of the device datasheet).

To configure a phase offset for an output, click on the output to open the OUT Configuration Window, and then enter the phase offset goal in the box. See Figure 5 – a -7ns phase offset is entered for OUT0 which is 125MHz divided from a FoD frequency of 500MHz. Please note output phase adjustment is both positive and negative. Refer to the sections above for how the clock moves with a positive and negative phase adjustment.

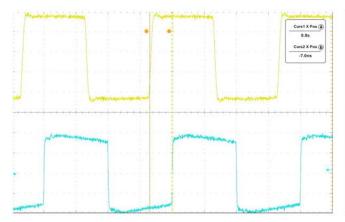

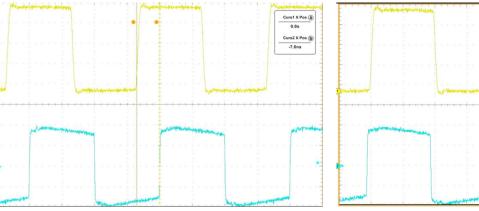

### Figure 5. Phase Adjustment by Configuring OUT0\_PHASE\_ADJ

No input-to-output phase adjustment is configured, Input clock leads output clock by 7ns

|                    | OUT0 Config            |

|--------------------|------------------------|

| Output Label:      |                        |

| Squeich:           | squelch disabled 🛛 🔻 🗂 |

| Squeich Value:     | low 🔹 🗂                |

| Divider:           | 20 📑                   |

| VDDO:              | 3.3V 🔹 🞦               |

| Duty Cycle High:   | 0                      |

| Goal phase adjust: | Ons 🞦                  |

By configuring OUT0\_PHASE\_ADJ = -7ns, due to the resolution of 2ns, it's rounded up to -8ns. Thus the output clock is about 1ns leading the input clock.

No output phase adjustment is configured. Input clock (yellow trace) is leading the output clock (blue trace) by 7ns

By configuring OUT0\_PHASE\_ADJ = -7ns, the output clock (blue trace) is over adjusted by about 1ns due to the resolution of this adjustment.

The resolution of output phase adjustment is based on the FoD frequency. In this example (Figure 5), DPLL0 FoD = 500MHz. The resolution is 2ns. By setting -7ns, the total phase adjustment is rounded up to -8ns. Therefore, the result is shown that the phase-adjusted output clock is about 1ns leading the input clock in the right-hand side portion of Figure 5.

# Method 4: Frequency Snap and Phase Snap – 1PPS Snap

In an application when 1PPS or other frequencies are generated from a DPLL that is locked to a 1PPS input, a few special settings are needed to ensure that fast lock to 1PPS is achieved. Other than the bandwidth of the DPLL, when aiming to lock to 1PPS input mandatory to be set at 17 mHz ( $\leq 1/60$  of input frequency), frequency, and phase snap must be enabled. In Timing Commander, the snap can be enabled as shown in Figure 6.

| Figuro 6  | Enabling Frequency and Phase Snap for DPLL0 to Fast Lock to 1PPS Input |

|-----------|------------------------------------------------------------------------|

| Figure 0. | Enabling Frequency and Fhase Shap for DFLLO to Fast Lock to FFS input  |

| 8A34001               |                                |         |                        |           |

|-----------------------|--------------------------------|---------|------------------------|-----------|

|                       | Diagram                        | в       | it Sets                | Registers |

|                       | Q fastlock                     | All     | · ]                    |           |

| DPLL0 Fastlock Bandw  | idth (DPLL0_FASTLOCK_BW)       | _       |                        | 0         |

| DPLL0 Fastlock Bandw  | idth Unit (DPLL0_FASTLOCK_BW   | UNIT)   | uHz                    | 💌 🛅       |

| DPLL0 Fastlock Dampi  | ng Factor (DPLL0_FASTLOCK_DA   | MP_FTR) | 1.002, 0.02 dB, overda | - 3       |

| DPLL0 Fastlock Freque | ency Slope Limit (DPLL0_FASTLO | CK_FSL) |                        | 0 ゴ       |

| DPLL0 Fastlock Phase  | Slope Limit (DPLL0_FASTLOCK_   | PSL)    |                        | 0 🗂       |

| DPLLO_FASTLOCK_LO     | OCKACQ_FAST_ACQ_EN             |         |                        |           |

| DPLLO_FASTLOCK_LO     | OCKACQ_FREQ_SNAP_EN            |         |                        |           |

| DPLLO_FASTLOCK_LO     | OCKACQ_OL_PULL_IN_EN           |         |                        |           |

| DPLLO_FASTLOCK_L      | OCKACQ_PHASE_SNAP_EN           |         |                        |           |

| DPLLO_FASTLOCK_LO     | OCKREC_FAST_ACQ_EN             |         |                        |           |

| DPLLO_FASTLOCK_LO     | OCKREC_FREQ_SNAP_EN            |         |                        |           |

| DPLLO_FASTLOCK_LO     | OCKREC_OL_PULL_IN_EN           |         |                        | <u></u>   |

| DPLLO_FASTLOCK_LO     | CKREC_PHASE_SNAP_EN            |         |                        | <u> </u>  |

The above settings will enable "automatic" frequency/phase snap. Frequency and phase snap can also be initiated in "manual" mode. To start a manual frequency snap, write a Frequency Control Word (FCW) to DCO (i.e., in write-frequency mode); or write DCO using GPIO increment/decrement (GPIOx\_DCO\_INC\_DEC\_DPLL\_INDEX) with a DCO step size (DPLLx\_DCO\_INC\_DEC\_SIZE). Manual phase snap can be triggered by writing a phase skew to Qn divider or by writing a ToD trigger source (ToDx\_WRITE\_REF\_INDEX[3:0]. For more information, please contact IDT Support.

To adjust output phase alignment with respect to the input 1PPS when locking is achieved, the above three methods – input, input-to-output, and output phase adjustment, are applicable.

To compensate static phase offset inside the device, the external feedback can be used. In such a configuration, a 1PPS output is externally fed back into one of the inputs on top of the primary 1PPS input, as shown in the following Timing Commander configuration window.

# RENESAS

8A34001 Diagran 0 Co e TOD A34001 V5.1.0 SOMH2 7 7 -System DPLL -Cha el 0 DPLL M

### Figure 7. Configuring 1PPS External Feedback

To enable external loopback or to select which input is used for the external loopback, further configurations are needed for DPLL1 as shown in Figure 8.

| K0 Configure                 | Combo Mode - Master (for Filtered source)                                             |

|------------------------------|---------------------------------------------------------------------------------------|

| DPLL Mode                    | Filter input integrator value only 🌱 🎦                                                |

| Combo: System DPLL Channel 3 | Bandwidth: 0                                                                          |

|                              | Units: UHz Image: Comparison of the sum of proportional and integrator of the Master. |

| Channel 1 Configue           | Lock Criteria                                                                         |

| DPLL Mode                    | Error: 6 🙆 * 10ns 🗸 😭                                                                 |

| Combo: System DPLL           | Duration (sec): 1 600ns over 1 second                                                 |

|                              | External Feedback                                                                     |

| Channel 2 Configure          | Enabled:                                                                              |

| LK2<br>DPLL Mode             | Reference: Input 9 (GPIO 15) Y                                                        |

| Combo: System DPLL Channel 3 |                                                                                       |

Please note that 1PPS frequency and phase snap are enabled (as shown in Figure 8) for the external feedback operations.

### Summary

As shown in Figure 2 through Figure 8, the output phase adjustment can be implemented by input, input-to-output, and output phase adjustments. These methods can be used individually or in combination to achieve the desired applications goals in terms of phase alignment among outputs clocks or between an output and an input with a high degree of precision.

Frequency and phase snap are more often used to accelerate 1PPS locking, thus a phase alignment can be achieved more quickly.

### References

- 1. 8A34001 Datasheet, September 26, 2018

- 2. 8A3xxxx Family Programming Guide, V4.7, September 12, 2018

- 3. ClockMatrix GUI Step-by-Step Guide PR4.7

### **Revision History**

| Revision Date    | Description of Change |

|------------------|-----------------------|

| January 18, 2019 | Initial release.      |

### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.