-

-

设计资源

- 设计和开发

- 特色设计工具

- 合作伙伴

- 内容和培训

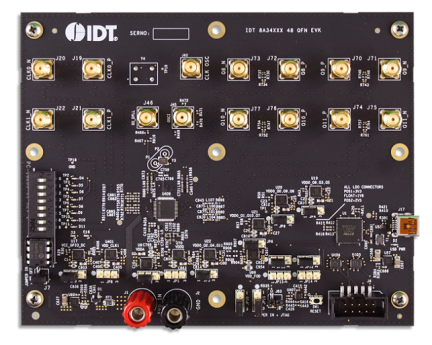

8A34003-EVK

circle有效可提供样片Evaluation Kit for 8A34003 ClockMatrix

概览

简介

This is the evaluation kit for the 8A34003, 8A34004, 8A34013, and 8A34043. The 8A34003 is functionally a superset of these products, making it suitable to evaluate any of the four. Please return to the device product page for more information on each specific device. The 8A34003 provides four independent timing channels that can be configured as Digital PLLs (DPLLs) or as Digitally Controlled Oscillators (DCOs). The DPLL channels can be used for jitter attenuation and frequency translation. The DCOs can be programmed to synthesize the desired frequency and they can be steered by external software with resolution of 1.11E-16. The DPLLs can lock to virtually any frequency from 1kHz to 1GHz and the DPLLs and DCOs can generate virtually any frequency from 0.5Hz to 1GHz with typical jitter below 150fs RMS from 12kHz to 20MHz.

特性

- 2 differential clock inputs

- 12 differential outputs

- 1 serial port channel

- On-board EEPROM

- 7 GPIO controls

- Selectable voltage controls

应用

相关产品

文档

|

|

|

|

|---|---|---|

| 类型 | 文档标题 | 日期 |

| 手册 - 硬件 | PDF 1.99 MB | |

| 应用文档 |

PWM Co-located Carrier, PWM Squelch, and PWM Reference Switching Description for ClockMatrix Devices

登录后下载

PDF

96 KB

|

|

| 原理图 | PDF 199 KB | |

3 items

|

||

产品选择

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product