# Data Converter Datasheet Dual Channel 12b D/A Converter

## Overview

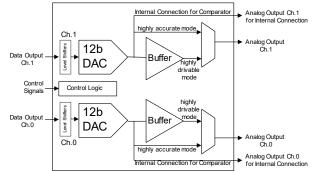

A Dual Channel 12b D/A converter are provided with TSMC T40ULP+ESF3 wafer process. They are voltage output D/A Converter, supporting the wide supply range from 1.62 to 3.63V. The reference voltage can be set independently on the power supply. The linearity is excellent and the transition is fast. They support 2 operation choices; at the 1<sup>st</sup> mode; high buffered mode, they can drive 50pF capacitive load and 5k-ohm resistive load. And at the 2<sup>nd</sup> mode; high accuracy mode, they can show the high linearity from 0 to FS.

#### Block Diagram of Dual Channel DAC

#### Technology

- TSMC T40ULP+ESF3

- Available metallization technologies :7lm4x1z1u, DACs use only 4x1z metals.

## **Key Features**

- 12b resolution, 3us conversion time

- Level Shifter inside. Directly connectable Interface to the digital section.

- Dual channel

- Independent Reference Voltage from the power supply

- Support 2 output mode; highly drivable mode / highly accurate mode.

- High Drivability of 50pF capacitive load and 5k-ohm resistive load at the highly drivable mode.

- Excellent linearity from 0 to FS at the accurate mode.

## **Electrical characteristics**

| Item                                        |                         | Unit     | Spec  |      |          | Description |

|---------------------------------------------|-------------------------|----------|-------|------|----------|-------------|

|                                             |                         |          | MIN   | TYP  | MAX      | Description |

| Power Supply AVCC                           |                         | V        | 1.62  | -    | 3.63     |             |

| Power Supply VDD                            |                         | V        | 0.81  | -    | 1.21     |             |

| Temperature                                 |                         | degree-C | -40   | 25   | 125      |             |

| Output Range                                | highly drivable mode    | V        | 0.2   | -    | AVCC-0.2 |             |

|                                             | highly accurate mode    | V        | 0     | -    | AVCC     |             |

| Conversion time                             |                         | us       | -     | -    | 3        |             |

| Integral Non-Linearity (INL)                |                         | LSB      | -4    | -    | +4       |             |

| Differential Non-Linearity (DNL)            |                         | LSB      | -1    | -    | +1       |             |

| Center Offset Error at highly drivable mode |                         | LSB      | -20   | -    | +20      |             |

| Gain Error                                  | at highly drivable mode | %        | -1    | -    | +1       |             |

| Power<br>consumption                        | highly drivable mode    | mA       | -     | 2.6  | -        |             |

|                                             | highly accurate mode    | mA       | -     | 0.25 | -        |             |

| Area                                        |                         | mm2      | 0.113 |      |          | size on Si  |

\*This IP is contract design IP. Please contact for detail.

Renesas Electronics Corporation www.renesas.com

#### © 2018 Renesas Electronics Corporation. All rights reserved.