# Application Note

# Extending the GreenFET Load Switch Maximum Operating Current

AN-CM-272

#### Abstract

This application note describes how to extend the maximum operating current range of the GreenFET load switches while preserving all protection features. Corresponding oscilloscope captures of operational behavior are included.

### Contents

| Ab  | stract                                                          | . 1 |

|-----|-----------------------------------------------------------------|-----|

| Со  | ntents                                                          | 2   |

| Fig | jures                                                           | 2   |

| 1   | Terms and Definitions                                           | 3   |

| 2   | References                                                      | . 3 |

| 3   | Introduction                                                    | 4   |

| 4   | Using a Pair of SLG59H1006Vs in Parallel                        | 4   |

| 5   | Using a Pair of SLG59M1714Vs in Parallel                        | 11  |

| 6   | Using a Single, High-current GreenFET Load Switches SLG59M1568V | 15  |

| 7   | Recommended PCB Layouts                                         | 18  |

| 8   | Conclusions                                                     | 19  |

| Re  | vision History                                                  | 20  |

### **Figures**

| Figure 2: Two SLG59H1006Vs Op<br>C <sub>SLEW</sub> = 18 nF, R <sub>LOAD</sub> = 100 $\Omega$ , C <sub>LO</sub> ,<br>Figure 3: Two SLG59H1006Vs Op<br>C <sub>SLEW</sub> = 18 nF, R <sub>LOAD</sub> = 100 $\Omega$ , C <sub>LO</sub> ,<br>Figure 4: Two SLG59H1006Vs Op<br>C <sub>SLEW</sub> = 18 nF, R <sub>LOAD</sub> = 100 $\Omega$ , no (C<br>Figure 5: Two SLG59H1006Vs Op<br>C <sub>SLEW</sub> = 18 nF, R <sub>LOAD</sub> = 100 $\Omega$ , no (C<br>Figure 6: Two SLG59H1006Vs Op<br>C <sub>SLEW</sub> = 18 nF, R <sub>LOAD</sub> = 100 $\Omega$ , C <sub>LO</sub><br>Figure 7: Two SLG59H1006Vs Op<br>C <sub>SLEW</sub> = 18 nF, R <sub>LOAD</sub> = 100 $\Omega$ , C <sub>LO</sub><br>Figure 7: Two SLG59H1006Vs Op<br>C <sub>SLEW</sub> = 18 nF, R <sub>LOAD</sub> = 100 $\Omega$ , C <sub>LO</sub><br>Figure 8: Two SLG59H1006Vs Op<br>V, C <sub>SLEW</sub> = 18 nF, I <sub>ACL</sub> = 12 A, R <sub>SET</sub> | erating in Parallel: Turn ON Operating in Parallel: Turn OFF op CLOAD, Load Enable = HIGH<br>erating in Parallel: Turn OFF op CLOAD, Load Enable = HIGH<br>erating in Parallel: Turn OFF op CLOAD, Load Enable = HIGH<br>erating in Parallel: Turn OFF op CLOAD, Load Enable = HIGH<br>erating in Parallel: Turn OFF op AD = 10 $\mu$ F, Load Enable = HIGH<br>erating in Parallel: Turn OFF op AD = 10 $\mu$ F, Load Enable = HIGH<br>erating in Parallel: Turn OFF op AD = 10 $\mu$ F, Load Enable = HIGH<br>erating in Parallel: Turn OFF op AD = 10 $\mu$ F, Load Enable = HIGH<br>erating in Parallel: ACL with SO CLUE = 15 k $\Omega$ , R <sub>L</sub> | $ \begin{array}{l} \text{H} & \dots & 5 \\ \text{eration; } V_{\text{LOGIC}} = 5 \text{ V, } V_{\text{IN}} = 12 \text{ V,} \\ \text{H} & \dots & 5 \\ \text{eration; } V_{\text{LOGIC}} = 5 \text{ V, } V_{\text{IN}} = 5 \text{ V,} \\ \text{meration; } V_{\text{LOGIC}} = 5 \text{ V, } V_{\text{IN}} = 12 \text{ V,} \\ \text{H} & \dots & 7 \\ \text{H} & \text{eration; } V_{\text{LOGIC}} = 5 \text{ V, } V_{\text{IN}} = 12 \text{ V,} \\ \text{H} & \dots & 7 \\ \text{H} & \dots & 7 \\ \text{H} & \text{Operation; } V_{\text{LOGIC}} = 5 \text{ V, } V_{\text{IN}} = 12 \text{ V,} \\ \text{H} & \dots & 7 \\ \text{H} & \dots & 7 \\ \text{H} & \text{Operation; } V_{\text{LOGIC}} = 5 \text{ V, } V_{\text{IN}} = 12 \text{ V,} \\ \text{H} & \dots & 7 \\ \text{H} & \text{Operation; } V_{\text{LOGIC}} = 5 \text{ V, } V_{\text{IN}} = 12 \end{array} $                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V, C <sub>SLEW</sub> = 18 nF, I <sub>ACL</sub> = 12 A, R <sub>SET</sub> .<br>HIGH<br>Figure 10: Two SLG59H1006Vs O<br>5 A R <sub>IOUT_U1</sub> = 84.5 kΩ, C <sub>IOUT_U1</sub> = 1<br>Figure 11: Application Diagram of u<br>Figure 12: Two SLG59H1006Vs O<br>12 V, I <sub>DS</sub> = 5 A, R <sub>IOUT</sub> = 44.2 kΩ, C <sub>I</sub><br>Figure 13: Application Diagram of u<br>Figure 14: Two SLG59M1714Vs O<br>R <sub>LOAD</sub> = 100 Ω, C <sub>LOAD</sub> = 10 µF, Loa<br>Figure 16: Two SLG59M1714Vs O<br>R <sub>LOAD</sub> = 100 Ω, no C <sub>LOAD</sub> , Load Ena<br>Figure 16: Two SLG59M1714Vs O                                                                                                                                                                                                                                                                                                            | = 15 kΩ, R <sub>SET_U2</sub> = 15 kΩ, R <sub>L</sub><br>perating in Parallel: IOUT opera<br>80 pF, R <sub>IOUT_U2</sub> = 84.5 kΩ, C <sub>IOUT</sub><br>using two SLG59H1006Vs in pa<br>perating in Parallel: Common IC<br><sub>OUT</sub> = 180 pF, ON = HIGH<br>using a pair of SLG59M1714Vs<br>perating in Parallel: Turn ON Op<br>d Enable = HIGH<br>perating in Parallel: Turn OFF C<br>able = HIGH                                                                                                                                                                                                                                                                                                                                                    | $\begin{array}{l} {}_{\text{OAD}} = 1.4 \ \Omega, \ C_{\text{LOAD}} = 10 \ \mu\text{F}, \ \text{ON} = \\ {}_{\text{9}} \\ {}_{\text{ntion; } V_{\text{LOGIC}} = 5 \ \text{V}, \ \text{V}_{\text{IN}} = 12 \ \text{V}, \ \text{Ibs} = \\ {}_{\text{1}_{\text{0}}\text{2}_{\text{2}}} = 180 \ \text{pF}, \ \text{ON} = \text{HIGH} \dots 10 \\ {}_{\text{0}} \\ {}_{\text{0}} \\ {}_{\text{1}}\text{allel with common IOUT pins } \dots 10 \\ {}_{\text{0}}\text{DUT operation; } \ \text{V}_{\text{LOGIC}} = 5 \ \text{V}, \ \text{V}_{\text{IN}} = \\ {}_{\text{11}} \\ {}_{\text{11}} \\ {}_{\text{11}} \\ {}_{\text{11}} \\ {}_{\text{11}} \\ {}_{\text{peration; } \ \text{V}_{\text{DD}} = 5 \ \text{V}, \ \text{V}_{\text{IN}} = 5 \ \text{V}, \\ {}_{\text{12}} \\ \\ {}_{\text{0}} \\ {}_{\text{0}} \\ {}_{\text{12}} \\ \\ {}_{\text{0}} \\ {}_{\text{peration; } \ \text{V}_{\text{DD}} = 5 \ \text{V}, \ \text{V}_{\text{IN}} = 5 \ \text{V}, \\ {}_{\text{12}} \\ \\ {}_{\text{0}} \\ {}_{\text{13}} \end{array} $ |

| Application Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Revision 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22-Feb-2019                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 17: Two SLG59M1714Vs Operating in Parallel: ACL with thermal protection operation; $V_{DD} = 5$ V, $V_{IN} = 5$ V, $I_{ACL} = 8$ A, $R_{SET\_U1} = 20$ k $\Omega$ , $R_{SET\_U2} = 20$ k $\Omega$ , $R_{LOAD} = 0.6$ $\Omega$ , $C_{LOAD} = 10$ µF, ON = HIGH 13                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 18: Two SLG59M1714Vs Operating in Parallel: Independent Iout operation; $V_{DD} = 5 \text{ V}$ , $V_{IN} = 5 \text{ V}$ , $I_{DS} = 4 \text{ A}$ , $R_{IOUT}U1 = 10 \text{ k}\Omega$ , $C_{IOUT}U1 = 10 \text{ nF}$ , $R_{IOUT}U2 = 10 \text{ k}\Omega$ , $C_{IOUT}U2 = 10 \text{ nF}$ , $ON = HIGH$                                                                                                                                                                                                                                                                                                                                         |

| 14Figure 19: Application Diagram of using two SLG59M1714Vs in parallel with common IOUT pins 14Figure 20: Two SLG59M1714Vs Operating in Parallel: Common IOUT operation; $V_{DD} = 5 V$ , $V_{IN} = 5 V$ , $I_{DS} = 4 A$ , $R_{IOUT} = 4.99 k\Omega$ , $C_{IOUT} = 10 nF$ , $ON = HIGH$ 15Figure 21: Application Diagram of using SLG59M1568V15Figure 22: SLG59M1568V Turn ON Operation; $V_{DD} = 5 V$ , $V_{IN} = 5 V$ , $C_{SLEW} = 4.7 nF$ , $R_{LOAD} = 20 \Omega$ , $C_{LOAD} = 10 \ \mu$ F, Load Enable = HIGH16Figure 23: SLG59M1568V Turn OFF Operation; $V_{DD} = 5 V$ , $V_{IN} = 5 V$ , $C_{SLEW} = 4.7 nF$ , $R_{LOAD} = 20 \Omega$ , |

| no C <sub>LOAD</sub> , Load Enable = HIGH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

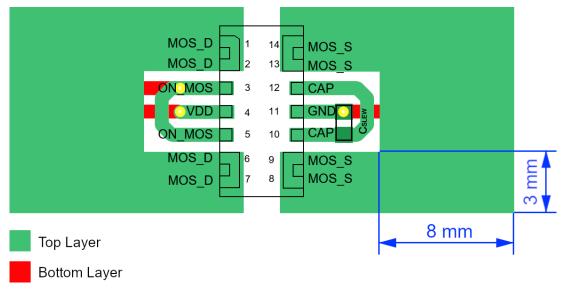

| Figure 28: Recommended PCB layout for using a SLG59M1568V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

### **1** Terms and Definitions

- SOA Safe Operation Area

- PCB Printed Circuit Board

#### 2 References

- [1] SLG59H1006V, Datasheet

- [2] SLG59M1714V, Datasheet

- [3] SLG59M1568V, Datasheet

- [4] AN-1068, GreenFET and High Voltage GreenFET Load Switch Basics, Application Note

#### 3 Introduction

Some applications require a load switch to control high drive currents. One way to address this application requirement is to select a load switch with a higher current handling capability at least 20% higher than the usage scenario's maximum steady-state requirement. However, if such a product exists, the solution may very well occupy a larger PCB area, may consume more power, and may be quite expensive. Another option is to use two, lower-IDS-rated, lower-priced GreenFET load switches in parallel. An immediate benefit in using two GreenFET load switches in parallel is a smaller overall RDS<sub>ON</sub> while maintaining low supply current consumption when both GreenFET load switches are ON. Renesas's proprietary MOSFET design and driver IP has the distinct advantage of very low part-to-part RDS<sub>ON</sub> variation and thus current sharing between two GreenFET load switches in parallel is very well balanced.

#### 4 Using a Pair of SLG59H1006Vs in Parallel

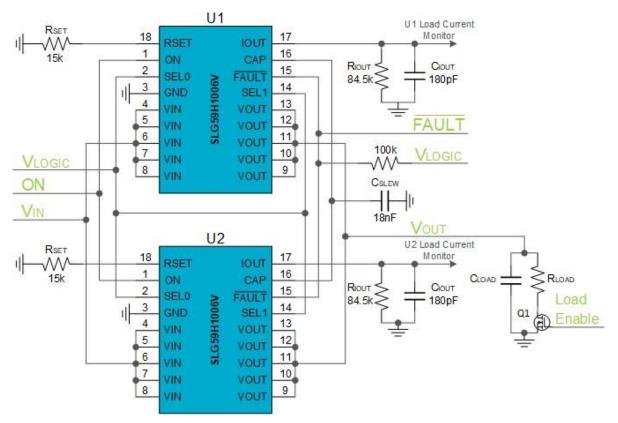

One of the GreenFET load switches that can be connected in parallel is the HFET1 line of 13.2- and 25.2-V GreenFET load switches. As an example, a pair of SLG59H1006Vs will be illustrated with its corresponding application circuit shown in Figure 1. The SLG59H1006V is a high-performance, self-powered 13.1 m $\Omega$  NMOS load switch designed for all 4.5 V to 22 V power rails up to 5 A. Using a proprietary MOSFET design, the SLG59H1006V achieves a stable 13.1 m $\Omega$  RDS<sub>ON</sub> across a wide input voltage range. In combining novel FET design and copper pillar interconnects, the SLG59H1006V package also exhibits a low thermal resistance for high-current operation.

Typical operational waveforms of this parallel GreenFET load switch solution are illustrated in Figure 2 through Figure 7.

|    | 11 C 1 |      |      |

|----|--------|------|------|

| nn | lica   | tion | Note |

| P٢ | nou    | uon  | HOLO |

**Revision 1.0**

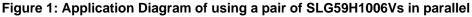

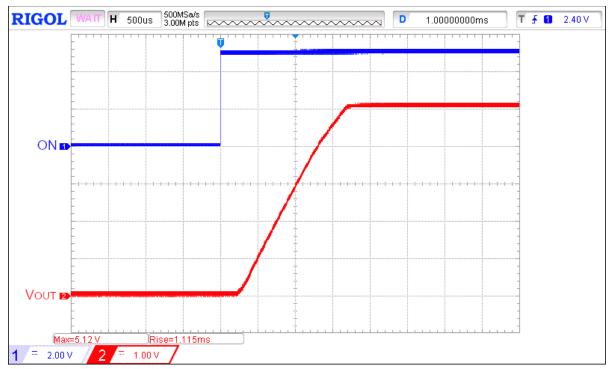

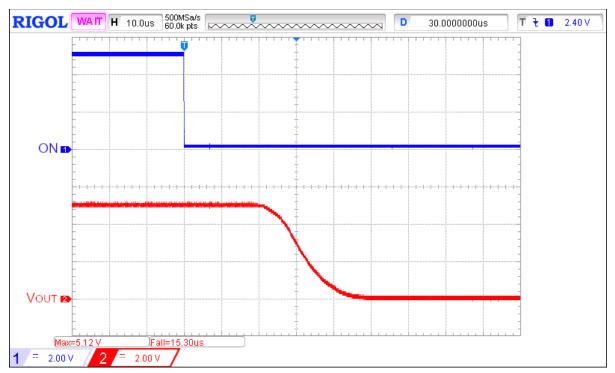

Figure 2: Two SLG59H1006Vs Operating in Parallel: Turn ON Operation;  $V_{LOGIC} = 5 V$ ,  $V_{IN} = 5 V$ ,  $C_{SLEW} = 18 nF$ ,  $R_{LOAD} = 100 \Omega$ ,  $C_{LOAD} = 10 \mu F$ , Load Enable = HIGH

Figure 3: Two SLG59H1006Vs Operating in Parallel: Turn ON Operation;  $V_{LOGIC} = 5 V$ ,  $V_{IN} = 12 V$ ,  $C_{SLEW} = 18 nF$ ,  $R_{LOAD} = 100 \Omega$ ,  $C_{LOAD} = 10 \mu$ F, Load Enable = HIGH

| <u> </u> |          |      |

|----------|----------|------|

| App      | lication | Note |

**Revision 1.0**

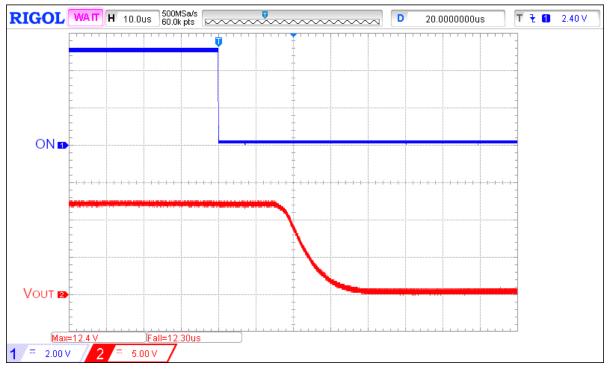

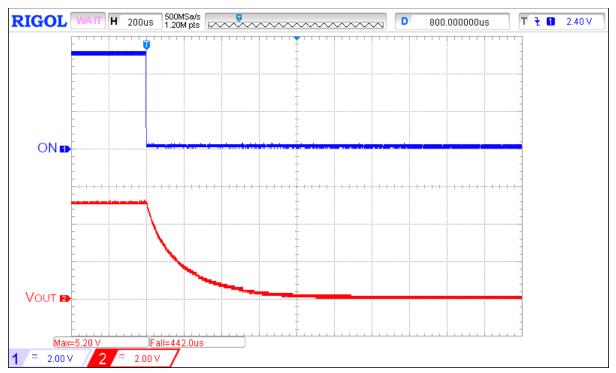

Figure 4: Two SLG59H1006Vs Operating in Parallel: Turn OFF operation;  $V_{LOGIC} = 5 V$ ,  $V_{IN} = 5 V$ ,  $C_{SLEW} = 18 nF$ ,  $R_{LOAD} = 100 \Omega$ , no  $C_{LOAD}$ , Load Enable = HIGH

Figure 5: Two SLG59H1006Vs Operating in Parallel: Turn OFF operation;  $V_{LOGIC} = 5 V$ ,  $V_{IN} = 12 V$ ,  $C_{SLEW} = 18 nF$ ,  $R_{LOAD} = 100 \Omega$ , no  $C_{LOAD}$ , Load Enable = HIGH

| Applic | ation | Note |

|--------|-------|------|

**Revision 1.0**

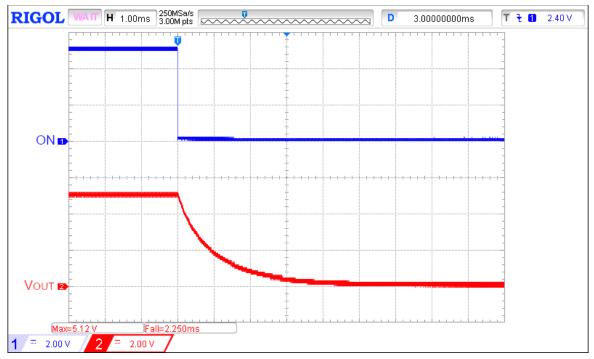

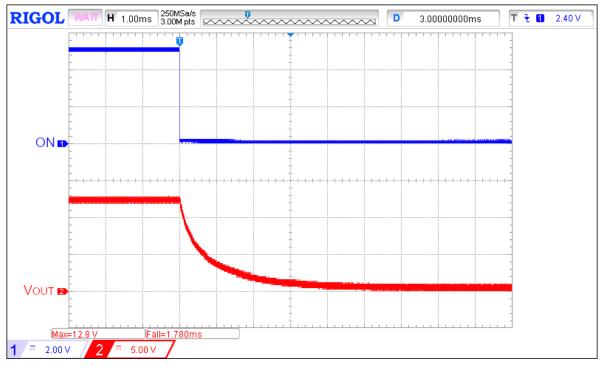

Figure 6: Two SLG59H1006Vs Operating in Parallel: Turn OFF operation;  $V_{LOGIC} = 5 V$ ,  $V_{IN} = 5 V$ ,  $C_{SLEW} = 18 nF$ ,  $R_{LOAD} = 100 \Omega$ ,  $C_{LOAD} = 10 \mu$ F, Load Enable = HIGH

Figure 7: Two SLG59H1006Vs Operating in Parallel: Turn OFF operation; V<sub>LOGIC</sub> = 5 V, V<sub>IN</sub> = 12 V, C<sub>SLEW</sub> = 18 nF, R<sub>LOAD</sub> = 100 Ω, C<sub>LOAD</sub> = 10 μF, Load Enable = HIGH

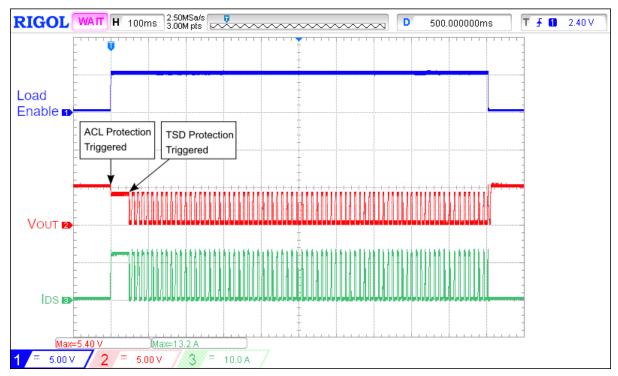

A circuit configuration like this one retains all the SLG59H1006V's protection features: active current limit (ACL), short circuit protection (SCL), inrush current control, thermal shutdown, and FET safe

**Application Note**

**Revision 1.0**

operation area (SOA). For inrush current control, separate capacitors at each CAP pin of U1 and U2, as well as a common capacitor for both CAP pins can be used. It should be noted that in the case of a common capacitor at CAP pins, VOUT ramp time will be twice as fast when compared to the case for same CSLEW value at each CAP pin. This is caused by the fact that the slew capacitor is being charged by two GreenFET load switches simultaneously. This common CSLEW configuration is preferred as both GreenFET load switches will power up simultaneously. Since the ACL for both GreenFET load switches is set to 6 A with external resistors to the RSET pins, the ACL of the overall circuit is 12 A. Corresponding operating waveforms for different input voltages are presented in Figure 8 and Figure 9.

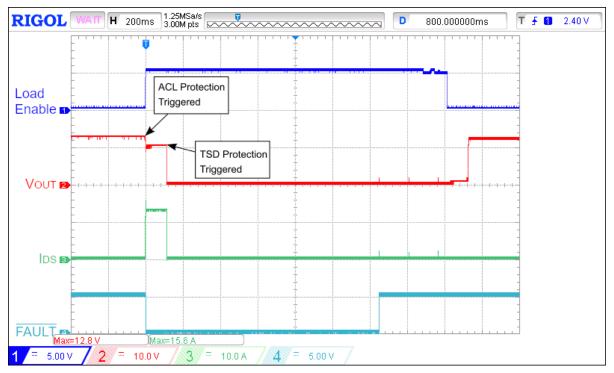

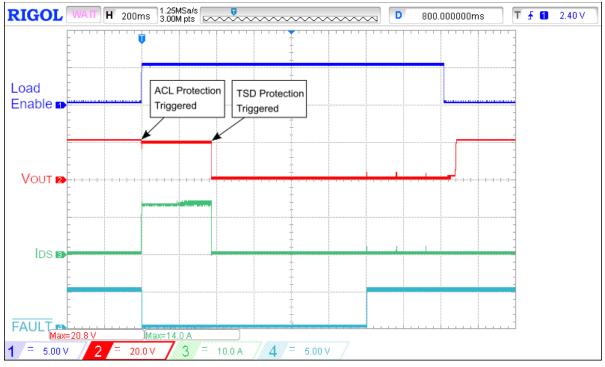

Figure 8: Two SLG59H1006Vs Operating in Parallel: ACL with SOA operation;  $V_{LOGIC} = 5 V$ ,  $V_{IN} = 12 V$ ,  $C_{SLEW} = 18 nF$ ,  $I_{ACL} = 12 A$ ,  $R_{SET\_U1} = 15 k\Omega$ ,  $R_{SET\_U2} = 15 k\Omega$ ,  $R_{LOAD} = 0.8 \Omega$ ,  $C_{LOAD} = 10 \mu$ F, ON = HIGH

Figure 9: Two SLG59H1006Vs Operating in Parallel: ACL with SOA operation;  $V_{LOGIC} = 5 V$ ,  $V_{IN} = 20 V$ ,  $C_{SLEW} = 18 nF$ ,  $I_{ACL} = 12 A$ ,  $R_{SET\_U1} = 15 k\Omega$ ,  $R_{SET\_U2} = 15 k\Omega$ ,  $R_{LOAD} = 1.4 \Omega$ ,  $C_{LOAD} = 10 \mu F$ , ON = HIGH

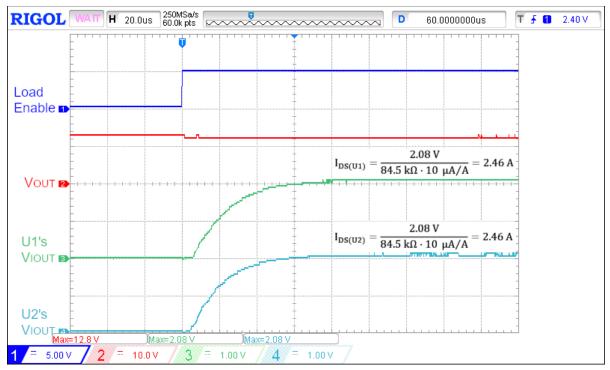

There are two implementations for current monitoring of such a system. The first one is to monitor currents through each GreenFET load switch using their component IOUT pins as was shown in Figure 1. In this case, each IOUT will generate a 10  $\mu$ A/A transfer characteristic. The corresponding waveform is presented in Figure 10.

Figure 10: Two SLG59H1006Vs Operating in Parallel: IOUT operation;  $V_{LOGIC} = 5 V$ ,  $V_{IN} = 12 V$ , Ibs = 5 A Riout\_u1 = 84.5 k $\Omega$ , Ciout\_u1 = 180 pF, Riout\_u2 = 84.5 k $\Omega$ , Ciout\_u2 = 180 pF, ON = HIGH

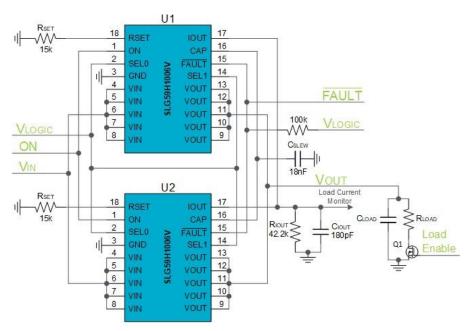

A second way is to monitor the load current of the whole circuit by connecting component IOUT pins together. Such a connection is illustrated in Figure 11. In this case, the combination circuit will also generate a 10  $\mu$ A/A transfer characteristic; however, the IOUT resistor should be changed to extend current measurement range and this should be taken into consideration. The operating waveform is shown in Figure 12.

Figure 11: Application Diagram of using two SLG59H1006Vs in parallel with common IOUT pins

Figure 12: Two SLG59H1006Vs Operating in Parallel: Common IOUT operation;  $V_{LOGIC} = 5 V$ ,  $V_{IN} = 12 V$ ,  $I_{DS} = 5 A$ ,  $R_{IOUT} = 44.2 k\Omega$ ,  $C_{IOUT} = 180 pF$ , ON = HIGH

#### 5 Using a Pair of SLG59M1714Vs in Parallel

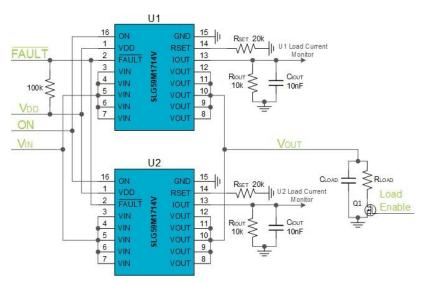

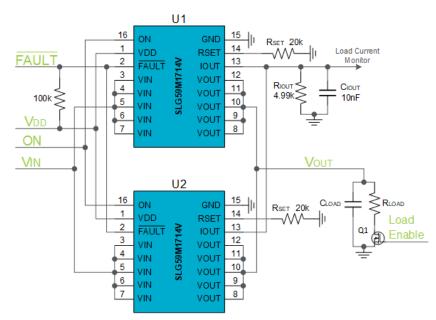

For V<sub>IN</sub> voltages up to 5.5 V and load current higher than 4 A, a SLG59M1714V GreenFET load switch can be configured in a similar fashion to that of the SLG59H1006V. Operating from 2.5 V to 5.5 V supply voltage, the SLG59M1714V is a 15 m $\Omega$ , 4 A single channel GreenFET load switch with back-to-back reverse-current blocking when OFF. Incorporating two-stage current protection as well as thermal protection and fault signaling, the SLG59M1714V is designed for all 0.8 V to 5.5 V power rail applications. Typical application connection using two SLG59M1714V in parallel is illustrated in Figure 13.

Figure 13: Application Diagram of using a pair of SLG59M1714Vs in parallel

|  | Application Note | Revision 1.0 | 22-Feb-2019 |

|--|------------------|--------------|-------------|

|--|------------------|--------------|-------------|

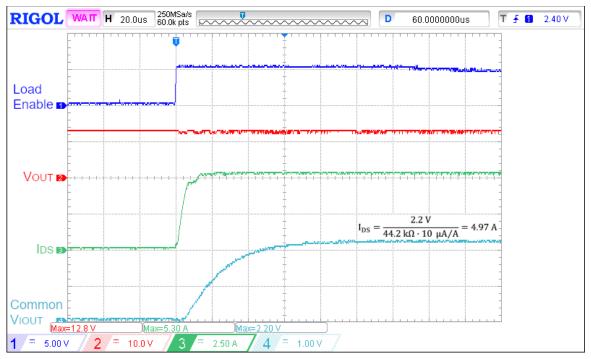

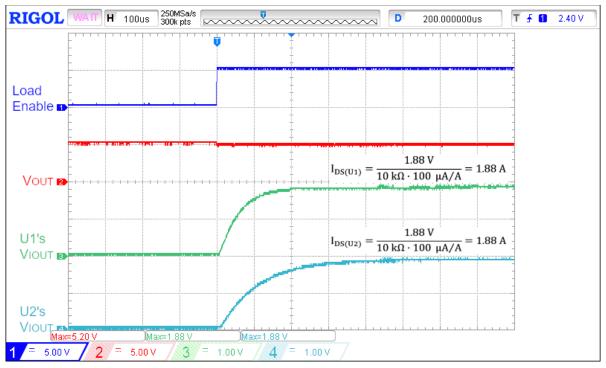

As shown in Figure 13, the component IOUT pins are separated to independently monitor current through each power MOSFET. The SLG59M1714V's IOUT transfer characteristic is 100  $\Box$ A/A and this should be considered when choosing resistor on IOUT pin. Typical operational waveforms of this GreenFET load switch solution are illustrated from Figure 14 through Figure 18.

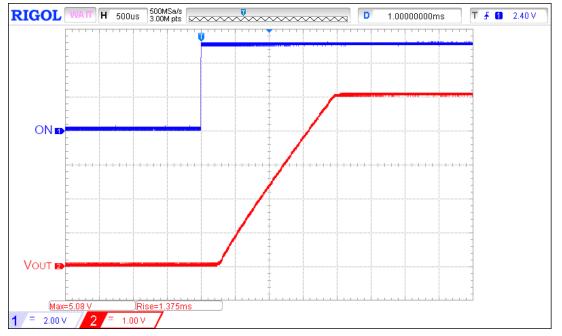

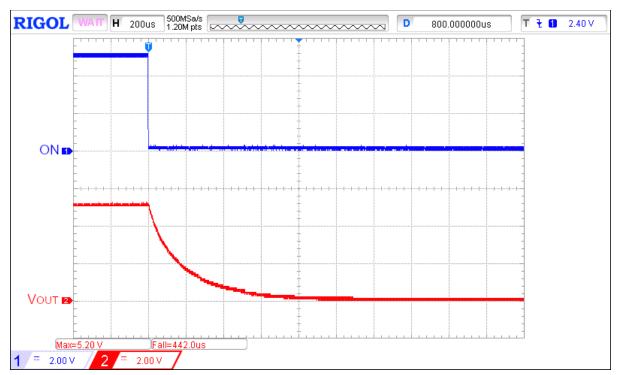

Figure 14: Two SLG59M1714Vs Operating in Parallel: Turn ON Operation;  $V_{DD} = 5 V$ ,  $V_{IN} = 5 V$ , R<sub>LOAD</sub> = 100  $\Omega$ , C<sub>LOAD</sub> = 10  $\mu$ F, Load Enable = HIGH

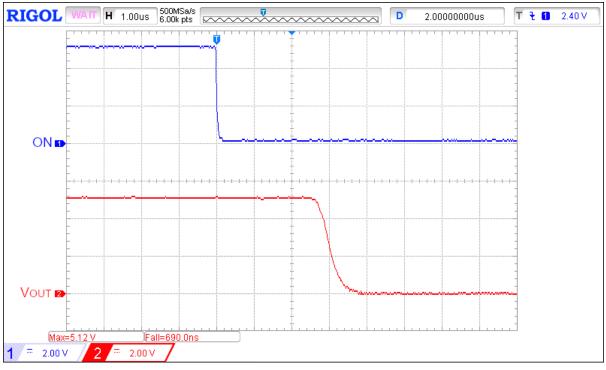

Figure 15: Two SLG59M1714Vs Operating in Parallel: Turn OFF Operation;  $V_{DD} = 5 V$ ,  $V_{IN} = 5 V$ ,  $R_{LOAD} = 100 \Omega$ , no  $C_{LOAD}$ , Load Enable = HIGH

| Appl | ication | Note |  |

|------|---------|------|--|

|------|---------|------|--|

Revision 1.0

Figure 16: Two SLG59M1714Vs Operating in Parallel: Turn OFF Operation;  $V_{DD} = 5 V$ ,  $V_{IN} = 5 V$ ,  $R_{LOAD} = 100 \Omega$ ,  $C_{LOAD} = 10 \mu$ F, Load Enable = HIGH

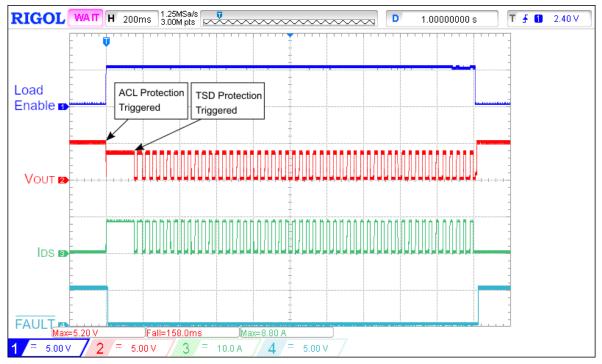

Figure 17: Two SLG59M1714Vs Operating in Parallel: ACL with thermal protection operation;  $V_{DD} = 5 \text{ V}, V_{IN} = 5 \text{ V}, I_{ACL} = 8 \text{ A}, R_{SET_U1} = 20 \text{ k}\Omega, R_{SET_U2} = 20 \text{ k}\Omega, R_{LOAD} = 0.6 \Omega, C_{LOAD} = 10 \mu\text{F},$ ON = HIGH

| Application Note | Revision 1.0 | 22-Feb-2019 |

|------------------|--------------|-------------|

|                  |              |             |

Figure 18: Two SLG59M1714Vs Operating in Parallel: Independent I<sub>OUT</sub> operation;  $V_{DD} = 5 V$ ,  $V_{IN} = 5 V$ ,  $I_{DS} = 4 A$ ,  $R_{IOUT}U1 = 10 k\Omega$ ,  $C_{IOUT}U1 = 10 nF$ ,  $R_{IOUT}U2 = 10 k\Omega$ ,  $C_{IOUT}U2 = 10 nF$ , ON = HIGH

Also, as was the case with the SLG59H1006V, it is possible to combine the component IOUT pins to monitor total load current from one pin. The corresponding SLG59M1714V application configuration and its IOUT signal are illustrated in Figure 19 and Figure 20 respectively. Please note that the system will also generate a 100  $\mu$ A/A transfer characteristic and the IOUT resistor (RIOUT) should be changed to extend measurement current range.

Figure 19: Application Diagram of using two SLG59M1714Vs in parallel with common IOUT pins

| Ap | plic | ation | No | te |

|----|------|-------|----|----|

|    | pilo | ation |    |    |

Revision 1.0

Figure 20: Two SLG59M1714Vs Operating in Parallel: Common IOUT operation;  $V_{DD} = 5 V$ ,  $V_{IN} = 5 V$ ,  $I_{DS} = 4 A$ ,  $R_{IOUT} = 4.99 k\Omega$ ,  $C_{IOUT} = 10 nF$ , ON = HIGH

# 6 Using a Single, High-current GreenFET Load Switches SLG59M1568V

If a load-current monitor feature is not required, it is possible to use single SLG59M1568V GreenFET load switch. Operating from 2.5 V to 5.5 V supply voltage, the SLG59M1568 is a 7.3 m $\Omega$ , 9 A single channel GreenFET load switch that can switch power rails from 1 V to 5.5 V. An application diagram of using SLG59M1568V is illustrated in Figure 21

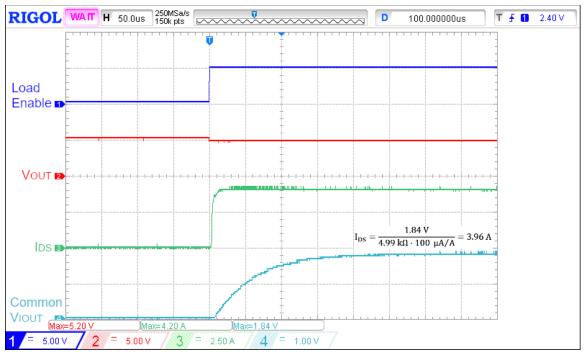

Figure 21: Application Diagram of using SLG59M1568V

| Application Note | Revision 1.0 | 22-Feb-2019 |

|------------------|--------------|-------------|

|                  |              |             |

#### AN-CM-272

#### Extending the GreenFET Load Switch Maximum Operating Current

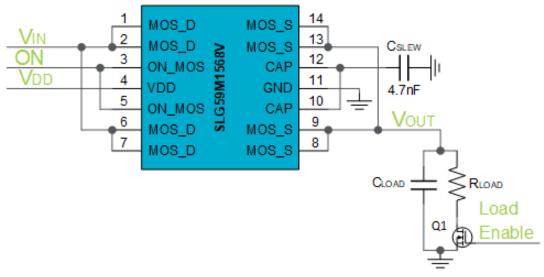

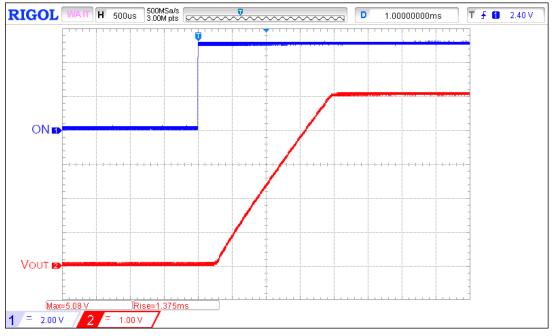

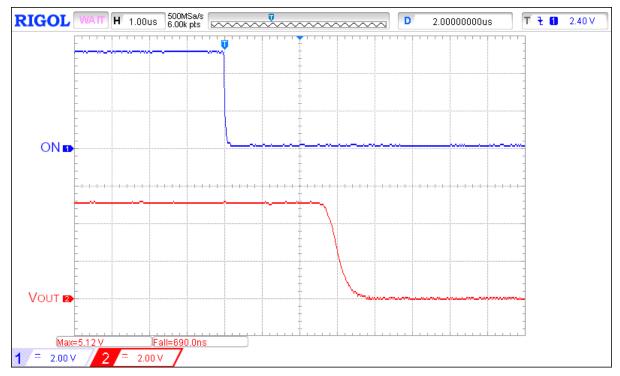

Typical operational waveforms of this GreenFET load switch solution are illustrated from Figure 22 through Figure 25.

Figure 22: SLG59M1568V Turn ON Operation;  $V_{DD} = 5 \text{ V}$ ,  $V_{IN} = 5 \text{ V}$ ,  $C_{SLEW} = 4.7 \text{ nF}$ ,  $R_{LOAD} = 20 \Omega$ ,  $C_{LOAD} = 10 \mu$ F, Load Enable = HIGH

Figure 23: SLG59M1568V Turn OFF Operation;  $V_{DD} = 5 \text{ V}$ ,  $V_{IN} = 5 \text{ V}$ ,  $C_{SLEW} = 4.7 \text{ nF}$ ,  $R_{LOAD} = 20 \Omega$ , no  $C_{LOAD}$ , Load Enable = HIGH

| Application Note | Revision 1.0 | 22-Feb-2019 |

|------------------|--------------|-------------|

|                  |              |             |

Figure 24: SLG59M1568V Turn OFF Operation;  $V_{DD}$  = 5 V,  $V_{IN}$  = 5 V,  $C_{SLEW}$  = 4.7 nF, R<sub>LOAD</sub> = 20  $\Omega$ , C<sub>LOAD</sub> = 10  $\mu$ F, Load Enable = HIGH

Figure 25: SLG59M1568V ACL with thermal protection operation;  $V_{DD} = 5 V$ ,  $V_{IN} = 5 V$ ,  $I_{ACL} = 12 A$ ,  $R_{LOAD} = 0.4 \Omega$ ,  $C_{LOAD} = 10 \mu$ F, ON = HIGH

| Application Note | Revision 1.0 |

|------------------|--------------|

|                  |              |

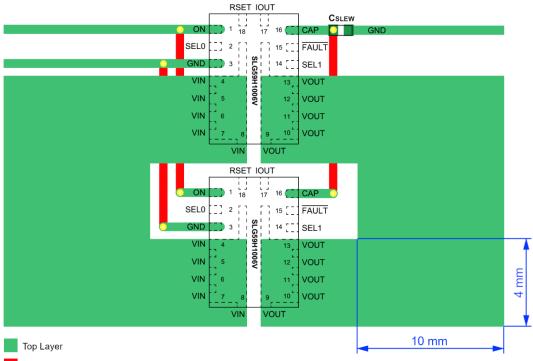

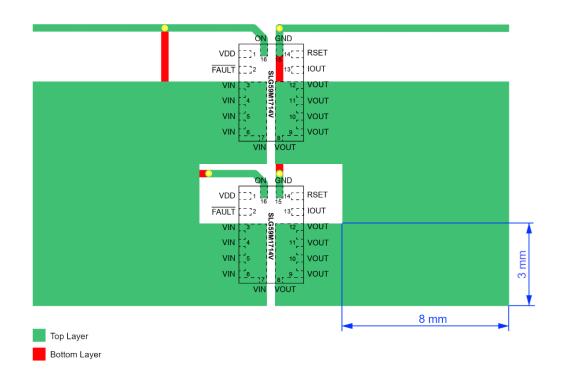

### 7 Recommended PCB Layouts

All PCB traces have parasitic resistance, capacitance, and inductance. If there were a difference in path length from the input power source to the GreenFET load switches' VIN, VOUT pads, this delta trace length would create a current imbalance. In this case, the PCB layout should be designed properly to minimize parasitic impedance and, especially parasitic inductance, on both sets of VIN and VOUT pins.

Excess trace inductance may cause a delay effect during on/off operation. Figure 26, Figure 27 and Figure 28 show the recommended PCB layouts for applications using SLG59H1006Vs, SLG59M1714Vs and SLG59M1568V, respectively.

Bottom Layer

Figure 26: Recommended PCB layout for two SLG59H1006Vs operating in parallel

#### Figure 27: Recommended PCB layout for two SLG59M1714Vs operating in parallel

#### 8 Conclusions

Renesas provides a number of highly differentiated, low system cost load switches for various load current applications. To extend maximum operating current, the GreenFET load switches are an excellent choice for their very low, high-performance RDS<sub>ONs</sub> and can be used in parallel with minimal risk of current-hogging or imbalance. The GreenFET load switches used in parallel retain all their circuit protection features and a select number of the GreenFET load switches offer analog load-current monitor outputs.

| Application Note | Revision 1.0 |          | 22-Feb-2019 |  |  |

|------------------|--------------|----------|-------------|--|--|

|                  | 10, 100      | 0 0000 D |             |  |  |

### **Revision History**

| Revision | Date        | Description     |

|----------|-------------|-----------------|

| 1.0      | 22-Feb-2019 | Initial Version |

**Application Note**

**Revision 1.0**

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.