# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# SH7263 グループ

# LCD コントローラ表示動作

#### 要旨

本アプリケーションノートは, SH7263/SH7203 に内蔵された LCD コントローラ (LCDC) の表示設定例について説明したものです。ソフトウェア設計の際のご参考例としてお役立てください。

# 動作確認デバイス

SH7263

# 目次

| 1. | はじめに            | 2  |

|----|-----------------|----|

| 2. | 応用例の説明          | 3  |

| 3  | <b>糸老ドキュメント</b> | 28 |

#### 1. はじめに

#### 1.1 仕様

本応用例では,パワーオンリセット解除後に,周辺モジュールを初期化し LCD コントローラ (LCDC) の表示動作を行います。

- ◆ CSO 空間のフラッシュメモリにプログラムを配置しています。

- CS3 空間に SDRAM を 16 ビットバスで接続し,表示データを格納しています。

- LCD パネル (TFT 液晶) を接続し, 色の深さは 16 bpp に設定しています。

- 表示イメージサイズは QVGA サイズです。

#### 1.2 使用機能

クロックパルス発振器 (CPG)

バスステートコントローラ (BSC)

ピンファンクションコントローラ (PFC)

LCD コントローラ (LCDC)

#### 1.3 適用条件

マイコン: SH7263

動作周波数: 内部クロック 200 MHz

バスクロック 66 MHz 周辺クロック 33 MHz

評価ボード: SH7263 評価ボード(R0K572630D001BR)

SDRAM 16 M バイト 16 ビットバス幅固定 (エルピーダ製 EDS1216AATA-75E)

NOR フラッシュメモリ 4 M バイト (ルネサス製 M5M29KT331AVP)

LCD パネル: TFT カラーLCD H320 × V240

C コンパイラ: ルネサス テクノロジ製

SuperH RISC engine ファミリ C/C++ コンパイラパッケージ Ver.9.01 Release 01

コンパイルオプション: -cpu = sh2afpu -fpu = single -include = "\$(WORKSPDIR)¥inc" -message

-object = "\$(CONFIGDIR)\forall \forall \forall

-del vacant loop = 0 -struct alloc = 1 -nologo

#### 1.4 関連アプリケーションノート

本資料の参考プログラムは,「SH7263/SH7203 グループ アプリケーションノート 初期設定例 (RJJ06B0899)」の設定条件で動作設定を行っています。そちらも合わせてご参照ください。

#### 2. 応用例の説明

本応用例では, LCD表示動作における初期設定例を説明します。

本プログラム実行にあたっては,本設定例以外に,メモリの初期化など最低限のハードウェア初期設定処理を行う初期設定プログラムが必要です。

#### 2.1 機能概要

LCD コントローラ (LCDC) は ,表示用の画像をシステムメモリに格納するユニファイドメモリアーキテクチャをとっています。LCDC モジュールはシステムメモリからデータを読み出し , パレットメモリを使って色を決定した後 , LCD パネルに送ります。また , システムメモリからダイレクトにデータを読み出し , LCD パネルに表示することも可能です。シリアルインタフェース方式の STN/Dual STN/TFT パネル液晶モジュールを接続することが可能です。

CPU に接続された SDRAM (CS3 空間)\*の一部を LCDC の表示データ格納用 VRAM として使用することで専用の表示用メモリが不要です。また,2.4~K~バイトのラインバッファを LCDC に内蔵にしており,安定した表示が可能です。

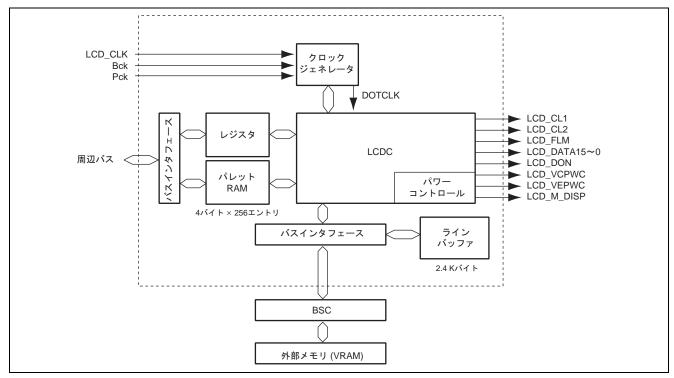

表1にLCDCの機能概要を,図1にLCDCのブロック図を示します。

また,表2に端子構成を,表3にレジスタ構成を示します。

【注】 \* SDRAM (CS2 空間), および内蔵 RAM からの表示は行えません。

備考 特長 機能 パネルインタフェース シリアルインタフェース方式 液晶の種別 STN / Dual STN / TFT \_\_\_ パネルデータフォーマット 8 / 12 / 16 / 18 ビットバス幅 カラーモード 4/8/15/16 bpp グレースケールモード 1/2/4/6 bpp パネルサイズ 16 × 1 ~ 1024 × 1024 ドット カラーパレット 24 ビット 24 ビット中, 16 ビットが有効 R:5 / G:6 / B:5 STN/DSTN パネルの中間色 RGB 各 8 ビットの, 24 ビットの空間変 ちらつきの少ない 65536 の色制御 表示 VRAM CPU に接続された SDRAM (CS3 空間) 専用の表示用メモリが不要 の一部を VRAM として使用 ラインバッファ 2.4 K バイト 安定した表示を実現 プログラマブル 信号極性 出力信号のレベル反転機能をサ ポート バイト内のエンディアン設定, データフォーマット バックドピクセル方式選択可能 ハードウェア 回転前の横幅は320ピクセル以下 あり ローテーションモード に限定 割り込み ユーザー指定位置で割り込み発生可能 ティアリング (ちらつき) を回避

表1 LCDC の機能概要

図1 LCDC のブロック図

表 2 端子構成

| 端子名          | 入出力 | 機能                                            |

|--------------|-----|-----------------------------------------------|

| LCD_DATA15~0 | 出力  | LCD パネル用データ                                   |

| LCD_DON      | 出力  | 表示開始信号 (DON)                                  |

| LCD_CL1      | 出力  | シフトクロック 1 (STN/DSTN) / 水平同期信号 (HSYNC) (TFT)   |

| LCD_CL2      | 出力  | シフトクロック 2 (STN/DSTN) / ドットクロック (DONCLK) (TFT) |

| LCD_M_DISP   | 出力  | 液晶交流化信号/DISP 信号                               |

| LCD_FLM      | 出力  | ファーストラインマーカ/垂直同期信号 (VSYNC) (TFT)              |

| LCD_VCPWC    | 出力  | 液晶モジュール電源制御 (VCC)                             |

| LCD_VEPWC    | 出力  | 液晶モジュール電源制御 (VEE)                             |

| LCD_CLK      | 入力  | LCD クロックソース入力                                 |

# 表3 レジスタ構成

| レジスタ名                     | 略称             | R/W    | 初期値         | アドレス           | アクセスサイズ |

|---------------------------|----------------|--------|-------------|----------------|---------|

| LCDC インプットクロック            | LDICKR         | R/W    | H'0101      | H'FFFF FC00    | 16      |

| レジスタ                      |                |        |             |                |         |

| LCDC モジュールタイプレジスタ         | LDMTR          | R/W    | H'0109      | H'FFFF FC02    | 16      |

| LCDC データフォーマット            | LDDFR          | R/W    | H'000C      | H'FFFF FC04    | 16      |

| レジスタ                      |                |        |             |                |         |

| LCDC スキャンモードレジスタ          | LDSMR          | R/W    | H'0000      | H'FFFF FC06    | 16      |

| LCDC 上部表示パネル用データ          | LDSARU         | R/W    | H'0C00 0000 | H'FFFF FC08    | 32      |

| 取り込み開始アドレスレジスタ            |                |        |             |                |         |

| LCDC 下部表示パネル用データ          | LDSARL         | R/W    | H'0C00 0000 | H'FFFF FC0C    | 32      |

| 取り込み開始アドレスレジスタ            |                |        |             |                |         |

| LCDC 表示パネル用取り込み           | LDLAOR         | R/W    | H'0280      | H'FFFF FC10    | 16      |

| データラインアドレスオフセット           |                |        |             |                |         |

| レジスタ                      |                |        |             |                |         |

| LCDC パレットコントロール           | LDPALCR        | R/W    | H'0000      | H'FFFF FC12    | 16      |

| レジスタ                      |                |        |             |                |         |

| パレットデータレジスタ 00~FF         | LDPR00         | R/W    | _           | H'FFFF F800    | 32      |

|                           | ~ FF           |        |             | ~              |         |

| 1000 4 7 1 2 5 5 1 1      | LBUIONB        | D 04/  | 1114550     | H'FFFF FBFC    | 40      |

| LCDC 水平キャラクタナンバー          | LDHCNR         | R/W    | H'4F52      | H'FFFF FC14    | 16      |

| レジスタ                      | 1 5110) (115   | 5.44   | 1,1100=0    |                | 1.0     |

| LCDC 水平同期信号レジスタ           | LDHSYNR        | R/W    | H'0050      | H'FFFF FC16    | 16      |

| LCDC 垂直表示ラインナンバー          | LDVDLNR        | R/W    | H'01DF      | H'FFFF FC18    | 16      |

| レジスタ                      | LD) (TLND      | D 44/  | LUCADE      | LUEEEE EOAA    | 10      |

| LCDC 垂直総ラインナンバー           | LDVTLNR        | R/W    | H'01DF      | H'FFFF FC1A    | 16      |

| レジスタ                      | 1 D) (0) (A) D | DAA    | LUCADE      | LUEEEE EOAO    | 40      |

| LCDC 垂直同期信号レジスタ           | LDVSYNR        | R/W    | H'01DF      | H'FFFF FC1C    | 16      |

| LCDC AC モジュレーション信号        | LDACLNR        | R/W    | H'000C      | H'FFFF FC1E    | 16      |

| トグルラインナンバーレジスタ            | LDINTR         | R/W    | H'0000      | H'FFFF FC20    | 16      |

| LCDC 割り込みコントロール           | LDINTR         | R/VV   | H 0000      | H FFFF FC20    | 10      |

| レジスタ<br>LCDC パワーマネジメントモード | LDDMMD         | DAM    | H'0010      | H'FFFF FC24    | 16      |

| レジスタ                      | LDPIVIIVIK     | R/W    | H 0010      | H F F F F C 24 | 10      |

| LCDC 電源シーケンス期間            | LDPSPR         | R/W    | H'F60F      | H'FFFF FC26    | 16      |

| レジスタ                      | LDFSFK         | 11/00  | 111 001     | 111111111020   | 10      |

| LCDC コントロールレジスタ           | LDCNTR         | R/W    | H'0000      | H'FFFF FC28    | 16      |

| LCDC コフトロールレジスタ           | LDUINTR        | R/W    | H'0000      | H'FFFF FC34    | 16      |

| コントロールレジスタ                | LDONAIN        | 13/ ۷۷ | 110000      | 11111111034    | 10      |

| LCDC ユーザ指定割り込み            | LDUINTLNR      | R/W    | H'004F      | H'FFFF FC36    | 16      |

| ラインナンバーレジスタ               | LDONVILIAN     | 13/ ۷۷ | 110041      | 11111111030    | 10      |

| LCDC メモリアクセス              | LDLIRNR        | R/W    | H'0000      | H'FFFF FC40    | 16      |

| インターバルナンバーレジスタ            | LDLININ        | 17,44  | 110000      |                |         |

| コンターハルノンハーレンスツ            |                |        |             |                | 1       |

#### 2.2 LCD 回路接続例

#### 2.2.1 LCD 評価回路接続

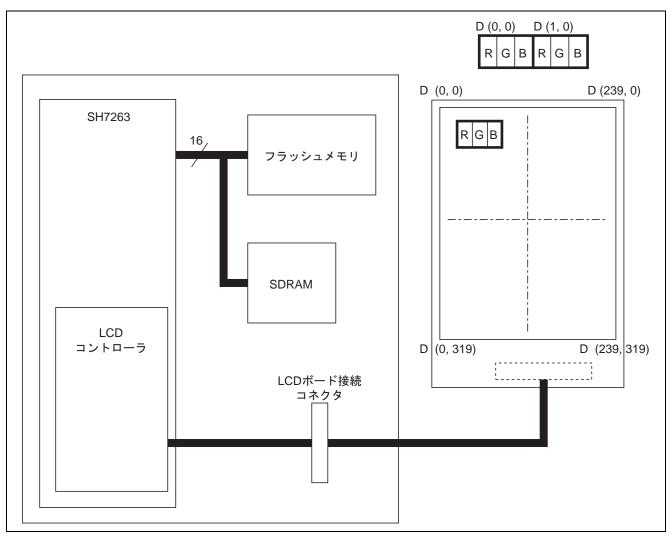

本応用例で使用している LCD パネル (TFT 液晶) は,16 ビット RGB データ,QVGA サイズです。また,表示データ格納用 VRAM には CS3 空間 (0x0C00 0000 ~ 0x0FFF FFFF: キャッシュ有効空間,または 0x2C00 0000 ~ 0x2FFF FFFF: キャッシュ無効空間) に配置されている SDRAM を使用します。

図2に本応用例のハードウェア構成を示します。

図2 本応用例のハードウェア構成

#### 2.2.2 LCD パネルとの接続

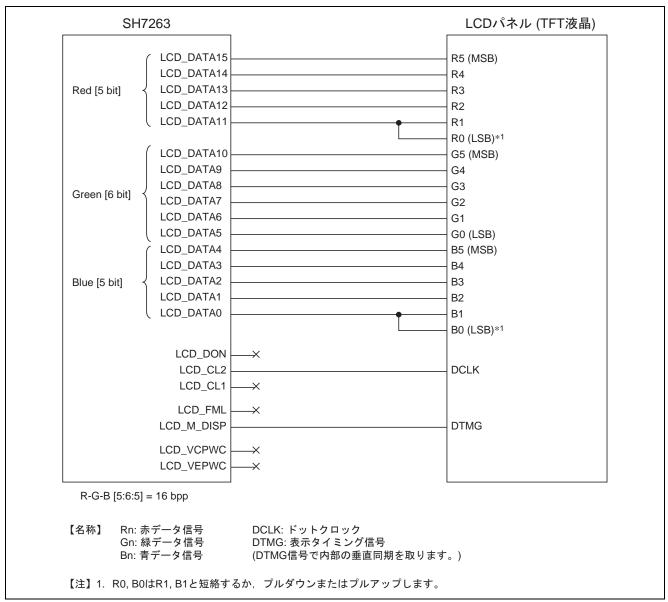

図3に本応用例で使用したLCDパネルとの接続例を示します。また,表4にLCD端子一覧を示します。

図3 LCDパネルとの接続例

表 4 LCD 端子一覧

| 端子名                    | 名称                   |

|------------------------|----------------------|

| LCD_DATA15 ~ LCD_DATA0 | LCD パネルデータ           |

| LCD_DON                | 表示開始信号               |

| LCD_CK1                | シフトクロック 1: 水平同期信号    |

| LCD_CK2                | シフトクロック 2: ドットクロック   |

| LCD_M_DISP             | 液晶交流化信号              |

| LCD_FLM                | ファーストラインマーカ (垂直同期信号) |

| LDC_VCPWC              | 液晶モジュール: 電源制御 (VCC)  |

| LCD_VEPWC              | 液晶モジュール: 電源制御 (VEE)  |

| LCD_CLK                | LCD クロック: ソース入力      |

# 2.2.3 クロックと LCD データ信号例図 4 に LCD データ信号例を示します。

| DOTCLK     | $\neg$ |                   | $\neg$ |                   |     |               |     |   |

|------------|--------|-------------------|--------|-------------------|-----|---------------|-----|---|

| DOTCLK     |        |                   |        |                   |     |               |     | - |

| LCD_CL2    |        |                   |        |                   |     |               |     | - |

| LCD_DATA15 | R05    | $\rightarrow$     | R15    | $\rightarrow$     | R25 | $\rightarrow$ | R35 | > |

| LCD_DATA14 | R04    | $\rightarrow$     | R14    | $\rightarrow$     | R24 | $\rightarrow$ | R34 | > |

| LCD_DATA13 | R03    | $\rightarrow$     | R13    | $\rightarrow$     | R23 | $\rightarrow$ | R33 | > |

| LCD_DATA12 | R02    | $\rightarrow$     | R12    | $\rightarrow$     | R22 | $\rightarrow$ | R32 | > |

| LCD_DATA11 | R01    | $\rightarrow$     | R11    | $\rightarrow$     | R21 | $\rightarrow$ | R31 | > |

| LCD_DATA10 | G05    | $\rightarrow$     | G15    | $\rightarrow$     | G25 | $\rightarrow$ | G35 | > |

| LCD_DATA9  | G04    | $\rightarrow$     | G14    | $\rightarrow$     | G24 | $\rightarrow$ | G34 | > |

| LCD_DATA8  | G03    | $\supset \subset$ | G13    | $\rightarrow$     | G23 | $\rightarrow$ | G33 | > |

| LCD_DATA7  | G02    | $\supset \subset$ | G12    | $\rightarrow$     | G22 | $\rightarrow$ | G32 | > |

| LCD_DATA6  | G01    | $\supset \subset$ | G11    | $\supset \subset$ | G21 | $\rightarrow$ | G31 | > |

| LCD_DATA5  | G00    | $\supset \subset$ | G10    | $\supset \subset$ | G20 | $\rightarrow$ | G30 | > |

| LCD_DATA4  | B05    | $\supset \subset$ | B15    | $\rightarrow$     | B25 | $\rightarrow$ | B35 | > |

| LCD_DATA3  | B04    | $\rightarrow$     | B14    | $\rightarrow$     | B24 | $\rightarrow$ | B34 | > |

| LCD_DATA2  | B03    | $\supset \subset$ | B13    | $\rightarrow$     | B23 | $\rightarrow$ | B33 | > |

| LCD_DATA1  | B02    | $\rightarrow$     | B12    | $\rightarrow$     | B22 | $\rightarrow$ | B32 | > |

| LCD_DATA0  | B01    | $\rightarrow$     | B11    | $\rightarrow$     | B21 | $\rightarrow$ | B31 | > |

|            |        |                   |        |                   |     |               |     |   |

図 4 LCD データ信号例 (TFT カラー16 ビットデータバスモジュール)

#### 2.3 エリア概要

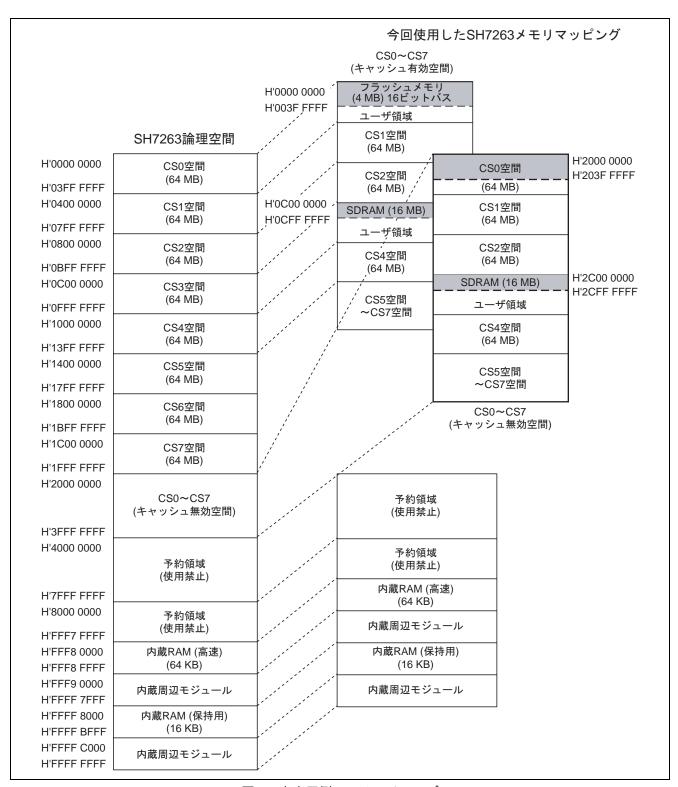

SH7263 は 32 ビットのアドレス空間を有しており,上位ビットで,キャッシュ有効空間,キャッシュ無効空間,内蔵空間(内蔵 RAM,内蔵周辺モジュール,予約)に分割されています。

図5に本応用例でのメモリマップを示します。

図5 本応用例でのメモリマップ

#### 2.4 動作説明

#### 2.4.1 バス占有率について

LCDC は,機能としては  $1024\times1024$  ドット,16 bpp (ビットパーピクセル) の表示を行うことが可能です。しかし,表示される画像のイメージは CPU と共有である VRAM に格納されており,本 LCDC は表示に間に合うように VRAM からデータの読み出しを行う必要があります。

SH7263 では , 最大 32 バーストのメモリリードと 2.4 K バイトのラインバッファ内蔵により , 表示の破綻が起こりにくいのですが ,組み合わせによっては ,表示が困難になることがあります。フレームレート 60 Hz とした場合の推奨するサイズとしては ,16 bpp 時 320 × 240 ドット ,もしくは 8 bpp 時 640 × 480 ドットです。

目安としては,下記に示されたバス占有率が40%を超えないようにしてください。

オーバヘッド係数は, CL2の SDRAM が 32 ビットバスのときに 1.375, 16 ビットバスのときに 1.118 となります。今回用いた SDRAM はバス幅 16 ビット固定なので, オーバヘッド係数は 1.118 となります。

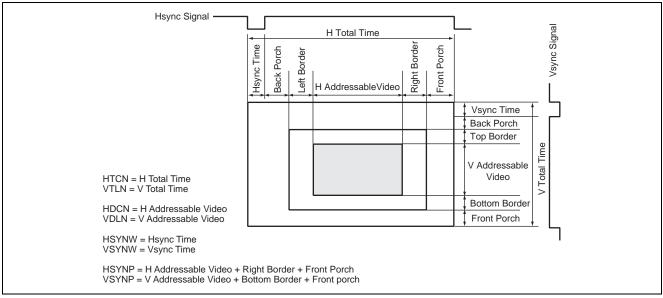

表5に本応用例でのバス占有率を示します。また,図6に有効な表示と帰線期間について示します。

| オーバヘッド係数      | CL2 16 bit バス                | 1.118       |

|---------------|------------------------------|-------------|

| 水平表示キャラクタナンバー | 240 ドット = (HDCN + 1) × 8 ドット | HDCN = 29   |

| 垂直表示ラインナンバー   | 320 ライン = VDLN + 1           | VDLN = 319  |

| フレームレート       | _                            | 60 Hz       |

| 色数            | R-G-B [5:6:5]                | 16 bpp      |

| CKIO          | バスクロック                       | 66 MHz (Βφ) |

| バス占有率         | 7.80%                        | •           |

表 5 本応用例でのバス占有率

【注】 HDCN は表示キャラクタ (8 ビット単位) – 1 で指定します。

図 6 有効な表示と帰線期間

#### 2.4.2 カラーパレットについて

本応用例ではカラーパレットレジスタの設定をしていません。カラーパレットを使用する場合は , 以下の 説明を参考に設定をしてください。

#### • (1) カラーパレットレジスタ

本 LCDC は 1 エントリにつき 24 ビットデータ出力で 256 エントリ同時使用可能なカラーパレットを有しており,本カラーパレットを利用することで 16 M 色中 256 色同時発色が可能です。また,本カラーパレットは以下の手順によって,ユーザにより随時設定可能です。

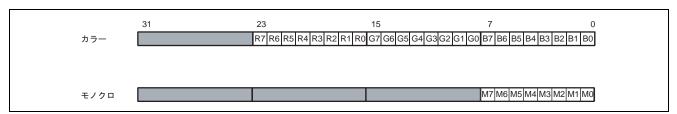

図 7 にカラーパレットデータフォーマットを,表 6 にパレットデータレジスタの設定を示します。

LDPALCR の PALEN ビットを 0 (初期値) に設定: 通常表示動作

- 2. LDPALCR にアクセスし PALEN を 1 に設定: カラーパレット設定モード移行は周辺クロック の 3 サイクル後

- 3. LDPALCR にアクセスし, PALS が 1 であることを確認

- 4. LDPR00~FF にアクセスし PALD00~FF に必要な値を書き込む

- 5. LDPALCR にアクセスし PALEN を 0 に設定: 通常表示モードに移行は周辺クロックの 1 サイクル後

なお,LDPALCR の PALS が 1 にセットされている間,LCDC 表示データ出力(LCD\_DATA) は 0 値出力となります。

図7 カラーパレットデータフォーマット

#### 表 6 パレットデータレジスタの設定 (PALDnn 色/階調)

| ビット     | ビット名     | 色データ    | カラー                    | モノクロ                  |

|---------|----------|---------|------------------------|-----------------------|

| 31 ~ 24 | _        | _       | Read Only のため , 書き込み不可 | Read Only のため,書き込み不可  |

| 23      | PALDnn23 | Rデータ    | R データの設定値              | Don't care            |

| 22      | PALDnn22 |         |                        |                       |

| 21      | PALDnn21 |         |                        |                       |

| 20      | PALDnn20 |         |                        |                       |

| 19      | PALDnn19 |         |                        |                       |

| 18      | PALDnn18 |         | 設定値が"0"の場合: "0"書き込み    |                       |

| 17      | PALDnn17 |         | それ以外: "1"か"0"どちらか書き込み  |                       |

| 16      | PALDnn16 |         |                        |                       |

| 15      | PALDnn15 | G データ   | G データの設定値              |                       |

| 14      | PALDnn14 |         |                        |                       |

| 13      | PALDnn13 |         |                        |                       |

| 12      | PALDnn12 |         |                        |                       |

| 11      | PALDnn11 |         |                        |                       |

| 10      | PALDnn10 |         |                        |                       |

| 9       | PALDnn9  |         | 設定値が"0"の場合: "0"書き込み    |                       |

| 8       | PALDnn8  |         | それ以外: "1"か"0"どちらか書き込み  |                       |

| 7       | PALDnn7  | (カラー時)  | B データの設定値              | M データの設定値             |

| 6       | PALDnn6  | Βデータ    |                        |                       |

| 5       | PALDnn5  |         |                        |                       |

| 4       | PALDnn4  | (モノクロ時) |                        |                       |

| 3       | PALDnn3  | Μ データ   |                        |                       |

| 2       | PALDnn2  |         | 設定値が"0"の場合: "0"書き込み    | 設定値が"0"の場合: "0"書き込み   |

| 1       | PALDnn1  | ]       | それ以外: "1"か"0"どちらか書き込み  | それ以外: "1"か"0"どちらか書き込み |

| 0       | PALDnn0  | ]       |                        |                       |

【注】 の部分は無効のデータとなりますが,書き込んでください。

詳細な設定方法は「SH7263 グループ ハードウェアマニュアル (RJJ09B0284) カラーパレット仕様について」を参照ください。

#### 2.4.3 使用上の注意事項

- 表示データ格納用 VRAM (CS3 空間の SDRAM) アクセスの停止手順は、以下のフローに従ってください。

- 現在の状態が LDPMMR の LPS1 と LPS0 ビットが 1 であることを確認します。

- 2. LDCNTR の DON ビットを 0 (表示オフモード) に設定します。

- 3. LDPMMR の LPS1 と LPS0 ビットが 0 になることを確認します。

- 4. 1フレームの表示時間を待ちます。

表示データ格納用 VRAM (CS3 空間の SDRAM)をセルフリフレッシュに設定する前、スタンバイモード、モジュールスタンバイモード等に入る前には、この停止手順が必要です。

- SDRAM 初期化前に SDRAM ヘアクセスしないでください。

参考プログラムは、HardwareSetup 関数でバスステートコントローラ (BSC) を初期化した後に、SDRAM 上の領域を使用しています。未初期化の SDRAM を使用した場合は正常に動作しませんのでご注意ください。

- スタック領域である S セクションを SDRAM 上に配置しないでください。

スタックポインタの初期値は,リセットベクタに設定されている値 (S セクションの最終番地 + 1) が設定されます。参考プログラムは S セクションを内蔵 RAM 上に配置するため問題はありませんが,SDRAM 上に配置すると初期設定プログラム内の関数コール実行時に,未初期化の SDRAM をアクセスしてしまいます。

- INITSCT 関数実行前に静的変数領域をアクセスしないでください。

C 言語の静的領域は ,INITSCT 関数の実行によって初期化されます。それ以前にアクセスした場合は値が不定となりますのでご注意ください。

- 画像データ領域をキャッシュ空間に設定しないください。 画像データ領域 (B\_IMAGE\_AREA セクション) をキャッシュ有効空間に配置した場合,コヒーレンシの問題により正しく LCD パネルに表示できない場合があります。

#### 2.4.4 セクション

表7に本応用例で適用したセクション配置を示します。

#### 表7 セクション配置

| セクション名       | セクション用途             | 配置アドレス      | 空間             |

|--------------|---------------------|-------------|----------------|

| DVECTTBL     | リセットベクタテーブル         | H'0000 0000 | CS0 空間         |

| DINTTBL      | 割り込みベクタテーブル         |             | (キャッシュ有効)      |

| PResetPRG    | リセットプログラム           | H'0000 0800 |                |

| PIntPRG      | 割り込み関数              |             |                |

| Р            | プログラム領域 (指定なしの場合)   | H'0000 1000 |                |

| С            | 定数領域                |             |                |

| C\$BSEC      | 未初期化データ領域用アドレス構造体   |             |                |

| C\$DSEC      | 初期化データ領域用アドレス構造体    |             |                |

| D            | 初期化データ (初期値)        |             |                |

| PCACHE       | プログラム領域 (キャッシュ無効空間) | H'203F F000 | CS0 空間 (Flash) |

|              |                     |             | (キャッシュ無効)      |

| B_IMAGE_AREA | 画像データ領域 (未初期化データ領域) | H'2C00 0000 | CS3 空間 (SDRAM) |

| В            | 未初期化データ領域           |             | (キャッシュ無効)      |

| RINTTBL      | 割り込みベクタテーブル         | H'FFF8 0000 | 内蔵 RAM         |

| R            | 初期化データ領域            |             |                |

| S            | スタック領域              | H'FFF8 FC00 |                |

【注】セクションの詳細については ,「SuperH RISC enjine C/C++ コンパイラ ,アセンブラ ,最適化リンケー ジエディタ ユーザーズマニュアル (RJJ10J1885)」を参照ください。

#### 2.5 参考プログラムの説明

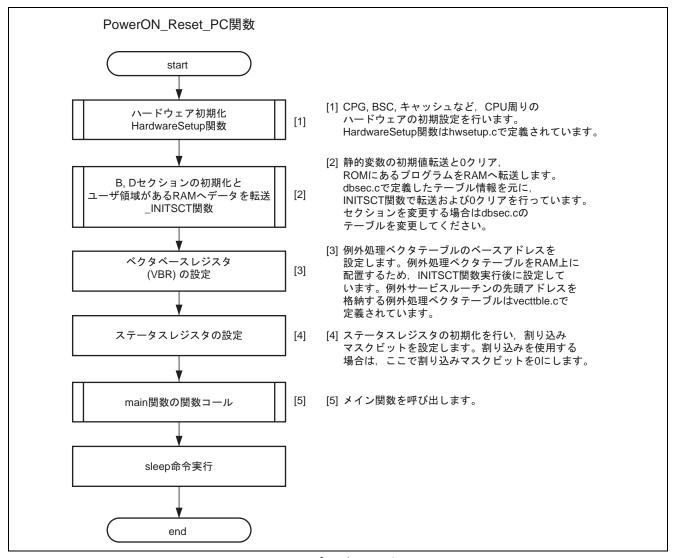

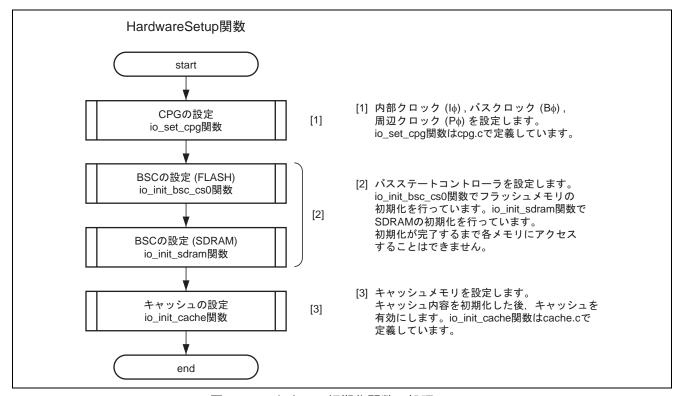

初期設定プログラムは,電源投入後実行する PowerON\_Reset\_PC 関数を含む resetprg.c と,ハードウェア初期化関数を含む hwsetup.c などの複数のソースファイルから構成されています。以下に主要なソースファイルの構成概略を示します。

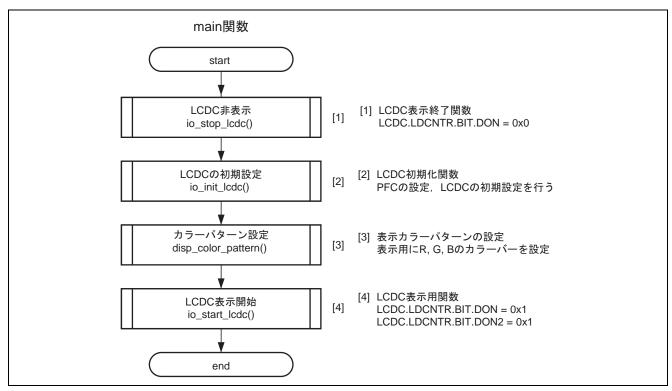

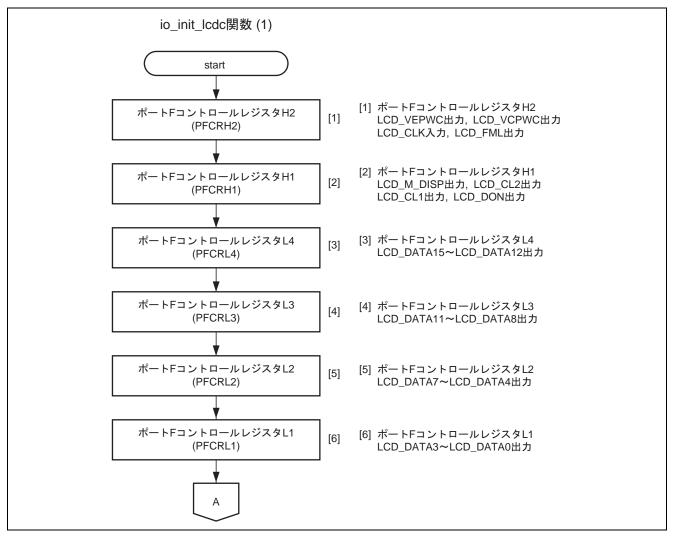

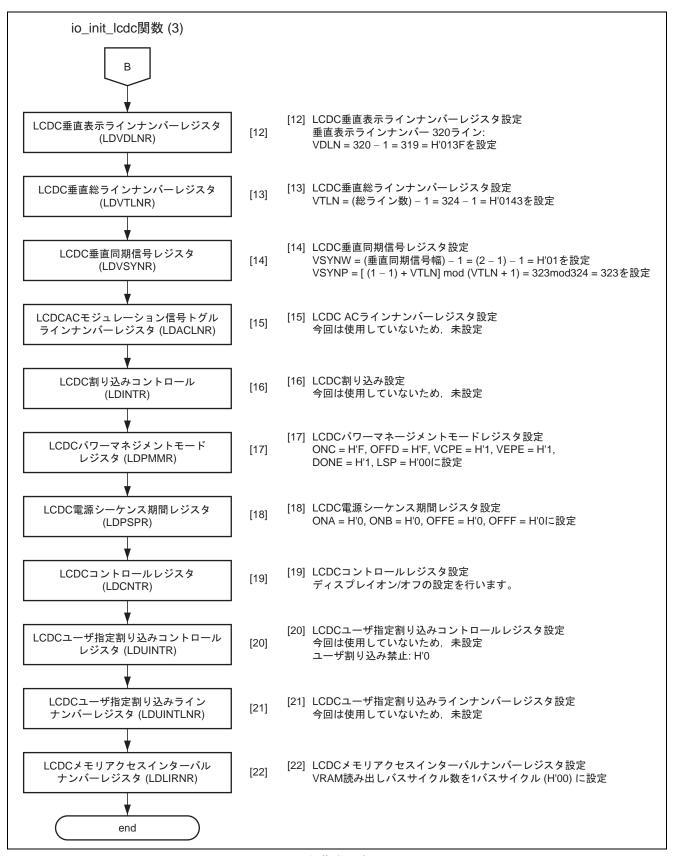

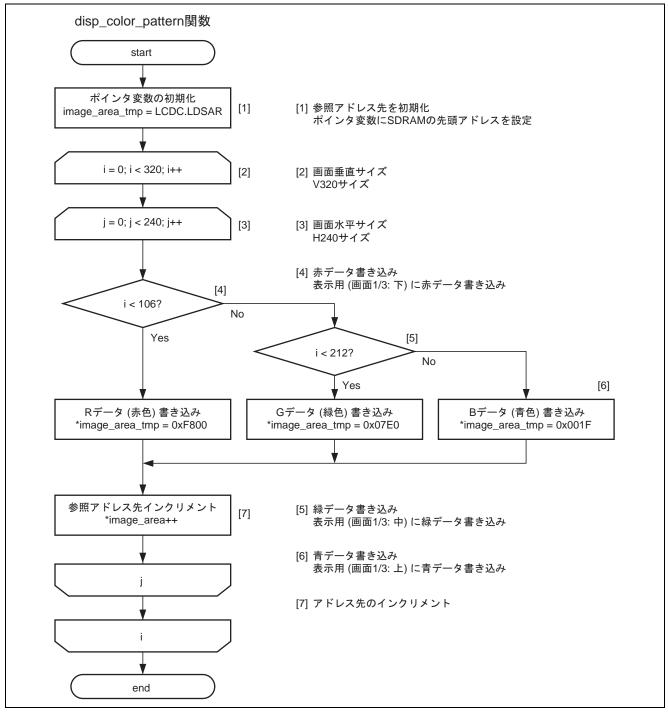

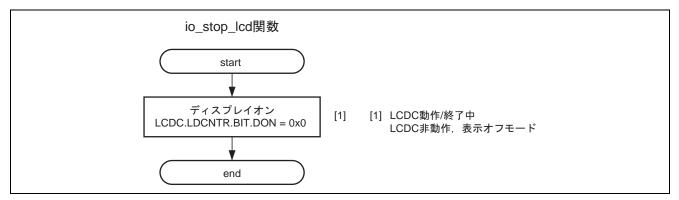

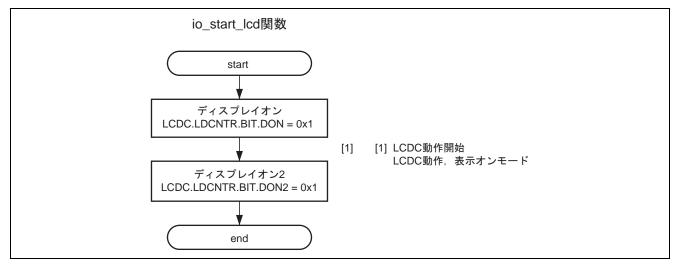

図 8 にリセットプログラムの処理フローを ,図 9 にハードウェア初期化関数の処理フローを ,図 10 に main 関数の処理フローを ,図 11 と図 12 と図 13 に LCDC 初期化の処理フローを ,図 14 にカラーパターンの設定の処理フローを示します。また ,図 15 に LCDC 表示終了処理フローを ,図 16 に LCDC 表示開始フローを示します。

図8 リセットプログラムの処理フロー

図 9 ハードウェア初期化関数の処理フロー

図 10 main 関数の処理フロー

図 11 LCDC 初期化の処理フロー (1)

図 12 LCDC 初期化の処理フロー (2)

図 13 LCDC 初期化の処理フロー (3)

図 14 カラーパターン設定の処理フロー

図 15 LCDC 表示終了処理フロー

図 16 LCDC 表示開始処理フロー

# 2.6 参考プログラムにおけるレジスタ設定内容

# 2.6.1 各モジュール (CPG, BSC, PFC)

表8にLCDコントローラ以外で使用した各モジュールのレジスタ設定を示します。

表8 各モジュールのレジスタ設定

| モジュール | 設定内容                                     | レジスタ設定               |

|-------|------------------------------------------|----------------------|

| CPG   | 内部クロック: 200 MHz                          | FRQCR = H'1104       |

|       | バスクロック: 66 MHz                           |                      |

|       | 周辺クロック: 33 MHz                           |                      |

| BSC   | CS0 空間 (フラッシュメモリ)                        | ·                    |

|       | ライト-リード/ライト-ライトサイクル間アイドル指定: 1 アイドル       | CS0BCR = H'1000 0400 |

|       | データバス指定: 16 ビットバス幅                       |                      |

|       | アサート遅延サイクル: 1.5 サイクル                     | CS0WCR = H'0000 0AC1 |

|       | アクセスウェイトサイクル: 5 サイクル                     |                      |

|       | ネゲート遅延サイクル: 1.5 サイクル                     |                      |

|       | CS3 空間 (SDRAM)                           |                      |

|       | メモリ指定: SDRAM                             | CS3BCR = H'0000 4400 |

|       | データバス指定: 16 ビットバス幅                       |                      |

|       | プリチャージ待ちサイクル: 1 サイクル                     | CS3WCR = H'0000 2892 |

|       | ACTV READ/WRITE コマンド間ウェイトサイクル: 2 サイクル    |                      |

|       | CAS レイテンシ: 2 サイクル                        |                      |

|       | プリチャージ起動待ちサイクル: 2 サイクル                   |                      |

|       | REF コマンド/セルフリフレッシュ解除: 5 サイクル             |                      |

|       | リフレッシュ制御: リフレッシュを行う                      | SDCR = H'0000 0809   |

|       | : オートリフレッシュ                              |                      |

|       | バンクアクティブモード: オートプリチャージ                   |                      |

|       | エリア3ロウアドレスビット数: 12 ビット                   |                      |

|       | エリア 3 カラムアドレス数: 9 ビット                    |                      |

|       | クロックセレクト: Βφ/16                          | RTCSR = H'A55A 0010  |

|       | リフレッシュ回数: 1 回                            |                      |

|       | リフレッシュ間隔: 65 (0x41) サイクル/リフレッシュ回数        | RTCOR = H'A55A 0041  |

|       | AC 特性スイッチ: 切り替えを行い,遅延時間を延長する             | RTCSR = H'A55A 0010  |

| PFC   | CS0 および CS3 で使用するアドレスバス,データバス,および LCD 液晶 | の制御端子を設定             |

|       | LCDC 端子: LCD_DATA15~LCD_DATA0            | PFCRH2 = H'2222      |

|       | : LCD_DON                                | PFCRH1 = H'2222      |

|       | : LCD_CLK, LCD_CK1, LCD_CK2              | PFCRL4 = H'2222      |

|       | : LCD_M_DISP                             | PFCRL3 = H'2222      |

|       | : LCD_FLM                                | PFCRL2 = H'2222      |

|       | : LCD_VCPWC, LCD_VEPWC                   | PFCRL1 = H'2222      |

|       | 外部メモリ端子: CS3                             | PCCRL4 = H'0011      |

|       | : CKE                                    | PCCRL3 = H'0011      |

|       | : RAS, CAS                               | PCCRL2 = H'0011      |

|       | : RD/WR                                  | PCCRL1 = H'1010      |

|       | : WE0, WE1                               | PECRL1 = H'0100      |

#### 2.6.2 LCD コントローラ

表 9~表 14に LCD コントローラのレジスタ設定を示します。

# 表 9 LCDC レジスタ設定 (1)

| レジスタ名   | ビット名          | アドレス        | 設定値         | 設定説明                                               |

|---------|---------------|-------------|-------------|----------------------------------------------------|

| LDICKR  | ICKSEL[1:0]   | H'FFFF FC00 | H'1006      | 入力クロック選択ビット                                        |

|         |               |             |             | B'01: 周辺クロックを選択 (Pck)                              |

|         | DCDR[5:0]     |             |             | クロック分周比                                            |

|         |               |             |             | B'000110: 1/6 分周 (5.5 MHz 設定)                      |

| LDMTR   | FLMPOL        | H'FFFF FC02 | H'C02B      | FML (垂直同期) 極性選択                                    |

|         |               |             |             | B'1: LCD_FML パルスはローアクティブ                           |

|         | CL1POL        |             |             | CL1 (水平同期) 極性選択                                    |

|         |               |             |             | B'1: LCD_CL1 パルスはローアクティブ                           |

|         | DISPPOL       |             |             | DISP (表示許可) 極性選択                                   |

|         |               |             |             | B'0: LCD_M_DISP パルスはハイアクティブ                        |

|         | DPOL          |             |             | 表示データ極性選択                                          |

|         |               |             |             | B'0: LCD_DATA パルスはハイアクティブ                          |

|         | MCNT          |             |             | M 信号制御                                             |

|         |               |             |             | B'0: M (AC ラインモジュレーション) 信号を出力する                    |

|         | CL1CNT        |             |             | CL1 (水平同期) 制御                                      |

|         |               |             |             | B'0: 垂直帰線期間中, LCD_CL1 は出力する                        |

|         | CL2CNT        |             |             | CL2 (液晶モジュールのドットクロック) 制御                           |

|         |               |             |             | B'0: 垂直水平帰線期間中, LCD_CL2 は出力する                      |

|         | MIFTYP[5:0]   |             |             | モジュールインタフェースタイプ選択                                  |

|         |               |             |             | B'101011: TFT カラー,16 ビットデータバス                      |

| LDDFR   | PABD          | H'FFFF FC04 | H'002D      | バイトデータピクセルアライメント                                   |

|         |               |             |             | B'0: バイトデータ内をビッグエンディアン                             |

|         | DSPCOLOR[6:0] |             |             | 表示カラー選択                                            |

|         |               |             |             | B'0101101: カラー,64 K (RGB:5-6-5),16 bpp             |

| LDSMR   | ROT           | H'FFFF FC06 | H'0000      | ローテーションモジュール選択                                     |

|         |               |             |             | B'0: 回転しない                                         |

|         | AU[1:0]       |             |             | アクセスユニット選択                                         |

|         |               |             |             | B'00: 4 バースト                                       |

| LDSARU  | SAU25 ~ SAU4  | H'FFFF FC08 | H'0C00 0000 | 上部パネル表示データの取り込み開始アドレス                              |

|         |               |             |             | H'0C00 0000: 表示データの取り込み開始アドレス                      |

|         |               |             |             | はエリア3のシンクロナス DRAM 領                                |

| I DOAD! | SAL25 ~ SAL4  | LUEEEE E000 |             | 域内に設定                                              |

| LDSARL  | SAL25 ~ SAL4  | H'FFFF FC0C | _           | 下部パネル表示データの読み取り開始アドレス                              |

|         |               |             |             | TFT: 使用しません。<br>  表示データの取り込み開始アドレスはエリア3のシ          |

|         |               |             |             | 表示アータの取り込み開始アトレスはエリア3のシ  <br>  ンクロナス DRAM 領域内に設定   |

| LDLAOR  | LAO15 ~ LAO0  | H'FFFF FC10 | H'0200      | ラインアドレスオフセット                                       |

| LDLAUK  | LACISTLACO    | TITEFF FOID | 110200      | 256 × 2 = H'0200                                   |

|         |               |             |             | 236×2= 0200<br>  画像イメージ横幅 (この例では 240 画素) 以上の 2     |

|         |               |             |             | 回家・パーラ損幡(この)がでは2+0回祭)のエの2   のべき乗の値を推奨します。推奨値に設定するた |

|         |               |             |             | め,512を設定します。                                       |

|         | 1             | l           | L           | ======                                             |

# 表 10 LCDC レジスタ設定 (2)

| レジスタ名   | ビット名            | アドレス        | 設定値    | 設定説明                                                             |

|---------|-----------------|-------------|--------|------------------------------------------------------------------|

| LDPALCR | PALS            | H'FFFF FC12 | H'0000 | パレット状態                                                           |

|         |                 |             |        | B'0: LCDC がパレットを使用。通常表示モード                                       |

|         | PALEN           |             |        | パレット読み出し/書き込みイネーブル                                               |

|         |                 |             |        | B'0: 通常表示モードへの遷移要求                                               |

| LDPR00  | PALDnn23        | H'FFFF F800 | -      | パレットデータ                                                          |

| ~       | ~               | ~           |        | パレット未使用のため未設定                                                    |

| LDPRFF  | PALDnn0         | H'FFFF FBFC |        |                                                                  |

| LDHCNR  | HDCN7           | H'FFFF FC14 | H'1D20 | 水平表示キャラクタナンバー                                                    |

|         | HDCN6           |             |        | 水平画面方向の表示キャラクタ数を設定します (キャラ                                       |

|         | HDCN5           |             |        | クタ = 8 ドット単位)。                                                   |

|         | HDCN4           |             |        | 本例では横幅 240 ピクセルですので ,                                            |

|         | HDCN3           |             |        | HDCN = (表示キャラクタ数) – 1 = (240 / 8) – 1                            |

|         | HDCN2           |             |        | = 29 = H'1D                                                      |

|         | HDCN1           |             |        | とします。                                                            |

|         | HDCN0           | -           |        | 1.70                                                             |

|         | HTCN7           |             |        | 水平総キャラクタナンバー                                                     |

|         | HTCN6           |             |        | 水平画面方向の総キャラクタ数を設定します (キャラク                                       |

|         | HTCN5           |             |        | タ = 8 ドット単位)。<br>最小の水平帰線期間は 3 キャラクタ (24 ドット) です                  |

|         | HTCN4           |             |        | 版小の小千帰線期間は3 キャラグラ (24 ドッド) に9     が、本例では水平帰線期間を10 キャラクタ (80 ドット) |

|         | HTCN3           |             |        | とします。                                                            |

|         | HTCN2           |             |        | HTCN = [ (240 / 8) – 1] + 3 = 32 = H'20                          |

|         | HTCN1           |             |        | とします。                                                            |

| LDHSYNR | HTCN0<br>HSYNW3 | H'FFFF FC16 | H'0022 | ・・・・・・   水平同期信号幅                                                 |

| LDHSTNK | HSYNW2          | HEFFE FC 10 | H 0022 | 水平向新信号幅<br>  水平画面方向の同期信号 (CL1, Hsync) 幅を設定します                    |

|         | HSYNW1          |             |        | (キャラクタ = 8 ドット単位)。                                               |

|         | HSYNW0          |             |        | HSYNW = (水平同期信号幅) – 1                                            |

|         | 11011400        |             |        | = (8 ドット/8 ドット/キャラクタ) – 1 = 0                                    |

|         | HSYNP7          | -           |        | 水平同期信号出力位置                                                       |

|         | HSYNP6          |             |        | 水平画面方向の同期信号の出力位置を設定します (キャ                                       |

|         | HSYNP5          |             |        | ラクタ = 8 ドット単位)。                                                  |

|         | HSYNP4          |             |        | (水平同期信号出力位置) - 1 の値を設定してください。                                    |

|         | HSYNP3          |             |        | HSYNP = [ (272 / 8) + 1] - 1 = H'22                              |

|         | HSYNP2          |             |        |                                                                  |

|         | HSYNP1          |             |        |                                                                  |

|         | HSYNP0          |             |        |                                                                  |

| LDVDLNR | VDLN10          | H'FFFF FC18 | H'013F | 垂直表示ラインナンバー                                                      |

|         | VDLN9           |             |        | 垂直画面方向の表示ライン数を設定します (ライン単                                        |

|         | VDLN8           |             |        | 位)。                                                              |

|         | VDLN7           |             |        | (表示ライン数) - 1 の値を設定してください。                                        |

|         | VDLN6           |             |        | VDLN = 320 – 1 = H'013F                                          |

|         | VDLN5           |             |        |                                                                  |

|         | VDLN4           |             |        |                                                                  |

|         | VDLN3           |             |        |                                                                  |

|         | VDLN2           |             |        |                                                                  |

|         | VDLN1           |             |        |                                                                  |

|         | VDLN0           |             |        |                                                                  |

# 表 11 LCDC レジスタ設定 (3)

| レジスタ名   | ビット名    | アドレス        | 設定値    | 設定説明                                     |

|---------|---------|-------------|--------|------------------------------------------|

| LDVTLNR | VTLN10  | H'FFFF FC1A | H'0143 | 垂直総ラインナンバー                               |

|         | VTLN9   |             |        | 垂直画面方向の総ライン数を設定します (ライン単位)。              |

|         | VTLN8   |             |        | (総ライン数) – 1 の値を設定してください。                 |

|         | VTLN7   |             |        | 最小の垂直総ライン数は2ラインです。                       |

|         | VTLN6   |             |        | VTLN≥VDLN, VTLN≥1を満足してください。              |

|         | VTLN5   |             |        | VDLN = 324 – 1 = H'0143                  |

|         | VTLN4   |             |        |                                          |

|         | VTLN3   |             |        |                                          |

|         | VTLN2   |             |        |                                          |

|         | VTLN1   |             |        |                                          |

|         | VTLN0   |             |        |                                          |

| LDVSYNR | VSYNW3  | H'FFFF FC1C | H'1143 | 垂直同期信号幅                                  |

|         | VSYNW2  |             |        | 垂直画面方向の同期信号 (FLM, Vsync) 幅を設定します         |

|         | VSYNW1  |             |        | (ライン単位)。                                 |

|         | VSYNW0  |             |        | (垂直同期信号幅) – 1 の値を設定してください。               |

|         |         |             |        | 垂直同期信号幅2ラインなので                           |

|         |         |             |        | VSYNW = (2 – 1) = H'01                   |

|         | VSYNP10 |             |        | 垂直同期信号出力位置                               |

|         | VSYNP9  |             |        | 垂直画面方向の同期信号 (FLM, Vsync) の出力位置を設         |

|         | VSYNP8  |             |        | 定します (ライン単位)。                            |

|         | VSYNP7  |             |        | (垂直同期信号出力位置)-2の値を設定してください。               |

|         | VSYNP6  |             |        | DSTN の場合は奇数値を設定してください。                   |

|         | VSYNP5  |             |        | (設定値 + 1) / 2 として扱われます。                  |

|         | VSYNP4  |             |        | 320 ラインの液晶モジュールを使用し ,帰線期間が 0 ライ          |

|         | VSYNP3  |             |        | ン ,つまり VTLN = 323 で 1 ライン目に垂直同期信号をア      |

|         | VSYNP2  |             |        | クティブにする場合                                |

|         | VSYNP1  |             |        | ・シングルディスプレイの場合                           |

|         | VSYNP0  |             |        | $VSYNP = [(1-1) + VTLN] \mod (VTLN + 1)$ |

|         |         |             |        | $= [(1-1) + 323] \mod (324+1)$           |

|         |         |             |        | = 323mod324 = 323 = H'143                |

| LDACLNR | ACLN4   | H'FFFF FC1E | _      | AC ラインナンバー                               |

|         | ACLN3   |             |        | 液晶モジュール交流化信号をトグルする行数を設定しま                |

|         | ACLN2   |             |        | す (ライン単位)。                               |

|         | ACLN1   |             |        | (トグルする行数) - 1 の値を設定してください。               |

|         | ACLN0   |             |        | 本応用例では使用していません。                          |

# 表 12 LCDC レジスタ設定 (4)

| レジスタ名  | ビット名     | アドレス        | 設定値    | 設定説明                                                           |

|--------|----------|-------------|--------|----------------------------------------------------------------|

| LDINTR | MINTEN   | H'FFFF FC20 | H'0000 | メモリアクセス割り込みイネーブル                                               |

|        |          |             |        | B'0: 割り込みを発生しません。                                              |

|        | FINTEN   | 1           |        | フレーム終了割り込みイネーブル                                                |

|        |          |             |        | B'0: 割り込みを発生しません。                                              |

|        | VSINTEN  |             |        | Vsync 開始割り込みイネーブル                                              |

|        |          |             |        | B'0: 割り込みを発生しません。                                              |

|        | VEINTEN  |             |        | Vsync 終了割り込みイネーブル                                              |

|        |          |             |        | B'0: 割り込みを発生しません。                                              |

|        | MINTS    |             |        | メモリアクセス割り込み状態                                                  |

|        |          |             |        | メモリアクセス割り込みの処理状態を表します。                                         |

|        | FINTS    |             |        | フレーム終了割り込み状態                                                   |

|        |          |             |        | フレーム終了割り込みの処理状態を表します。                                          |

|        | VSINTS   |             |        | Vsync 開始割り込み状態                                                 |

|        |          |             |        | LCDC Vsync 開始割り込みの処理状態を表します。                                   |

|        | VEINTS   |             |        | Vsync 終了割り込み状態                                                 |

|        |          |             |        | LCDC Vsync 終了割り込みの処理状態を表します。                                   |

| LDPMMR | ONC3     | H'FFFF FC24 | H'FF70 | LCDC 電源投入シーケンス期間                                               |

|        | ONC2     |             |        | LCD モジュールの電源投入シーケンスにおいて                                        |

|        | ONC1     |             |        | LCD_VEPWC 端子のアサートから LCD_DON 端子のア                               |

|        | ONC0     |             |        | サートまでの期間をフレーム周期単位設定します。                                        |

|        |          |             |        | (期間) – 1 の値を設定してください。                                          |

|        |          |             |        | 詳細は「SH7263 グループ ハードウェアマニュアル                                    |

|        |          |             |        | (RJJ09B0284) 電源制御シーケンスと液晶モジュールの                                |

|        |          |             |        | 動作状態」を参照ください。                                                  |

|        | OFFD3    |             |        | LCDC 電源遮断シーケンス期間                                               |

|        | OFFD2    |             |        | LCD モジュールの電源遮断シーケンスにおいて                                        |

|        | OFFD1    |             |        | LCD_DON 端子のネゲートから LCD_VEPWC 端子のネ                               |

|        | OFFD0    |             |        | ゲートまでの期間をフレーム周期単位で設定します。                                       |

|        |          |             |        | (期間) - 1 の値を設定してください。                                          |

|        |          |             |        | 詳細は「SH7263 グループ ハードウェアマニュアル<br>(RJJ09B0284) 電源制御シーケンスと液晶モジュールの |

|        |          |             |        | (1330950204)  電源制御シーグンスと液晶とジュールの   動作状態」を参照ください。               |

|        | VCPE     |             |        | LCD_VCPWC 端子イネーブル                                              |

|        | VCFE     |             |        | B'1: LCD_VCPWC 端子を用いた電源制御シーケンス処理                               |

|        |          |             |        | の有無を設定します。                                                     |

|        | VEPE     | _           |        | LCD_VEPWC 端子イネーブル                                              |

|        | VEIL     |             |        | B'1: LCD_VEPWC 端子を用いた電源制御シーケンス処理                               |

|        |          |             |        | の有無を設定します。                                                     |

|        | DONE     | 1           |        | LCD_DON 端子イネーブル                                                |

|        | 30.12    |             |        | B'1: LCD_DON 端子を用いた電源制御シーケンス処理の                                |

|        |          |             |        | 有無を設定します。                                                      |

|        | LPS[1:0] | 1           |        | 液晶モジュール電源入力状態                                                  |

|        | 5[0]     |             |        | B'00: 電源 ,制御機能を使用しているときの液晶モジュー                                 |

|        |          |             |        | ルの電源投入状態を示します。                                                 |

# 表 13 LCDC レジスタ設定 (5)

| レジスタ名  | ビット名  | アドレス        | 設定値    | 設定説明                                   |

|--------|-------|-------------|--------|----------------------------------------|

| LDPSPR | ONA3  | H'FFFF FC26 | H'0000 | LCDC 電源投入シーケンス期間                       |

|        | ONA2  |             |        | LCD モジュールの電源投入シーケンスにおいて                |

|        | ONA1  |             |        | LCD_VCPWC 端子のアサートから表示データ               |

|        | ONA0  |             |        | (LCD_DATA) とタイミング信号 (LCD_FLM, LCD_CL1, |

|        |       |             |        | LCD_CL2, LCD_M_DISP) の出力開始までの期間をフ      |

|        |       |             |        | レーム周期単位で設定します。                         |

|        |       |             |        | (期間) – 1 の値を設定してください。                  |

|        | ONB3  |             |        | LCDC 電源投入シーケンス期間                       |

|        | ONB2  |             |        | LCD モジュールの電源投入シーケンスにおいて表示デー            |

|        | ONB1  |             |        | タ (LCD_DATA) とタイミング信号 (LCD_FLM,        |

|        | ONB0  |             |        | LCD_CL1, LCD_CL2, LCD_M_DISP) の出力開始から  |

|        |       |             |        | LCD_VEPWC 端子のアサートまでの期間をフレーム周           |

|        |       |             |        | 期単位で設定します。                             |

|        |       |             |        | (期間) – 1 の値を設定してください。                  |

|        | OFFE3 |             |        | LCDC 電源遮断シーケンス期間                       |

|        | OFFE2 |             |        | 液晶モジュールの電源遮断シーケンスにおいて                  |

|        | OFFE1 |             |        | LCD_VEPWC 端子ネゲートから表示データ                |

|        | OFFE0 |             |        | (LCD_DATA) とタイミング信号 (LCD_FLM, LCD_CL1, |

|        |       |             |        | LCD_CL2, LCD_M_DISP) の出力停止までの期間をフ      |

|        |       |             |        | レーム周期単位で設定します。                         |

|        |       |             |        | (期間) – 1 の値を設定してください。                  |

|        | OFFF3 |             |        | LCDC 電源遮断シーケンス期間                       |

|        | OFFF2 |             |        | 液晶モジュールの電源遮断シーケンスにおいて表示デー              |

|        | OFFF1 |             |        | タ (LCD_DATA) とタイミング信号 (LCD_FLM,        |

|        | OFFF0 |             |        | LCD_CL1, LCD_CL2, LCD_M_DISP) の出力停止から  |

|        |       |             |        | LCD_VCPWC 端子のネゲートまでの期間をフレーム周期          |

|        |       |             |        | 単位で設定します。                              |

|        |       |             | T1 1/  | (期間) – 1 の値を設定してください。                  |

| LDCNTR | DON2  | H'FFFF FC28 | 動作時:   | ディスプレイオン 2                             |

|        |       |             | H'0011 | LCDC による表示動作開始を指示します。                  |

|        |       |             |        | 0: LCDC 動作/終了中                         |

|        |       |             | 非動作時:  | 1: 動作開始                                |

|        |       |             | H'0000 | このビットを読み出すと常に0が読み出されます。表示              |

|        |       |             |        | 動作開始時のみ1を書き込み,表示動作開始以外では書              |

|        |       |             |        | き込まないでください。                            |

|        | DON   |             |        | ディスプレイオン                               |

|        |       |             |        | LCDC による表示動作の開始/終了を指示します。制御            |

|        |       |             |        | シーケンスの状態は LDPMMR の LPS[1:0] 値を参照する     |

|        |       |             |        | ことで確認できます。                             |

|        |       |             |        | 0: LCDC 非動作。表示オフモード                    |

|        |       |             |        | 1: LCDC 動作。表示オンモード                     |

# 表 14 LCDC レジスタ設定 (6)

| レジスタ名     | ビット名     | アドレス        | 設定値    | 設定説明                               |

|-----------|----------|-------------|--------|------------------------------------|

| LDUINTR   | UINTEN   | H'FFFF FC34 | H'0000 | ユーザ指定割り込みイネーブル                     |

|           |          |             |        | B'0: LCDC ユーザ指定割り込みを発生しません。        |

|           | UINTS    |             |        | ユーザ指定割り込み状態                        |

|           |          |             |        | LCDC ユーザ割り込みが発生した時点で1を示します(セット     |

|           |          |             |        | 状態)。ユーザ指定割り込みに対する処理ルーチン中で,レジ       |

|           |          |             |        | スタへの0書き込みでクリアしてください。               |

| LDUINTLNR | UINTLN10 | H'FFFF FC36 | _      | ユーザ指定割り込み発生ラインナンバー                 |

|           | UINTLN9  |             |        | ユーザ指定割り込みを発生するラインを設定します (ライン       |

|           | UINTLN8  |             |        | 単位)。                               |

|           | UINTLN7  |             |        | (割り込み発生ライン数)-1の値を設定してください。         |

|           | UINTLN6  |             |        | SNT/TFT の液晶モジュールを使用する場合 ,本レジスタの設   |

|           | UINTLN5  |             |        | 定値は LDVDLNR の垂直表示ラインナンバー (VDLN) 以下 |

|           | UINTLN4  |             |        | にしてください。                           |

|           | UINTLN3  |             |        |                                    |

|           | UINTLN2  |             |        |                                    |

|           | UINTLN1  |             |        |                                    |

|           | UINTLN0  |             |        |                                    |

| LDLIRNR   | LIRN7    | H'FFFF FC40 | H'0000 | LCDC の VRAM 読み出しバスクロック間隔           |

|           | ~        |             |        | LCDC が VRAM を読み出すバーストバスサイクルの間に実行   |

|           | LIRN0    |             |        | 可能な CPU/DMAC のバスサイクルの数を指定します。      |

|           |          |             |        | H'00: 1 バスクロック                     |

#### 3. 参考ドキュメント

- ソフトウェアマニュアル SH-2A, SH2A-FPU ソフトウェアマニュアル (RJJ09B0086) (最新版をルネサス テクノロジホームページから入手してください)

- ハードウェアマニュアル SH7263 グループ ハードウェアマニュアル (RJJ09B0284) (最新版をルネサス テクノロジホームページから入手してください)

ホームページとサポート窓口

ルネサス テクノロジホームページ

http://japan.renesas.com/

お問合せ先

http://japan.renesas.com/inquiry

csc@renesas.com

# 改訂記録

|      |            | 改訂内容 |      |  |

|------|------------|------|------|--|

| Rev. | 発行日        | ページ  | ポイント |  |

| 1.00 | 2009.03.11 | _    | 初版発行 |  |

|      |            |      |      |  |

|      |            |      |      |  |

|      | _          |      |      |  |

|      | _          |      |      |  |

すべての商標および登録商標は,それぞれの所有者に帰属します。

#### 本資料ご利用に際しての留意事項 =

- 1. 本資料は、お客様に用途に応じた適切な弊社製品をご購入いただくための参考資料であり、本資料中に記載の技術情報について弊社または第三者の知的財産権その他の権利の実施、使用を許諾または保証するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例など全ての情報の使用に起因する損害、第三者の知的財産権その他の権利に対する侵害に関し、弊社は責任を負いません。

- 3. 本資料に記載の製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他 軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替および外国貿易法」 その他輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。

- 4. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例などの全ての情報は本資料発行時点のものであり、弊社は本資料に記載した製品または仕様等を予告なしに変更することがあります。弊社の半導体製品のご購入およびご使用に当たりましては、事前に弊社営業窓口で最新の情報をご確認いただきますとともに、弊社ホームページ(http://www.renesas.com)などを通じて公開される情報に常にご注意ください。

- 5. 本資料に記載した情報は、正確を期すため慎重に制作したものですが、万一本資料の記述の誤りに 起因する損害がお客様に生じた場合においても、弊社はその責任を負いません。

- 6. 本資料に記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他 応用回路例などの情報を流用する場合は、流用する情報を単独で評価するだけでなく、システム 全体で十分に評価し、お客様の責任において適用可否を判断してください。弊社は、適用可否に 対する責任は負いません。

- 7. 本資料に記載された製品は、各種安全装置や運輸・交通用、医療用、燃焼制御用、航空宇宙用、原子力、海底中継用の機器・システムなど、その故障や誤動作が直接人命を脅かしあるいは人体に危害を及ぼすおそれのあるような機器・システムや特に高度な品質・信頼性が要求される機器・システムでの使用を意図して設計、製造されたものではありません(弊社が自動車用と指定する製品を自動車に使用する場合を除きます)。これらの用途に利用されることをご検討の際には、必ず事前に弊社営業窓口へご照会ください。なお、上記用途に使用されたことにより発生した損害等について弊社はその責任を負いかねますのでご了承願います。

- 8. 第7項にかかわらず、本資料に記載された製品は、下記の用途には使用しないでください。これらの用途に使用されたことにより発生した損害等につきましては、弊社は一切の責任を負いません。

- 1)生命維持装置。

- 2) 人体に埋め込み使用するもの。

- 3)治療行為(患部切り出し、薬剤投与等)を行うもの。

- 4) その他、直接人命に影響を与えるもの。

- 9. 本資料に記載された製品のご使用につき、特に最大定格、動作電源電圧範囲、放熱特性、実装条件 およびその他諸条件につきましては、弊社保証範囲内でご使用ください。弊社保証値を越えて製品 をご使用された場合の故障および事故につきましては、弊社はその責任を負いません。

- 10. 弊社は製品の品質および信頼性の向上に努めておりますが、特に半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。弊社製品の故障または誤動作が生じた場合も人身事故、火災事故、社会的損害などを生じさせないよう、お客様の責任において冗長設計、延焼対策設計、誤動作防止設計などの安全設計(含むハードウェアおよびソフトウェア)およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特にマイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 1 1. 本資料に記載の製品は、これを搭載した製品から剥がれた場合、幼児が口に入れて誤飲する等の 事故の危険性があります。お客様の製品への実装後に容易に本製品が剥がれることがなきよう、 お客様の責任において十分な安全設計をお願いします。お客様の製品から剥がれた場合の事故に つきましては、弊社はその責任を負いません。

- 12. 本資料の全部または一部を弊社の文書による事前の承諾なしに転載または複製することを固く お断りいたします。

- 13. 本資料に関する詳細についてのお問い合わせ、その他お気付きの点等がございましたら弊社営業 窓口までご照会ください。

D039444

© 2009. Renesas Technology Corp., All rights reserved.