-

-

-

Design Resources

- Design & Development

- Featured Design Tools

- Partners

- Content & Training

-

Support

-

Support Forums

Get help from our expert Renesas technical staff and community.

- Technical Support

- Training & Events

- Quality & Packaging

-

Support Forums

-

Sample & Buy

-

Buy Direct from Renesas

Customers can now choose the convenience of buying direct from Renesas.

- Ordering Resources

-

Buy Direct from Renesas

723624

circleObsolete256 x 36 x 2 SyncBiFIFO, 5.0V

Jump to Page Section:

arrow_drop_down

Overview

Description

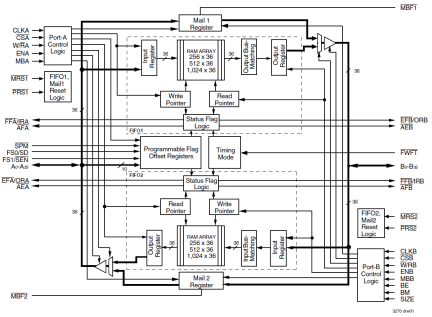

The 723624 is a CMOS bidirectional synchronous (clocked) FIFO. Two independent 256 x 36 dual-port SRAM FIFOs on board each chip buffer data in opposite directions. The clocks for each port are independent of one another and can be asynchronous or coincident. The enables for each port are arranged to provide a simple bidirectional interface between microprocessors and/or buses with synchronous control.

Features

- Clock frequencies up to 83 MHz (8 ns access time)

- Two independent clocked FIFOs buffering data in opposite directions

- Programmable Almost-Empty and Almost-Full flags

- Serial or parallel programming of partial flags

- Port B bus sizing of 36-bits (long word), 18-bits (word) and 9-bits (byte)

- Big- or Little-Endian format for word and byte bus sizes

- Mailbox bypass registers for each FIFO

- Free-running CLKA and CLKB may be asynchronous or coincident

- Auto power down minimizes power dissipation

- Available 128-pin TQFP package

- Industrial temperature range (–40C to +85C) is available

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Product Options

Processing table

Pkg. Type |

Lead Count (#) |

Temp. Grade |

Pb (Lead) Free |

Carrier Type |

Price (USD) | 1ku |

Buy / Sample |

|

|---|---|---|---|---|---|---|---|

| Part Number | |||||||

| TQFP | 128 | C | No | Tray | |||

| TQFP | 128 | C | No | Reel | |||

| TQFP | 128 | C | Yes | Tray | 66.04 | ||

| TQFP | 128 | C | Yes | Reel | 55 |

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product