発行日: 2015年3月%1日

# RENESAS TECHNICAL UPDATE

〒211-8668 神奈川県川崎市中原区下沼部 1753 ルネサス エレクトロニクス株式会社

問合せ窓口 http://japan.renesas.com/contact/

E-mail: csc@renesas.com

| 製   | 品分類            | MPU & MCU                                                          | 発行番号   | TN-RX*-A118A/J |      | Rev. A % % |

|-----|----------------|--------------------------------------------------------------------|--------|----------------|------|------------|

| 題名  | MTU2           | A/D 変換ディレイド機能の使用上の注意事                                              | 情報分類   | 技術情報           |      |            |

| 適   |                | /621 グループ                                                          | 対象ロット等 |                |      |            |

| 用製品 | RX210<br>RX21A | /631 グループ、RX630 グループ<br>グループ、RX220 グループ<br>グループ、RX111 グループ<br>グループ | 全ロット   | 関連資料           | 下記参照 |            |

マルチファンクションタイマパルスユニット2 (MTU2,MTU2a) に以下に示す注意事項があります。

また、これらに伴いマニュアルを訂正しますので、訂正内容を示します。RX62N グループ、RX621 グループユーザーズマニュアル ハードウェア編を例に、ユーザーズマニュアルの訂正内容を記載します。

その他のグループのマニュアルでの掲載箇所は末尾の「適用製品及び関連資料」を参考にしてください。

## 【注意事項】

# 1. A/D 変換ディレイド機能による A/D 変換の開始要求の許可期間について

- 相補 PWM モードにおいて、MTUn.TADCR の UT4AE、UT4BE ビットに 1 を設定すると、MTUn.TCNT のアップカウント期間に A/D 変換の開始要求を許可します。A/D 変換の開始要求の許可期間は、0 ≦ MTUn.TCNT ≦ TCDR-1 です。

- 相補 PWM モードにおいて、MTUn.TADCR の DT4AE、DT4BE ビットに 1 を設定すると、MTUn.TCNT のダウンカウント期間に A/D 変換の開始要求を許可します。A/D 変換の開始要求の許可期間は、TCDR ≥ MTUn.TCNT ≥ 1 です。

- 相補 PWM モード以外のときは、MTUn.TADCR の DT4AE、DT4BE ビットに 0 を設定してください。MTUn.TADCR の UT4AE、UT4BE ビットに 1 を設定すると、MTUn.TCNT のアップ/ダウンカウントに関係なく、MTUn.TCNT と MTUn.TADCORA/B のコンペアマッチで A/D 変換の開始要求を行います。(n=4,10)

#### 2. 相補 PWM モードにおける A/D 変換ディレイド機能について

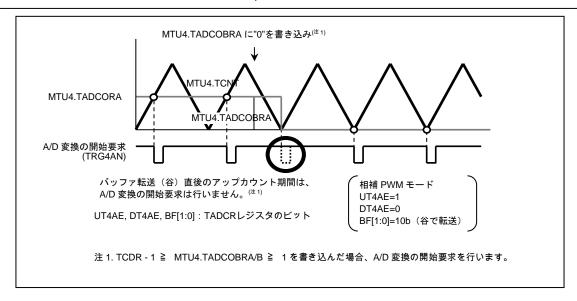

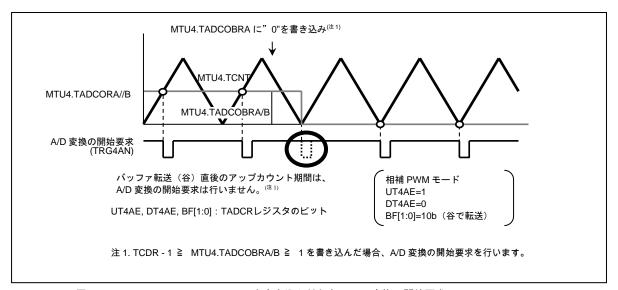

- MTUn.TADCOBRA/B に 0、かつ、MTUn.TADCR の UT4AE、UT4BE ビットに 1 を設定して、MTUn.TCNT の谷でバッファ転送した時、転送直後のアップカウント期間については A/D 変換の開始要求を行いません (図 2.1)。

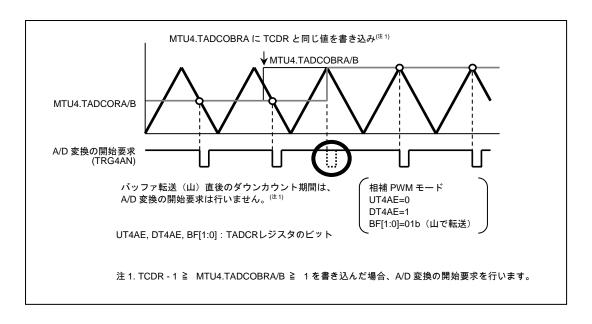

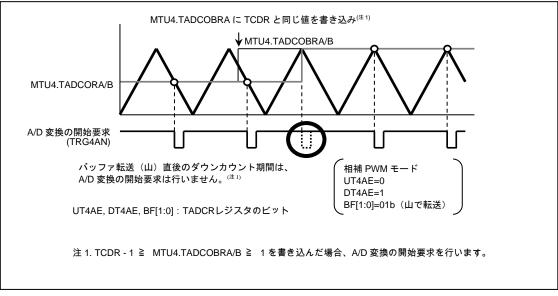

- MTUn.TADCOBRA/Bに TCDR と同じ値、かつ、MTUn.TADCR の DT4AE、DT4BE ビットに 1 を設定して、MTUn.TCNT の山でバッファ転送した時、転送直後のダウンカウント期間については A/D 変換の開始要求を行いません (図 2.2)。

- 割り込み間引き機能と連動して A/D 変換の開始要求を行う場合、2 ≦ MTUn.TADCORA/B ≦ TCDR-2 を満たすように MTUn.TADCORA/B を設定してください。(n=4,10)

図 2.1 MTU4.TADCOBRA に"0"を書き込んだときの A/D 変換の開始要求(ユニット 0)

図 2.2 MTU4.TADCOBRA に TCDR と同じ値を書き込んだときの A/D 変換の開始要求(ユニット 0)

【マニュアル修正内容】

# 18.2.9 タイマ A/D 変換開始要求コントロールレジスタ(TADCR)

< 訂正前(p.896) >

アドレス MTU4.TADCR 0008 8640h、MTU10.TADCR 0008 8A40h

注 1. b6、b4~0 は、相補 PWM モード以外では、"1"に設定しないでください。

| ビット     | シンボル    | ビット名                             | 機能                                                                                                 | R/W |

|---------|---------|----------------------------------|----------------------------------------------------------------------------------------------------|-----|

| b0      | ITB4VE  | TCIV4割り込み間引き連動<br>許可ビット          | 0:TCI4V割り込み間引き機能と連動しない<br>1:TCI4V割り込み間引き機能と連動する                                                    | R/W |

| b1      | ITB3AE  | TGIA3割り込み間引き連動<br>許可ビット          | 0:TGI3A割り込み間引き機能と連動しない<br>1:TGI3A割り込み間引き機能と連動する                                                    | R/W |

| b2      | ITA4VE  | TCIV4割り込み間引き連動<br>許可ビット          | 0:TCI4V割り込み間引き機能と連動しない<br>1:TCI4V割り込み間引き機能と連動する                                                    | R/W |

| b3      | ITA3AE  | TGIA3割り込み間引き連動<br>許可ビット          | 0:TGI3A割り込み間引き機能と連動しない<br>1:TGI3A割り込み間引き機能と連動する                                                    | R/W |

| b4      | DT4BE   | ダウンカウントTRG4BN<br>許可ビット           | 0: MTU4.TCNTのダウンカウント時にA/D変換の開始<br>要求(TRG4BN)を禁止<br>1: MTU4.TCNTのダウンカウント時にA/D変換の開始<br>要求(TRG4BN)を許可 | R/W |

| b5      | UT4BE   | アップカウントTRG4BN<br>許可ビット           | 0: MTU4.TCNTのアップカウント時にA/D変換の開始<br>要求(TRG4BN)を禁止<br>1: MTU4.TCNTのアップカウント時にA/D変換の開始<br>要求(TRG4BN)を許可 | R/W |

| b6      | DT4AE   | ダウンカウントTRG4AN 許可ビット              | 0: MTU4.TCNTのダウンカウント時にA/D変換の開始<br>要求(TRG4AN)を禁止<br>1: MTU4.TCNTのダウンカウント時にA/D変換の開始<br>要求(TRG4AN)を許可 | R/W |

| b7      | UT4AE   | アップカウントTRG4AN 許可ビット              | 0: MTU4.TCNTのアップカウント時にA/D変換の開始<br>要求(TRG4AN)を禁止<br>1: MTU4.TCNTのアップカウント時にA/D変換の開始<br>要求(TRG4AN)を許可 | R/W |

| b13-b8  | _       | 予約ビット                            | 読むと"0"が読めます。書く場合、"0"としてください                                                                        | R/W |

| b15-b14 | BF[1:0] | MTU4.TADCOBRA/B 転送タイミング<br>選択ビット | 詳細は表 18.31 を参照してください。                                                                              | R/W |

注 1. チャネル 4 と 10 はそれぞれ同一機能であるため、ここではユニット 0 を説明しています。

注 2. TADCR の 8 ビット単位でのアクセスは禁止です。常に 16 ビット単位でアクセスしてください。

注 3. 割り込み間引きが禁止のとき(タイマ割り込み間引き設定レジスタ(TITCR)の T3AEN、T4VEN ビットを"0" に設定したとき、または TITCR の間引き回数設定ビット(T3ACOR、T4VCOR)を"0"に設定したとき)は、割り込み間引き機能と連動しない(タイマ A/D 変換開始要求コントロールレジスタ(TADCR)の ITA3AE、ITA4VE、ITB3AE、ITB4VE ビットを 0 に設定)設定にしてください

注 4. 割り込み間引きが禁止のときに、割り込み間引きと連動する設定にした場合、A/D 変換の開始要求が行われません。

日:2015年3月11日

< 訂正後(p.896) >

アドレスMTU4.TADCR 0008 8640h、MTU10.TADCR 0008 8A40h

注 1. b6、b4~0 は、相補 PWM モード以外では、0 を設定してください。

| ビット     | シンボル                | ビット名                             | 機能                                                                                                 | R/W |

|---------|---------------------|----------------------------------|----------------------------------------------------------------------------------------------------|-----|

| b0      | ITB4VE<br>(注 1,注 2) | TCIV4割り込み間引き連動<br>許可ビット          | 0:TCI4V割り込み間引き機能と連動しない<br>1:TCI4V割り込み間引き機能と連動する                                                    | R/W |

| b1      | ITB3AE<br>(注 1,注 2) | TGIA3割り込み間引き連動<br>許可ビット          | 0:TGI3A割り込み間引き機能と連動しない<br>1:TGI3A割り込み間引き機能と連動する                                                    | R/W |

| b2      | ITA4VE<br>(注 1,注 2) | TCIV4割り込み間引き連動<br>許可ビット          | 0:TCI4V割り込み間引き機能と連動しない<br>1:TCI4V割り込み間引き機能と連動する                                                    | R/W |

| b3      | ITA3AE<br>(注 1,注 2) | TGIA3割り込み間引き連動<br>許可ビット          | 0:TGI3A割り込み間引き機能と連動しない<br>1:TGI3A割り込み間引き機能と連動する                                                    | R/W |

| b4      | DT4BE               | ダウンカウントTRG4BN<br>許可ビット           | 0: MTU4.TCNTのダウンカウント時にA/D変換の開始<br>要求(TRG4BN)を禁止<br>1: MTU4.TCNTのダウンカウント時にA/D変換の開始<br>要求(TRG4BN)を許可 | R/W |

| b5      | UT4BE               | アップカウントTRG4BN<br>許可ビット           | 0: MTU4.TCNTのアップカウント時にA/D変換の開始<br>要求(TRG4BN)を禁止<br>1: MTU4.TCNTのアップカウント時にA/D変換の開始<br>要求(TRG4BN)を許可 | R/W |

| b6      | DT4AE               | ダウンカウントTRG4AN 許可ビット              | 0: MTU4.TCNTのダウンカウント時にA/D変換の開始<br>要求(TRG4AN)を禁止<br>1: MTU4.TCNTのダウンカウント時にA/D変換の開始<br>要求(TRG4AN)を許可 | R/W |

| b7      | UT4AE               | アップカウントTRG4AN 許可ビット              | 0: MTU4.TCNTのアップカウント時にA/D変換の開始<br>要求(TRG4AN)を禁止<br>1: MTU4.TCNTのアップカウント時にA/D変換の開始<br>要求(TRG4AN)を許可 | R/W |

| b13-b8  | _                   | 予約ビット                            | 読むと"0"が読めます。書く場合、"0"としてください                                                                        | R/W |

| b15-b14 | BF[1:0]             | MTU4.TADCOBRA/B 転送タイミング<br>選択ビット | 詳細は表18.31を参照してください。                                                                                | R/W |

注. チャネル4と10はそれぞれ同一機能であるため、ここではユニット0を説明しています。

注. TADCR の 8 ビット単位でのアクセスは禁止です。常に 16 ビット単位でアクセスしてください。

注 1. 割り込み間引きが禁止のとき (タイマ割り込み間引き設定レジスタ (TITCR) の T3AEN、T4VEN ビットを"0" に設定した

とき、または TITCR の間引き回数設定ビット(T3ACOR、T4VCOR)を"0"に設定したとき)は、"<mark>0"にしてください</mark>。

注 2. 割り込み間引きが禁止のときに、割り込み間引きと連動する設定にした場合、A/D 変換の開始要求が行われません。

日:2015年3月11日

## < 訂正前 897 >

表 18.31 BF[1:0]ビットによる転送タイミングの設定

| ビット 15 | ビット14 | 説明                                               |

|--------|-------|--------------------------------------------------|

| BF1    | BF0   |                                                  |

| 0      | 0     | 周期設定バッファレジスタから周期設定レジスタへ転送しない                     |

| 0      | 1     | MTUn.TCNT の山で周期設定バッファレジスタから周期設定レジスタへ転送する(注 1)    |

| 1      | 0     | MTUn.TCNT の谷で周期設定バッファレジスタから周期設定レジスタへ転送する(注 2)    |

| 1      | 1     | MTUn.TCNT の山と谷で周期設定バッファレジスタから周期設定レジスタへ転送する (注 2) |

【記号説明】n=4、10 m=3、9

注1. 相補PWMモードではMTUn.TCNTの山、リセット同期PWMモードではMTUm.TCNTがMTUm.TGRAとコンペアマッチしたとき、PWMモード1 /ノーマルモードではMTUn.TCNTがMTUn.TGRAとコンペアマッチしたときに、周期設定バッファレジスタから周期設定レジスタへ転送します。

注 2. 相補 PWM モード以外では設定禁止です。

# < 訂正後(p.897 >

表 18.31 BF[1:0]ビットによる転送タイミングの設定

| ビット 15 | ビット14 | 説明                                                                                    |                                                                                                        |  |  |

|--------|-------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|

| BF1    | BF0   | 相補 PWM モード時                                                                           | リセット同期 PWM モード時                                                                                        |  |  |

| 0      | 0     | 周期設定パッファレジスタ (MTUn.TADCOBRA/B) から周<br>期設定レジスタ (MTUn.TADCORA/B) へ転送しない                 | 周期設定バッファレジスタ(MTUn.TADCOBRA/B)から周<br>期設定レジスタ(MTUn.TADCORA/B)へ転送しない                                      |  |  |

| 0      | 1     | MTUn.TCNT の山で周期設定バッファレジスタ<br>(MTUn.TADCOBRA/B) から周期設定レジスタ<br>(MTUn.TADCORA/B) へ転送する   | MTUm.TCNT が MTUm.TGRA とコンペアマッチしたとき周<br>期設定パッファレジスタ(MTUn.TADCOBRA/B)から周期<br>設定レジスタ(MTUn.TADCORA/B)へ転送する |  |  |

| 1      | 0     | MTUn.TCNT の谷で周期設定パッファレジスタ<br>(MTUn.TADCOBRA/B) から周期設定レジスタ<br>(MTUn.TADCORA/B) へ転送する   | 設定禁止                                                                                                   |  |  |

| 1      | 1     | MTUn.TCNT の山と谷で周期設定パッファレジスタ<br>(MTUn.TADCOBRA/B) から周期設定レジスタ<br>(MTUn.TADCORA/B) へ転送する | 設定禁止                                                                                                   |  |  |

| ビット15 | ビット14 | 説                                                                                                      | 明                                                                                                      |

|-------|-------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| BF1   | BF0   | PWM モード 1 時                                                                                            | ノーマルモード時                                                                                               |

| 0     | 0     | 周期設定バッファレジスタ (MTUn.TADCOBRA/B) から周<br>期設定レジスタ (MTUn.TADCORA/B) へ転送しない                                  | 周期設定バッファレジスタ(MTUn.TADCOBRA/B)から周<br>期設定レジスタ(MTUn.TADCORA/B)へ転送しない                                      |

| 0     | 1     | MTUn.TCNT が MTUn.TGRA とコンペアマッチしたとき周<br>期設定バッファレジスタ(MTUn.TADCOBRA/B)から周期<br>設定レジスタ(MTUn.TADCORA/B)へ転送する | MTUn.TCNT が MTUn.TGRA とコンペアマッチしたとき周<br>期設定バッファレジスタ(MTUn.TADCOBRA/B)から周期<br>設定レジスタ(MTUn.TADCORA/B)へ転送する |

| 1     | 0     | 設定禁止                                                                                                   | 設定禁止                                                                                                   |

| 1     | 1     | 設定禁止                                                                                                   | 設定禁止                                                                                                   |

【記号説明】n=4、10 m=3、9

日:2015年3月11日

日:2015年3月11日

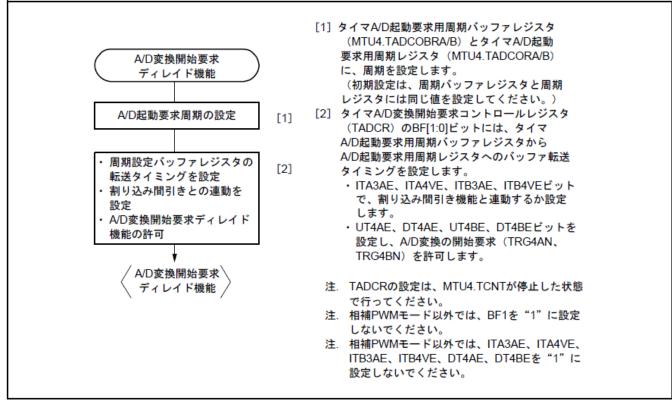

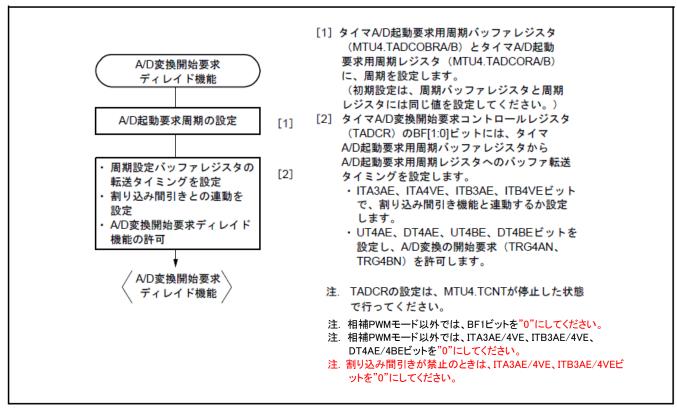

- 11.4.9 A/D 変換開始要求ディレイド機能

- (a) A/D 変換開始要求ディレイド機能の設定手順例

- < 訂正前(p.985) >

図 18.74 A/D 変換開始要求ディレイド機能の設定手順例

## < 訂正後(p.985) >

図 18.74 A/D 変換開始要求ディレイド機能の設定手順例

## 日:2015年3月11日

#### (b) A/D 変換開始要求ディレイド機能の基本動作例

#### < 訂正前(p.986) >

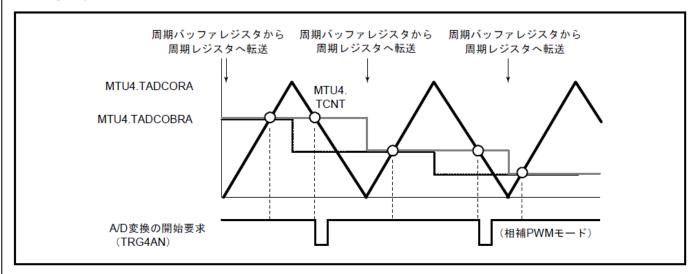

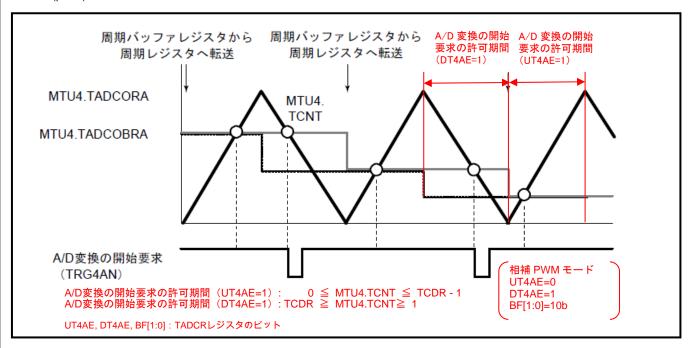

図 18.75 A/D 変換の開始要求信号(TRG4AN)の基本動作例(ユニット 0)

#### < 訂正後(p.986) >

図 18.75 A/D 変換の開始要求信号 (TRG4AN) の基本動作例(ユニット 0)

## < 追加(p.986) >

#### (3) A/D 変換の開始要求の許可期間

MTUn.TADCR の UT4AE、DT4AE、UT4BE、DT4BE ビットで許可した期間内に MTUn.TCNT と MTUn.TADCORA/B が一致したとき、それぞれの A/D 変換の開始要求(TRG4AN、TRG4BN)を行います。

相補 PWM モードで UT4AE、UT4BE ビットを"1"に設定すると、MTUn.TCNT のアップカウント期間(0≦MTUn.TCNT≦TCDR-1)に A/D 変換の開始要求を許可します。DT4AE、DT4BE ビットを"1"に設定すると、MTUnTCNT のダウンカウント期間(TCDR≧MTUn.TCNT ≧1)に A/D 変換の開始要求を許可します(図 18.75)。

相補 PWM モード以外のときは、DT4AE、DT4BE ビットを"0"に設定してください。UT4AE、UT4BE ビットに 1 を設定すると、MTUn.TCNT のアップ/ダウンカウントに関係なく、MTUn.TCNT と MTUnTADCORA/B のコンペアマッチで A/D 変換の開始要求を行います。(n=4,10)

(3) バッファ転送

タイトルを「(4) バッファ転送」に変更します。

< 訂正前(p.986) >

タイマA/D 起動要求用周期設定レジスタ (MTUn.TADCORA/B) のデータ更新は、タイマA/D 起動要求用周期設定バッファレジスタ (MTUn.TADCOBRA/B) にデータを書き込むことにより行います。タイマA/D 起動要求用周期設定バッファレジスタからタイマA/D 起動要求用周期設定レジスタへの転送タイミングは、タイマA/D 変換開始要求コントロールレジスタ (MTUn.TADCR) のBF[1:0] ビットを設定することにより選択することができます。(n=4,10)

#### < 訂正後(p.986) >

タイマA/D 起動要求用周期設定レジスタ (MTUn.TADCORA/B) のデータ更新は、タイマA/D 起動要求用周期設定バッファレジスタ (MTUn.TADCOBRA/B) にデータを書き込むことにより行います。タイマA/D 起動要求用周期設定バッファレジスタからタイマA/D 起動要求用周期設定レジスタへの転送タイミングは、タイマA/D 変換開始要求コントロールレジスタ (MTUn.TADCR) のBF[1:0] ビットを設定することにより選択することができます。(n=4,10)

相補PWMモードでバッファ転送を使用する場合、バッファ転送のタイミングについて注意事項があります。詳細は、「18.6.25 相補PWMモードにおけるA/D変換ディレイド機能の注意事項」をご覧ください。

また、相補PWMモード以外のときは、BF1 ビットを"0"にしてください。

(4) 割り込み間引き機能と連動した A/D 変換開始要求ディレイド機能

タイトルを「(5) 割り込み間引き機能と連動した A/D 変換開始要求ディレイド機能」に変更します。

< 訂正前(p.986) >

タイマA/D 変換開始要求コントロールレジスタ(TADCR)のITA3AE、ITA4VE、ITB3AE、ITB4VE ビットの設定により、割り込み間引き機能と連動してA/D 変換の開始要求(TRG4AN、TRG4BN)を行うことが可能です。MTUn.TCNT のアップカウント時、およびダウンカウント時にTRG4AN 出力を許可する設定にし、割り込み間引き機能と連動した場合のA/D 変換の開始要求信号(TRG4AN)の動作例を図18.76に示します。

また、MTUn.TCNT のアップカウント時にTRG4AN 出力を許可する設定にし、割り込み間引き機能と連動した場合のA/D 変換の開始要求信号 (TRG4AN) の動作例を図18.77 に示します。 (n=4,10)

注. 本機能は割り込み間引き機能と組み合わせて使用してください。

割り込み間引きが禁止のとき(タイマ割り込み間引き設定レジスタ(TITCR)のT3AEN、T4VEN ビットを"0"にしたとき、またはTITCR の間引き回数設定 ビット(T3ACOR、T4VCOR)を0 に設定したとき)は、割り込み間引き機能と連動しない(TADCR.ITA3AE、ITA4VE、ITB3AE、ITB4VE ビットを"0")にしてください。A/D コンバータへの変換要求信号は、TRG4ABN(TRG4AN またはTRG4BN)になりますので注意してください。

< 訂正後(p.986) >

相補PWMモードでは、タイマA/D 変換開始要求コントロールレジスタ(MTUn.TADCR)のITA3AE、ITA4VE、ITB3AE、ITB4VE ビットの設定により、割り込み間引き機能と連動してA/D 変換の開始要求(TRG4AN、TRG4BN)を行うことが可能です。MTUn.TCNT のアップカウント時、およびダウンカウント時にTRG4AN 出力を許可する設定にし、割り込み間引き機能と連動した場合のA/D 変換の開始要求信号(TRG4AN)の動作例を図18.76 に示します。

また、MTUn.TCNT のアップカウント時にTRG4AN 出力を許可する設定にし、割り込み間引き機能と連動した場合のA/D 変換の開始要求信号 (TRG4AN) の動作例を図18.77 に示します。 (n=4,10)

相補PWMモード以外では、割り込み間引き機能と連動したA/D変換開始要求ディレイド機能は使用できません。

MTUn.TADCRのITA3AE、ITA4VE、ITB3AE、ITB4VEビットを"0"にしてください。

注. 本機能は割り込み間引き機能と組み合わせて使用してください。

割り込み間引きが禁止のとき (タイマ割り込み間引き設定レジスタ (TITCR) のT3AEN、T4VEN ビットを"0"にしたとき、またはTITCR の間引き回数設定 ビット (T3ACOR、T4VCOR) を0 に設定したとき) は、割り込み間引き機能と連動しない (TADCR.ITA3AE、ITA4VE、ITB3AE、ITB4VE ビットを"0")

発行日: 2015年3月11日

にしてください。A/D コンバータへの変換要求信号は、TRG4ABN (TRG4AN またはTRG4BN) になりますので注意してください。 また、本機能使用時、MTU4.TADCORA、MTU4.TADCORA(MTU7.TADCORA、MTU7.TADCORB)には"0002h" ~ TCDRA の設定値- 2 (TCDRB の設定値- 2) の値にしてください。(n=4,10)

# < 追加(p.1023) >

#### 18.6.25 相補 PWM モードにおける A/D 変換ディレイド機能の注意事項

- MTUn.TADCOBRA、MTUn.TADCOBRB レジスタに "0"、かつ、MTUn.TADCR レジスタの UT4AE、UT4BE ビットに "1" を設定して、MTUn.TCNT カウンタの谷でバッファ転送したとき、転送直後のアップカウント期間については A/D 変換の開始要求を行いません (図 18.125)。

- MTUn.TADCOBRA、MTUn.TADCOBRB レジスタに TCDR レジスタと同じ値、かつ、MTUn.TADCR レジスタの DT4AE、DT4BE ビットに"1" を設定して、MTUn.TCNT カウンタの山でバッファ転送したとき、転送直後のダウンカウント期間については A/D 変換の開始要求を行いません(図 18.126)。

- 割り込み間引き機能と連動して A/D 変換の開始要求を行う場合、2≦MTUn.TADCORA/B≦TCDR 2 を満たすように MTUn.TADCORA、MTUn.TADCORB レジスタを設定してください。(n=4,10)

図 18.125 MTU4.TADCOBRA に"0"を書き込んだときの A/D 変換の開始要求(ユニット 0)

図 18.126 MTU4.TADCOBRA に TCDR と同じ値を書き込んだときの A/D 変換の開始要求(ユニット 0)

発行日: 2015年3月11日

【適用製品及び関連資料】

| [超/13年17] |           |                                     |       |                 |           |  |

|-----------|-----------|-------------------------------------|-------|-----------------|-----------|--|

| シリーズ      | グループ      | 関連資料                                | Rev.  | 管理番号            | MTU2 の章番号 |  |

| RX600     | RX62N/621 | RX62N グループ、RX621 グループ ユーザーズマニュアル ハー | 1. 40 | R01UH0033JJ0140 | 18        |  |

|           |           | ドウェア編                               |       |                 |           |  |

|           | RX63N/631 | RX63Nグループ、RX631グループ ユーザーズマニュアル ハー   | 1 00  |                 | 23        |  |

|           |           | ドウェア編                               | 1. 80 | R01UH0041JJ0180 |           |  |

|           | RX630     | RX630 グループ ユーザーズマニュアル ハードウェア編       | 1. 60 | R01UH0040JJ0160 | 22        |  |

| RX200     | RX210     | RX210 グループ ユーザーズマニュアル ハードウェア編       | 1. 50 | R01UH0037JJ0150 | 21        |  |

|           | RX220     | RX220 グループ ユーザーズマニュアル ハードウェア編       | 1. 10 | R01UH0292JJ0110 | 21        |  |

|           | RX21A     | RX21A グループ ユーザーズマニュアル ハードウェア編       | 1. 10 | R01UH0251JJ0110 | 22        |  |

| RX100     | RX111     | RX111 グループ ユーザーズマニュアル ハードウェア編       | 1. 10 | R01UH0365JJ0110 | 20        |  |

|           | RX113     | RX113 グループ ユーザーズマニュアル ハードウェア編       | 1. 02 | R01UH0448JJ0102 | 20        |  |

以上

発行日: 2015年3月11日